# IMPROVING POWER LEVELING RANGE OF MICROWAVE SIGNAL SOURCE USING DUAL-SLOPE LOGARITHMIC AMPLIFIER

by

# LOO CHOO KHIAM

Thesis submitted in fulfillment of the requirements for the degree of Master of Science (Engineering)

December 2007

#### ACKNOWLEDGEMENTS

This work has been carried out at Agilent Technologies as part of the Master of Science in Electrical and Electronics Engineering, in collaboration with University Science of Malaysia. The results will hopefully be of great use in any design of microwave signal source. I would like to thank everyone that has helped and encouraged me during the work of this thesis.

I would like to thank the following people. Firstly, Professor Syed Idris Syed Hassan, my supervisor for all his guidance and advice; also in reviewing my thesis report and providing his valuable comments and feedback. I am deeply indebted to Professor Syed Idris, whose help, stimulating suggestions and encouragement helped me in all the time of my research and writing of this thesis.

Also, I have to thank my mentor Phuoc Tran from Agilent Technologies, Inc., United States, for all the time he has spent on explaining the theories and practical of complex signal source systems and for all support given. Not forgetting my manager Wee Kah Khim, for giving me the opportunity to do my part-time master's degree at Agilent Technologies and for all help and support while working on the project.

My gratitude to my colleagues and all those who gave me the possibility to complete this thesis and for their stimulating support in my research work. I want to thank them for all their help, interest, valuable hints, and also in offering suggestions for improvement.

Special thanks to my wife Sharon whose patience and love enabled me to complete this work and the effort in writing the thesis.

П

### TABLE OF CONTENTS

### PAGE

| ACKNOWLEDGEMENTSII       |

|--------------------------|

| TABLE OF CONTENTSIII     |

| LIST OF TABLES VI        |

| LIST OF FIGURES          |

| LIST OF PLATESIX         |

| LIST OF SYMBOLSX         |

| LIST OF ABBREVIATIONSXII |

| ABSTRAKXIII              |

| ABSTRACTXV               |

| CHAPTER 1 INTRODUCTION   |

| 1.0 | Background        | 1 |

|-----|-------------------|---|

| 1.1 | Objective         | 2 |

| 1.2 | Scope of Research | 3 |

| 1.3 | Thesis Outline    | 7 |

# CHAPTER 2 ALC AND LOG AMP REVIEW

| 2.0 | Signal Generator Output Stages                                                            | 8  |

|-----|-------------------------------------------------------------------------------------------|----|

| 2.0 | 0.1 RF Level Accuracy                                                                     | 10 |

| 2.0 | 0.2 Attenuator Compromises                                                                | 12 |

| 2.0 | 0.3 AM and Transient Behavior                                                             | 13 |

| 2.1 | Logarithmic Amplifiers<br>1.1 Classic DC Logarithmic Amplifier<br>1.2 Dual Slope Approach | 15 |

| 2.2 | ALC Leveling Range                                                                        | 19 |

| 2.3 | Summary of Review                                                                         | 21 |

### CHAPTER 3 TECHNOLOGY AND METHODOLOGY

| 3.0                                    | Yttrium Iron Garnet (YIG) Theory         |

|----------------------------------------|------------------------------------------|

| 3.1                                    | YIG Filters                              |

| 3.3                                    | Ferrimagnetic Resonator                  |

| 3.4<br>3.4<br>3.4<br>3.4<br>3.4        | .2 Generating Negative Resistance        |

| 3.5<br>3.5<br>3.5<br>3.5<br>3.5        | .2 YIG Oscillator Output Drive Operation |

| 3.6<br>3.6<br>3.6<br>3.6               | .1 Schottky Diode                        |

| 3.7<br>3.7<br>3.7<br>3.7<br>3.7<br>3.7 | .2 AC Equivalent Of Detector Circuit     |

| 3.8<br>3.8<br>3.8                      |                                          |

| J.0                                    | .2 PIN Diode Large Signal Model          |

# CHAPTER 4 IMPLEMENTATION

| 4.0 Introduction                                      |    |

|-------------------------------------------------------|----|

| 4.0.1 Single Transistor Method                        | 72 |

| 4.0.2 Two-Transistor Method                           | 74 |

| 4.0.1 Detector Log Amp Composite                      | 75 |

|                                                       |    |

| 4.1 Dual Slope Logger                                 | 77 |

|                                                       | =0 |

| 4.2 Modulator and Exponential Current Driver          |    |

| 4.2.1 Open Loop Operation                             | 81 |

| 4.3 Amplitude Modulation                              | 82 |

| 4.3.1 Hardware Implementation of Amplitude Modulation |    |

|                                                       |    |

| 4.3.2 Amplitude Modulation Logger                     |    |

| 4.3.3 Amplitude Modulation Logger Simplification      | 88 |

| 4.3.4 Amplitude Modulation Logger Transfer Function   | 89 |

| 4.4 Al | C Circuit Improvements            | 90 |

|--------|-----------------------------------|----|

|        | Detector Non-Linear Compensation  |    |

|        | Modulator Non-Linear Compensation |    |

### CHAPTER 5 RESULTS AND ANALYSIS

| 5.0 | Design Verification Circuit | 95  |

|-----|-----------------------------|-----|

| 5.1 | Measurement Results         | 96  |

| 5.3 | Log-Amp Output Sensitivity  | 101 |

| 5.4 | ALC Bandwidth               | 104 |

| 5.5 | ALC Mode of Operations      |     |

| 5.5 | 5.1 Closed Loop Mode        |     |

| 5.5 | 5.2 Open Loop Mode          |     |

| 5.5 | 5.3 ALC Hold Mode           |     |

| 5.5 | 5.4 RF Off Mode             |     |

### CHAPTER 6 SUMMARY AND CONCLUSION

| 6.0  | Summary    |                                   | 112 |

|------|------------|-----------------------------------|-----|

| 6.1  | Conclusion |                                   | 113 |

| 6.2  | Recommend  | lations For Future Research       | 113 |

| BIBL | OGRAPHY    |                                   | 115 |

| APPE | NDIX A     | DETECTOR SELECTION CONSIDERATIONS | 118 |

| APPE | NDIX B     | PIN DIODE CHARACTERISTICS         | 122 |

### LIST OF TABLES

| Table 3.1: | Measurement Results of $P_{IN}$ versus $V_o$                | .54 |

|------------|-------------------------------------------------------------|-----|

| Table 5.1: | Output Power Readings for System using Single Slope Log Amp | .97 |

| Table 5.2: | Output Power Readings for System using Dual Slope Log Amp   | .97 |

## LIST OF FIGURES

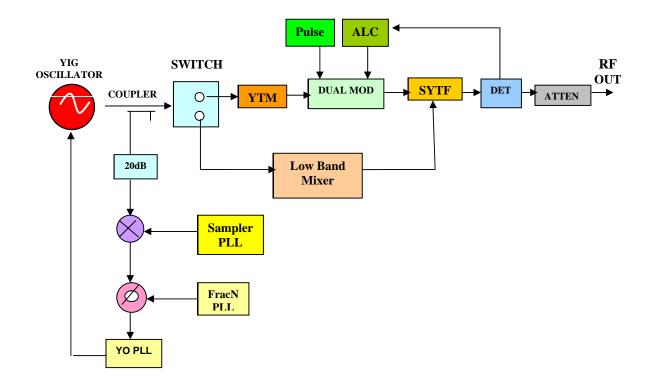

| Figure 1.1:  | Simplified RF Block Diagram of a Typical Signal Source                |

|--------------|-----------------------------------------------------------------------|

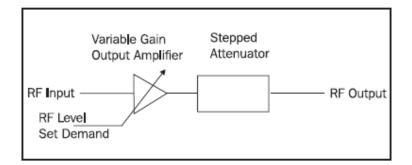

| Figure 2.1:  | Basic Variable Output Level System8                                   |

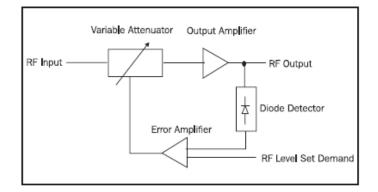

| Figure 2.2:  | ALC Output Leveling Loop9                                             |

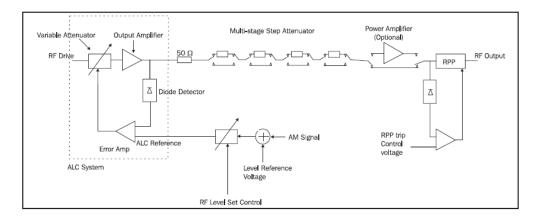

| Figure 2.3:  | A Typical Output System of a Signal Generator10                       |

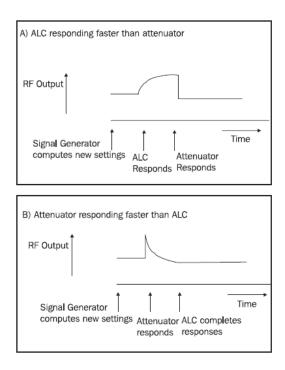

| Figure 2.4:  | Transient effects caused by the interaction of attenuator and ALC14   |

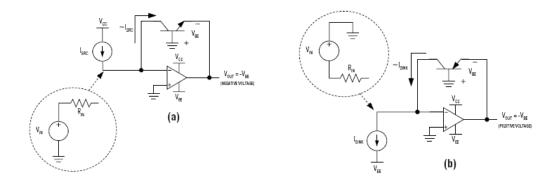

| Figure 2.5:  | Classic Log Amp in Current-Sinking and Sourcing Configuration16       |

| Figure 2.6:  | Typical Matched-Transistor Pair Log Amp17                             |

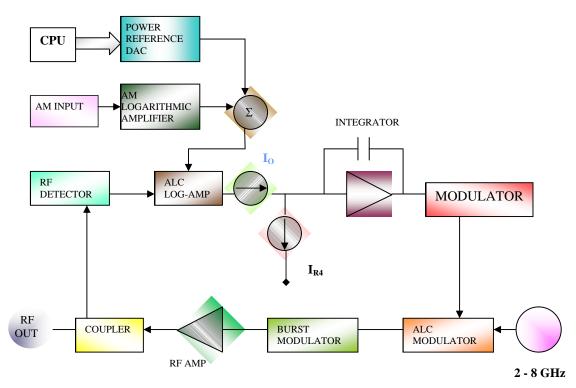

| Figure 2.7:  | ALC Loop Basic Block Diagram19                                        |

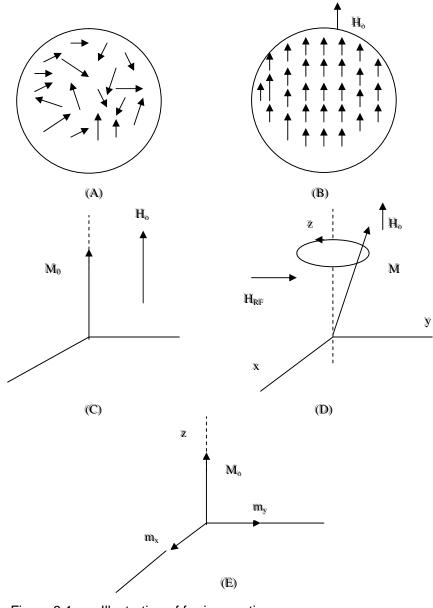

| Figure 3.1:  | Illustration of ferrimagnetic resonance23                             |

| Figure 3.2:  | Basic Elements of YIG Filter25                                        |

| Figure 3.3:  | Schematic Representation of YIG-Tuned Filter26                        |

| Figure 3.4:  | Plot of Biasing Field versus Angle of Rotation of YIG Sphere28        |

| Figure 3.5:  | YIG Oscillator magnetic structure29                                   |

| Figure 3.6:  | Equivalent Circuit of Negative Resistance Oscillator                  |

| Figure 3.7:  | Simplified Lumped Model of a Bipolar Transistor                       |

| Figure 3.8:  | Creating negative resistance using a bipolar transistor               |

| Figure 3.9:  | An amplifier with positive feedback                                   |

| Figure 3.10: | I-V Characteristic of positive feedback amplifier                     |

| Figure 3.11: | Plot of Average Negative Resistance versus Amplitude of Oscillation36 |

| Figure 3.12: | Simplified Schematic of YIG Oscillator                                |

| Figure 3.13: | YIG Oscillator Driver Block Diagram                                   |

| Figure 3.14: | Constant +10V Reference Circuit40                                     |

| Figure 3.15: | Simplified +10V Reference                                        | 41 |

|--------------|------------------------------------------------------------------|----|

| Figure 3.16: | YIG Oscillator Output Drive Circuit                              | 42 |

| Figure 3.17: | Simplified Buffer Circuit                                        | 46 |

| Figure 3.18: | Slew Limit Circuit                                               | 47 |

| Figure 3.19: | Structure of Various Types of Schottky Diodes                    | 50 |

| Figure 3.20: | Basic Diode Circuit                                              | 51 |

| Figure 3.21: | Schottky Diode Circuit                                           | 52 |

| Figure 3.22: | I-V Characteristics of Regular Diode versus Schottky Diode       | 53 |

| Figure 3.23: | Detector Circuit for Characterization                            | 54 |

| Figure 3.24: | Plot of Detector Voltage versus Input Power                      | 55 |

| Figure 3.25: | Detector Circuit For Simplified Square Law Analysis              | 55 |

| Figure 3.26: | Detector Diode Output Equivalent Circuit                         | 56 |

| Figure 3.27: | AC Equivalent of Detector Circuit                                | 57 |

| Figure 3.28: | Detector Output with a Load                                      | 58 |

| Figure 3.29: | Detector Output Showing Load Current                             | 59 |

| Figure 3.30: | Zero-Order Modified Bessel Function of the 1 <sup>st</sup> kind  | 61 |

| Figure 3.31: | Plot Of Detector Response (V) versus Incident Power (dBm)        | 62 |

| Figure 3.32: | Simplified PIN Diode Structure                                   | 62 |

| Figure 3.33: | Forward Current versus Forward Voltage of HSMP=3830 PIN Diode.   | 64 |

| Figure 3.34: | PIN Diode RF Resistance versus Forward Current at 25°C           | 65 |

| Figure 3.35: | Plot of RF Resistance versus Diode Forward Current               | 66 |

| Figure 3.36: | PIN Diode Reverse Bias Model                                     | 67 |

| Figure 3.37: | PIN Diode in a 50 $\Omega$ System                                | 67 |

| Figure 3.38: | ALC PIN Diode Modulator Circuit                                  | 68 |

| Figure 3.39: | Theoretical Plot of PIN Diode Attenuation versus Forward Current | 69 |

| Figure 3.40: | Plot of Actual Attenuation versus Forward Current                | 69 |

| Figure 3.41: | Equivalent Circuit for Modulator Analysis over Frequency         | 71 |

| Figure 3.42: | Plot of Attenuation versus Frequency                             | 71 |

| Figure 4.1:  | Single-Transistor Single Slope Logger72                                |

|--------------|------------------------------------------------------------------------|

| Figure 4.2:  | Plot of Detector Voltage versus Log Amp Output73                       |

| Figure 4.3:  | Two-Transistor Single Slope Logger74                                   |

| Figure 4.4:  | Detector Circuit with Buffer Amp75                                     |

| Figure 4.5:  | Detector Log Amp Composite Circuit76                                   |

| Figure 4.6:  | Logging Detector Voltage versus Output Power77                         |

| Figure 4.7:  | Detector Circuit with Dual Slope Logger78                              |

| Figure 4.8:  | PIN Diode Modulator Drive Circuit79                                    |

| Figure 4.9:  | Plot of Modulator Attenuation versus I <sub>MOD</sub> 80               |

| Figure 4.10: | Plot of Modulator Attenuation versus I <sub>F</sub> 81                 |

| Figure 4.11: | Block Diagram for ALC OFF82                                            |

| Figure 4.12: | Amplitude Modulation As Seen On Oscilloscope83                         |

| Figure 4.13: | Amplitude Modulation Signal as Seen on a Spectrum Analyzer84           |

| Figure 4.14: | Amplitude Modulation Hardware Implementation85                         |

| Figure 4.15: | Amplitude Modulation Logger Circuit87                                  |

| Figure 4.16: | Simplified Amplitude Modulation Logger Circuit I88                     |

| Figure 4.17: | Simplified Amplitude Modulation Logger Circuit II89                    |

| Figure 4.18: | Plots of AM Modulation Depth versus Modulation Index90                 |

| Figure 4.19: | A Typical Plot of Detector Output Voltage with Input Power at 25°C91   |

| Figure 4.20: | The Characteristics of an Actual Modulator94                           |

| Figure 5.1:  | Plot of ALC Level versus Linearity98                                   |

| Figure 5.2:  | Log Amp Output Error as a Function of $I_{IN}$ 100                     |

| Figure 5.3:  | Non-Ideal Variations of Log Amp Output100                              |

| Figure 5.4:  | Plot of Detector Voltage versus Output Power102                        |

| Figure 5.5:  | Dual Slope Logger without the Clamp Circuit104                         |

| Figure 5.6:  | Simplified ALC Block Diagram Combining Detector and Log-Amp105         |

| Figure 5.7:  | Simplified ALC Block Diagram Ignoring the Gain Blocks105               |

| Figure 5.8:  | Simplified ALC Block Diagram with Transfer Function Representation 106 |

| Figure 5.9:  | ALC in Closed Loop Mode | 109 |

|--------------|-------------------------|-----|

| Figure 5.10: | ALC in Open Loop Mode   | 110 |

| Figure 5.11: | ALC in Hold Mode        | 110 |

| Figure 5.12: | ALC in RF Off Mode      | 111 |

# LIST OF PLATES

| Plate 5.1: | A Simple Microwave Signal Source with Amplitude Modulation and |    |

|------------|----------------------------------------------------------------|----|

|            | Automatic Leveling Control Capability                          | 95 |

| Plate 5.2: | YIG Oscillator Driver and ALC Circuitry on Proto Board         | 96 |

# LIST OF SYMBOLS

| ω                                         | Angular frequency                                  |

|-------------------------------------------|----------------------------------------------------|

| R <sub>av</sub>                           | Average resistance                                 |

| $V_{BE}$                                  | Base to emitter voltage of bipolar transistor      |

| Z <sub>b</sub>                            | Bipolar transistor base impedance                  |

| Ze                                        | Bipolar transistor emitter impedance               |

| I <sub>BP</sub>                           | Breakpoint current                                 |

| f <sub>c</sub>                            | Cut-off frequency                                  |

| H <sub>o</sub>                            | DC magnetic field                                  |

| dB                                        | Decibel                                            |

| dBm                                       | Decibel with reference to 1mW                      |

| dBc                                       | Decibel with reference to carrier wave             |

| $\Delta f$                                | Delta frequency                                    |

| $\Delta T$                                | Delta time                                         |

| I <sub>D</sub>                            | Drain current of field effect transistor           |

| V <sub>DS</sub>                           | Drain to source voltage of field effect transistor |

| ۱ <sub>F</sub>                            | Forward current                                    |

| $V_{GS}$                                  | Gate to source voltage of field effect transistor  |

| GHz                                       | Gigahertz                                          |

| γ                                         | Gyromagnetic ratio                                 |

| Hz                                        | Hertz                                              |

| I <sub>in</sub> or I <sub>IN</sub>        | Input current                                      |

| $P_{in}  or  P_{IN}$                      | Input power                                        |

| $V_{\text{in}} \text{ or } V_{\text{IN}}$ | Input voltage                                      |

| V <sub>int</sub>                          | Integrator output voltage                          |

| kHz                                       | Kilohertz                                          |

| I <sub>S</sub>                            | Leakage current                                    |

- Z<sub>L</sub> Load impedance

- M<sub>o</sub> Magnetization produced by DC magnetic field

- MHz Megahertz

- μF Microfarad

- mHz Millihertz

- *m* Modulation index

- I<sub>MOD</sub> Modulator current

- *v<sub>n</sub>* Noise voltage

- I<sub>o</sub> or I<sub>out</sub> Output current

- Po or Pout Output power

- $V_o \text{ or } V_{out}$  Output voltage

- V<sub>pk</sub> Peak voltage

- V<sub>REF</sub> Reference voltage

- μ Relative permeability

- m<sub>x</sub> or m<sub>y</sub> RF magnetization components

- V<sub>SAT</sub> Saturation voltage

- R<sub>S</sub> Series resistance

- V<sub>T</sub> Thermal voltage

- *g<sub>m</sub>* Transconductance

- R<sub>V</sub> Video resistance

### LIST OF ABBREVIATIONS

| ALC                                                         | Automatic leveling loop                                                                                                                                                                                                |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AM                                                          | Amplitude modulation                                                                                                                                                                                                   |

| CW                                                          | Carrier wave                                                                                                                                                                                                           |

| DAC                                                         | Digital to analog converter                                                                                                                                                                                            |

| DET                                                         | Detector                                                                                                                                                                                                               |

| FET                                                         | Field effect transistor                                                                                                                                                                                                |

| FM                                                          | Frequency modulation                                                                                                                                                                                                   |

| IF                                                          | Intermediate frequency                                                                                                                                                                                                 |

| LAN                                                         | Local area network                                                                                                                                                                                                     |

| LO                                                          | Local oscillator                                                                                                                                                                                                       |

| LOG-AMP                                                     | Logarithmic amplifier; sometimes abbreviated as logger.                                                                                                                                                                |

| MMIC                                                        | Monolithic microwave integrated circuit                                                                                                                                                                                |

| ΟΤΑ                                                         | Operational transconductance amplifier                                                                                                                                                                                 |

| PLL                                                         | Phase lock loop                                                                                                                                                                                                        |

| PLL                                                         | T hase lock loop                                                                                                                                                                                                       |

| RF                                                          | Radio frequency                                                                                                                                                                                                        |

|                                                             |                                                                                                                                                                                                                        |

| RF                                                          | Radio frequency                                                                                                                                                                                                        |

| RF<br>RPP                                                   | Radio frequency<br>Reverse power protection                                                                                                                                                                            |

| RF<br>RPP<br>SRD                                            | Radio frequency<br>Reverse power protection<br>Step recovery diode                                                                                                                                                     |

| RF<br>RPP<br>SRD<br>SYTF                                    | Radio frequency<br>Reverse power protection<br>Step recovery diode<br>Switched YIG tuned filter                                                                                                                        |

| RF<br>RPP<br>SRD<br>SYTF<br>TC                              | Radio frequency<br>Reverse power protection<br>Step recovery diode<br>Switched YIG tuned filter<br>Temperature coefficient                                                                                             |

| RF<br>RPP<br>SRD<br>SYTF<br>TC<br>TTL                       | Radio frequency<br>Reverse power protection<br>Step recovery diode<br>Switched YIG tuned filter<br>Temperature coefficient<br>Transistor-transistor logic                                                              |

| RF<br>RPP<br>SRD<br>SYTF<br>TC<br>TTL<br>VCO                | Radio frequency<br>Reverse power protection<br>Step recovery diode<br>Switched YIG tuned filter<br>Temperature coefficient<br>Transistor-transistor logic<br>Voltage control oscillator                                |

| RF<br>RPP<br>SRD<br>SYTF<br>TC<br>TTL<br>VCO<br>VSWR        | Radio frequency<br>Reverse power protection<br>Step recovery diode<br>Switched YIG tuned filter<br>Temperature coefficient<br>Transistor-transistor logic<br>Voltage control oscillator                                |

| RF<br>RPP<br>SRD<br>SYTF<br>TC<br>TTL<br>VCO<br>VSWR<br>YIG | Radio frequency<br>Reverse power protection<br>Step recovery diode<br>Switched YIG tuned filter<br>Temperature coefficient<br>Transistor-transistor logic<br>Voltage control oscillator<br>Voltage standing wave ratio |

#### Memperbaiki Julat Penyamaan Kuasa Dalam Penjana Isyarat Gelombang Mikro Dengan Menggunakan Penguat Logaritma Dwicerun

#### ABSTRAK

Penjana atau sumber isyarat adalah penting untuk sebarang pengukuran yang memerlukan isyarat masukan sebagai perangsang. Beberapa sifat penjana isyarat yang penting adalah termasuk kejituan frekuensi dan kuasa keluaran. Selain daripada itu, kestabilan juga adalah satu faktor yang penting untuk menjamin hasil pengukuran yang boleh diharap. Walaupun sesuatu penjana isyarat ditetapkan untuk berfungsi dalam julat frekuensi and kuasa tertentu tetapi ia agak susah untuk mengekalkan kejituan kuasa keluaran dalam julat yang lebar disebabkan sifat tak linear sesetengah komponen dalam sistem.

Oleh itu, tujuan utama tesis ini adalah untuk memperkenalkan penguat logaritma dwicerun yang boleh memperbaik julat penyamaan kuasa. Selain daripada itu, fungsi pelbagai komponen dalam penjana isyarat tipikal juga dikemukakan. Pelbagai modul litar-mikro telah diintegrasikan untuk membina komponen-komponen yang asas bagi suatu sistem penjana isyarat gelombang mikro. Sistem is telah digunakan untuk menentusahkan fungsi litar ALC yang the diperbaik. Sistem yang dibina telah menggunakan pengayun YIG 2 -8 GHz dan modulator gelombang mikro untuk membekalkan fungsi modulasi amplitud, dan ia juga digunakan untuk mengekalkan kuasa keluaran yang tetap melalui skim *Automatic Leveling Control (ALC)*. Litar pengawalan pengayun boleh menalakan frekuensi pengayun dengan kepekaan 20MHz/mA. Litar-litar ALC berfungsi untuk mengimbangi sebarang perubahan dalam sistem yang boleh menjejaskan kuasa keluaran.

Kemampuan penyamaan kuasa telah diperbaik sekurang-kurangnya 10dB tanpa penukaran rujukan ALC. Penyamaan kuasa dari -20dBm ke +20dBm boleh dicapai dengan menggunakan penguat logaritma dwicerun jika dibandingkan dengan reka bentuk penguat logaritma satu cerun yang hanya mampu membuat penyamaan

XIII

kuasa dari -15dBm ke +5dBm. Ia telah terbukti bahawa penguat logaritma dwicerun telah memberikan pemampasan tambahan dalam sifat *transition* dan *linear* pengesan. Ini telah menyebabkan voltan keluaran yang berkadar terus dengan kuasa masukan (dari rendah ke tinggi).

### IMPROVING POWER LEVELING RANGE OF MICROWAVE SIGNAL SOURCE USING DUAL-SLOPE LOGARITHMIC AMPLIFIER

#### ABSTRACT

Signal generator or source is essential to any measurements requiring an input signal as stimulant. Some of the important characteristics of a signal generator include frequency and output power accuracy. Apart from that, stability is also an important factor in order to guarantee a reliable measurement result. Although a signal generator can be specified to operate within certain frequency and power range, it's hard to maintain an accurate power level over a broad range due to non-linear behavior of some components.

Therefore, the main objective of this thesis has been to develop a dual-slope logarithmic amplifier to improve the power leveling range, and also to present the operation of the various components in a typical microwave signal source in order to understand how these circuits are related. In this project, microcircuit modules have been integrated to construct the fundamental components of a microwave signal source system, which is used to verify the improved Automatic Leveling Control (ALC) circuits. The system makes use of a 2 - 8 GHz YIG oscillator, and a microwave modulator to provide amplitude modulation as well as to maintain a constant output power through ALC. The oscillator driver tunes the oscillator frequency at 20MHz/mA sensitivity. The ALC circuitry serves as an automatic compensator for any change in the system gain, which could affect the output power level.

The power leveling capability has improved by at least 10dB without changing the ALC reference. Power leveling from -20 dBm to +20 dBm is achieved using ALC with dual slope log-amp as compared with design using single slope log-amp, which is only -15dBm to +5dBm. It has proven that the dual slope log-amp circuit has provided extra compensation for the detector transition and linear characteristics, thus providing an output voltage proportional to input power (from low to high).

XV

#### CHAPTER 1 INTRODUCTION

#### 1.0 Background

A high-performance signal source combines the excellent frequency resolution, power level control, signal purity, and modulation capabilities of a high-performance synthesized signal generator with the speed and convenience of a sweep oscillator. They are ideal for the demanding requirements of signal simulation, local oscillator, and stimulus/response component or subsystem test applications. Most test measurements require precise frequency and maintaining constant output through out the test. This makes a good Automatic Leveling Loop (ALC) design essential for a high-performance signal source (Manassewitsch, 2005).

The function of the ALC loop is to control the RF power level at some point, either at the RF output or some external point. This includes doing amplitude and pulse modulation as well as keeping the power constant. Constant loop gain and wide dynamic range are achieved by logging the detector voltage and driving the modulator with an exponentiating current source driver. With an ideal square law detector, this would give the desired result (Hewlett-Packard App Note 986, 1981). This technique is used in many signal generators.

The RF detector output is processed by the detector log-amp so as to produce a voltage that is proportional to RF power in dBm. This voltage is summed with the reference and modulation inputs to the loop and integrated. If this voltage does not balance the reference inputs to the loop, the integrator output changes, which changes the modulator drive current. This changes the RF attenuation in the modulator and causes the power level downstream at the detector to change (Hunton & Ryals, 1962). The purpose of detector log-amp circuit is to first convert the leveling detector voltage into a voltage that is linear with dBm of RF power before further processing can be made. The performance requirements are: good DC accuracy over a 40 dB RF power range, and the ability to pass 1 microsecond pulses over all or most of that range. These determine the instrument specs for leveling range, AM depth, and minimum closed-loop pulse width.

The detector output is not linear with power over this range; instead it has two distinct asymptotes (Hewlett-Packard App Note 907, 1967). At lower levels it is linear with power; this is called the Square Law Region because output voltage is proportional to RF voltage squared. At higher levels it is linear with RF voltage because the detector is peak detecting at these levels. The transition between these asymptotes is smooth and gradual. In the design, it is clear that the single-slope log-amp output has different sensitivity (3mV/dB and 6mV/dB) in the Square Law and Linear region. Therefore, it is difficult to set a reference voltage for the useful range of output power, which is -20dBm to +20dBm. The firmware routine can be very complicated and compensation accuracy is also compromised due to the transition point between Square Law and Linear is different for different detector. For this reason, it is desirable to improve the log-amp circuit such that it gives a constant gain in volts/dB over the whole RF power range.

### 1.1 Objective

This thesis will investigate the building blocks used in the output stages of a RF signal generator and how they interact to affect the critical specification of power level accuracy. The concentration will be mainly on ALC subsystem as the role of the ALC is to provide control of output power. Therefore, the objectives of this thesis are to:

- (1) Improve the ALC circuits so as to achieve a leveling system that stabilizes power drift over temperature and time at least within the useful range of -20dBm to +20dBm.

- (2) Design of Dual-Slope Log-Amp that compensates for the non-linearity of the detector and Exponential Modulator Current Drive that provides a drive current proportional to attenuation level.

### 1.2 Scope of Research

The simplified RF block diagram of Figure 1.1 shows main building blocks of a typical signal generator. For the purpose of analysis, a simple CW source will be constructed, which covers 2 to 8 GHz with amplitude modulation capability and of course with internal power leveling feature. Much of the research work done involved the ALC circuitry and possible improvements.

Figure 1.1: Simplified RF Block Diagram of a Typical Signal Source

The fundamental oscillator is a 2 to 8 GHz YIG oscillator (YO) followed by a 16dB coupler (Kerwin,1986; Rhea, 2000). The signal at the coupling arm is attenuated by 20dB before driving the high performance Sampler. The main arm of the coupler feeds the input of an 8 GHz switch whose function is to divide the YO signal into low band mixer (10 MHz to 2.3 GHz at the RF output) and high band mixer (2.3 to 26.5 GHz or higher frequencies). The high band signal is multiplied by a Step Recovery Diode (SRD) inside the YIG Tuned Multiplier (YTM) to produce higher frequencies

using harmonic generation approach. MMIC amplifiers are used to boost the YO power to +25dBm approximately before turbo-charging the SRD.

Because the SRD is very rich in harmonics, the YIG-tuned filter inside the YTM alone is insufficient of rejecting the unwanted harmonics therefore sub-harmonics are often seen at the RF output. A second broad band 26.5 GHz Switch YIG Tuned Filter (SYTF) is used to achieve a cleaner signal, better than -55dBc harmonic and sub-harmonic. The Dual-Modulator between the two YIG structures provides the capabilities of Pulse and AM modulation, amplification, power leveling and low-pass filtering in the frequency range of 2 to 26.5 GHz.

The Bridge Detector following the SYTF is used to couple and detect a fraction of RF energy for automatic level control. A typical coupling factor of the coupler or bridge is 16 dB. The minimum usable leveled power of the ALC loop is –20dBm because the dynamic range of the ALC loop is limited by op-amp noise. In order to deliver an accurate and leveled power as low as –110dBm, a 90 dB step attenuator is used before the output connector.

From microcircuit standpoint, the Superhetrodyne Low Band is a self-contained module whose front-end input is taken from the YO signal separated by the Diode Switch then amplified before driving the Local Oscillator (LO) port of an internal 8 GHz mixer. The RF port of the mixer is driven by a 5.4 GHz local oscillator to down-convert a range of YO frequency from 5.41 - 7.4 GHz to 0.01 - 2.0 GHz. In Low Band, Pulse and AM modulations are done only at a single frequency (5.4 GHz) between the Voltage Controlled Oscillator (VCO) and the mixer. The IF is then amplified and filtered. Another leveling detector is integrated in the Low Band microcircuit to produce a DC voltage for ALC. The high frequency signal (2 - 26.5 GHz) and the low frequency signal (0.01 - 2 GHz) are finally combined inside the SYTF by a PIN switch.

ALC stands for Automatic Level Control. It allows the user to set power level in a closed loop fashion as well as to apply modulation on the RF signal. In the case of pulse modulation, the pulse circuit takes the TTL input waveform and pulse-modulates the RF signal; in other words, the RF power is being turned on and off according to the duty cycle of the TTL signal. There are other features provided often provided by a signal source like external leveling, power meter leveling, and millimeter head leveling. The design theory of ALC will be discussed in detailed later in Chapter 3 and 4.

Each YIG structure has its own driver, which delivers a DC current to the magnet coil in order to tune the resonant frequency (Kerwin, 1986). The YO Driver will determine the YO frequency by a programmable voltage, which is then converted to current by a voltage-to-current converter. It also generates the YO-V/GHz signal for the YTM and YTF driver to track along with the YO down the RF stream. The YTM and YTF Driver scale the YO-V/GHz voltage according to the harmonic number used. Each has its own voltage-to-current converter, which is made of low drift sense resistors, power transistor and heat sink. The current required to tune the YTM and YTF to 26.5 GHz is around 450mA; the combined power dissipation on the reference resistors and transistor is round 12 W, high enough to demand heat sink and air flow.

Sampler is a device to sample microwave signal. Without Fourier transforming a pulse train from time to frequency domain, we can visualize a sampler as the combination of a broad band microwave mixer and a comb generator. The LO port is driven by a 200 MHz signal and the comb generator generates a large number of harmonics of the LO, namely N x LO for N=1 to 100 for example. The RF, in this case is the YO frequency, can be anywhere between 2 to 8 GHz. No matter where the RF is, there is always a comb N such that the distance in MHz between N x LO and RF falls within the IF bandwidth, any other high frequency IF is rejected by the low pass filter at the output of the mixer. Effectively we have down-converted the RF signal to an IF around 80 to 150 MHz in the application. Sampler Drive is an RF circuit, which manufactures a synthesized RF frequency to approximately 100 MHz then phase lock the YO with Fractional-N Loop. The 200 to 220 MHz frequency range is selected so that the entire YO frequency range is covered without frequency gaps. For a given YO

5

frequency, there exits many sampler frequencies satisfying the phase lock equation such that the IF produced falls within its bandwidth. This will complicate the phase lock algorithm as one has to decide which comb to use and which sideband, upper or lower, to lock the YO.

Fractional-N Loop is another RF circuit, which generates a fractional frequency from 30-60 MHz at 1mHz step. The Sampler IF is phase compared with the Fractional-N frequency and the phase error is integrated on the YO Loop Board to lock the YO through the FM coil as well as the main coil. Because the main coil is an LC circuit, which has two-pole roll-off at 7 kHz, a crossover network is needed so that the high frequency error voltage will drive and lock the FM coil while the low frequency error will takes care of the main coil. Reference Loop produces numerous low noise, phasecoherent reference frequencies as follows:

- i) 100 MHz for the Low Band PLL.

- ii) 20 MHz for the Sampler Drive PLL.

- iii) 125 KHz for the 30-60 MHz Fractional-N PLL.

- iv) 10 MHz clock for the Sweep Generator.

- v) 10 MHz rear panel output for phase locking other instruments.

The above descriptions have provided an overview of a complete system. However, the scope of this thesis will be limited to analysis of circuits which are related to power level control. They include:-

- i) YIG Oscillator and its driver

- ii) RF detector characteristics and its application in ALC

- iii) PIN diode as power leveling device and modulator

- iv) Automatic Leveling Control (ALC) main components, which include logarithmic amplifier and modulator drive.

- v) Analysis of the system when these components are integrated together.

All the other components in Figure 1.1 are beyond discussion of this thesis.

### 1.3 Thesis Outline

Chapter 2, ALC and Log Amp Review, review the essential elements which make-up the output stages of a signal generator, their weaknesses and improvements that can be made in relation to implementations in this thesis. Also include classic log amp design and modifications to suit application in ALC.

Chapter 3, Technology and Methodology, include theory and analysis of components involved in order to illustrate how they interact and how changes are brought about to improve their performance. There are also simulations done.

Chapter 4, Implementation, describes the implemented improvements to existing design and advantages of doing so.

Chapter 5, Results and Analysis, presents the results of the thesis and a discussion around verifying the improved design, including analysis.

Chapter 6, Summary and Conclusion, provides a summary of improvements implemented, and discusses the conclusions made as well as future works that can be done for continuous upgrade.

The appendices contain the fundamental theory about RF detector and PIN diode, which form the basis of studies for this thesis and the system improvement design.

#### CHAPTER 2 ALC AND LOG AMP REVIEW

This chapter will review the development in the output system of a signal generator in order to improve power level accuracy it can provide. The problems associated with various components, especially ALC related circuits like the log amp will be highlighted, and how the problems can be reduced or eliminated.

### 2.0 Signal Generator Output Stages

The RF output system of a signal generator varies considerably according to the type of generator and the preferred architectures (Manassewitsch, 2005; Rohde, 1997; Crawford, 2002) favored by different manufacturers. There is however a common underlying format. Figure 2.1 illustrates the concept of a basic variable output level system. The adjustable gain block satisfies the need for a continuously variable output (Meyer et al., 1991). The stepped attenuator is required because the output level range of a practical variable gain block is insufficient to cover the operating level range needed from a professional signal source.

Figure 2.1: Basic Variable Output Level System

This very basic scheme is limited to CW and other signal formats with constant carrier amplitude modulation schemes such as FM. It also lacks the refinements of Automatic Level Control for amplitude stabilization and Reverse Power Protection (RPP) facilities. ALC also provides an opportunity to implement amplitude modulation schemes (Mazilu et al., 2004; Hunton & Ryals, 1962). A more practical scheme

employing ALC Output Leveling is shown in Figure 2.2 below. Here, an RF drive signal is applied to the output amplifier via a limited range variable attenuator (Meyer et al., 1991).

Figure 2.2: ALC Output Leveling Loop

The output from the diode detector, which is proportional to the Output Amplifier RF output level, is compared with the RF Level Set Demand in a feedback loop formed by the error amplifier and the variable attenuator. The servo action of the ALC loop ensures that gain variations in the RF drive voltage and the output amplifier do not appear in the RF output as level errors (Mazilu et al., 2004; Rohde, 1997). Figure 2.3 adds the remainder of the blocks to complete a practical output system with wide output level range, including a capability for AM, amplitude modulation. Here the error amplifier input voltage is derived from a fixed level reference voltage. The reference voltage has any amplitude modulation required to be added to the signal generator output superimposed upon it. The resulting composite signal has its level adjusted (usually by a DAC). The addition of AM to the reference voltage ensures that if the user requests AM, or other form of non-constant amplitude modulation, then the ALC system will not try to remove it.

Having obtained a precise RF level covering a limited output range the signal is then passed on to a switched multi-stage attenuator (which can use mechanical or electronic switches). The diode detector in the ALC has only a limited dynamic range (Cowley & Sorensen, 1966), so this switched attenuator is used to increase the adjustment range of the RF output. Once the signal has passed through the attenuator some generators then have an optional power amplifier which can be switched in. This position is chosen for the amplifier since it does not have to overcome the loss of the switched attenuator, or avoid its non-linearity if it is an electronic attenuator (Robins, Hughes, & Flood, 1984; Scott, 2005). So the deceptively simple connector on the front panel of the signal generator is driven by a complex output processing system which can have an impact on how the generator behaves in normal use. Understanding the limitations and compromises with different types of output systems is an important factor in choosing a signal generator.

Figure 2.3: A Typical Output System of a Signal Generator

#### 2.0.1 RF Level Accuracy

The RF output level accuracy of a signal generator is considered to be a prime specification parameter. It can also be the most difficult parameter to measure over the full frequency and level range of a signal generator (Rohde, 1997; Manassewitsch, 2005). To provide accurate output signal levels the ALC system needs to compensate for the insertion loss between the output amplifier and the output connector (Scott, 2005; Manassewitsch, 2005; Stirling, 1987). The first requirement is that the system is calibrated with all the attenuator pads switched out. If a switchable power amplifier is fitted an additional calibration is also required with it enabled to correct for the frequency response of the power amplifier and associated switching system. The

correction factors adjust the output from the output amplifier as the frequency is varied. Clearly the flatter the uncorrected output can be made with frequency the fewer the correction points that need to be applied. A typical signal generator may need a calibration point every 150 MHz, with perhaps closer intervals as the frequency increases (Rohde, 1997).

The reason for increased density of calibration data as the frequency rises is that there is more likely to be a worse Voltage Standing Wave Ratio (VSWR) and therefore more rapidly changing insertion loss (Manassewitsch, 2005). Calibration of the RF level can however be performed using an adjustment procedure and a power meter. The problems become more complex as the RF level is reduced. When attenuator pads are switched in they are unlikely to be precisely their nominal value. As a result additional correction data is applied to correct for the pads. Each attenuator pad is designed to operate in a perfect  $50\Omega$  system but the reality is different. As more attenuator pads are added their mismatches interact and cause errors that are dependent on which combination of pads is in use, and the distance between each of them. These are so called 'stacking' errors (Robins, Hughes, & Flood, 1984). It becomes harder to calibrate the attenuator. Therefore the worse the VSWR of the attenuator, the more complex the correction factors that need to be applied and the more complex the test procedure. It also causes the user increasing problems when a signal generator has poor output VSWR but tight RF level accuracy specifications. Calibration of the generator requires increasingly complex test and correction routines to be performed with very demanding load accuracy conditions.

As the output power is reduced more correction data is applied to the output system to account for attenuator stacking errors, and the harder it becomes to verify the performance with even the best power meter. The better the output VSWR the less likely it is that errors are introduced (Crawford, 2002). The easiest generators to test and use are those with a low output VSWR. What is clear is that the issue of RF Level accuracy cannot be separated from the output VSWR specification of the generator. A

11

poor output VSWR leads to increasing difficulty in verifying level accuracy and more complex calibration routines.

#### 2.0.2 Attenuator Compromises

The attenuator design on a signal generator is a critical item since its performance largely determines the RF level accuracy, particularly when the RF level is low, and has a major impact on the output VSWR (Crawford, 2002; Stirling, 1987; Rohde, 1997). The better the inherent VSWR of the attenuator the less likely it is to have interactive errors between the attenuator pads as they are switched in and out, and the simpler the adjustment and correction routines. It also leads to less additional errors and more predictable performance in typical use. Attenuators are typically implemented using either electronic or mechanical switches. Generally speaking mechanical attenuators are likely to have better VSWR (and therefore better uncorrected accuracy), not be prone to linearity errors and be more robust (in terms of accidentally applied reverse power). The mechanical switches can be either implemented using commercially available sealed switch assemblies or using an edge line switch structure. In general the sealed switches provide longer life while the edge line structures provide higher frequency cover, lower insertion loss and often better repeatability.

Electronic attenuators typically use either PIN diodes or FETs as electronic switches (Caverly, 2004; Caverly & Hiller, 1987). The FET designs provide much better low frequency cover than PIN diodes, but their performance is rather less predictable (especially at low frequency) and they make fast acting fuses if they are not protected from external power sources. PIN diode designs can be extended to higher frequencies and lower loss than FETs, but require complicated drive arrangements because of the need for heavy forward current if non-linear behavior is to be avoided. The insertion loss of electronic attenuators is generally higher than their mechanical equivalents and

12

this makes it more likely that switched high power amplifiers are required if restrictions in output level are to be avoided (the linearity issues also make this more likely).

Electronic attenuators typically have a much longer life than mechanical attenuators, have good repeatability, but are more likely to suffer changes in performance with temperature (Collin, Dudley & Donald, 2000). The linearity of solid state attenuators and their loss can have a major effect on the design of the signal generator, especially when complex modulation schemes or combining systems are deployed.

The higher typical VSWR of electronic attenuators also means they are likely to have much more complex RF level calibration systems, requiring more calibration at more levels. This leads to the need for complex interactive algorithms to optimize the performance (Rohde, 1997; Stirling, 1987). Calibration over the full power range using specialist test fixtures is much more likely to be required than with mechanical attenuators.

#### 2.0.3 AM and Transient Behavior

For an analog signal generator there are a variety of ways used to produce amplitude modulation. The simplest scheme is to use the ALC system to produce AM usually known as envelope feedback. The wanted AM signal is added to the RF Level reference voltage, shown in Figure 2.3, and therefore appears on the ALC reference. The ALC system then forces the RF output to be modulated in sympathy with this varying voltage (Green, 1983).

The ALC is required to have a large bandwidth in order to ensure the modulation is relatively distortion free (Caverly & Hiller, 1987) and the detector has to be designed to be linear (or the signal has to be pre-distorted to correct for the non-linearity). Signal generators can use envelope feedback method to achieve excellent broadband AM. The bandwidth of the ALC leads to a potential problem in suppressing positive RF level transients when changing frequency or level. A positive level transient

can prove to be destructive when the signal generator is testing high power amplifiers, or could cause erroneous failures when performing EMC tests. Signal generators can use software sequencing to suppress any significant positive transient (Stirling, 1987; Crawford, 2002).

Figure 2.4: Transient effects caused by the interaction of attenuator and ALC

The transients arise because of the interaction of the electronic (ALC) level control and the attenuator having different response times for a level change (as illustrated in Figure 2.4), or from a frequency change temporarily exposing a change in the gain of the output system with frequency (Rohde, 1997). A filter change, an oscillator change, a divider change or any other change of setting in the generator architecture could cause this. If the ALC bandwidth is high it may change the output level faster than the attenuator. If the generator uses a 10 dB step attenuator and has a top range of 0 to +10dBm, and if the level is changed from 0dBm to -1dBm, the ALC may increase the output by 9 dB before the attenuator switches a 10 dB pad into circuit. If the ALC BW is slower than the attenuator, and taking the same signal generator ranges, and if the RF level is changed from -1dBm to 0dBm the output will

rise to +9dBm until the ALC reduces the level. A worse situation can occur because of attenuator timing (Hunton & Ryals, 1962; Mazilu et al., 2004). If attenuator pads are removed before they are inserted very large transients can be generated. Take the above example with the generator providing a -21dBm signal (a 20 dB pad in circuit). If the level is changed to -11dBm (a 10 dB pad in circuit), and the 20 dB pad switches out before the 10 dB pad is switched in, a positive 10 dB transient is generated. At low levels the relative amplitudes could be much worse.

For this reason the designer of the signal generator should include software routines to sequence the RF level changes to avoid these positive transients. This leads to unavoidable negative transients. If a major change of conditions is caused by a frequency change the RF output should be temporarily suppressed to avoid positive transients (Manassewitsch, 2005). This does slow the operation of the signal generator down, but it is preferable to causing damage to the devices under test.

### 2.1 Logarithmic Amplifiers

For over half a century, engineers have used log amps for compressing signals and for computation (Fiore, 2000; Franco, 2001). Although digital ICs have mostly replaced the log amp in applications that require computing, engineers continue to use log amps to compress signals. Therefore, the log amp remains a key component in many video, fiber, medical, test and measurement, and wireless systems. As implied by the name, a logarithmic amplifier expresses an output that is related to its input by the mathematical log function (the logarithmic base is not important, as the different logbased functions are related by constants). The conversion to a logarithmic parameter is also useful in many applications where measured quantities are evaluated in decibels, or where sensors exhibit exponential or near exponential transfer characteristics.

#### 2.1.1 Classic DC Logarithmic Amplifier

In the classic pn-junction-based implementation of the DC log amp, a bipolar transistor is used to generate the logarithmic I-to-V relationship (Gayakwad, 1999;

15

Fiore, 2000; Franco, 2001). As shown in Figure 2.5, bipolar junction transistors (BJTs) are placed in the feedback path of an operational amplifier. Depending on the type of transistor chosen, NPN or PNP, the log amp is either a current-sinking or currentsourcing circuit, as shown in Figures 2.5a and 2.5b respectively. Through negative feedback, the op amp places enough output voltage on the base-emitter junction of the BJT to ensure that all available input current is drawn through the collector of the device (Watson, 1969; Sze, 1981). Note that a floating-diode implementation causes the op-amp output voltage to include input-referred offset; the grounded-base implementation does not possess this problem. With the addition of an input series resistor, the DC log amp can also function as a voltage-input device (Coughlin et al., 2000). Input voltages are converted to a proportional current though the resistor, using the op amp's virtual ground as the reference. Clearly, op-amp input-referred offset must be minimized so that accurate voltage-to-current conversion can be achieved (Fiore, 2000; Irvine, 1994; Franco, 2001). The bipolar-transistor approach is prone to temperature variations but, as will be discussed, this sensitivity is drastically reduced by using a reference current and temperature compensation.

Figure 2.5: Classic Log Amp in Current-Sinking and Sourcing Configuration

However, this classic log amp has a single sensitivity response (also known as single slope log amp), and if used in the ALC circuit to log the detector voltage can only operate for a limited range since the detector output is non-linear in nature. Therefore, it would be good to extend this log amp circuit to one that automatically compensates for the non-linear nature of the RF detectors. The dual slope log amp is introduced to suit application in ALC circuits.

#### 2.1.2 Dual Slope Approach

The purpose of log amp circuit in ALC is to convert the leveling detector voltage into a voltage that is linear with dBm of RF power. The performance requirement is good DC accuracy over a 40 dB RF power range (-20dBm to +20dBm). The detector output is not linear with power over this range (Cowley & Sorensen, 1966). At lower levels the output voltage is proportional to RF voltage squared. At higher levels it is linear with RF voltage because the detector is peak detecting at these levels. The transition between these asymptotes is smooth and gradual.

Figure 2.6: Typical Matched-Transistor Pair Log Amp

Figure 2.6 shows the basic configuration of single slope log amp designed for negative polarity detectors. The current in the emitter-base junction of a PNP transistor ( $I_{log}$ ) is controlled by the input voltage; the voltage drop across this junction is then a logarithmic function of the input voltage (Irvine, 1994; Coughlin et al., 2000). By taking the difference between the  $V_{BE}$  of two matched transistors, one of which has the logging current in it and one of which has a constant current in it, all of the temperature and unit variations in the transistors cancel out, leaving only the absolute temperature

effect discussed earlier. With an ideal square law detector, this topology would give the desired result. Another basic feature to note here is that a ground reference transfer takes place in the log amp because the logging current is generated with respect to the detector ground, and the logging transistor base is connected to ALC circuit ground. The difference between these two grounds appears across the collector-base junction of the logging transistor. Assuming this voltage is no more than a few mV, it has no effect.

In order to obtain a dual slope log amp, three dual transistors are used instead of one. The circuit is explained in detailed in Chapter 4 (Section 4.1). The middle one is the same one shown in Figure 2.6. The upper one (connected as diodes) is a second logging device that runs with a DC bias current ( $I_{bp}$ ) in each side. For logging currents smaller than the bias value, the drop across the diode is relatively constant, and the Output V<sub>o</sub> follows the same function as in the basic topology. For currents larger than the bias value, the log amp scale factor is doubled (Franco, 2001; Coughlin et al., 2000).

The transition between these regions of operation is smooth and gradual. If the breakpoint current  $I_{bp}$  corresponds to the detector output voltage at the intersection of its square law and peak detecting asymptotes, then this circuit 'unbends' the detector characteristic and gives a constant gain in volts/dB over the whole RF power range. Also, the temperature variation in the square law region of the detector characteristic can be compensated for by making the bias current in the upper logging transistor vary. As temperature increases, the detector voltage in square law gets smaller, reducing  $I_{log}$  and  $V_o$ ; by making  $I_{bp}$  increase with temperature,  $V_o$  is kept constant by the increased drop across the upper logging transistor. When the detector is in the peak detecting region, its output doesn't change with temperature; but the drop across the upper logging transistor doesn't change either because  $I_{log}$  is much larger than  $I_{bp}$ . Thus, this scheme will compensate the temperature drift the square law asymptote of the detector without messing up the peak detecting range.

18

The lower dual transistor acts as a clamp when the RF is off and  $I_{log}$  goes to zero. When this happens, V<sub>o</sub> falls to the point where the left hand transistor turns on, sinking some current through the logging transistor and preventing it from cutting off. The low end of the dynamic range is limited by the DC drift errors of the hardware. Since the lowest detector voltage to be processed is about 0.1 mV, the drift errors referred to the input must be much smaller than that. This is one reason the input buffer has a gain of 10 and that minimizes the drift contribution from the circuit following the buffer. The necessary drift performance can be obtained using low drift op amps like the OP-77.

### 2.2 ALC Leveling Range

Figure 2.7: ALC Loop Basic Block Diagram

The function of the ALC loop is to control the RF power level at some point, either at the instrument front panel or some external point (Stirling, 1987; Robins, Hughes, & Flood, 1984). Leveling at the instrument front panel is called Internal Level, and leveling at some external point is called External Level. In addition to keeping the power constant, the ALC loop can perform AM modulation and Burst modulation. In many cases we can measure the power more accurately and repeatedly than we can control it directly (Mazilu et al., 2004; Stirling, 1987), so a feedback control loop is used. Figure 2.7 shows the general idea with a typical RF section. Note that all of the RF hardware from the ALC modulator to the leveling point (the RF detector) is part of the loop and can affect its performance.

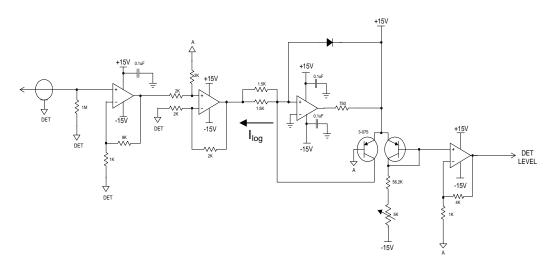

The ALC modulator is to perform power control and AM modulation, while the Burst modulator is for pulse modulation, turning RF power on and off very rapidly. After the Burst modulator is the RF amplifier. The Coupler in this block diagram is just a resistive divider. The RF detector output is processed by the detector log-amp so as to produce a current I<sub>o</sub> proportional to RF power in milliwatt.

The ALC log-amp takes two inputs, the detector voltage and the ALC reference. When the detector voltage is equal to the ALC reference, it implies that the RF output power is equal to the desired power and the output current of the log-amp is equal to  $I_{R4}$ , which is 60  $\mu$ A. The loop integrator reached its steady state condition, or no current flowing in or out of the integrator capacitor. When the detector voltage is not equal to the ALC reference, the difference current between  $I_O$  and  $I_{R4}$  will either charge or discharge the integrator to drive the RF power equal to the desired power.

The detector output voltage is a function of RF power into the detector, but it also varies with temperature and RF frequency (Cowley & Sorensen, 1966; Shashkin et al., 2005). Therefore, forcing the detector output voltage to a level does not guarantee that the RF power will remain constant as the temperature or frequency changes. A directional coupler is used to sample the RF output power by connecting a detector to the coupling arm. Its coupled arm produces a signal smaller than the level of the RF output. The coupling factor is not perfectly flat, that is, it is not constant as a function of RF frequency (Crawford, 2002; Shashkin et al., 2005). In addition, the coupler does couple some reverse power into the detector. There is a step attenuator between the coupler and the front panel RF output which is also not flat.

As the leveling loop holds the detector output voltage constant, the RF output power will vary with frequency due to the flatness of the detector, coupler, attenuator and RF hardware (Hunton & Ryals, 1962). If graphed, this variation can be approximated with several straight line segments to within  $\pm 1$ dB. Straight line variations can be compensated out by making the reference voltage change as a function of frequency. This compensation is performed by the ALC subsystem.

However, the leveling range achieved is only -20dBm to +10dBm. Constant loop gain and wide dynamic range are partially achieved by logging the detector voltage. The other part comes from the modulator drive and the series pin-diode modulator driven by an exponential current source. In common practice, the RF amplifiers are inserted between oscillator and ALC modulator and between ALC Modulator and Burst Modulator to improve matching at the same time provide power gain to make-up the power loss in modulators (Manassewitsch, 2005; Stirling, 1987). These improvements can help the system achieving leveling range of -20dBm to +20dBm, thus fulfilling the objective of this thesis.

#### 2.3 Summary of Review

In previous sections, one will notice that the introduction of one component to enhance the system will cause disadvantages or problems to the other. But the ultimate goal is still to obtain a system that ensures power level accuracy without compromising other performances. The signal generator itself requires a lot of compensation due to non-ideality of components and their interaction. Internal calibration routines have to be added to correct for these imperfections. The more routines added the longer the systems response time. One way to avoid most complicated routines is improve the time needed for ALC feedback loop to level the output power.

There has not been work published which are specific to logarithmic amplifier design in the signal generator as part of the ALC that are publicly available. The review

21

presented in this chapter therefore is on the theory of classic single-slope log-amp design and how it can be improved to provide dual-slope function specific to power leveling in the signal source. The design of dual-slope log-amp is therefore an improvement to the original single-slope log-amp design in extending the power leveling range. The new design is based on good knowledge of the original design and related theories of the output stages of the signal generator. Some of these will be presented in the next two chapters, and the rest of documents remain to be internal to Agilent Technologies.

### CHAPTER 3 TECHNOLOGY AND METHODOLOGY

#### 3.0 Yttrium Iron Garnet (YIG) Theory

Yttrium-Iron-Garnet (YIG) is a ferrimagnetic material (Kerwin, 1986; Scott, 2005) that exhibits ferrimagnetic resonance. Highly polished spheres of single crystal YIG, when placed in an RF structure under the influence of a DC magnetic field, exhibit a high Q resonance at a frequency proportional to the DC magnetic field. To understand the phenomenon of ferrimagnetic resonance, consider Figure 3.1.

Figure 3.1: Illustration of ferrimagnetic resonance

In the ferrite with no DC magnetic field applied (Figure 3.1A), there is a high density of randomly oriented magnetic dipoles, each consisting of a minute current loop formed by a spinning electron; there is no net effect because of the random orientations. When a DC magnetic field,  $H_o$ , of sufficient magnitude is applied, the dipoles align parallel to the applied field (Figure 3.1B), producing a strong net magnetization,  $M_o$ , in the direction of  $H_o$ , (Figure 3.1C).

If an RF magnetic field is applied at the right angles to  $H_o$ , the net magnetization vector will precess, at the frequency of the RF field, about an axis coincident with  $H_o$  (Figure 3.1D). The precessing magnetization vector may be represented as the sum  $M_o$  and two circularly polarized RF magnetization components  $m_x$  and  $m_y$  (Figure 3.1E). The angle of precession, and therefore the magnitudes of  $m_x$  and  $m_y$ , will be small, except at the natural precession frequency. This frequency known as the ferrimagnetic resonant frequency, is a linear function of the DC field  $H_o$ . For a low value of  $H_o$ , the angle will be large and the resonant frequency low, and vice-versa. The resonant frequency of the YIG sphere, therefore, also is proportion to the bias current.

The direction of precession is determined by the direction of the DC magnetic field and when the DC magnetic field strength is changed, the precession frequency changes (Kerwin, 1986). Useful microwave devices required a means to couple the microwave energy into the spins to produce an interaction. The best coupling is obtained when the microwave magnetic field is perpendicular to the applied DC magnetic field and the microwave energy is at the precession frequency.

Highly polished spheres of Yttrium-Iron-Garnet exhibit very high Q-factor, up to values of 10000. These spheres are physically very small, a few millimeters, or less, in diameter. The bulk of the size of YIG devices is due to the magnet assemblies required for biasing field. The resonant frequency of spherical specimens is independent of the saturation magnetization. Electrical tuning of the resonators can be accomplished over a range of about 10:1 through variation of the biasing field.

24