# THERMAL INVESTIGATIONS OF FLIP CHIP MICROELECTRONIC PACKAGE WITH NON-UNIFORM POWER DISTRIBUTION

by

**GOH TECK JOO**

June 2004

Thesis submitted in fulfillment of the requirements for the degree of Doctor of Philosophy

## DEDICATED TO

## **MY BELOVED PARENTS**

FOR THEIR YEARS OF SACRIFICE

#### **ACKNOWLEDGMENTS**

The research work is the result of several discussions I had with my research supervisors Prof. K.N. Seetharamu, Assoc. Prof. G. A. Quadir, and Assoc. Prof. Z. A. Zainal, School of Mechanical Engineering. I would like to express my deepest gratitude to them for their fine technical guidance and for the support rendered by them.

I would like to thank Dr. Chia-Pin Chiu and Dr. Abhay Watwe, Assembly Technology Development Department, Intel Corporation, as well as Assoc. Prof. Gary Solbrekken, Department of Mechanical Engineering, University of Missouri at Columbia for providing their guidance on the thermal modeling and validations.

I thank Dr. Martin Tay, Dr. Chandra Jayaram, and Dr. Ravi Mahajan, my managers in Intel, for their support and motivation in my thermal research. I am also thankful to Kin Gan, my department manager in Intel Malaysia, for taking keen interest in my research work.

I wish to express my sincere thanks to Mr. Ahmad Nordin Amir, Mr. Chee Kan Lee, and many other members of my thermal group in Intel for providing the data collection support in various stages of the research.

I am also grateful to Mr. K. Jeevan and Mr. Parthiban Arunasalam for sharing their knowledge on Genetic Algorithm.

I sincerely thank Mr. Kor Onn Lee for helping me to translate the abstract into Bahasa Malaysia.

I wish to thank Ms. Yin Peng Cheong and her family for their encouragement in the last seven years of my life.

Lastly, I take this opportunity to express my deep sense of gratitude to my family members for their patience, understanding, motivation, and support throughout the course of this work.

## **ABSTRAK**

Arah aliran pempakejan sistem-sistem dan subsistem mikroelektronik adalah ke arah pengurangan saiz dan peningkatan prestasi, di mana kedua-duanya menyumbang kepada peningkatan kadar penjanaan haba. Bukti arah aliran tersebut boleh diperhatikan daripada peningkatan tahap integrasi pada aras pakej/alat mikroelektronik. Penempatan lebih banyak fungsi dalam pakej/alat mikroelektronik yang lebih kecil menyebabkan taburan kuasa yang tidak seragam dengan kepadatan haba yang ekstrem. Keadaan ini memberi mandat supaya pengurusan terma diberi keutamaan yang lebih tinggi dalam kitar rekabentuk demi mengekalkan prestasi dan keutuhan sistem.

Dalam kajian ini, metodologi untuk analisa terma dan pencirian pakej mikroelektronik *flip chip* dengan taburan kuasa tidak seragam telah dibina. Walaupun topik ini adalah penting untuk industri mikroelektronik, jarang terdapat sebarang karya dalam penerbitan ilmiah. Untuk analisa terma, kaedah analitikal, penggunaan regresi linear berbilang (MLR), superposisi suhu, dan teknik interpolasi Lagrangian telah diperkenalkan untuk menjangka taburan suhu bagi peralatan mikroelektronik berkuasa tidak seragam. Untuk pengoptimuman, algoritma genetik telah digunakan. Kaedah-kaedah tersebut adalah berguna untuk menyelidik interaksi terma antara punca-punca haba dalam cip silikon. Parameter-parameter terma kritikal seperti jarak perletakan punca haba, tahap pelesapan haba, dan magnitud pemindahan haba perolakan telah dikaji dalam lebih daripada 900 simulasi. Perletakan optimum punca-punca haba di dalam cip silikon telah ditentukan melalui algoritma genetik. Lokasi-lokasi perletakan tersebut telah ditentusahkan dengan analisa unsur terhingga.

Berdasarkan analisis yang telah dijalankan, tatacara rekabentuk yang komprehensif, serta panduan dan syarat-syarat untuk pakej ujian terma *flip chip* telah dirangka. Keperluan-keperluan dan proses-proses terperinci yang terlibat dalam

rekabentuk cip ujian telah dibincangkan. Kajian terma telah dijalankan untuk menyelidik keupayaan dan batasan rekabentuk pakej ujian terma dalam pembangunan panduan rekabentuk. Prosedur-prosedur pengesahan dan penentukuran bagi struktur rekabentuk yang diperihalkan untuk aplikasi-aplikasi pakej ujian terma yang berbeza telah dibincangkan secara mendalam.

Kajian ini juga mendirikan satu metodologi eksperimen yang sistematik untuk mengira dan menciri prestasi terma peralatan/pakej mikroelektronik *flip chip* dengan taburan kuasa tidak seragam. Prosedur terperinci untuk menghasilkan data yang tepat, boleh-ulang, dan yang boleh dihasilkan semula serta kaedah untuk menampal termokupel dalam eksperimen telah dijelaskan. Sistem pengukuran yang dibina khas untuk mengukur prestasi keadaan mantap suatu penyelesaian terma pakej telah dijelaskan dengan terperinci. Keunikan analisa keupayaan mengukur (MCA) pada metrologi terma, untuk mendemonstrasikan kestabilan dan keupayaan sistem dalam penyediaan metrologi dengan menggunakan artifak yang stabil telah diperkenalkan. Metodologi eksperimen tersebut telah didemonstrasikan selanjutnya dalam pencirian terma dan pengoptimuman pakej melalui proses perhimpunan dua rekabentuk pakej mikropemproses Pentium® !!! Xeon<sup>TM</sup> dengan taburan kuasa tidak seragam.

#### **ABSTRACT**

The trend in packaging microelectronic systems and subsystems has been to reduce size and increase performance, both of which contribute to increase heat generation. Evidence of this trend can be observed in higher level of integration in the device/package level. Placing more functions in a smaller microelectronic device/package has resulted in non-uniform power distribution with extreme heat density, mandating that thermal management be given higher priority in the design cycle in order to maintain the system performance and reliability.

In the present work, the methodology for thermal analysis and characterization of a flip chip microelectronic package with non-uniform power distribution has been developed. Though this topic is important to the industry, hardly any paper has been published in the literature. Analytical methods, employing multiple linear regression (MLR), temperature superposition, and Langrangian interpolation techniques, to predict the temperature distribution of non-uniform powered microelectronic devices for thermal analysis and genetic algorithms for optimization are introduced. These methods are useful in investigating the thermal interactions of heat sources within the silicon chip. Critical thermal parameters i.e. the heat source placement distance, level of heat dissipation, and magnitude of convection heat transfer are examined in more than 900 simulations. Optimal placement of heat sources within silicon chip is being carried out using genetic algorithms. The locations of this placement have been verified with the finite element analysis.

Based on the analyses, comprehensive design procedures, rules and guidelines for flip chip thermal test vehicles are developed. The requirements and the detailed processes involved in the test chip design are discussed. Thermal studies have been carried out to investigate the capability and limitations of thermal test vehicle designs

in support of developing design guidelines. The validation and calibration procedures of the described design structures for different thermal test vehicle applications have been discussed in detail.

The present work also establishes a systematic experimental methodology to quantify and characterize the thermal performance of flip chip microelectronic device/package with non-uniform power distribution. The detailed procedures for accurate, repeatable, and reproducible data and the method of attaching thermocouple used in thermal experiments are outlined. The custom built measurement system for gauging steady state performance of a given package thermal solution is described in detail. The unique measurement capability analysis (MCA) on the thermal metrology to demonstrate the stability and capability of the system and metrology set-up using stable artifacts is introduced. The experimental methodology has been further demonstrated in the package thermal characterization and optimization (through manufacturing process) of two Pentium® !!!! Xeon<sup>TM</sup> microprocessor designs with non-uniform power distribution.

## **CONTENTS**

|               |                                         | Page  |

|---------------|-----------------------------------------|-------|

| ACKNOWLED     | OGEMENTS                                | iii   |

| ABSTRACT      |                                         | iv    |

| LIST OF TABLE | ES                                      | xiii  |

| LIST OF FIGUR | RES                                     | xv    |

| NOMENCLATU    | JRES                                    | xxiii |

| CHAPTER 1     | INTRODUCTION                            | 1     |

| 1.1           | IC Background and Trend                 | 3     |

| 1.2           | Packaging Technology                    | 7     |

| 1.2.1         | Area-Array Flip Chip Technology         | 12    |

| 1.2.2         | Ball Gird Array (BGA) Technology        | 13    |

| 1.2.3         | TCP                                     | 13    |

| 1.2.4         | TSOP and PQFP                           | 14    |

| 1.2.5         | CSP and DCA                             | 14    |

| 1.3           | Driving Forces on Packaging Performance | 16    |

| 1.3.1         | Package Electrical Design               | 16    |

| 1.3.2         | Package Mechanical Design               | 17    |

| 1.3.3         | Package Thermal Design                  | 18    |

| 1.4           | Summary                                 | 21    |

|               |                                         |       |

| CHAPTER 2     | LITERATURE SURVEY                       | 24    |

| 2.1           | Thermal Management Hardware             | 24    |

| 2.2.          | Thermal Analysis and Design             | 30    |

| 2.3       | Thermal Measurements                                 | 33  |

|-----------|------------------------------------------------------|-----|

| 2.4       | Thermal Test Vehicle                                 | 35  |

| 2.5       | Closure to Literature Review and Problem Enunciation | 47  |

|           |                                                      |     |

| CHAPTER 3 | ANALYTICAL INVESTIGATIONS                            | 49  |

| 3.1       | Introduction                                         | 49  |

| 3.2       | Finite Element Analysis (FEA)                        | 50  |

| 3.2.1     | Three Dimensional Finite Element Formulation         | 50  |

| 3.2.2     | Finite Element Model                                 | 53  |

| 3.2.3     | Model Validation                                     | 56  |

| 3.3       | Multiple Linear Regression (MLR) Method              | 58  |

| 3.3.1     | Research Approach                                    | 59  |

| 3.3.2     | FEA Results and Discussions                          | 60  |

| 3.3.3     | MLR Results and Discussions                          | 64  |

| 3.3.4     | Conclusions                                          | 67  |

| 3.4       | Temperature Superposition Method                     | 67  |

| 3.4.1     | Proposed Non-Uniform Power Dissipation Thermal Model | 68  |

| 3.4.2     | Finite Element Analysis                              | 70  |

| 3.4.3     | Results and Discussions                              | 70  |

| 3.4.4     | Conclusions                                          | 87  |

| 3.5       | Lagrangian Interpolation Method                      | 87  |

| 3.5.1     | Lagrangian Interpolation Function in 2D              | 87  |

| 3.5.2     | Research Method                                      | 89  |

| 3.5.3     | Verification of Methodology                          | 95  |

| 3.5.4     | Conclusions                                          | 101 |

| 3.6       | Optimization of Heat Source Placement Using Genetic Algorithm    | 101 |

|-----------|------------------------------------------------------------------|-----|

| 3.6.1     | Introduction                                                     | 101 |

| 3.6.2     | Genetic Algorithm Overview                                       | 102 |

| 3.6.3     | Analysis                                                         | 105 |

| 3.6.4     | Genetic Algorithm Parameter Selection                            | 106 |

| 3.6.5     | Results and Discussions                                          | 108 |

| 3.6.6     | Validation of GA                                                 | 113 |

| 3.6.7     | Conclusions                                                      | 113 |

| 3.7       | Summary                                                          | 114 |

|           |                                                                  |     |

| CHAPTER 4 | EXPERIMENTAL INVESTIGATIONS: ANALYSIS AND                        | 116 |

|           | DESIGN OF THERMAL TEST VEHICLE DESIGN                            |     |

| 4.1       | Introduction                                                     | 116 |

| 4.2       | Thermal Test Chip Design                                         | 118 |

| 4.3       | Thermal Package Substrate and Printed-Circuit Board (PCB) Design | 134 |

| 4.4       | Thermal Test Vehicle Validation and Calibration                  | 135 |

| 4.5       | Conclusions                                                      | 136 |

|           |                                                                  |     |

| CHAPTER 5 | EXPERIMENTAL INVESTIGATIONS: PACKAGE                             | 137 |

|           | CHARACTERIZATION METHODOLOGY                                     |     |

| 5.1       | Introduction                                                     | 137 |

| 5.2       | Thermocouple Attachment Procedures                               | 138 |

| 5.3       | Thermal Measurement System                                       | 139 |

| 5.3.1     | Wind Tunnel and Heat Sink Tester                                 | 139 |

| 5.3.2 | Data Acquisition/Control System                                      | 141 |

|-------|----------------------------------------------------------------------|-----|

| 5.3.3 | Edge Connector                                                       | 157 |

| 5.3.4 | PCB                                                                  | 159 |

| 5.3.5 | Solid State Relays for PCB                                           | 159 |

| 5.3.6 | Connecting Harnesses                                                 | 160 |

| 5.3.7 | Calibration of System Developed for Measurement                      | 161 |

| 5.4   | Measurement Capability Analysis                                      | 162 |

| 5.5   | Experimental Characterization of Workstation Class<br>Microprocessor | 163 |

| 5.5.1 | Background                                                           | 163 |

| 5.5.2 | Metrology and Design Metrics                                         | 164 |

| 5.5.3 | Experimental Setup of Thermal Metrology                              | 166 |

| 5.5.4 | Measurement Capability Analysis                                      | 167 |

| 5.5.5 | Thermal Design Target                                                | 168 |

| 5.5.6 | Characterization and Design Validation                               | 170 |

| 5.5.7 | Thermal Design Optimization through Manufacturing Process            | 176 |

| 5.5.8 | Conclusions                                                          | 178 |

| 5.6   | Experimental Characterization of Server Class Microprocessor         | 178 |

| 5.6.1 | Background                                                           | 178 |

| 5.6.2 | Metrology and Design Metrics                                         | 179 |

| 5.6.3 | Experimental Setup of Thermal Metrology                              | 184 |

| 5.6.4 | Measurement Capability Analysis                                      | 185 |

| 5.6.5 | Thermal Design Target                                                | 186 |

| 5.6.6 | Thermal Design Characterization and Validation                       | 187 |

| 5.6.7 | Conclusions                                                          | 192 |

| 5./            | Summary                                                                                                                              | 193 |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| CHAPTER 6      | CONCLUSIONS                                                                                                                          | 194 |

| 6.1            | General                                                                                                                              | 194 |

| 6.2            | Thermal Analytical Methods                                                                                                           | 195 |

| 6.3            | Thermal Test Vehicle Design                                                                                                          | 197 |

| 6.4            | Thermal Experimental Methodology                                                                                                     | 197 |

| CHAPTER 7      | RECOMMENDATIONS FOR FUTURE WORK                                                                                                      | 199 |

| REFERENCES     |                                                                                                                                      | 200 |

| APPENDIX       |                                                                                                                                      | 206 |

| APPENDIX A     | Descriptions of Effective Convection Heat Transfer Coefficient                                                                       | 207 |

| APPENDIX B     | Full Data Set for MLR Correlation                                                                                                    | 209 |

| APPENDIX C     | Descriptions and Data Set for Verification Study of<br>Temperature Superposition Method                                              | 212 |

| APPENDIX D     | Overall Specification of Thermal Measurement System                                                                                  | 230 |

| APPENDIX E     | Results and Calculations of Repeatability and Reproducibility<br>Tests for Thermal Metrology of Workstation Class<br>Microprocessors | 237 |

| APPENDIX F     | Results and Calculations of Repeatability and Reproducibility<br>Tests for Thermal Metrology of Server Class Microprocessors         | 239 |

| LIST OF PUBLIC | CATIONS                                                                                                                              | 241 |

## LIST OF TABLES

| Table No. | Title                                                                                         | Page |

|-----------|-----------------------------------------------------------------------------------------------|------|

| 1.1       | Lithography technology requirements for high performance                                      | 4    |

|           | logic devices                                                                                 |      |

| 2.1       | Summary of available thermal test chip data                                                   | 38   |

| 3.1       | Thermal model component dimensions                                                            | 55   |

| 3.2       | Isotropic thermal conductivity of components                                                  | 55   |

| 3.3       | Coordinates of Lagrangian element's nodes                                                     | 89   |

| 3.4       | Temperature contribution at the nodes of Lagrangian element for P= 1W                         | 91   |

| 3.5       | Temperature contribution at the nodes of Lagrangian element for P= 2W                         | 92   |

| 3.6       | Temperature contribution at the nodes of Lagrangian element for P= 3W                         | 93   |

| 3.7       | Temperature contribution at the nodes of Lagrangian element for $P=4W$                        | 94   |

| 3.8       | Lagrangian interpolation verification cases                                                   | 96   |

| 3.9       | Basic genetic algorithm implementation                                                        | 104  |

| 3.10      | Effects of mutation operations                                                                | 107  |

| 3.11      | Effects of crossover operations                                                               | 107  |

| 3.12      | Results of placement study for silicon chip with $P = 10 \text{ W}$                           | 109  |

| 3.13      | Results of placement study for silicon chip with $P = 10$ W and                               | 110  |

| 3.14      | two fixed heat sources<br>Results of placement study for silicon chip with $P = 15 \text{ W}$ | 111  |

| 3.15      | Results of placement study for silicon chip with $P = 20 \text{ W}$                           | 112  |

| 4.1       | Critical dimension, thermal properties, and mesh resolution used in the FEA model             | 123  |

| 5.1       | Standard Measurement Values Used in System Validation                                         | 161  |

| Table No. | Title                                                                                      | Page |

|-----------|--------------------------------------------------------------------------------------------|------|

| 5.2       | Thermal design target of Pentium® !!! Xeon <sup>TM</sup> workstation class microprocessors | 169  |

| 5.3       | Values of z for some common confidence levels                                              | 169  |

| 5.4       | Thermal design target of Pentium® !!! Xeon <sup>TM</sup> server class microprocessors      | 187  |

| A.1       | Representative values of heat transfer coefficient                                         | 207  |

## LIST OF FIGURES

| Figure No. | Title                                                                                                                         | Page |

|------------|-------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1        | Microelectronic package hierarchy                                                                                             | 2    |

| 1.2        | IC process technology trends                                                                                                  | 3    |

| 1.3        | IC feature size trends                                                                                                        | 4    |

| 1.4        | Power supply voltage trends                                                                                                   | 5    |

| 1.5        | IC devices and packaging trends                                                                                               | 6    |

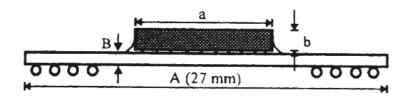

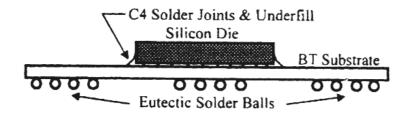

| 1.6        | Solder-bumped flip chip on PCB: direct chip attach (DCA)                                                                      | 8    |

| 1.7        | Solderless flip chip with stud bump and conductive paste                                                                      | 8    |

| 1.8        | Solderless flip chip with anisotropic conductive adhesive (ACA) on PCB (DCA)                                                  | 8    |

| 1.9        | Solderless flip chip with anisotropic conductive film (ACF) on PCB (DCA)                                                      | 9    |

| 1.10       | Typical anisotropic conductive film (ACF)                                                                                     | 9    |

| 1.11       | NEC 3-D stack-up chip scale package (CSP) for memory devices                                                                  | 9    |

| 1.12       | Overmold plastic ball grid array package (PBGA) with wire-bonding chip on organic substrate                                   | 10   |

| 1.13       | Plastic ball grid array package (PBGA) with solder bumped flip chip with organic substrate: flip chip ball grid array (FCBGA) | 10   |

| 1.14       | Ceramic ball grid array (CBGA) package with heat sink (C4: controlled-collapse-chip-connection)                               | 11   |

| 1.15       | 3M single metal layer cavity down wire bonding tape ball grid array (TBGA)                                                    | 11   |

| 1.16       | IBM area array solder-bumped flip chip tape ball grid array (TBGA) package                                                    | 11   |

| 1.17       | Olin metal ball grid array (MBGA) package with wire bonding                                                                   | 12   |

| 1.18       | IBM metal ball grid array (MBGA) package with solder-bumped flip chip                                                         | 12   |

| Figure No. | Title                                                                                                                             | Page |

|------------|-----------------------------------------------------------------------------------------------------------------------------------|------|

| 1.19       | PCB and CMOS feature dimension trends                                                                                             | 15   |

| 2.1        | Thermal resistance model for a typical microelectronic package                                                                    | 33   |

| 2.2        | One cell and the chip layout of the Infineon test chip                                                                            | 40   |

| 2.3        | Infineon G423 connection of the diode sensors                                                                                     | 40   |

| 2.4        | Layout arrangement of TTD-1000 of TEA                                                                                             | 41   |

| 2.5        | Layout arrangement of the IMEC PTCA thermal test chip                                                                             | 42   |

| 2.6        | Layout of the THBII thermal test chip of TUB-TIMA                                                                                 | 43   |

| 2.7        | Layout of a dissipater/sensor cell of the THBII chip                                                                              | 44   |

| 2.8        | Layout arrangement of the MicReD-TIMA chip                                                                                        | 45   |

| 2.9        | MicReD-TIMA suggested layout of the test chips                                                                                    | 46   |

| 3.1        | Three dimensional conduction heat transfer                                                                                        | 51   |

| 3.2        | 8-node Brick element                                                                                                              | 52   |

| 3.3        | Exploded view of 3D finite element thermal model                                                                                  | 54   |

| 3.4        | Independent matrix cells of silicon die                                                                                           | 56   |

| 3.5        | Schematic of the 2C112L test chip                                                                                                 | 57   |

| 3.6        | Comparison between model predictions and experimental measurements                                                                | 58   |

| 3.7        | Heat source placement configuration of D=5.7 mm                                                                                   | 60   |

| 3.8        | Typical temperature distribution of silicon die for $D$ =4.0 mm heat source placement configuration                               | 61   |

| 3.9        | Variation of $T_{j, max}$ for the corresponding levels of $P$ and $h_{eff}$ in heat source placement configuration of $D$ =4.0mm  | 61   |

| 3.10       | Variation of $\Theta_{ja}$ for the corresponding levels of $P$ and $h_{eff}$ in heat source placement configuration of $D$ =4.0mm | 62   |

| 3.11       | Temperature distribution of silicon die for $D = 11.3$ mm heat source placement configuration                                     | 63   |

| Figure No. | Title                                                                                                                                | Page |

|------------|--------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.12       | Variation of $T_{j, max}$ for the corresponding levels of $P$ and $h_{eff}$ in heat source placement configuration of $D = 11.3$ mm  | 63   |

| 3.13       | Variation of $\Theta_{ja}$ for the corresponding levels of $P$ and $h_{eff}$ in heat source placement configuration of $D = 11.3$ mm | 64   |

| 3.14       | Variation of 'a' and 'D' for different $h_{eff}$                                                                                     | 66   |

| 3.15       | Generalization of the data for different values of $h_{\it eff}$                                                                     | 66   |

| 3.16       | Thermal resistance network for the non uniform power distributed die                                                                 | 68   |

| 3.17       | Heating configurations: (a) Concentrated, (b) Spread, & (c) Random                                                                   | 70   |

| 3.18       | Typical temperature distribution of silicon die for Concentrated heating configuration                                               | 71   |

| 3.19       | Typical temperature distribution of silicon die for Random heating configuration                                                     | 71   |

| 3.20       | Typical temperature distribution of silicon die for Spread heating configuration                                                     | 72   |

| 3.21       | Average junction-to-ambient thermal resistance, $\Theta_{ja, avg}$ of verification cases                                             | 73   |

| 3.22       | Distribution of cell specific thermal resistance, $\zeta_i$ , for Concentrated heating configuration in forced convection mode       | 73   |

| 3.23       | Distribution of cell specific thermal resistance, $\zeta_i$ , for Spread heating configuration in forced convection mode             | 74   |

| 3.24       | Distribution of cell specific thermal resistance, $\zeta_i$ , for Random heating configuration in forced convection                  | 74   |

| 3.25       | Junction temperature distribution, $T_{j,i}$ of the edge nodes for Concentrated heating configuration in forced convection           | 75   |

| 3.26       | Junction temperature distribution, $T_{j,i}$ the off-center nodes for Concentrated heating configuration under forced convection     | 76   |

| 3.27       | Junction temperature distribution, $T_{j,i}$ the center nodes for Concentrated heating configuration under forced convection         | 76   |

| 3.28       | Junction temperature distribution, $T_{j,i}$ of the edge nodes for Concentrated heating configuration in mixed convection            | 77   |

| Figure No. | Title                                                                                                                            | Page |

|------------|----------------------------------------------------------------------------------------------------------------------------------|------|

| 3.29       | Junction temperature distribution, $T_{j,i}$ the off-center nodes for Concentrated heating configuration under mixed convection  | 77   |

| 3.30       | Junction temperature distribution, $T_{j,i}$ the center nodes for Concentrated heating configuration under mixed convection      | 78   |

| 3.31       | Junction temperature distribution, $T_{j,i}$ of the edge nodes for Spread heating configuration in forced convection             | 78   |

| 3.32       | Junction temperature distribution, $T_{j,i}$ the off-center nodes for Spread heating configuration under forced convection       | 79   |

| 3.33       | Junction temperature distribution, $T_{j,i}$ the center nodes for Spread heating configuration under forced convection           | 79   |

| 3.34       | Junction temperature distribution, $T_{j,i}$ of the edge nodes for Spread heating configuration in mixed convection              | 80   |

| 3.35       | Junction temperature distribution, $T_{j,i}$ the off-center nodes for Spread heating configuration under mixed convection        | 80   |

| 3.36       | Junction temperature distribution, $T_{j,i}$ the center nodes for Spread heating configuration under mixed convection            | 81   |

| 3.37       | Junction temperature distribution, $T_{j,i}$ of the left edge nodes for Random heating configuration in forced convection        | 82   |

| 3.38       | Junction temperature distribution, $T_{j,i}$ the left off-center nodes for Random heating configuration under forced convection  | 82   |

| 3.39       | Junction temperature distribution, $T_{j,i}$ the center nodes for Random heating configuration under forced convection           | 83   |

| 3.40       | Junction temperature distribution, $T_{j,i}$ the right off-center nodes for Random heating configuration under forced convection | 83   |

| 3.41       | Junction temperature distribution, $T_{j,i}$ of the right edge nodes for Random heating configuration in forced convection mode  | 84   |

| 3.42       | Junction temperature distribution, $T_{j,i}$ of the left edge nodes for Random heating configuration in mixed convection mode    | 84   |

| 3.43       | Junction temperature distribution, $T_{j,i}$ the left off-center nodes for Random heating configuration under mixed convection   | 85   |

| 3.44       | Junction temperature distribution, $T_{j,i}$ the center nodes for Random heating configuration under mixed convection            | 85   |

| Figure No. | Title                                                                                                                                                                                                                                                           | Page |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.45       | Junction temperature distribution, $T_{j,i}$ the right off-center nodes for Random heating configuration under mixed convection                                                                                                                                 | 86   |

| 3.46       | Junction temperature distribution, $T_{j,i}$ of the right edge nodes for Random heating configuration in mixed convection mode                                                                                                                                  | 86   |

| 3.47       | Natural coordinates for a Lagrangian element                                                                                                                                                                                                                    | 88   |

| 3.48       | Schematic of non-uniform power dissipation patterns: (a) concentrated heat source, (b) wider spread heat sources                                                                                                                                                | 95   |

| 3.49       | Comparison of: (a) prediction of Lagrangian interpolation, and (b) FEA results for verification Case #1                                                                                                                                                         | 97   |

| 3.50       | Comparison of: (a) prediction of Lagrangian interpolation, and (b) FEA results for verification Case #2                                                                                                                                                         | 97   |

| 3.51       | Comparison of: (a) prediction of Lagrangian interpolation, and (b) FEA results for verification Case #4                                                                                                                                                         | 98   |

| 3.52       | Percentage difference between the prediction from Lagrangian interpolation and the FEA results for verification (a) Case #1, (b) Case #2, and (c) Case #4.                                                                                                      | 99   |

| 3.53       | Maximum percentage difference between the Lagrangian interpolation prediction and FEA                                                                                                                                                                           | 100  |

| 3.54       | Relationship of number of matrix cells and maximum percentage difference between the Lagrangian interpolation prediction and FEA for verification Case #2                                                                                                       | 101  |

| 3.55       | Typical GA Chromosome                                                                                                                                                                                                                                           | 102  |

| 3.56       | Crossover and mutation process                                                                                                                                                                                                                                  | 103  |

| 3.57       | Heat source placement within silicon chip                                                                                                                                                                                                                       | 106  |

| 3.58       | Evolution of fitness score for GA parameter selection study                                                                                                                                                                                                     | 107  |

| 3.59       | Comparison of GA predictions with FEA results                                                                                                                                                                                                                   | 113  |

| 4.1        | Schematic of modular thermal test chip design: (a) single cell thermal test chip design, (b) medium-size thermal test chip design by combining two single-cell test chips, and (c) large-size thermal test chip design by combining four single-cell test chips | 117  |

| 4.2        | Schematics of heater design                                                                                                                                                                                                                                     | 120  |

| Figure No. | Title                                                                                                                                            | Page |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.3        | Heater leg arrangement for product burn-in simulation                                                                                            | 120  |

| 4.4        | Heater leg arrangement for thermal resistance characterization                                                                                   | 121  |

| 4.5        | Schematic of the thermal model                                                                                                                   | 123  |

| 4.6        | Temperature contour comparison between an ideal heater and a serpentine heater with $MC < 0.2$                                                   | 125  |

| 4.7        | Comparison of typical temperature profiles across the die, between the ideal heater with uniform heating and a serpentine heater with $MC < 0.2$ | 125  |

| 4.8        | Die temperature comparison between an ideal heater and a serpentine heater with $MC = 0.5$                                                       | 126  |

| 4.9        | Bump assignment of dual-application heater design                                                                                                | 127  |

| 4.10       | Fireball heater locations in thermal test chip                                                                                                   | 128  |

| 4.11       | Infra-red thermal image of an inappropriate fireball heater design with high trace resistance                                                    | 129  |

| 4.12       | Detailed schematics of fireball heater design                                                                                                    | 130  |

| 4.13       | Kelvin four-terminal measurement of standard RTD                                                                                                 | 131  |

| 4.14       | Schematics of RTD design                                                                                                                         | 132  |

| 4.15       | Number and location of temperature sensors in thermal test chip                                                                                  | 133  |

| 4.16       | $N^{\text{th}}$ order of matrix RTDs                                                                                                             | 134  |

| 5.1        | Thermocouple Attach with Epoxy                                                                                                                   | 139  |

| 5.2        | Wind tunnel                                                                                                                                      | 140  |

| 5.3        | Test head for wind tunnel                                                                                                                        | 140  |

| 5.4        | Heat sink tester                                                                                                                                 | 141  |

| 5.5        | Heat sink tester test head                                                                                                                       | 141  |

| 5.6        | Data acquisition/control system                                                                                                                  | 142  |

| 5.7        | Components of main DAC & extender                                                                                                                | 143  |

| Figure No. | Title                                                                                                           | Page |

|------------|-----------------------------------------------------------------------------------------------------------------|------|

| 5.8        | Power delivery circuit diagram                                                                                  | 145  |

| 5.9        | Circuit diagram for relays & shunt in the DAC                                                                   | 145  |

| 5.10       | Overall layout of shunts and relays with respect to their channel (C) and power supply (P) number               | 146  |

| 5.11       | Power-resistance curve for HP 6032A auto-ranging system DC power supply                                         | 147  |

| 5.12       | Power-resistance curve for HP 6624A and 6627A DC power supplies (low voltage)                                   | 147  |

| 5.13       | Power-resistance curve for HP 6624A and 6627A DC power supplies (high voltage)                                  | 148  |

| 5.14       | Layout of power leads for heaters of thermal test vehicle                                                       | 148  |

| 5.15       | Basic control structure for temperature sensors                                                                 | 152  |

| 5.16       | Switching structure for matrix temperature sensors                                                              | 153  |

| 5.17       | Default position of channel (normally closed)                                                                   | 153  |

| 5.18       | PCB overall layout                                                                                              | 155  |

| 5.19       | Relay configurations in PCB                                                                                     | 156  |

| 5.20       | Pin layout of 110-pin edge connector                                                                            | 158  |

| 5.21       | Segment of relay validation data                                                                                | 160  |

| 5.22       | Connector harness                                                                                               | 161  |

| 5.23       | Exploded isometric view of SEC cartridge design for Pentium® !!! Xeon <sup>TM</sup> workstation class processor | 164  |

| 5.24       | Schematic of thermal metrology setup for workstation class Pentium® !!! microprocessor                          | 167  |

| 5.25       | Phase I Pentium® !!! Xeon <sup>TM</sup> processor experimental characterization procedures.                     | 171  |

| 5.26       | EOL R <sub>jp</sub> measurement results                                                                         | 172  |

| 5.27       | Power cycling R <sub>ip</sub> measurement results                                                               | 172  |

| Figure No. | Title                                                                                                                                                   | Page |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.28       | Pre and Post mechanical shock test $R_{jp}$ measurement results                                                                                         | 173  |

| 5.29       | Pre and Post mechanical vibration $R_{jp}$ measurement results                                                                                          | 174  |

| 5.30       | Pre and Post Bake R <sub>jp</sub> measurement results                                                                                                   | 175  |

| 5.31       | Comparison of $R_{jp}$ measurements with and without simulated $\\$ Systest                                                                             | 177  |

| 5.32       | Exploded isometric view of SEC cartridge design for Pentium® !!! Xeon <sup>TM</sup> server processor                                                    | 179  |

| 5.33       | Thermal resistance model for Pentium® !!! Xeon <sup>TM</sup> server processor cartridge                                                                 | 180  |

| 5.34       | Non-uniform temperature distribution (normalized by lowest temperature) of Pentium® !!! Xeon <sup>TM</sup> server processor based on thermal simulation | 180  |

| 5.35       | Primary Side of 2SFTV1                                                                                                                                  | 183  |

| 5.36       | Secondary Side of 2SFTV1                                                                                                                                | 183  |

| 5.37       | Heater band of 2SFTV1 thermal test chip                                                                                                                 | 184  |

| 5.38       | Temperature sensor distribution on 2SFTV1 thermal test die                                                                                              | 184  |

| 5.39       | Schematic of Pentium® !!! Xeon <sup>TM</sup> server processor thermal metrology setup                                                                   | 185  |

| 5.40       | Pentium® !!! Xeon <sup>TM</sup> server processor experimental characterization procedures                                                               | 189  |

| 5.41       | EOL $\Psi_{jp}$ measurement results                                                                                                                     | 190  |

| 5.42       | Pre and post power cycling $\Psi_{jp}$ measurement results                                                                                              | 190  |

| 5.43       | Pre and post mechanical shock test $\Psi_{jp}$ measurement results                                                                                      | 191  |

| 5.44       | Pre and post mechanical vibration $\Psi_{jp}$ measurement results                                                                                       | 192  |

## **NOMENCLATURES**

f Processor frequency, MHz or GHz

f Number of fireball heater trace

*g* Trace-to-trace pitch, μm

h Coefficient of convection heat transfer, W/m<sup>2</sup>.K

$h_{eff}$  Effective coefficient of convection heat transfer, W/m<sup>2</sup>.K

j Number of resistance temperature sensor/detector trace

$k_{TE}$  Thermal conductivity of TEC element, W/m.K

*n* Number of heater legs

*m* Number trace per heater leg

p Dissipated power of a single cell/region within the silicon die, W

q Heat flux leaving the boundary,  $W/m^2$

W Trace width, μm

*W<sub>max</sub>* Maximum allowable trace width, μm

x Mean or average value

x<sub>c</sub> X-coordinate at the center of Lagrangian Element

y<sub>c</sub> Y-coordinate at the center of Lagrangian Element

A Heat generation or die surface area, cm<sup>2</sup>

$A_{base}$  Heat sink base area, cm<sup>2</sup>

A<sub>heater</sub> Heater area, cm<sup>2</sup>

$A_{RTD}$  Resistance temperature sensor/detector area, mm<sup>2</sup>

*COP* Coefficient of performance

COP<sub>OPT</sub> Optimum COP

Distance from the center heat source to the corner heat source, m or mm

G Area/length ratio of TEC element, m

G Heat generation of the element per unit volume, W/m<sup>3</sup>

I Current requirement, A

*I<sub>bump</sub>* Current carrying capability of a bump, A/bump

$I_{max}$  Current limit for current control thermal measurement setup, A

$I_{via}$  Current carrying capability of a via, A/via

K Thermal Conductivity, W/m.K

L<sub>heater</sub> Heater leg length, mm

*L<sub>FB</sub>* Fireball heater length, mm

*L<sub>RTD</sub>* Resistance temperature sensor/detector length, mm

MC Metal coverage or ratio of metal and non metal in test die

Number of matrix cells in chip

*N<sub>c</sub>* Number of couples

$N_{bump}$  Number of flip chip bump

$N_{via}$  Number of flip chip via

$N_{RTD}$  Number of resistance temperature sensor/detector

$N_i^{(e)}$  Shape function for Lagrangian 9-node element

P Total dissipated power, W

$\overline{P}$  Heat flux, W/cm<sup>2</sup>

$P_{cache}$  On-die integrated cache power, W

$P_{cell}$  Single cell dissipated heat, W

$P_{core}$  Core processor power, W

$P_{in}$  Work input to the refrigeration, W

$P_{non-unif}$  Total non-uniform dissipated power, W

P/T Precision to tolerance ratio, %

Q Refrigeration capacity or cooling power, W

R Cache and Core power ratio

$R_{heater}$  Electrical resistance of the serpentine metal resistor heater,  $\Omega$

$R_{ic}$  Junction-to-case thermal impedance, °C cm<sup>2</sup>/W

$R_{ip}$  Junction-to-plate thermal impedance, °C cm<sup>2</sup>/W

$R\square_{jp, max}$  Maximum allowable junction-to-plate thermal impedance, °C cm<sup>2</sup>/W

$R_{jp,spec}$  Junction-to-plate thermal impedance specification, °C cm<sup>2</sup>/W

$R_{leg}$  Electrical resistance of individual heater leg,  $\Omega$

$R_{RTD}$  Electrical resistance of the serpentine metal resistance temperature

sensor/detector,  $\Omega$

$R_s$  Metal layer sheet resistance,  $\Omega$ /square

$R_{shunt}$  Resistance of the shunt,  $\Omega$

T Temperature, °C

$T_a$  Ambient temperature,  ${}^{\circ}C$

$T_c$  Case temperature,  ${}^{\circ}C$

T<sub>exp</sub> Measured temperature from experiment, °C

$T_i$  Nodal temperature,  ${}^{\circ}C$

$T_i$  Junction temperature,  ${}^{\circ}C$

*T<sub>i, actual</sub>* Actual junction temperature, °C

$T_{i,i}$  Junction temperature of the *i* th region or cell of the die

$T_{i, max}$  Maximum die temperature,  ${}^{\circ}C$

*T<sub>j, predict</sub>* Predicted junction temperature, °C

$T_m$  Melting temperature,  ${}^{\circ}C$

T<sub>model</sub> Predicted temperature from model, <sup>o</sup>C

$T_p$  Thermal plate temperature,  ${}^{\circ}C$

$T_{AV}$  Average temperature of TEC, K

$T_C$  Cold side temperature of TEC, K

$T_H$  Hot side temperature of TEC, K

T<sub>room</sub> Room temperature, K

$V_{max}$  Voltage limit for voltage control thermal measurement setup, V

V<sub>shunt</sub> Voltage drop across the shunt, V

W<sub>FB</sub> Fireball heater width, mm

$W_{RTD}$  Resistance temperature sensor/detector width, mm

Z Figure of merit, 1/K

#### **Greek letters:**

α<sub>s</sub> Seebeck coefficient

$\rho_{TE}$  Resistivity of TEC element

σ Standard deviation of thermal data

*∆T* Temperature differential, °C

ΔT<sub>max</sub> Maximum temperature differential, °C

$\Delta V$  Voltage or potential difference, V

$\Psi_{ip}$  Junction-to-plate thermal relation resistance, °C cm<sup>2</sup>/W

$\Psi_{cp}$  Case-to-plate thermal relation resistance,  ${}^{\circ}\text{C/W}$

$\Psi_{jc}$  Non uniform power junction-to-case thermal relation resistance,  ${}^{\circ}\text{C/W}$

$\Psi_{ic}$  Uniform power junction-to-case thermal relation resistance, °C/W

$\Psi_{ip}$  Junction-to-plate thermal resistance,  ${}^{\circ}C/W$

| $\Psi_{jp,spec}$         | Junction-to-plate thermal resistance specification, °C/W            |

|--------------------------|---------------------------------------------------------------------|

| $\mathcal{O}_{ja}$       | Junction to ambient thermal resistance, °C/W                        |

| $\mathcal{O}_{ja,\;avg}$ | Average junction to ambient thermal resistance, °C/W                |

| $\mathcal{O}_{ja,\;i,}$  | Chip-location-specific junction-to-ambient thermal resistance, °C/W |

| $\zeta_i$                | Cell specific thermal resistance, °C/W                              |

#### **CHAPTER 1 – INTRODUCTION**

The invention of the bipolar transistors by John Bardeen, Walter Brattain, and William Shockley at Bell Laboratories in 1947 foreshadowed the development of generations of microelectronics. The invention of the silicon integrated circuit (IC) by Jack Kilby of Texas Instruments in 1958 and the planar process technology that was used to commercialize IC by Robert Noyce and Jean Hoerni of Fairchild Semiconductor in 1959 further excited the development of generations of scale integrations: small (SSI), medium (MSI), large (LSI), very large (VLSI), ultra large (ULSI), giga (GSI), and many others yet to come.

The IC chip is not an isolated island. It must communicate with other IC chips in a circuit through an input/output (I/O) system of interconnects. Furthermore, the IC chip and its embedded circuitry are delicate, requiring the package to both carry and protect it. Consequently, the major functions of the microelectronic package are: (1) to provide a path for electrical current that powers the circuits on the IC chip; (2) to distribute the signals onto and off the IC chip; (3) to remove the heat generated by the circuits on the IC chip; and (4) to support and protect the IC chip from hostile environments.

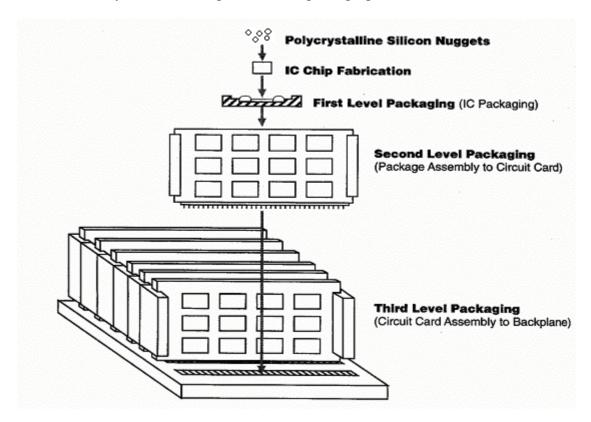

Figure 1.1 shows a schematic representation of microelectronic package hierarchy. Packaging focuses primarily on how chips may be packaged cost effectively and reliably. Packaging is an art based on the multi-disciplinary sciences of establishing interconnections ranging from zero level packages (i.e. chip level connections e.g. gold bond wire and solder bumps), to first level packages (either single- or multi-chip modules), second—level packages (e.g. printed circuit board (PCB)), and third-level packages (e.g. motherboard). It should be recognized that in this four-level hierarchy, a transistor on an IC might communicate by means of an electrical or optical signal to another IC. This signal communication poses a whole set of electrical, mechanical, thermal, chemical, and

environmental challenges which if not properly engineered and manufactured, may result in either poor communication or no communication at all. Each of theses challenges involves several key parameters or characteristics which often counteract with each other i.e. improvements in one often leads to deterioration in another. Furthermore, the current technologies are approaching numerous fundamental limits set by the properties of materials and by the structural geometries of packaging.

Figure 1.1 Microelectronic Package Hierarchy

In this chapter, the IC background and trends are briefly discussed, followed by a brief update of microelectronics packaging technologies. Driving factors of packaging performance from the electrical, mechanical, and thermal design perspectives are briefly discussed. Background on thermal management as one of the key enabling elements to microelectronics packaging development is also elaborated.

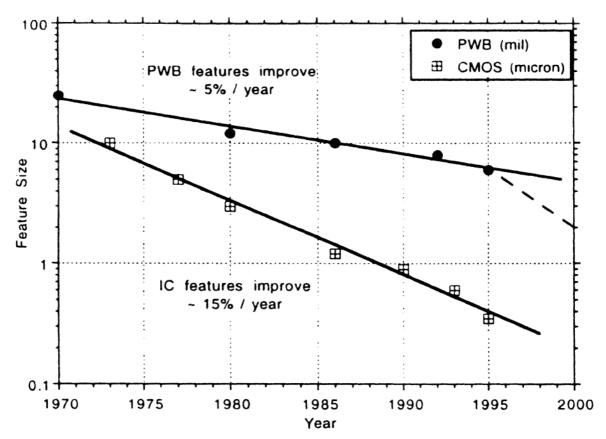

## 1.1 IC Background and Trends

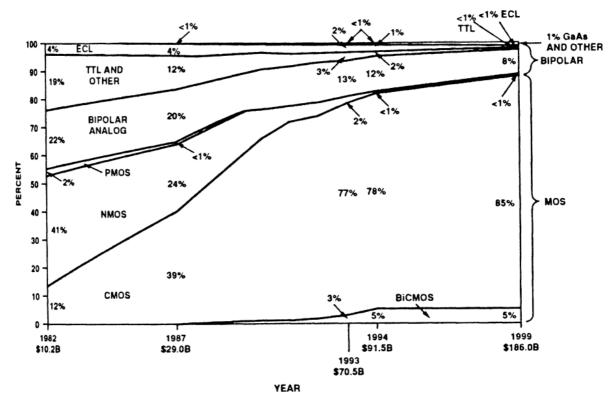

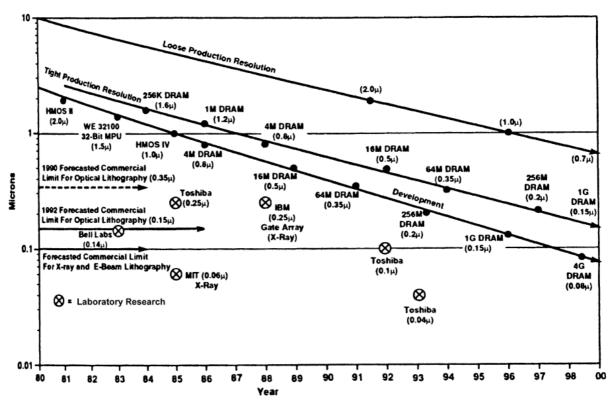

The past decade has witnessed an explosive growth in IC density i.e. number of transistors per chip and chip size. One of the key reasons is the advancement of the CMOS (complementary metal-oxide-semiconductor) process as depicted in Figure 1.2, which has very fine feature sizes and high yields (Figure 1.3.) Today, 0.13 µm is in volume production. According to International Technology Roadmap for Semiconductor (ITRS) (Semiconductor Industry Association, 2001), 90 nm technology is required for volume production in the year 2004 (Table 1.1).

Figure 1.2: IC Process Technology Trends (Tummala, 2001)

Figure 1.3: IC Feature Size Trends (Tummala, 2001)

Table 1.1 Lithography Technology Requirements for High Performance Logic Devices (Semiconductor Industry Association, 2001)

| Year of Production        | 2001    | 2002    | 2003    | 2004    | 2005    | 2006    | 2007    |

|---------------------------|---------|---------|---------|---------|---------|---------|---------|

| Line Width (nm)           | 130     | 115     | 100     | 90      | 80      | 70      | 65      |

| Gate Length (nm)          | 65      | 53      | 45      | 37      | 32      | 28      | 25      |

| Gate Oxide Thickness (nm) | 1.3-1.6 | 1.2-1.5 | 1.1-1.6 | 0.9-1.4 | 0.8-1.3 | 0.7-1.2 | 0.6-1.1 |

| Power Supply (V)          | 1.2     | 1.1     | 1.0     | 1.0     | 0.9     | 0.9     | 0.7     |

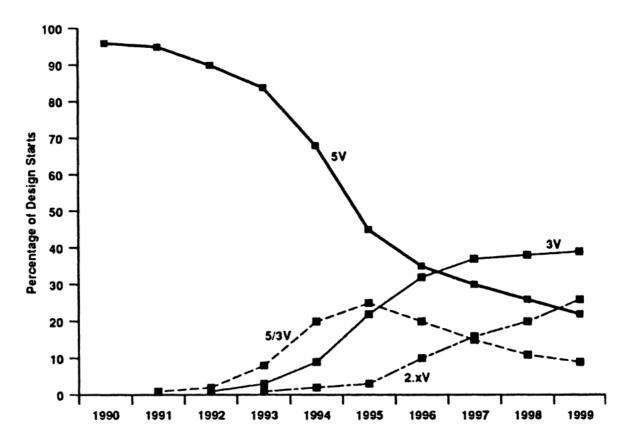

Because of the explosive growth in portable microelectronic products, the operating voltage (power supply) on the IC chip has been reducing from 5 V in the '90s to 1.0 V now, and to 0.9 V in 2005, then 0.7V in 2007 as can be seen from Figure 1.4 and Table 1.1. One of the key reasons is that the power consumption is proportional to the square of the

operating voltage – that is, the lower the operating voltage the longer the battery life for portable microelectronic products.

Figure 1.4: Transition of Operating Voltage (Tummala, 2001)

In most microelectronic products, there are four major IC devices: the microprocessor, the ASIC (application-specific IC), the cache memory, and the main memory. For example, the personal computer usually has one microprocessor; a few cache memories [e.g., fast SRAM (static random access memory)]; a few ASICs (e.g. video, sound, data path, high speed memory controller, NuBus controller, I/O controller); and many system memories such as ROM (read only memory), which contain permanent code used by software applications, and DRAM (dynamic random access memory) to store the information while power is turned on.

The microprocessor is the brain of a computing system. Some of the well known ones are: Intel's CISC (complex instruction set computing)-based microprocessor family (e.g. Pentium IV); Intel's RISC(reduce instruction-set computing)-based

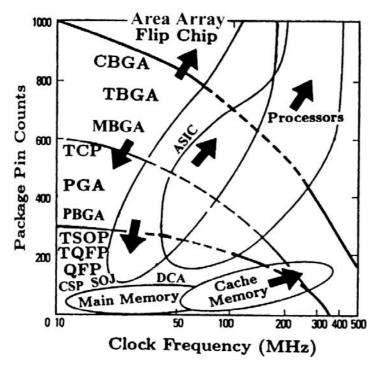

microprocessor(e.g. StrongArm, Xscale, etc.); Intel's RISC-based microprocessor (e.g. Itanium and Itanium2) IBM, Motorola, and Apple's RISC-based PowerPC microprocessors; Hewlett-Packard's RISC-based PA8000; Digital Equipment Corporation's RISC-based Alpha microprocessor; Silicon Graphics' RISC-based MIPS; AMD's CISC-based K6 and Athlon; Cyrix's CISC-based 6x86; and Sun Microsystem RISC Ultra Sparc. Both RISC-based and CISC-based microprocessors are expected to require over 1000 package pin counts and to perform over 400 MHz on chip clock frequency as shown in Figure 1.5.

Figure 1.5: IC Devices and Packaging Trends (Tummala, 2001)

The SRAMs for cache memories are expected to perform at high speed similar to that of microprocessors to prevent system data bottle necks. Even the ASICs are already running faster than 500 MHz on chip clock frequencies and have more than 1000 package pin counts.

Packaging technology is hard-pressed to meet all these requirements. Packaging becomes the bottleneck of high speed computing if advancement in packaging technologies

cannot keep pace with the semiconductor IC technologies. Thus, there is a golden opportunity to make a major contribution to the microelectronics industry by developing innovative and useful microelectronic packages.

### 1.2 Packaging Technology

For many years, the microelectronics industry has been concentrating on increasing the performance of ICs (i.e., more circuitry/silicon area operating at higher speeds) with little consideration of the fact that ICs in a microelectronic system must communicate with each other through the package containing them. As a result of the trend towards higher circuit densities and operating frequency on a chip, many effects become important considerations for packaging technology development such as: I/O requirements increasing sharply; signal transition time between ICs becoming a limiting factor to system speed; signal integrity between ICs degrading; power requirements per IC increasing thus creating a problem of heat dissipation in microelectronics packaging. All of these factors have forced microelectronics packaging technology into the spotlight in reconsideration of how ICs are being packaged. From these reconsiderations, many variants of packaging technologies have evolved to cater for different semiconductor IC devices and applications. Figure 1.5 shows some common packaging technologies available to date for the above mentioned four major IC devices: Microprocessor, ASIC, cache memory, and system memory.

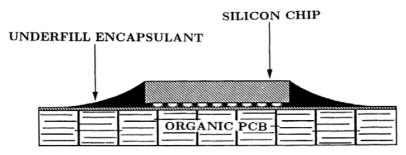

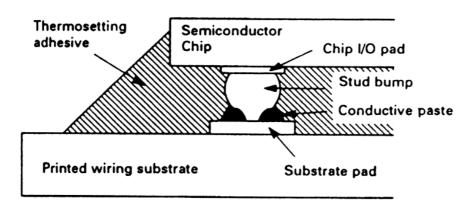

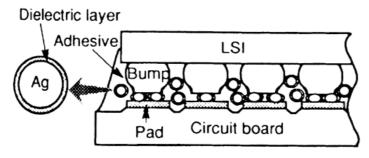

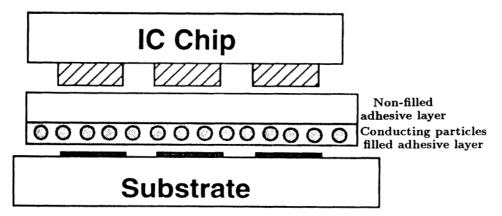

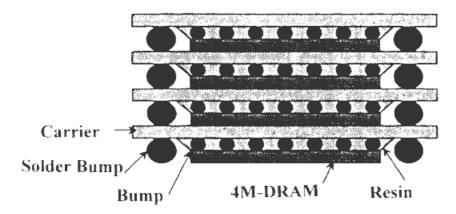

Figure 1.5 is divided into four regions (with three lines) of applications. The first region is for low-pin count IC devices, and the packaging technologies are, for example, PQFP (plastic quad flat pack), SOP (Swiss outline package), SOJ (Swiss outline J-leaded), SOIC (small outline IC), PLCC (plastic leaded chip carrier), DCA (direct chip attach on PCB), and CSP (chip scale package). Some examples of DCA are shown in Figures 1.6 through 1.9. Figure 1.6 shows a solder bumped flip chip on PCB. Figure 1.7 shows a stud

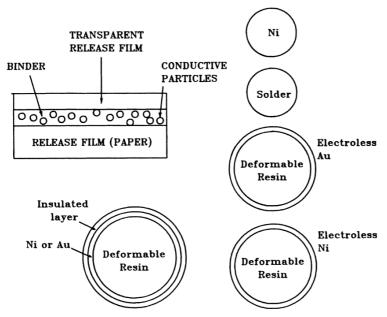

gold bumped flip chip on PCB with isotropic conductive adhesive. Figure 1.8 shows a stud gold bumped flip chip on PCB with anisotropic conductive adhesive (ACA) which has different conductivity in different directions. Figure 1.9 shows a gold bumped flip chip with anisotropic conductive film (ACF). ACA consists of thermosetting adhesive and conductive particles and it looks like paste. ACF consists of thermosetting adhesive, conductive particles, and release film and it looks like paper as can be seen from Figure 1.10. Figure 1.11 shows an example of a 3-D stacked CSP.

Figure 1.6: Solder Bumped Flip Chip on PCB (DCA)

Figure 1.7: Solderless Flip Chip with Stud Bumps and Conductive Paste (DCA)

Figure 1.8: Solderless Flip Chip with Anisotropic Conductive Adhesive (ACA) on PCB (DCA)

Figure 1.9: Solderless Flip Chip with Anisotropic Conductive Film (ACF) on PCB (DCA)

Figure 1.10: Typical Anisotropic Conductive Film (ACF)

Figure 1.11: NEC 3D Stacked Chip Scale Package (CSP) for Memory Devices

Figure 1.12: PBGA with Wire-bonding Chip on Organic Substrate

Figure 1.13: PBGA with Solder Bumped Flip Chip on Organic Substrate

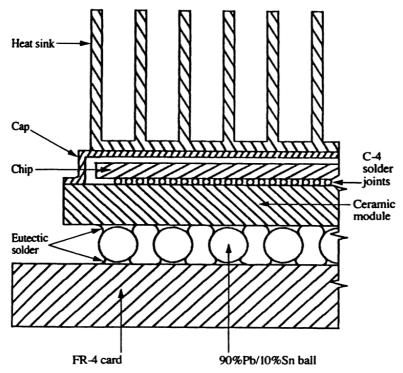

Figure 1.14: CBGA with Heat Sink (C4: Controlled-Collapse Chip Connection)

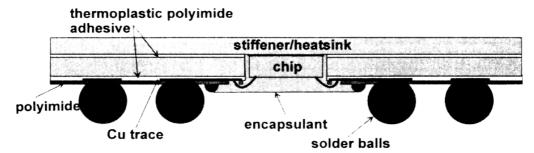

Figure 1.15: 3M Single Metal layer Cavity Down Wire-Bonding TBGA

Figure 1.16: IBM Area Array Solder Bumped Flip Chip TBGA

Figure 1.17: Olin Metal BGA (MBGA) with Wire-Bonding

Figure 1.18: IBM MBGA with Solder Bumped Flip Chip

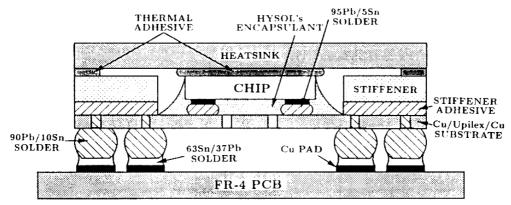

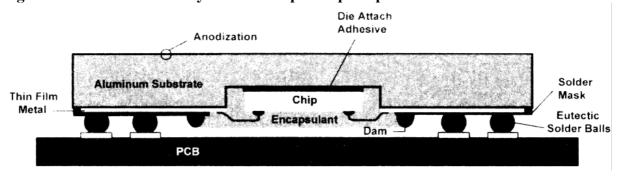

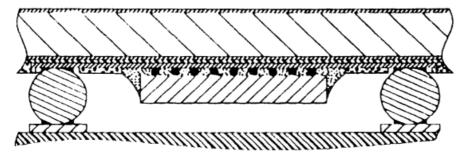

The packaging technologies such as TCP (tape carrier package), PPGA (plastic pin grid array), CPGA (ceramic pin grid array), and PBGA (plastic ball grid array) meets the

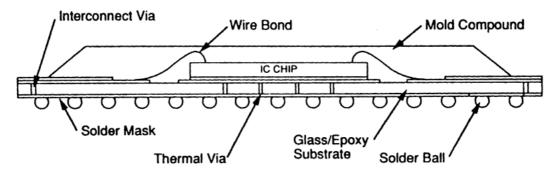

needs for the second region of applications. Some examples of PBGA are shown in Figure 1.12 for a wire bonded PBGA whereas a set of solder bumped flip chip PBGAs is shown in Figure 1.13. For higher pin-count and performance IC devices (the third region of applications), CBGA (ceramic ball grid array) is shown in Figure 1.14, TBGA (tape ball grid array) is shown in Figures 1.15 and 1.16, and MBGA (metal ball grid array) is shown in Figures 1.17 and 1.18. All of them are cost-effective packaging technology. For the forth region of applications (very high pin count and performance IC devices), area-array solder bumped flip chip technology is the solution.

## 1.2.1 Area-Array Flip Chip Technology

For high-price and high performance microprocessor and ASICs, complex IC designs require very high I/O and performance packages. For these types of IC and subsystems, area array solder bumped flip chip technology provides a viable answer to performance needs (Figure 1.15). Usually, they are packaged in a CPGA, a PPGA, a CBGA (Figure 1.14), a TBGA (Figure 1.16), or a MBGA (Figure 1.18) in a single-chip format. Recently, PBGAs with solder bumped flip clip (Figure 1.13), also known as flip chip ball grid array (FCBGA), have been considered for housing the high-price, high-speed microprocessors and ASICs.

### 1.2.2 Ball Gird Array (BGA) Technology

There are many different kinds of BGA packages (Lau, 1995). Depending on their substrates, there are CBGA (Figure 1.14), MBGA (Figures 1.17 and 1.18), TBGA (Figures 1.15 and 1.16), and PBGA (figure 1.13). Figure 1.15 shows that high I/O and performance ASICs and microprocessors, CBGA, MBGA, and TBGA could meet the high pin count (>500), power, and clock-frequency requirements but with higher costs.

Due to the fine pitch and pin-count limitations of PQFP and high cost of CBGAs, MBGAs, and TBGAs, the PBGA is a cost effective technology for package pin-count lying between 250 and 500. The major difference between PQFP and PBGA is that PQFP has a leadframe and PBGA has an organic substrate. The leadframe has been standardized for fanning the circuitry for more than 15 years, while the PBGA's substrate is still custom-designed. Today, the leadframe is cheaper than the organic substrate. Thus, in order for the PBGA packages to be popular, its substrate has to be standardized at a lower cost.

#### 1.2.3 TCP

TCP offers smaller pitches, thinner package profiles, and smaller footprints on the PCB. TCP can provide moderate-performance solutions for applications such as ASICs and microprocessors with up to about 600 package pin counts (Intel uses TCP to house its previous generation Pentium microprocessors for portable computers). It is noted that unless volume production is very high, TCP may not be cost effective due to the very high development cost of these custom-designed packages. Also, TCPs suffer the same drawbacks (e.g. peripheral chip carrier, long lead length, handling, board level manufacturing yield loss) as the POFPs.

### 1.2.4 TSOP and PQFP

Up to 208-pin (0.5 mm pitch and 28 mm body size), 240-pin (0.5 mm pitch, 32 mm body size), and 304-pin (0.5 mm pitch and 40 mm body size), PQFPs (Lau & Pao, 1997, Lau, 1994b) are the most cost-effective packages for SMT (surface mount technology). They have been used extensively for ASICs, and low-performance and low-pin-count microprocessors. Sometimes, they are used to house one or more cache memories. Currently, the price for the PQFP packages is less than one cent a pin. For example, the listing price for the 208-pin PQFP is less than US\$1.50.

TSOP is a very low profile plastic package, which is specifically designed for SRAM, DRAM, and flash memory (which retains information even when the power is turned off) devices for space –limit applications. Right now, the price for TSOP is less than one cent a pin.

### 1.2.5 CSP and DCA

One of the most cost effective packaging technologies is DCA (Lau & Pao, 1997, Lau, 1996, 1994a) as shown in Figures 1.6 through 1.9. However, because of the infrastructure and cost in supplying the known good die (KGD) and the cost and availability of corresponding fine line and spacing PCB (Figure 1.19), many technologists in the industry are still working on these issues. However, it should be noted that with the sequential build-up of PCB technologies such as DYCOstrate, plasma etched redistribution layer (PERL), surface laminar circuits (SLC), film redistribution layer (FRL), interpenetrating polymer build-up structure system (IBSS), high density interconnect (HDI), conductive adhesive bonded flex, sequential bonded films, sequential bonded sheets, and microfilled via technology, 0.5 mm (2-mil) line width and space PCBs should be available in the near future.

Figure 1.19: PCB and CMOS Feature Size Trends (Tummala, 2001)

In the meantime, a new class of technology called chip scale package (CSP) has surfaced. There are more than 40 different CSPs reported today (Lau & Lee, 1998) and most of them are used for SRAMs, DRAMs, flash memories and not-so-high-pin-count ASICs and microprocessors. The unique feature of most CSPs is the use of a substrate (carrier or interposer) to redistribute the very fine pitch (as small as 0.075 mm) peripheral pads on the chip to much larger pitch (1 mm, 0.75 mm, and 0.5 mm) area-array pads on the PCB.

The main advantages of CSP over DCA are that with the carrier (interposer), the CSP is easier to test-at-speed and burn-in for KGD. Furthermore, CSP is easier to handle, to reassemble, to rework, to standardize, to protect the die, to deal with die size shrinkage and it is subject to less infrastructure constraints. On the other hand, the advantages of DCA are that it has better electrical and thermal performance, and weighs less, smaller in size, and lower in cost.

# 1.3 Driving Factors on Packaging Performance

Historically, packaging has always been a substantial fraction of the cost of an IC (anywhere from 10% to 50%), and consequently, reducing packaging cost while maintaining reliability and performance has been the focus of packaging technology development. During this time, IC technology has transitioned from small-scale integration (SSI) in the 1960s to submicron feature size very-large-scale integration (VLSI) at the present time. Since packaging technology has not enjoyed anywhere near the performance advancement of ICs over the past 30 years, microelectronic system performance has become increasingly limited by IC packages. Thus, design decisions facing in the packaging technology development today are becoming increasingly driven by device performance.

Given the performance as one of the key primary concerns in microelectronics packaging, it is important to carefully examine the driving factors which relate performance to packaging technology choices. In general, a successful IC package can be gauged from its electrical, mechanical, and thermal performance. Factors for considerations in these areas are briefly discussed below.

## 1.3.1 Package Electrical Design

The on-chip switching speeds of ICs are continuously increasing. Furthermore, noise margins are generally decreasing at the same time. Unfortunately, chip I/O count and interconnection speed have not kept pace so that packaging interconnects now play a dominant and limiting role in determining overall system performance. Each lead from the chip to the package and each package lead to outside world has some parasitic capacitance, resistance, and inductance that limits the switching speed, distort the shape of signal passing through it, and serves as a source of electrical noise. These leads are also a source

of reliability problems. Likewise, the pattern of metal and dielectric that forms the circuitry between chips and from chips to outside world of a package contributes to the degradation of electrical performance. Consequently, some electrical design factors which must be considered include signal lead length (short parallel runs to minimize mutual inductance and crosstalk, and short runs near the ground plane to minimize the capacitive loading), use of matched impedances to avoid signal reflection, low ground resistance for minimum power supply drop, and power supply spiking caused by signal lines switching simultaneously. All of these factors are functions of geometries and materials used in packaging technology.

### 1.3.2 Package Mechanical Design

Mismatches in coefficients of thermal expansion (CTE) can cause stresses to be induced in ICs, package substrate, and packages of a microelectronic system as the temperature changes. Such stresses can be very localized, for example, under a small portion of the chip, or universal such as across an entire layer of a package substrate. Thus mechanical design aspect of microelectronic packaging technology is, in general, closely related to changes in temperature. Another mechanical property that may need to be considered is stiffness, characterized by the tensile modulus (E), which is important in area such as the chip attach where three materials (chip, package substrate, and adhesive) form two interfaces. Thermal stresses increase with increasing E and decreasing thickness of the adhesive layer. Thus, for example, a thin layer of high E adhesive material should only be used with larger area chips if CTE of the substrate or package closely matches that of the chip.

## 1.3.3 Package Thermal Design

The primary objective of thermal design or in a broader term thermal management is to control or remove the heat generated from the junctions of ICs. Heat generation in every microelectronic device and circuit is unavoidable and usually detrimental to its performance and reliability. Heat may be generated by the devices themselves or may present from other sources, both internal and external. Although heat dissipation per gate of ICs has decreased in recent years, the power dissipation per chip has increased during the same time since power per gate scales linearly with feature size, while on-chip circuit power density increases as the square of the feature size reduction ratio. Even CMOS circuit densities and operating frequencies are becoming great enough that thermal management cannot be ignored when packaging these chips.

The trend in packaging microelectronic systems, subsystems, and ICs has been to reduce in size and increase in performance, both of which contribute to heat generation and concentration. Evidence of this trend can be seen in the higher levels of integration in semiconductors and increased usage of hybrids and multichip modules (MCMs). Placing more functions in a smaller package has resulted in higher heat densities, mandating that thermal management be given a higher priority in the design cycle in order to maintain system performance and reliability.