#### TESI DI DOTTORATO

Università degli Studi di Napoli "Federico II"

DIPARTIMENTO DI INGEGNERIA BIOMEDICA, Elettronica e delle Telecomunicazioni

Dottorato di Ricerca in Ingegneria Elettronica e delle Telecomunicazioni

### TRUNCATED BINARY MULTIPLIERS WITH MINIMUM MEAN SQUARE ERROR: ANALYTICAL CHARACTERIZATION, CIRCUIT IMPLEMENTATION AND APPLICATIONS

#### VALERIA GAROFALO

Il Coordinatore del Corso di Dottorato Ch.mo Prof. Niccolò RINALDI Il Tutore Ch.mo Prof. Ettore NAPOLI

A. A. 2008-2009

To Fabrizio and to my grandparents

### Acknowledgments

First of all I would like to thank my tutor, Professor Ettore Napoli, for his constant support, his helpful suggestions, his teaching that has been crucial to achieve this goal.

Many thanks to Davide De Caro, who has always been helpful and able to solve all my problems.

A special thanks to Nicola Petra, for stimulating my activity and my interest with suggestions and discussions, for his friendship and support. The time spent in conferences wouldn't have been so great without him!

Many thanks to Professor Antonio Strollo for his priceless lessons.

I also want to thank Professor Florin Udrea for decisive help during the time spent in Cambridge and very useful meetings.

Without these people my experience through the years of the Ph.D wouldn't have been possible at all.

Thanks to HVM group of the University of Cambridge, Sumita, Prasanta, Marina, Maryline, Hatice, Wesley, Zeeshan, Floran, and to Serena and Dominik.

A really big thanks goes to the dear friends of the DIBET, Ilaria, Grazia, Michele, Maurizio, Pierluigi, Marino, Enzo, Salvatore, Matteo, Lucio, Dino, for the pleasant and funny moments we spent together, but most of all for their friendship.

I would like to thank all the people who support me since always, with great patience, great love... Alessio, Marco, Sara, Daniela, Gianfranco, Federica, Valentina, Marianne.

The final most important thanks goes to my parents and my sister. They make everything possible, they are my strength, my joy.

v

## Contents

| Ac | know    | vledgme | ents                                        | vi   |

|----|---------|---------|---------------------------------------------|------|

| Co | onten   | ts      |                                             | ix   |

| Li | st of l | Figures |                                             | xvii |

| Li | st of [ | Fables  |                                             | XX   |

| No | otatio  | ns      |                                             | xxi  |

| In | trodu   | ction   |                                             | XXV  |

| 1  | Bina    | ary Mu  | ltiplication                                | 1    |

|    | 1.1     | Partial | -Product Generation                         | 1    |

|    |         | 1.1.1   | Unsigned Multiplication                     | 2    |

|    |         | 1.1.2   | Two's Complement Multiplication             | 3    |

|    |         | 1.1.3   | Mixed-Operand Multiplication                | 4    |

|    | 1.2     | Full-w  | ridth Multiplier                            | 5    |

|    |         | 1.2.1   | Wallace-Tree Multiplier                     | 5    |

|    |         | 1.2.2   | -                                           | 7    |

|    |         | 1.2.3   | Array Multiplier                            | 8    |

|    |         | 1.2.4   | Three Dimensional Minimization (TDM) method | 11   |

|    | 1.3     | Trunca  | ated Multiplier                             | 12   |

|    |         | 1.3.1   | Full Rounded (Round-to-Nearest) Multiplier  | 14   |

|    |         | 1.3.2   | Constant Correction Methods                 | 15   |

|    |         | 1.3.3   | Variable Correction Methods                 | 16   |

|    | 1.4     | Conclu  | usion                                       | 21   |

vii

| 2 | LM  | S Truncated Multiplier                                                                                 |

|---|-----|--------------------------------------------------------------------------------------------------------|

|   | 2.1 | Definitions and Assumptions                                                                            |

|   | 2.2 | Error Analysis for Truncated Multiplier                                                                |

|   |     | 2.2.1 Statistical Properties of the Truncation Error $(e_{\text{trunc}})$ .                            |

|   |     | 2.2.2 Statistical Properties of the Erasing Error $(e_{\text{erasing}})$ .                             |

|   |     | 2.2.3 Optimal Compensation Function and Error Lower                                                    |

|   |     | Bound                                                                                                  |

|   | 2.3 | Optimal Compensation Function                                                                          |

|   |     | 2.3.1 The Intrinsic Error                                                                              |

|   | 2.4 | Linear compensation function.                                                                          |

|   | 2.5 | Linear Coefficients Quantization                                                                       |

|   |     | 2.5.1 Optimal Quantized Coefficients                                                                   |

|   | 2.6 | Mean Square Error<br>2.6.1 Analytical calculation of $\varepsilon_{\text{total}}^2$ for LMS1b function |

|   |     | 2.6.1 Analytical calculation of $\varepsilon_{\text{total}}^2$ for LMS1b function .                    |

|   |     | 2.6.2 Analytical calculation of $\varepsilon_{\text{total}}^2$ for LMS2b function .                    |

|   |     | 2.6.3 Results                                                                                          |

|   | 2.7 | Maximum Absolute Error                                                                                 |

|   | 2.8 | Signed and Mixed-Operand Multipliers                                                                   |

|   | 2.9 | Conclusions                                                                                            |

| 3 | VLS | SI implementation and Performances                                                                     |

|   | 3.1 | Truncated Multipliers Implementations                                                                  |

|   |     | 3.1.1 Implementation of LMS1b truncated multipliers                                                    |

|   |     | 3.1.2 Implementations of LMS2b truncated multipliers                                                   |

|   | 3.2 | Truncated Multipliers Performances                                                                     |

|   |     | 3.2.1 Mean Square Error Performances                                                                   |

|   |     | 3.2.2 Maximum Absolute Error Performances                                                              |

|   |     | 3.2.3 Electrical Performances (Area Occupation, Power                                                  |

|   |     | Dissipation, Propagation Delay)                                                                        |

|   |     | 3.2.4 Area versus Accuracy Trade-off                                                                   |

|   | 3.3 | Experimental Verification                                                                              |

|   | 3.4 | Conclusions                                                                                            |

| 4 | LM  | S Truncated Squarer                                                                                    |

| 1 | 4.1 | Folded squarer   Subscription                                                                          |

|   | т.1 | 4.1.1 Unsigned folded squarer                                                                          |

|   |     | 4.1.1     Onsigned folded squarer       4.1.2     Signed folded squarer                                |

|   | 4.2 | Truncated squarer                                                                                      |

|   | 4.2 | Optimal compensation function                                                                          |

|   | 4.3 |                                                                                                        |

|    |        | 4.3.1 Optimal compensation function $f_{opt}(IC)$ when $n_{eq}$ is |            |

|----|--------|--------------------------------------------------------------------|------------|

|    |        | 4.3.2 Optimal compensation function $f_{opt}(IC)$ when $n_{eq}$ is | 100        |

|    |        |                                                                    | 103        |

|    | 4.4    | Optimal Linear Compensation function                               | 106        |

|    | 4.5    | VLSI Implementation                                                | 109        |

| 5  | FIR    | filter                                                             | 113        |

|    | 5.1    | FIR filter with truncated MAC                                      | 114        |

|    | 5.2    | VLSI implementation                                                | 118        |

|    |        | 5.2.1 FIR synthesis                                                | 118        |

|    |        | 5.2.2 Comparison with the analytical results                       | 119        |

|    |        | 5.2.3 Effect of the probability distribution of the input on the   |            |

|    |        | error                                                              | 123        |

|    |        | 5.2.4 Example of FIR filter                                        | 124        |

|    | 5.3    | Conclusion                                                         | 125        |

| 6  | Tem    | perature Control for Gas Sensors                                   | 129        |

|    | 6.1    | Resistive gas sensors                                              | 129        |

|    |        | 6.1.1 Interface Circuitry                                          | 131        |

|    | 6.2    | Temperature Control                                                | 132        |

|    |        |                                                                    | 133        |

|    |        | 6.2.2 PI control                                                   | 135        |

|    |        | 6.2.3 Mixed control                                                | 137        |

|    | 6.3    | Silicon Implementation                                             | 138        |

| Co | onclus | sion                                                               | 143        |

| A  | Intr   | insic Error                                                        | 147        |

|    | A.1    |                                                                    | 147        |

|    |        |                                                                    |            |

|    | A.2    | Computing the covariance $\text{COV}_{i \ i \ l \ m}(A)$           | 147        |

|    |        |                                                                    | 147<br>149 |

# **List of Figures**

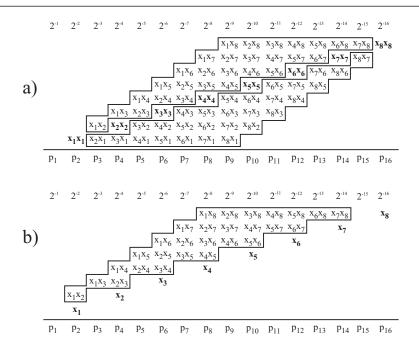

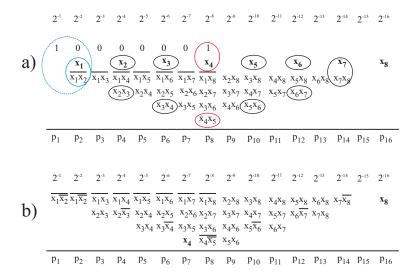

| 1.1  | Unsigned Partial Products matrix, $n = 8$                                                                                                                                                                                                                                | 2  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Two's complement Partial Products matrix, $n = 8$                                                                                                                                                                                                                        | 3  |

| 1.3  | Mixed-operand Partial Products matrix, $n = 8$ . Y is n bit two's                                                                                                                                                                                                        |    |

|      | complement fractional number, hence $y_1$ has weight equal to $-2^{-1}$ .                                                                                                                                                                                                | 5  |

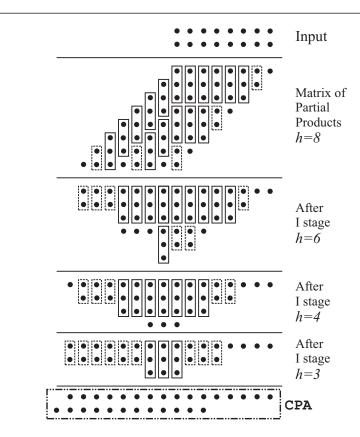

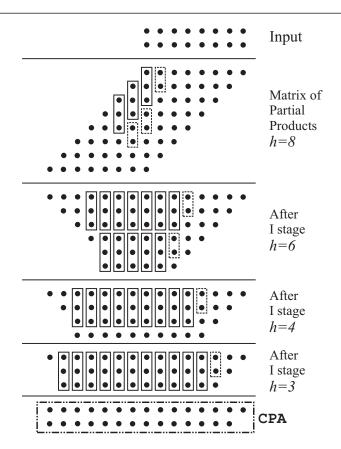

| 1.4  | Wallace reduction for an $8 \times 8$ multiplier. Full circle: Full                                                                                                                                                                                                      |    |

|      | Adder. Dashed circle: Half Adder                                                                                                                                                                                                                                         | 6  |

| 1.5  | Dadda reduction for an $8 \times 8$ multiplier. Full circle: Full Adder.                                                                                                                                                                                                 |    |

|      | Dashed circle: Half Adder.                                                                                                                                                                                                                                               | 7  |

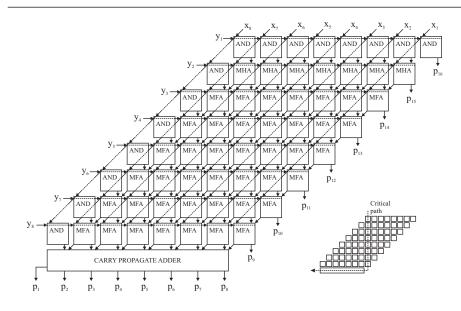

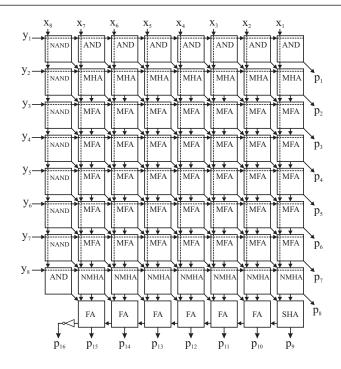

| 1.6  | Unsigned array multiplier, $n = 8$ .                                                                                                                                                                                                                                     | 8  |

| 1.7  | Unsigned array multiplier, $n = 8$ , rectangular shape                                                                                                                                                                                                                   | 9  |

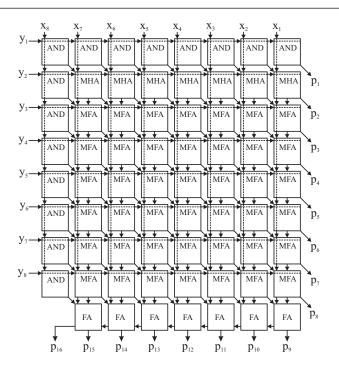

| 1.8  | Signed array multiplier, $n = 8. \ldots \ldots \ldots \ldots$                                                                                                                                                                                                            | 10 |

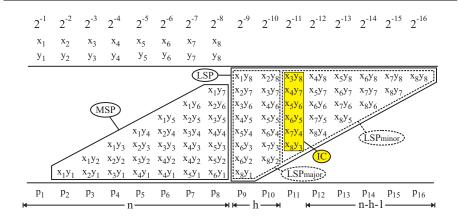

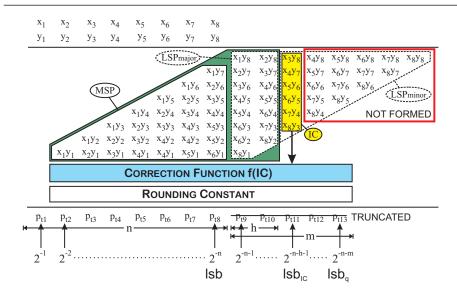

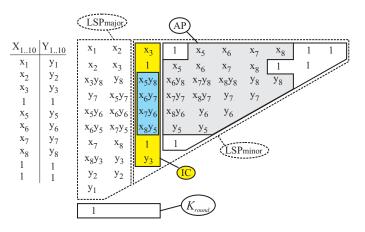

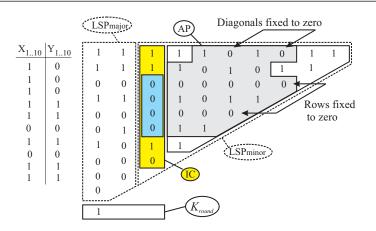

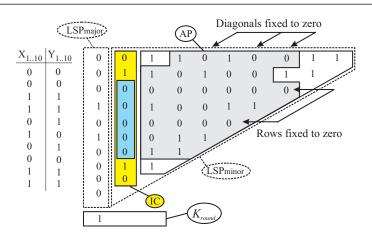

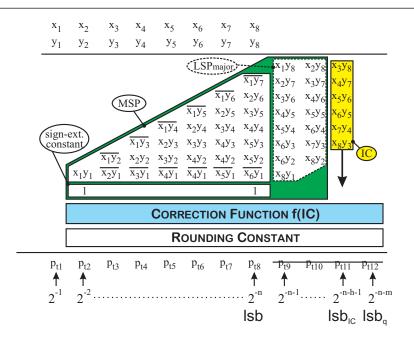

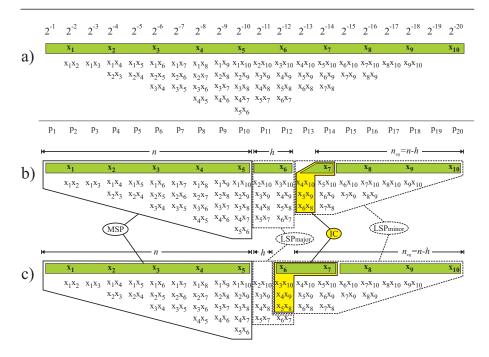

| 1.9  | Subdivision of the matrix of Partial Products, for unsigned<br>multiplier, $n = 8$ . MSP (Most Significant Part) of the PPs Ma-<br>trix is constituted by the first n columns. LSP (Less Significant<br>Part) of the PPs Matrix is constituted by the last n columns. IC |    |

|      | (Input Correction) vector is the $(n + h + 1)^{th}$ column.                                                                                                                                                                                                              | 13 |

| 1.10 | Unsigned array truncated multiplier, $n = 8$ . Dashed lines are                                                                                                                                                                                                          |    |

|      | for the not computed cells.                                                                                                                                                                                                                                              | 14 |

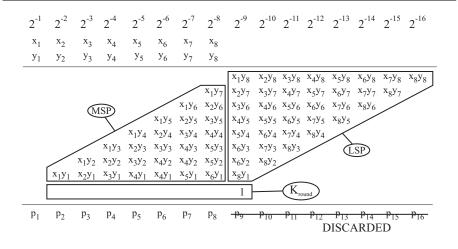

| 1.11 | Full-rounded multiplier, $n = 8$ . $K_{\text{round}}$ is the rounding constant. The <i>n</i> less significant bits of the results are discarded.                                                                                                                         | 15 |

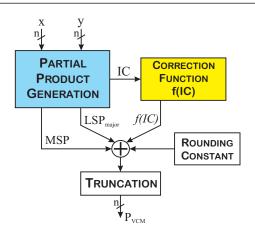

| 1.12 | General scheme of a truncated multiplier. The compensation function $f(IC)$ is estimated from the value of IC. The LSP <sub>minor</sub> is not computed. The result is reported on <i>n</i> bits with a trunca-                                                          |    |

| 0.1  | tion operation.                                                                                                                                                                                                                                                          | 16 |

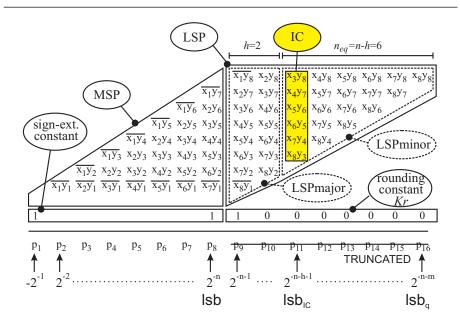

| 2.1  | Partial Products matrix for unsigned truncated multiplier, $n = 8$ and $h = 2$ , with variable-correction scheme.                                                                                                                                                        | 24 |

xi

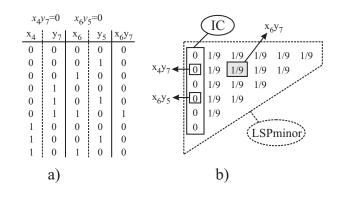

| 2.2  | Computation of $\mu_{\text{LSP}}$ for $n = 8$ unsigned multiplier with IC = 0. a) Computation of the mean value of $x_6y_7$ . b) Mean value of the elements of LSP <sub>minor</sub> .                                                                                                                                                                                           | 32       |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

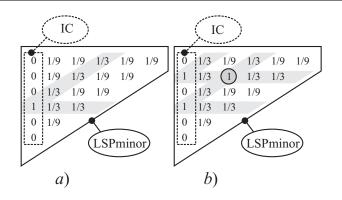

| 2.3  | Mean values of the elements of the LSP when IC is non-zero<br>for a $8 \times 8$ multiplier ( $h = 2$ ). a) Only one element of the IC<br>is equal to 1. b) Two or more elements of the IC are equal to 1.                                                                                                                                                                      | 33       |

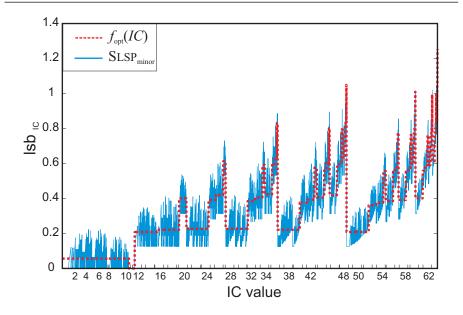

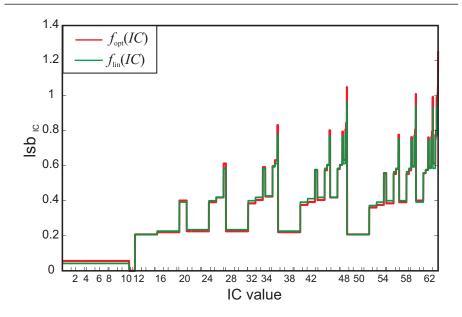

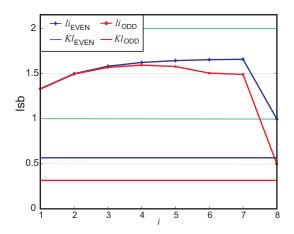

| 2.4  | Coefficients of the optimal error compensation function $f_{opt}(IC)$ for $n = 12, h = 1, \dots, \dots$                                                                                                                                                                                                                                                                         | 34       |

| 2.5  | Comparison between the optimal error compensation function $f_{opt}(IC)$ , red dashed line, and the $S_{LSP_{minor}}$ , green full line, for all the possible input values ( $n = 6, h = 0$ , collected accord-                                                                                                                                                                 |          |

|      | ing to the IC value.                                                                                                                                                                                                                                                                                                                                                            | 35       |

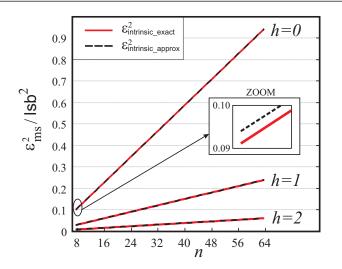

| 2.6  | Comparison between the exact value of $\varepsilon_{\text{intrinsic}}^2$ (red full line)<br>and the approximate value of $\varepsilon_{\text{intrinsic}}^2$ (black dashed line).                                                                                                                                                                                                | 37       |

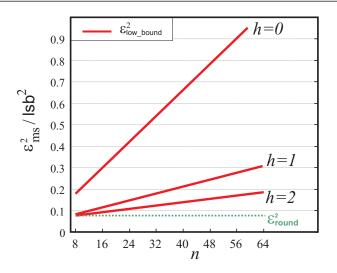

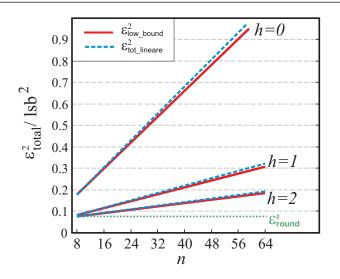

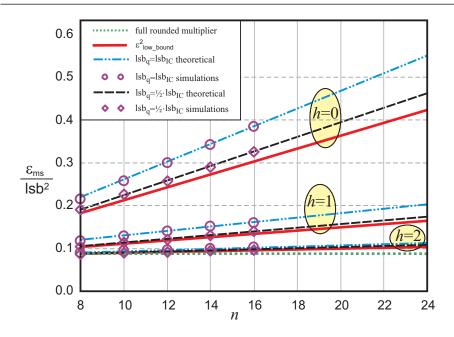

| 2.7  | $\varepsilon_{\text{low_bound}}^2$ values varying <i>n</i> and <i>h</i> , compared with $\varepsilon_{\text{round}}^2$                                                                                                                                                                                                                                                          | 38       |

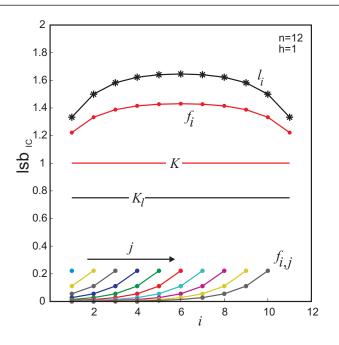

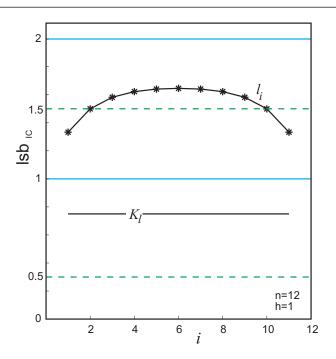

| 2.8  | Comparison between the coefficients of the linear compensa-<br>tion function $f_{lin}(IC)$ , black line with asterisk, and of the opti-<br>mum compensation function $f_{opt}(IC)$ , red line with circle, for                                                                                                                                                                  | 40       |

| 2.9  | n = 12, h = 1.                                                                                                                                                                                                                                                                                                                                                                  | 40       |

| 2.10 | Red full line: $f_{opt}(IC)$ . Green full line: $f_{lin}(IC)$ .<br>Normalized total mean square error as a function of <i>n</i> and <i>h</i> .<br>Red full line: error of optimal (quadratic) compensation func-<br>tion. Blue dashed line: linear compensation function with op-<br>timal coefficient. Green dotted line: mean square error of the<br>full-rounded multiplier. | 41<br>42 |

| 2.11 | Levels of quantization for $l_i$ . When $lsb_q = lsb_{IC}$ , only the blue full lines are admitted. When $lsb_q = 1/2lsb_{IC}$ , also the                                                                                                                                                                                                                                       |          |

| 0.10 | green dashed levels can be used.                                                                                                                                                                                                                                                                                                                                                | 43       |

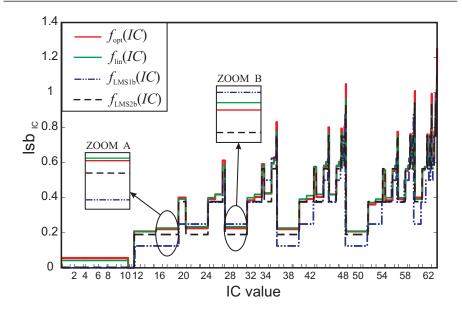

| 2.12 | Comparison between the optimal error compensation function $f_{opt}(IC)$ , red full line, $f_{lin}(IC)$ , green full line, $f_{LMS1b}(IC)$ , blue dashed-dotted line, $f_{LMS2b}(IC)$ , black dashed line                                                                                                                                                                       | 47       |

| 2.13 | Comparison between total mean square errors. Theoretical                                                                                                                                                                                                                                                                                                                        | .,       |

| 2.13 | values are computed by using the formulae described in the                                                                                                                                                                                                                                                                                                                      |          |

|      | chapter.                                                                                                                                                                                                                                                                                                                                                                        | 53       |

| 2.14 | Correlations between the terms of the IC and the AP $(LSP_{minor} - IC)$ . The gray part of the AP is correlated with the blue part of the IC. As example the partial products shown in bold depend on $x_6$ and $y_7$ . If $x_6y_6 = 0$ this means that the bold row or the bold diagonal or both are identically equal to |          |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | zero                                                                                                                                                                                                                                                                                                                        | 55       |

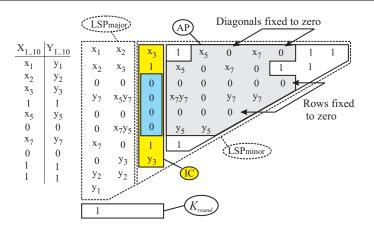

| 2.15 | LSP <sub>minor</sub> partial product matrix for $10 \times 10$ bit multiplier with $h = 2$ . The partial products of the AP that are uncorrelated with the central terms of the IC have been fixed to 1.                                                                                                                    | 56       |

| 2.16 | LSP <sub>minor</sub> partial product matrix for $10 \times 10$ bit multiplier with $h = 2$ . The central terms of the IC are fixed to zero. Each $\gamma_i$ term fixed to zero fixes one row and one diagonal of the AP to zero, alternatively.                                                                             | 57       |

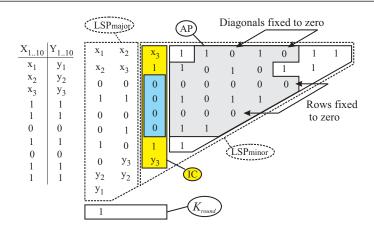

| 2.17 | LSP <sub>minor</sub> partial product matrix for $10 \times 10$ bit multiplier with $h = 2$ . The remaining available bits of the AP shown in                                                                                                                                                                                |          |

| 2.18 | Fig. 2.16 are fixed to 1                                                                                                                                                                                                                                                                                                    | 58       |

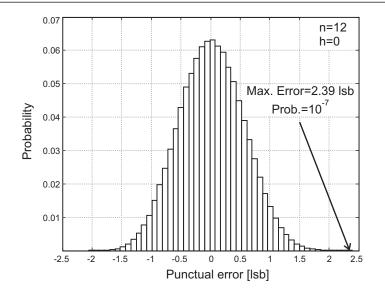

| 2.19 | punctual error                                                                                                                                                                                                                                                                                                              | 59<br>60 |

| 2.20 | Probability distribution of the punctual error for a $n = 12$ bit<br>LMS1b truncated multiplier, $h = 0$ . The maximum absolute<br>error is only present twice on the $2^{24} = 16.8 \times 10^6$ different                                                                                                                 | 00       |

| 2.21 | inputs                                                                                                                                                                                                                                                                                                                      | 63<br>64 |

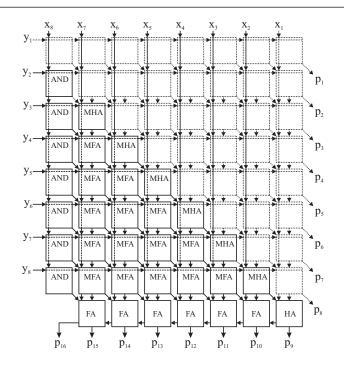

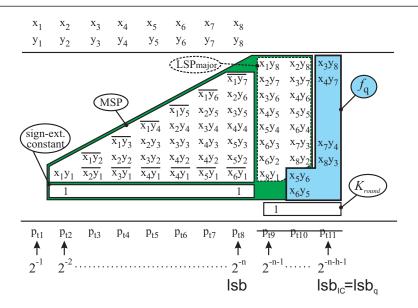

| 3.1  | Signed truncated multiplier with $n = 8$ , $h = 2$ . In this example $lsb_q = \frac{1}{2}lsb_{IC}$                                                                                                                                                                                                                          | 69       |

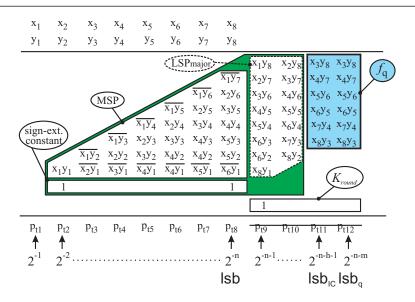

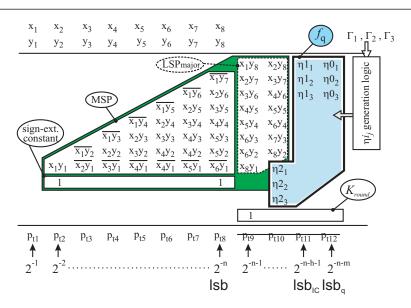

| 3.2  | Implementation of the proposed (signed) LMS1b truncated multiplier, $lsb_q = lsb_{IC}$ , $n = 8$ and $h = 2$ .                                                                                                                                                                                                              | 70       |

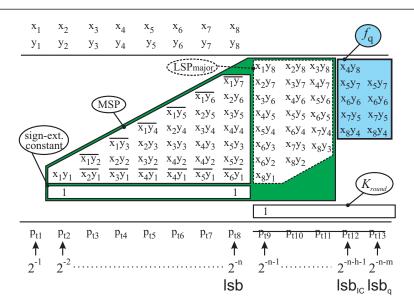

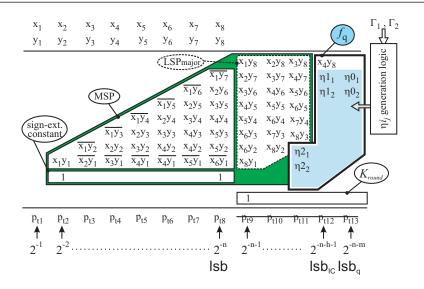

| 3.3  | Straightforward implementation of the proposed signed LMS2b truncated multiplier $lsb_q = \frac{1}{2}lsb_{IC}$ , $n = 8$ and $h =$                                                                                                                                                                                          |          |

| 3.4  | 2. Straightforward implementation of the proposed signed LMS2b truncated multiplier $lsb_q = \frac{1}{2}lsb_{IC}$ , $n = 8$ and $h = 3$ .                                                                                                                                                                                   | 72<br>74 |

|      |                                                                                                                                                                                                                                                                                                                             |          |

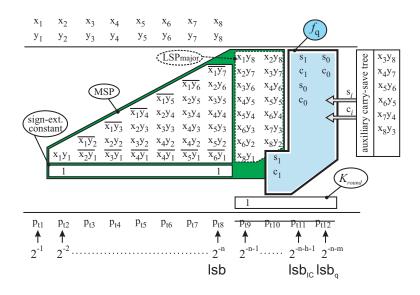

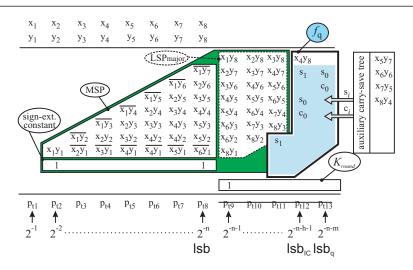

| 3 | 3.5  | Implementation Method 1 (IM1) of the proposed (signed)<br>LMS2b truncated multiplier $lsb_q = \frac{1}{2}lsb_{IC}$ , $n = 8, h = 2$                                                                                                        | 76 |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3 | 3.6  | Implementation Method 1 (IM1) of the proposed (signed)<br>LMS2b truncated multiplier $lsb_q = \frac{1}{2}lsb_{IC}$ , $n = 8, h = 3$                                                                                                        | 70 |

|   | 3.7  | Implementation Method 2 (IM2) of the proposed (signed)<br>LMS2b truncated multiplier $lsb_q = \frac{1}{2}lsb_{IC}$ , $n = 8, h = 2$                                                                                                        | 77 |

|   | 3.8  | Implementation Method 1 (IM1) of the proposed (signed) LMS2b truncated multiplier $lsb_q = \frac{1}{2}lsb_{IC}$ , $n = 8, h = 3$                                                                                                           | 78 |

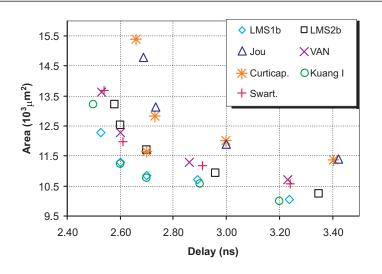

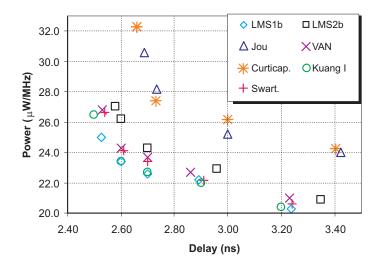

| 3 | 3.9  | Signed Multiplier performances for $n = 16$ and $h = 1$ by varying the delay constrain imposed during circuit synthesis $(0.18\mu m \text{ technology})$ .                                                                                 | 87 |

|   | 3.10 |                                                                                                                                                                                                                                            | 87 |

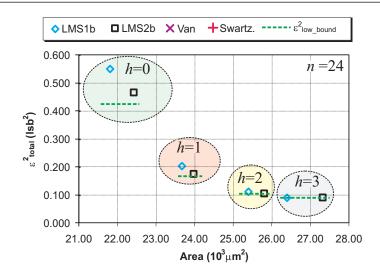

| 3 | 3.11 | Trade off between Area Occupation and Error (mean square total error - $\varepsilon_{\text{total}}^2$ ) for different Signed Truncated Multipliers, $n = 8$ . The mean square error is obtained through simulation.                        | 89 |

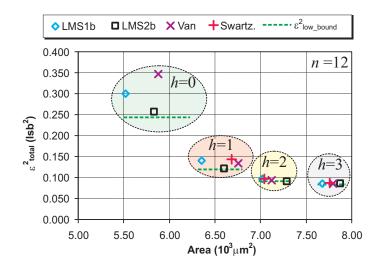

|   | 3.12 | Trade off between Area Occupation and Error (mean square total error - $\varepsilon_{\text{total}}^2$ ) for different Signed Truncated Multipliers, $n = 12$ . The mean square error is obtained through simulation.                       | 89 |

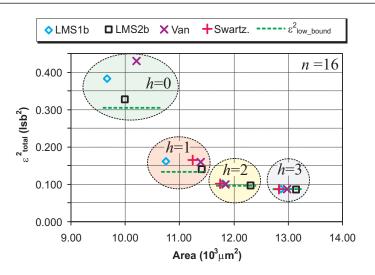

| 3 | 3.13 | Trade off between Area Occupation and Error (mean square total error - $\varepsilon_{\text{total}}^2$ ) for different Signed Truncated Multipliers, $n = 16$ . The mean square error is obtained through simulation.                       | 90 |

| 3 | 3.14 | Trade off between Area Occupation and Error (mean square total error - $\varepsilon_{\text{total}}^2$ ) for different Signed Truncated Multipliers, $n = 24$ . The mean square error is obtained by the theoretical                        |    |

| 3 | 3.15 | formulas of Ch. 2.<br>Trade off between Area Occupation and Error (mean square total error - $\varepsilon_{\text{total}}^2$ ) for different Signed Truncated Multipliers.<br>For $n = 16$ the mean square error is simulated. For $n = 24$ | 91 |

|   |      | the mean square error is obtained by the theoretical formulas of Ch. 2.                                                                                                                                                                    | 92 |

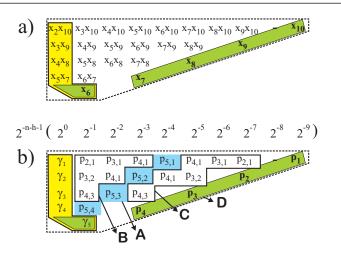

| 4.1  | Partial Products Matrix of unsigned squarer, $n$ even $(n = 8)$ .<br>The bold elements form the antidiagonal. a) Full original matrix of the squarer. b) Reduced matrix after applying (4.3).                                                                                                                                                                                                                                                                   | 94  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

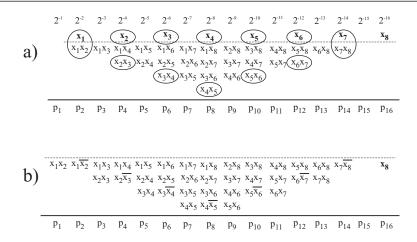

| 4.2  | Partial Products Matrix of unsigned squarer during the folding process, $n$ even ( $n = 8$ ). a) Partial Product Matrix to which (4.4) can be applied; in each column the circled elements will                                                                                                                                                                                                                                                                 |     |

|      | be grouped. b) Final folded matrix.                                                                                                                                                                                                                                                                                                                                                                                                                             | 95  |

| 4.3  | Final folded matrix for unsigned squarer, $n \text{ odd } (n = 9)$ .                                                                                                                                                                                                                                                                                                                                                                                            | 96  |

| 4.4  | Partial Products Matrix of signed squarer during the folding process, $n \operatorname{even}(n = 8)$ . a) Partial Product Matrix to which (4.8) can be applied; in each column the circled elements will be grouped. b) Final folded matrix.                                                                                                                                                                                                                    | 97  |

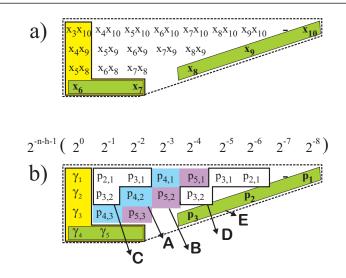

| 4.5  | Partial Products Matrix of unsigned squarer, $(n = 10)$ . a) Par-<br>tial Product Matrix before the last folding operation. In green<br>the matrix elements formed by a single bit. b) Subdivision<br>of the partial product matric in MSP, LSP <sub>major</sub> and LSP <sub>minor</sub><br>when $n_{eq}$ is even $(n = 10, h = 2)$ . c) Subdivision of the par-<br>tial product matric in MSP, LSP <sub>major</sub> and LSP <sub>minor</sub> when $n_{eq}$ is | 21  |

|      | odd $(n = 10, h = 1)$                                                                                                                                                                                                                                                                                                                                                                                                                                           | 99  |

| 4.6  | LSP <sub>minor</sub> of unsigned squarer, $(n = 10, h = 0)$ . a) LSP <sub>minor</sub> . In yellow, elements of IC vector, in green elements of the matrix composed by a single bit. b) LSP <sub>minor</sub> in which the dependence by the elements of IC is shown.                                                                                                                                                                                             | 101 |

| 4.7  | LSP <sub>minor</sub> of unsigned squarer, $(n = 10, h = 1)$ . a) LSP <sub>minor</sub> . In yellow, elements of IC vector, in green elements of the matrix formed by a single bit. b) LSP <sub>minor</sub> in which the dependence                                                                                                                                                                                                                               | 104 |

| 4.8  | by the elements of IC is shown                                                                                                                                                                                                                                                                                                                                                                                                                                  | 104 |

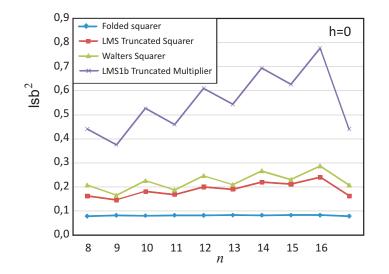

| 4.9  | Mean square error obtained using a full-width folded squarer with final rounding (blue line§), LMS truncated squarer (red line), Walters [33] squarer (green line) and LMS1b truncated multiplier (violet line), varying $n$ for $h = 0$ .                                                                                                                                                                                                                      | 100 |

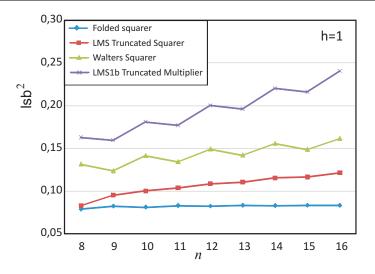

| 4.10 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 107 |

|      | multiplier (violet line), varying $n$ for $h = 1, \ldots, \ldots$                                                                                                                                                                                                                                                                                                                                                                                               | 110 |

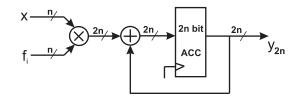

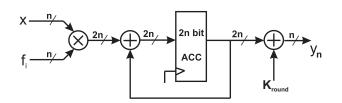

| 5.1 | MAC with $n$ bits inputs and $2n$ bits output. The error provided by this configuration is zero.                                                                                                                                                                                                                                    | 114 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.2 | MAC with $n$ bits inputs and $n$ bits output. It uses a full-width multiplier and the output is rounded to $n$ bits summing a rounding constant to the $2n$ bits output. In this configuration a round-                                                                                                                             |     |

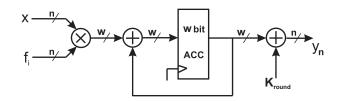

| 5.3 | ing error is present.<br>MAC with <i>n</i> bits inputs, <i>w</i> bits output. It uses a truncated mul-<br>tiplier with <i>n</i> bits inputs and $w < 2n$ bit output. This config-<br>uration presents the rounding error as in Fig. 5.2 and the error                                                                               | 115 |

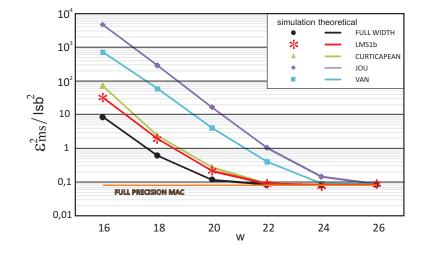

| 5.4 | introduced by the truncated multiplier                                                                                                                                                                                                                                                                                              | 115 |

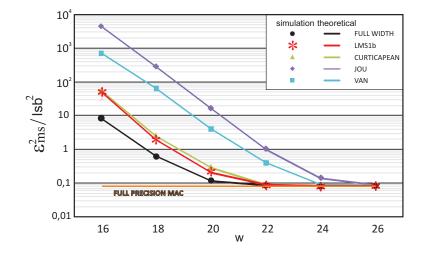

|     | precision MAC with a final rounding.                                                                                                                                                                                                                                                                                                | 120 |

| 5.5 | Mean square error of FIR implemented with different trun-<br>cated multipliers varying the number of outputs bits $w = n+h$<br>(n = 16, h = 0, 2, 4, 6, 8, 10). The applied input is a sinusoid.<br>The orange line is the mean square error of the full precision<br>MAC with a final rounding.                                    | 123 |

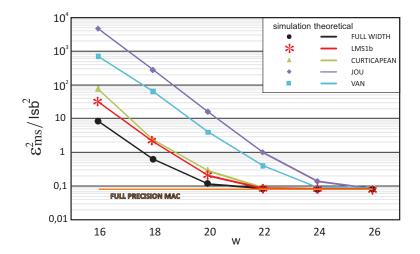

| 5.6 | Mean square error of FIR implemented with different trun-<br>cated multipliers varying the number of outputs bits $w = n+h$<br>(n = 16, h = 0, 2, 4, 6, 8, 10). The applied input has a gaus-<br>sian probability distribution (rised cosine frequency spectrum).<br>The orange line is the mean square error of the full precision |     |

| 5.7 | MAC with a final rounding                                                                                                                                                                                                                                                                                                           | 124 |

|     | square error of the full precision MAC with a final rounding.                                                                                                                                                                                                                                                                       | 125 |

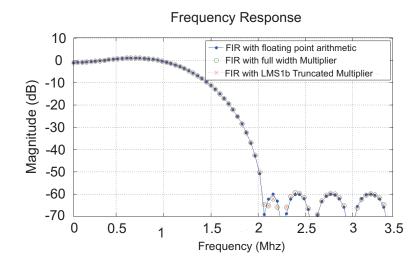

| 5.8 | Frequency Response of the FIR filter implemented using the architecture of Fig. 5.2 and Fig. 5.3 with $w = n = 20$ , $h = 2$ .                                                                                                                                                                                                      | 126 |

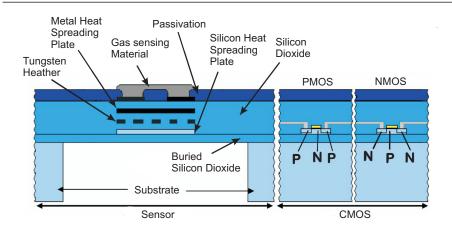

| 6.1 | Tungsten SOI chip: gas sensor and integrated CMOS circuitry.                                                                                                                                                                                                                                                                        | 131 |

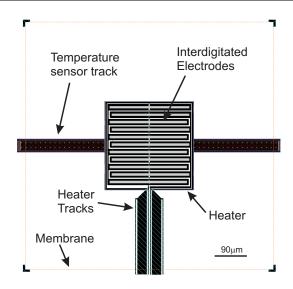

| 6.2 | Layout of the microhotplate device.                                                                                                                                                                                                                                                                                                 | 132 |

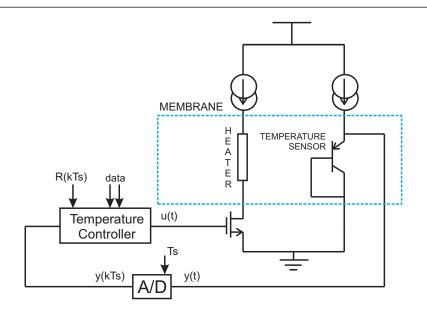

| 6.3 | Schematic of the circuit composed by the gas sensor (mem-         |     |

|-----|-------------------------------------------------------------------|-----|

|     | brane), cascode current mirror to drive heater and temperature    |     |

|     | sensor, A/D converter and a temperature controller. $y(t)$ is the |     |

|     | measured temperature, $R(kT_S)$ the desired temperature, $u(t)$   |     |

|     | is the control variable and $T_S$ is the sampling period          | 133 |

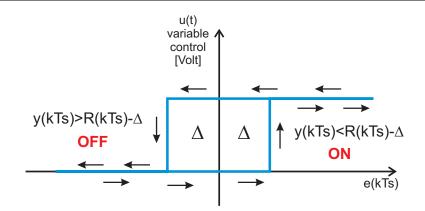

| 6.4 | On/Off controller.                                                | 134 |

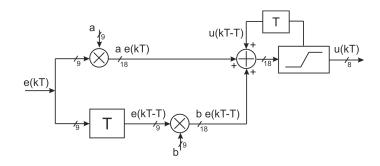

| 6.5 | Digital implementation of PI algorithm.                           | 136 |

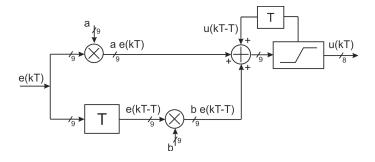

| 6.6 | Digital implementation of an optimized PI algorithm               | 136 |

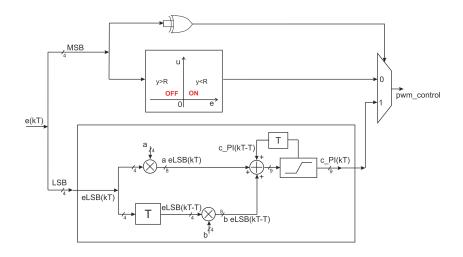

| 6.7 | Mixed controller.                                                 | 137 |

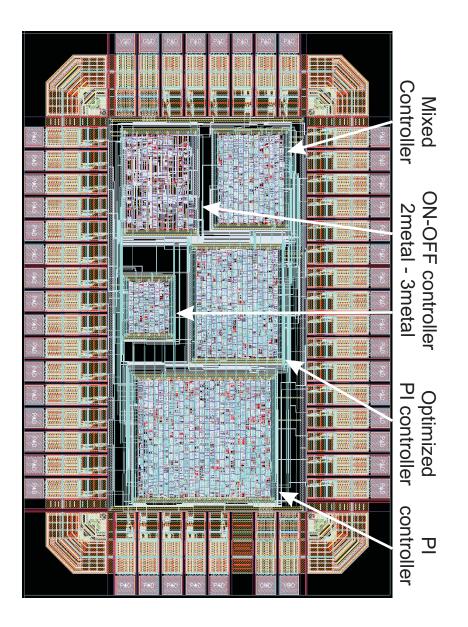

| 6.8 | Digital chip with controllers                                     | 140 |

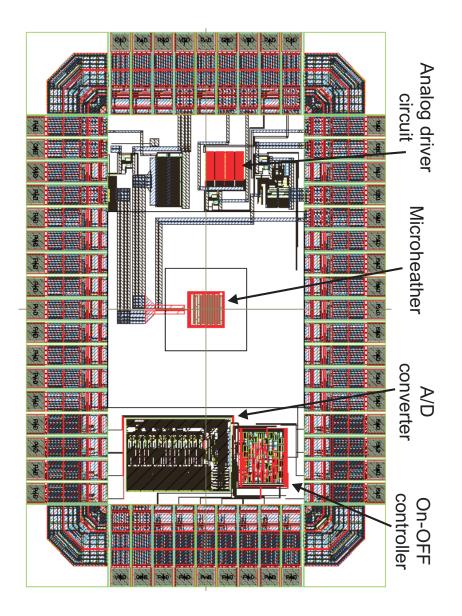

| 6.9 | Mixed signal chip.                                                | 141 |

|     |                                                                   |     |

# **List of Tables**

| 3.1 | Optimal quantized coefficient (Ch. 2). The $(\text{REM}(x, y))$ symbol indicates the remainder of the integer division $x/y$                                                                                              | 68  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Comparison of the performance of proposed truncated (signed) multipliers. Circuits are implemented in TSMC $0.18\mu m$ technology.                                                                                        | 71  |

| 3.3 | Truth table describing the Boolean relationship between $(\gamma'_{2i-1}, \gamma'_{2i})$ and $(\eta 2_i, \eta 1_i, \eta 0_i)$ .                                                                                           | 75  |

| 3.4 | Previously proposed truncated multipliers considered in the comparison.                                                                                                                                                   | 80  |

| 3.5 | Theoretical and simulated mean square errors of proposed and previously proposed truncated multiplier (S=signed multiplier; U=unsigned multiplier), $n = 8, 10, 12$ and $h = 0, 1, 2, 3$ .                                | 82  |

| 3.6 | Theoretical and simulated mean square errors of proposed and previously proposed truncated multiplier (S=signed multiplier; U=unsigned multiplier) $n = 14, 16, 32, 64$ and $h = 0, 1, 2, 3$ .                            | 83  |

| 3.7 | Theoretical and simulated maximum absolute error<br>of proposed and previously proposed truncated mul-<br>tipliers (S=signed multiplier; U=unsigned multiplier),<br>n = 10, 12, 14, 20, 24, 32, 64 and $h = 0, 1, 2, 3$ . | 85  |

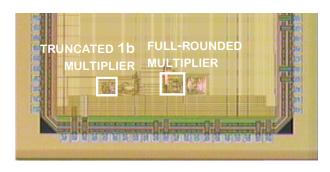

| 3.8 | Experimental performance of the signed 16 bit multipliers re-<br>alized in the test chip shown in Fig. 3.15                                                                                                               | 91  |

| 4.1 | Comparison between squarer, $h = 0$                                                                                                                                                                                       | 111 |

| 5.1 | Characteristic of the considered FIR Filters.                                                                                                                                                                             | 118 |

xix

| 5.2 | Performances of the FIR Filters implemented using various<br>Truncated Multipliers, with $n = 16$ . The results have been<br>obtained with an uniform distributed signal. Bold numbers in-<br>dicate the best performing circuit for each $w(h)$ value. |     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     |                                                                                                                                                                                                                                                         | 121 |

| 5.3 | Performances of the Low-Pass Filters implemented using var-                                                                                                                                                                                             |     |

|     | ious Fixed-width Multipliers, for $n = 12$ . The results have                                                                                                                                                                                           |     |

|     | been obtained with a uniform distributed signal. Bold num-                                                                                                                                                                                              |     |

|     | bers indicate the best performing circuit for each $m(h)$ value.                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                         | 122 |

| 5.4 | Performances of the Low-Pass Filters implemented using var-                                                                                                                                                                                             |     |

|     | ious Fixed-width Multipliers, for $n = 20$ . The results have                                                                                                                                                                                           |     |

|     | been obtained with a uniform distributed signal. Bold num-                                                                                                                                                                                              |     |

|     | bers indicate the best performing circuit for each $m(h)$ value.                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                         | 127 |

| 6.1 | Comparison Between Controllers.                                                                                                                                                                                                                         | 139 |

## Notations

| X                    | Multiplicand $(x_1x_2\ldots x_{n-1}x_n)$                                                                                                             |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Y                    | Multiplier $(y_1y_2\ldots y_{n-1}y_n)$                                                                                                               |

| P                    | Product Full-width Multiplier $(p_1p_2 \dots p_{2n-1}p_{2n})$                                                                                        |

| $P_t$                | Product Truncated Multiplier $(p_{t,1}p_{t,2} \dots p_{t,n-1}p_{t,n})$                                                                               |

| V                    | Boolean operator OR                                                                                                                                  |

| $\wedge$             | Boolean operator AND                                                                                                                                 |

| $\oplus$             | Boolean operator XOR                                                                                                                                 |

| MOD                  | n 1 most significant columns of the Portial Products matrix                                                                                          |

| MSP                  | <i>n</i> -1 most significant columns of the Partial Products matrix                                                                                  |

| MSP<br>LSP           | <i>n</i> less significant columns of the Partial Products matrix                                                                                     |

|                      | -                                                                                                                                                    |

| LSP                  | <i>n</i> less significant columns of the Partial Products matrix                                                                                     |

| LSP<br>IC            | <i>n</i> less significant columns of the Partial Products matrix<br>Input Correction vector $((n + h + 1)^{th}$ column)                              |

| LSP<br>IC $\gamma_i$ | <i>n</i> less significant columns of the Partial Products matrix<br>Input Correction vector $((n + h + 1)^{th}$ column)<br>Generic element of the IC |

xxi

| $lsb_{IC}$                         | Weight of the IC vector $[2^{-n-h-1}]$                                                    |

|------------------------------------|-------------------------------------------------------------------------------------------|

| $lsb_q$                            | Weight of the less-significant bit of $f(IC)$ [2 <sup>-n-m</sup> ]                        |

| $n_{eq} = n - h$                   | Number of columns in LSP <sub>minor</sub>                                                 |

| Θ                                  | Set of all possible values of the vector IC                                               |

| $\Omega(A)$                        | Subset of all couples $(x, y)$ which give $IC = A$                                        |

| $\mu_{\text{LSP}}(A)$              | Mean value of $LSP_{minor}$ in $\Omega(A)$                                                |

| $\sigma^2_{\rm LSP}(A)$            | Variance of $LSP_{minor}$ in $\Omega(A)$                                                  |

| $e_{\rm round}$                    | Rounding error                                                                            |

| $\mu_{\mathrm{round}}$             | Mean value of the rounding error                                                          |

| $\varepsilon_{\mathrm{round}}^2$   | Variance of the rounding error                                                            |

| $e_{\rm total}$                    | Error of the truncated multiplier $[e_{\text{total}} = P - P_t]$                          |

| $\mu_{ m total}$                   | Mean value of $e_{\text{total}}$                                                          |

| $\varepsilon_{\rm total}^2$        | Mean square error of $e_{\rm total}$                                                      |

| $\sigma_{\rm total}^2$             | Variance of $e_{\text{total}}$                                                            |

| $e_{\mathrm{trunc}}$               | Truncation error                                                                          |

| $\mu_{ m trunc}$                   | Mean value of $e_{\rm trunc}$                                                             |

| $\sigma^2_{ m trunc}$              | Variance of $e_{\rm trunc}$                                                               |

| $e_{\mathrm{erasing}}$             | Error related to $f(IC)$ , $[e_{\text{erasing}} = f(IC) - S_{\text{LSP}_{\text{minor}}}]$ |

| $\mu_{\mathrm{erasing}}$           | Mean value of $e_{\text{erasing}}$                                                        |

| $\varepsilon_{\mathrm{erasing}}^2$ | Mean square error of $e_{\text{erasing}}$                                                 |

#### Notations

| $\sigma^2_{\rm erasing}$         | Variance of $e_{\text{erasing}}$               |

|----------------------------------|------------------------------------------------|

| $\varepsilon_{ m intrinsic}^2$   | Intrinsic Error, independent by $f(IC)$        |

| $e_{\rm comp}$                   | Compensation error $(f(IC) - \mu_{LSP}(IC))$   |

| $\mu_{\rm comp}$                 | Mean value of $e_{\rm comp}$                   |

| $\varepsilon_{\rm comp}^2$       | Mean square value of $e_{\rm comp}$            |

| $\sigma^2_{ m comp}$             | Variance of $e_{\rm comp}$                     |

| $f_{opt}(IC)$                    | Optimal Compensation Function                  |

| $\varepsilon^2_{\rm low\_bound}$ | Lower error bound of truncated multiplier      |

| $f_{lin}(IC)$                    | Linear Correction Function                     |

| $\mu_{ m lin}$                   | Mean value of $(f_{lin}(IC) - \mu_{LSP}(IC))$  |

| $\sigma_{ m lin}^2$              | Variance of $(f_{lin}(IC) - \mu_{LSP}(IC))$    |

| $f_q(IC)$                        | Quantized-Coefficient correction function      |

| $\Delta f_{lin}(\mathrm{IC})$    | Difference between $f_q(IC)$ and $f_{lin}(IC)$ |

| $\mu_{\mathrm{quant}}$           | Mean value of $\Delta f_{lin}(\text{IC})$      |

| $\sigma_{ m q}^2$                | Variance of $\Delta f_{lin}(IC)$               |

| $\varepsilon_{\rm max}$          | Maximum absolute error                         |

| $\varepsilon_{FIR}$              | Error of the FIR filter with truncated MAC     |

| $\mu_{ m FIR}$                   | Mean error of $\varepsilon_{FIR}$              |

|                                  | 1 110                                          |

| $\varepsilon_{ m FIR}^2$         | Mean square error of $\varepsilon_{FIR}$       |

### Introduction

I not the wireless multimedia word, DSP systems are ubiquitous. DSP algorithms are computationally intensive and test the limits of battery life in portable device such as cell phones, hearing aids, MP3 players, digital video recorders and so on. Multiplication and squaring are the main operation in many signal processing algorithms (filtering, convolution, FFT, DCT, euclidean distance etc.), hence efficient parallel multipliers are desirable.

A full-width digital  $n \times n$  bits multiplier computes the 2n bits output as a weighted sum of partial products. A multiplier with the output represented on n bits output is useful, as example, in DSP datapaths which saves the output in the same n bits registers of the input. Note that the truncated multipliers are useful not only for DSP but also for digital, computational intensive, ASICs where the bit-widths at the output of the arithmetic blocks are chosen on the basis of system-related accuracy issues. Hence 2n bits of precision at the multiplier output are very often more than required.

A truncated multiplier is an  $n \times n$  multiplier with *n* bits output. Since in a truncated multiplier the *n* less-significant bits of the full-width product are discarded, some of the partial products are removed and replaced by a suitable compensation function, to trade-off accuracy with hardware cost. Several techniques have been proposed in the Literature following this basic idea. The difference between the various circuits is in the choice and the implementation of the compensation circuit.

The correction techniques proposed in the Literature are obtained through exhaustive search. This means that the results are only available for small n values and that the proposed approach are not extendable to greater bit widths. Furthermore the analytical characterization of the error is not possible.

In this dissertation an innovative solution for the design and characterization of truncated multipliers is presented.

The proposed circuits are based on the analytical calculation of the error of the truncated multiplier. This approach allows to have the description of a mul-

XXV

tiplier characterized by a minimum mean square error which gives a fast and low power VLSI implementation. Furthermore the analytical approach yields to a closed form expression of the mean square error and maximum absolute error for the proposed truncated multipliers. In this way the a priori knowledge of the output error is available. The errors are known for every bit width of the multiplier and it is also possible to decide, for a given bit width, which correction circuit has to be used in order to obtain a certain error. This analytical relation between the error and the parameters of hardware implementation is extremely important for the digital designer, since now it is possible to select the suitable implementation as a function of the desired accuracy.

Proposed truncated multipliers overcome the previously proposed truncated multipliers since provide lower error, lower power dissipation, lower area occupation and also provide higher working frequency. The circuits are also easily implemented and allow an automatic HDL description as a function of bit width and desired error. The complete description of the errors for the truncated multipliers allows the use of these circuits as building blocks for more complex systems. It will be shown how the proposed multiplier can be used to design low area occupation FIR filters and an efficient PI temperature controller.

#### **Dissertation outline**

The outline of the thesis is the following:

**Chapter 1** summarizes the state of art full-width and truncated multipliers. The two existent methods for the implementation of the truncated multipliers, constant correction and variable correction, are described and analyzed.

**Chapter 2** describes the analytical characterization of the proposed truncated multiplier. First the optimal compensation function  $f_{opt}(IC)$ , that minimizes the mean square error of the truncated multiplier, is analytically calculated and characterized. Since  $f_{opt}(IC)$  is a quadratic form, with the help of the developed theory, the derivation of a sub-optimal compensation function,  $f_{lin}(IC)$  (first grade approximation) is described. In the Chapter it is shown that the linear compensation function yields error performances very similar to the one achievable with  $f_{opt}(IC)$  and has the additional advantage of an

**Chapter 3** deals with the practical implementation of the quantized linear compensation function proposed in the Chapter 2. The performances of the new truncated multipliers are extensively compared with previously proposed circuits in terms of maximum absolute error, mean square error, hardware performances.

**Chapter 4** extends the methodology described in Chapter 2 for the truncated multipliers to the truncated squarer. After a brief introduction about the state of the art squarer, the optimal compensation function, its linear approximation and quantized version are shown. Finally the results of the simulations and hardware implementation are presented and a comparison with the existent techniques is highlighted.

**Chapter 5** is focused on a typical DSP application, FIR filter. In this chapter the analysis of the impact of the use of truncated multiplier in FIR filter is presented. The parameters of the truncated multipliers that are more significant for the optimization of a digital filter are defined. In order to evaluate the performances of the proposed LMS multiplier in this application, a comparison with the state of art multiplier is carried out in terms of error, power, frequency and area occupation.

**Chapter 6** describes another application where is possible to use the truncated multipliers: temperature control. In this chapter the implementation of a PI temperature controller for a gas sensor using the LMS truncated multiplier is described. This implementation is compared with the traditional PI controller, the OnOff controller, the mixed controller. Finally two chips are presented.

#### **Publications**

• V. Garofalo, E. Napoli, A.G.M. Strollo, "Code compression for ARM7 embedded systems". European Conference on Circuit Theory and De-

sign. 26-30 August 2007

- E. Della Sala, E. Sciagura, D. De Caro, A. Caravella, P. Longobardi, P. Zicari, V. Garofalo, G. Chapuano, P. Corsonello, E. Napoli, A.G.M. Strollo, "High Rate Data Down Link." proc. of 18th ESA Symposium for Sounding Rockets and Balloons, June, 2007

- V. Garofalo, N. Petra, D. De Caro, A.G.M. Strollo, E. Napoli, "Low error Truncated Multipliers for DSP applications", IEEE International Conference on Electronics, Circuits, and Systems 1-3 September 2008

- A.G.M. Strollo, D. De Caro, N. Petra, E. Napoli, V. Garofalo, "Constrained Piecewise Polinomial Approximation for Hardware Implementation of Elementary Functions", IEEE International Conference on Electronics, Circuits, and Systems 1-3 Sept. 2008

- V. Garofalo, "Fixed-width multipliers for the implementation of efficient digital FIR filters", Microelectronics Journal, vol. 39; p. 1491-1498, ISSN: 0959-8324 (doi:10.1016/j.physletb.2003.10.071)

- N. Petra, D. De Caro, V. Garofalo, E. Napoli, A.G.M. Strollo, "Truncated Binary Multipliers with Optimal Compensation Function", accepted to IEEE Transaction on Circuits and Systems I

- V. Garofalo, P.K. Guha, S.Z. Ali, S. Santra, E. Napoli, F. Udrea "Mixed Signal Temperature Control Circuit for On-Chip CMOS Gas Sensor", International Semiconductor Conference 2009, October 2009, Sinaia, Romania

- S.Z. Ali, S. Santra, P.K. Guha, I. Haneef, V. Garofalo, C. Schwandt, J.A. Covington, R.V. Kumar, J.W. Gardner, W.I. Milne, F. Udrea, "Nanowire Hydrogen Gas Sensor Employing CMOS Micro-Hotplate", IEEE SEN-SORS 2009 Conference, 25-28 October 2009, New Zealand

- V. Garofalo, N. Petra, E. Napoli, "Analytical calculation of the maximum error for a family of truncated multipliers providing minimum mean square error", submitted to IEEE Transaction on Computers

- V. Garofalo, M. Coppola, D. De Caro, E. Napoli, N. Petra, A.G.M. Strollo, "A Novel Truncated Squarer with Linear Compensation Function", submitted to IEEE Internat Symposium on Circuits and Systems (ISCAS) 2010

- N. Petra, D. De Caro, A. G. M. Strollo, V. Garofalo, E. Napoli, M. Coppola, P. Todisco, "Fixed-Width CSD Multipliers With Minimum Mean Square Error", submitted to IEEE ISCAS 2010

- A.G.M. Strollo, D. De Caro, N. Petra, E. Napoli, M. Coppola, V. Garofalo, "Non Uniform Piecewise-Linear Approximation For High Performance Direct Digital Frequency Synthesizers", submitted to IEEE IS-CAS 2010

- D. De Caro, M. Coppola, N. Petra, E. Napoli, A.G.M. Strollo, V. Garofalo, "High Speed Differential Resistor Ladder for A/D Converters", submitted to IEEE ISCAS 2010

# Chapter 1 Binary Multiplication

M ultiplication is one of the most area consuming arithmetic operations in high-performance circuits. As a consequence many research works deal with low-power design of high-speed multipliers. Multiplication involves two basic operations, the generation of the partial products and their sum, performed using two kinds of multiplication algorithms, serial and parallel. Serial multiplication algorithms use sequential circuits with feedbacks: inner products are sequentially produced and computed. Parallel multiplication algorithms often use combinational circuits and do not contain feedback structures.

A full-width digital  $n \times n$  multiplier computes the 2n bits output as a weighted sum of partial products. When an application requires a multiplication output with n bits, it is substituted by a truncated multiplier, which is a  $n \times n$  multiplier with n bits output. After a short description of the generation of partial product done in Sec. 1.1, Sec. 1.2 describes the common techniques used in order to implement full-width multipliers. Finally Sec. 1.3 summarizes the state of art for truncated multipliers.

#### **1.1 Partial-Product Generation**

The following notation is used in our discussion of multiplication algorithm:

| X     | Multiplicand                                 | $(x_1x_2\ldots x_{n-1}x_n)$               |

|-------|----------------------------------------------|-------------------------------------------|

| Y     | Multiplier                                   | $(y_1y_2\ldots y_{n-1}y_n)$               |

| P     | Product Full-width Multiplier $(X \cdot Y)$  | $(p_1p_2\ldots p_{2n-1}p_{2n})$           |

| $P_t$ | Product Truncated Multiplier $(X \cdot Y)_t$ | $(p_{t,1}p_{t,2}\ldots p_{t,n-1}p_{t,n})$ |

| WEIGHT       | 2 <sup>-1</sup> | 2 <sup>-2</sup>                    | 2 <sup>-3</sup> | 2 <sup>-4</sup> | 2 <sup>-5</sup> | 2-6            | 2-7            | 2-8                           | 2 <sup>-9</sup>                    | 2 <sup>-10</sup>              | 2 <sup>-11</sup>              | 2 <sup>-12</sup>              | 2 <sup>-13</sup>              | $2^{-14}$                     | 2 <sup>-15</sup>              | 2 <sup>-16</sup>              |

|--------------|-----------------|------------------------------------|-----------------|-----------------|-----------------|----------------|----------------|-------------------------------|------------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|

| MULTIPLICAND | $\mathbf{x}_1$  | $\mathbf{x}_2$                     | x <sub>3</sub>  | $\mathbf{x}_4$  | $\mathbf{x}_5$  | x <sub>6</sub> | $\mathbf{x}_7$ | $\mathbf{x}_8$                |                                    |                               |                               |                               |                               |                               |                               |                               |

| MULTIPLIER   | $\mathbf{y}_1$  | $y_2$                              | $y_3$           | y <sub>4</sub>  | У5              | y <sub>6</sub> | У7             | $y_8$                         |                                    |                               |                               |                               |                               |                               |                               |                               |

|              |                 |                                    |                 |                 |                 |                |                |                               | x <sub>1</sub> y <sub>8</sub>      | x <sub>2</sub> y <sub>8</sub> | x <sub>3</sub> y <sub>8</sub> | x <sub>4</sub> y <sub>8</sub> | x <sub>5</sub> y <sub>8</sub> | x <sub>6</sub> y <sub>8</sub> | x <sub>7</sub> y <sub>8</sub> | x <sub>8</sub> y <sub>8</sub> |

| PARTIAL      |                 |                                    |                 |                 |                 |                |                | $x_1y_7$                      | $x_2y_7$                           | x <sub>3</sub> y <sub>7</sub> | $x_4y_7$                      | $x_5y_7$                      | x <sub>6</sub> y <sub>7</sub> | $x_7y_7$                      | $x_8y_7$                      |                               |

| PRODUCTS     |                 |                                    |                 |                 |                 |                | $x_1y_6$       | x <sub>2</sub> y <sub>6</sub> | x <sub>3</sub> y <sub>6</sub>      | x <sub>4</sub> y <sub>6</sub> | x <sub>5</sub> y <sub>6</sub> | x <sub>6</sub> y <sub>6</sub> | x <sub>7</sub> y <sub>6</sub> | x <sub>8</sub> y <sub>6</sub> |                               |                               |

|              |                 |                                    |                 |                 |                 | $x_1y_5$       | $x_2y_5$       | x <sub>3</sub> y <sub>5</sub> | x <sub>4</sub> y <sub>5</sub>      | x <sub>5</sub> y <sub>5</sub> | x <sub>6</sub> y <sub>5</sub> | x <sub>7</sub> y <sub>5</sub> | $x_8y_5$                      |                               |                               |                               |

|              |                 |                                    |                 |                 | $x_1y_4$        | $x_2y_4$       | $x_3y_4$       | $x_4y_4$                      | x <sub>5</sub> y <sub>4</sub>      | x <sub>6</sub> y <sub>4</sub> | $x_7y_4$                      | $x_8y_4$                      |                               |                               |                               |                               |

|              |                 |                                    |                 | $x_1y_3$        | $x_2y_3$        | $x_3y_3$       | $x_4y_3$       | $x_5y_3$                      | x <sub>6</sub> y <sub>3</sub>      | $x_7y_3$                      | $x_8y_3$                      |                               |                               |                               |                               |                               |

|              |                 |                                    | $x_1y_2$        | $x_2y_2$        | $x_3y_2$        | $x_4y_2$       | $x_4y_2$       | $x_5y_2$                      | $x_6y_2$                           | $x_8y_2$                      |                               |                               |                               |                               |                               |                               |

|              |                 | $\boldsymbol{x}_1\boldsymbol{y}_1$ | $x_2y_1$        | $x_3y_1 \\$     | $x_4y_1$        | $x_4y_1$       | $x_5y_1$       | $x_6y_1$                      | $\boldsymbol{x}_8\boldsymbol{y}_1$ |                               |                               |                               |                               |                               |                               |                               |

| PRODUCT      | $p_1$           | p <sub>2</sub>                     | p <sub>3</sub>  | p <sub>4</sub>  | p <sub>5</sub>  | p <sub>6</sub> | $p_7$          | p <sub>8</sub>                | p <sub>9</sub>                     | p <sub>10</sub>               | p <sub>11</sub>               | p <sub>12</sub>               | p13                           | p14                           | p15                           | p16                           |

Figure 1.1: Unsigned Partial Products matrix, n = 8.

Parallel multipliers first generate partial products, then add them together to produce the product. In the following it will be described the generation of Partial Products for unsigned, two's complement, and mixed operand multipliers.

#### **1.1.1 Unsigned Multiplication**

Without loss of generality, let's assume that the inputs of the multiplier represent n bit unsigned fractional value in [0, 1):

$$X = \sum_{i=1}^{n} x_i \cdot 2^{-i} \tag{1.1}$$

$$Y = \sum_{i=1}^{n} y_i \cdot 2^{-i}$$

(1.2)

The output of the multiplier  $P = X \cdot Y$  is computed as:

$$P = \sum_{i=1}^{2n} p_i \cdot 2^{-i} = \sum_{i=1}^n \sum_{j=1}^n x_i y_j \cdot 2^{-i-j}$$

(1.3)

Fig. 1.1 shows the matrix of the Partial Products (PPs)  $x_i y_j$  for a  $8 \times 8$  multiplier. Each row of the matrix corresponds to the products of the multiplicand X and a single bit of the multiplier Y. Generation of the partial products for unsigned multiplication can be implemented with  $n^2 AND$  gates.

| WEIGHT       | -2 <sup>-1</sup> | 2 <sup>-2</sup> | 2-3                 | 2-4                 | 2 <sup>-5</sup>     | 2 <sup>-6</sup>     | 2-7                 | $2^{-8}$                      | 2 <sup>-9</sup>     | $2^{-10}$                     | 2 <sup>-11</sup>              | $2^{-12}$                     | 2 <sup>-13</sup>              | $2^{-14}$                     | $2^{-15}$                     | $2^{-16}$                     |

|--------------|------------------|-----------------|---------------------|---------------------|---------------------|---------------------|---------------------|-------------------------------|---------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|

| MULTIPLICAND | $\mathbf{x}_1$   | $\mathbf{x}_2$  | x <sub>3</sub>      | $\mathbf{x}_4$      | $\mathbf{x}_5$      | x <sub>6</sub>      | $\mathbf{x}_7$      | x <sub>8</sub>                |                     |                               |                               |                               |                               |                               |                               |                               |

| MULTIPLIER   | $\mathbf{y}_1$   | $y_2$           | y <sub>3</sub>      | У4                  | У5                  | y <sub>6</sub>      | У7                  | $y_8$                         |                     |                               |                               |                               |                               |                               |                               |                               |

|              |                  |                 |                     |                     |                     |                     |                     | 1                             | $\overline{x_1y_8}$ | x <sub>2</sub> y <sub>8</sub> | x <sub>3</sub> y <sub>8</sub> | x <sub>4</sub> y <sub>8</sub> | x <sub>5</sub> y <sub>8</sub> | x <sub>6</sub> y <sub>8</sub> | x <sub>7</sub> y <sub>8</sub> | x <sub>8</sub> y <sub>8</sub> |

| PARTIAL      |                  |                 |                     |                     |                     |                     |                     | $\overline{x_1y_7}$           | $x_2y_7$            | $x_3y_7$                      | $x_4y_7$                      | $x_5y_7$                      | $x_6y_7$                      | $x_7y_7$                      | $x_8y_7$                      |                               |