# UNIVERSITÀ DEGLI STUDI DI NAPOLI FEDERICO II

#### DOTTORATO DI RICERCA IN INGEGNERIA ELETTRICA XXI CICLO

### A Fast Digital Integrator for magnetic measurements

Relatori Ch.mo Prof. Nello **POLESE** Ch.mo Prof. Pasquale **ARPAIA**

Co-relatore Dott. Luca **BOTTURA**

Coordinatore Ch.mo Prof. Guido **CARPINELLI**  Candidato Giovanni **SPIEZIA**

Anno accademico 2008

To my parents

# Acknowledgments

I would like to thank my supervisor Prof. Pasquale Arpaia for his full-time guide. His enthusiasm encouraged me a lot by providing a strong motivation to do well my work during the thesis work as a whole.

I would like to express also my gratitude to Luca Bottura, my CERN supervisor, who launched the FDI project. Our discussions were always prone of clever suggestions.

I would like to acknowledge Louis Walchiers and Marco Buzio for their help and participation to the project.

I would like to express my appreciation to my tutor from the university of Naples, Prof. Nello Polese. His guide, helpfulness, and patience were important to achieve this final result.

I would like to acknowledge also the coordinators of the doctoral school from Naples, Prof. Giovanni Miano and Prof. Guido Carpinelli for their careful guide during my work.

I would like to express my gratitude to Prof. Felice Cennamo. He is a wise guide and a wonderful person who always helped me with his precious suggestions.

I would like to thank Alessandro Masi sincerely, who believed in me after my stage at CERN and introduced me to Prof. Arpaia and to the AT/MTM group to start this project.

My gratitude also goes to Walter Scandale for the trust he had in me, from our first meeting at CERN.

I would like to acknowledge Stefano Redaelli who always gave me precious advices. A special thanks also goes to Tatiana Pieloni.

I would like to acknowledge my colleagues from the the university of Naples too, for their help in academic activities.

My work is a part of a project that involved the work of many persons. I would like to express my gratitude to David Giloteaux for his fundamental contribution to the development of the FDI card. I learnt a lot from his experience in electronics.

I would like to thank Vitaliano Inglese. We worked together since I came in the AT department. I found in him a good desk-mate and above all a great friend.

I had the opportunity to work with consultants from University of Sannio. I would like to thank Pasquale Cimmino, to work with him was helpful and amusing. A special thanks also goes to Prof. Giuseppe Di Lucca, MarioLuca Bernardi, and Giuseppe La Commara, for the useful collaboration.

I would like to thank Domenico Della Ratta, Stefano Tiso, Giancarlo Golluccio, Giuseppe Montenero, and Ernesto De Matteis. We had a good time together and their final works for the master degree were a great contribution to the project.

A special thank also goes to Laurent Deniau, J. Garcia Perez, and Peter Galbraith from CERN, and Nathan Brooks, from the university of Texas, for their precious help.

I would like to thank mon amie urbaine Saskia. A very special thanks

also goes to Pierpaolo and Isabella. I cannot make a list of all my friends, because I am afraid to forget someone. Then, I take up the suggestion of my grandmother and I express my gratitude to all of them.

Last but not least, I would like to say *grazie* to my father Giuseppe, my mother Concetta, and my *little-big* brother Onofrio who supported me by showing their deep and unconditioned affect, the most precious contribution for my work.

# Contents

| Sı       | Summary 1 |          |                                                                                                            |    |  |

|----------|-----------|----------|------------------------------------------------------------------------------------------------------------|----|--|

| In       | trod      | uction   |                                                                                                            | 3  |  |

| 1        | CE        | RN co    | ntext of magnetic measurements                                                                             | 10 |  |

|          | 1.1       | CERN     | $V$ accelerators $\ldots$ | 10 |  |

|          | 1.2       | The L    | arge Hadron Collider                                                                                       | 12 |  |

|          | 1.3       | LHC s    | superconducting magnets                                                                                    | 15 |  |

|          |           | 1.3.1    | Dipole Magnets                                                                                             | 15 |  |

| <b>2</b> | Sta       | te of tl | he art of magnetic field measurements                                                                      | 19 |  |

|          | 2.1       | Metho    | ods and instrumentation                                                                                    | 20 |  |

|          |           | 2.1.1    | Rotating coils                                                                                             | 22 |  |

|          |           | 2.1.2    | Stretched wire                                                                                             | 25 |  |

|          |           | 2.1.3    | Magnetic resonance techniques                                                                              | 26 |  |

|          |           | 2.1.4    | Hall probes                                                                                                | 27 |  |

|          |           | 2.1.5    | Fluxgate magnetometer                                                                                      | 28 |  |

|          |           | 2.1.6    | Miscellanea                                                                                                | 29 |  |

|          | 2.2       | Digita   | l integrators                                                                                              | 29 |  |

|          |           | 2.2.1    | Portable Digital Integrator                                                                                | 29 |  |

|          |           | 2.2.2    | Technologies from other research centers                                                                   | 31 |  |

|          |           | 2.2.3    | Commercial integrators and rationale for a custom so-                                                      |    |  |

|          |           |          | lution                                                                                                     | 32 |  |

| 3        | Inst      | trumer   | nt requirements and main issues for fast magnetic                                                          | •  |  |

|          | mea       | asurem   | ients                                                                                                      | 34 |  |

|          | 3.1       | Analy    | sis of the rotating coil method                                                                            | 34 |  |

|          | 3.2 | Frequency bandwidth                           | 36 |

|----------|-----|-----------------------------------------------|----|

|          | 3.3 | Resolution, accuracy, and harmonic distortion | 37 |

|          | 3.4 | Gain and offset stability                     | 39 |

| 4        | Cor | aceptual design                               | 41 |

|          | 4.1 | Proposal                                      | 41 |

|          | 4.2 | Working principle and key design concepts     | 43 |

|          | 4.3 | The architecture                              | 45 |

|          | 4.4 | Measurement algorithm                         | 46 |

| <b>5</b> | Met | trological analysis                           | 48 |

|          | 5.1 | Analytical study                              | 49 |

|          |     | 5.1.1 Time-domain uncertainty                 | 49 |

|          |     | 5.1.2 Amplitude-domain uncertainty            | 50 |

|          | 5.2 | Preliminary numerical analysis                | 52 |

|          |     | 5.2.1 Integration algorithm and ADC rate      | 54 |

|          |     | 5.2.2 UTC                                     | 55 |

|          |     | 5.2.3 Time-domain uncertainty effects         | 55 |

|          |     | 5.2.4 Amplitude-domain uncertainty effects    | 57 |

|          | 5.3 | Comprehensive numerical analysis              | 60 |

|          |     | 5.3.1 Generic analysis strategy               | 61 |

|          |     | 5.3.2 Application to FDI                      | 66 |

|          | 5.4 | Discussion                                    | 76 |

| 6        | Phy | sical design and implementation               | 78 |

|          | 6.1 | The front-end panel                           | 78 |

|          | 6.2 | The digitizer chain                           | 80 |

|          |     | 6.2.1 PGA: AD625                              | 81 |

|          |     | 6.2.2 ADC: AD7634                             | 82 |

|          | 6.3 | DSP: Shark 21262                              | 85 |

|          | 6.4 | FPGA: Spartan XC3S1000L                       | 87 |

|          |     | 6.4.1 The UTC implementation                  | 88 |

|          |     | 6.4.2 Offset and gain correction              | 89 |

|          | 6.5 | The PXI communication bus                     | 90 |

|          | 6.6 | FDI firmware                                  | 91 |

|    |                | 6.6.1    | On-line measurement algorithm                       | . 94  |

|----|----------------|----------|-----------------------------------------------------|-------|

|    | 6.7            | FDI so   | oftware                                             | . 97  |

|    |                | 6.7.1    | Flexible Framework for Magnetic Measurements        | . 97  |

|    |                | 6.7.2    | FDI classes                                         | . 102 |

| 7  | Met            | trologi  | cal and throughput rate characterization            | 105   |

|    | 7.1            | Metro    | logical characterization                            | . 106 |

|    |                | 7.1.1    | Measurement station and characterization strategy . | . 106 |

|    |                | 7.1.2    | Static tests                                        | . 107 |

|    |                | 7.1.3    | Dynamic tests                                       | . 111 |

|    |                | 7.1.4    | Time base tests                                     | . 114 |

|    | 7.2            | Throu    | ghput rate characterization                         | . 116 |

|    |                | 7.2.1    | Test procedure                                      | . 117 |

|    |                | 7.2.2    | Results                                             | . 118 |

|    | 7.3            | FDI sj   | pecifications                                       | . 122 |

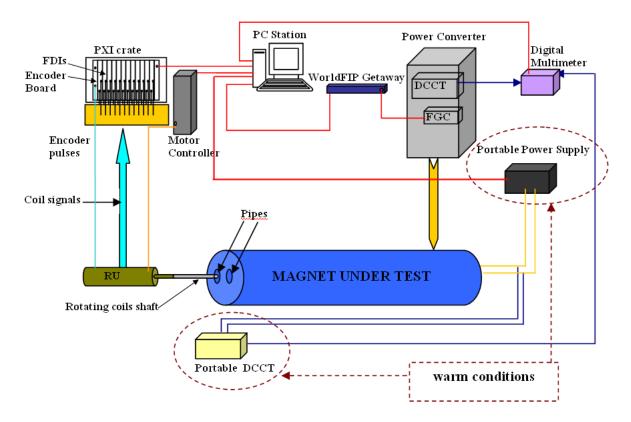

| 8  | On-            | field to | est on superconducting magnets                      | 123   |

|    | 8.1            | The te   | est plan                                            | . 123 |

|    |                | 8.1.1    | The measurement method                              | . 124 |

|    |                | 8.1.2    | The measurement station                             | . 127 |

|    |                | 8.1.3    | The validation procedure                            | . 128 |

|    |                | 8.1.4    | The characterization procedure                      | . 129 |

|    | 8.2            | Exper    | imental results                                     | . 131 |

| Co | onclu          | isions   |                                                     | 139   |

| Re | References 143 |          |                                                     |       |

# List of Figures

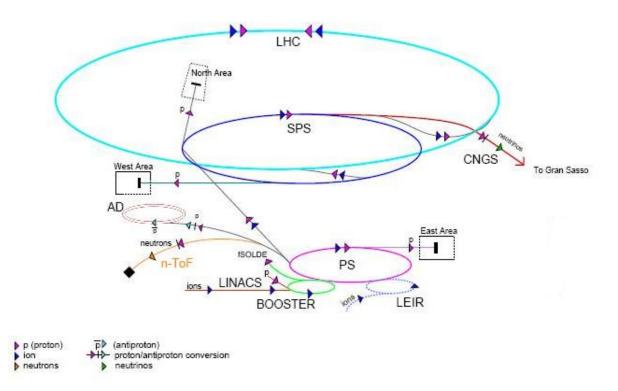

| 1.1 | The accelerator chain at CERN (PS, SPS, and the Large Hadron Collider)                     |    |

|-----|--------------------------------------------------------------------------------------------|----|

|     | and further experimental area (CNGS and AD)                                                | 11 |

| 1.2 | Overview of the Geneva area with a drawn of the two circular acceler-                      |    |

|     | ators: Super Proton Synchrotron (SPS 7 Km) and the Large Hadron                            |    |

|     | Collider (LHC 27 Km)                                                                       | 12 |

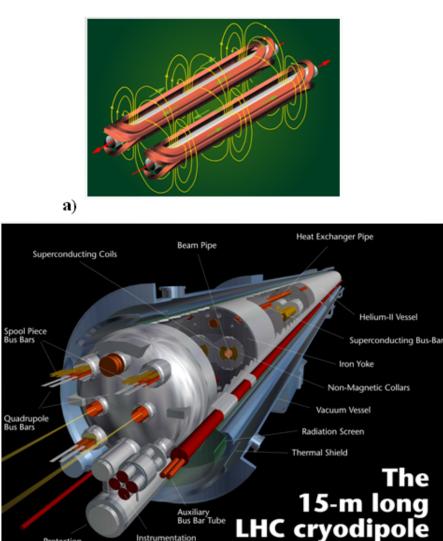

| 1.3 | The 15-m long LHC superconducting dipole: a) Magnetic field; b) par-                       |    |

|     | ticulars                                                                                   | 16 |

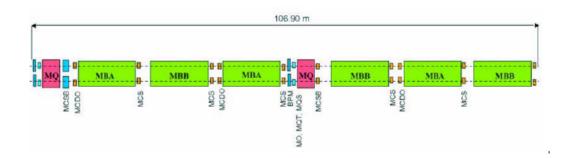

| 1.4 | Scheme of the LHC cell with main bending dipoles, main focusing quadrupoles                | ,  |

|     | and a full correction scheme. $\hdots$                                                     | 17 |

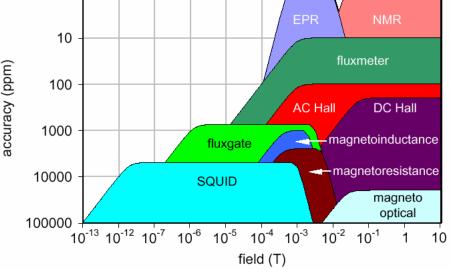

| 2.1 | Expected "best-case" accuracy of the main measurement techniques as a                      |    |

|     | function of the input range.                                                               | 21 |

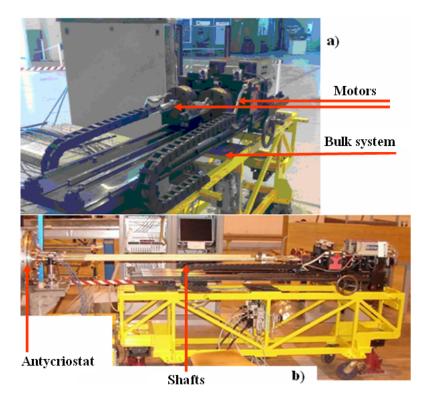

| 2.2 | The TRU unit (a) is attached to the magnet anticryostat by means of a                      |    |

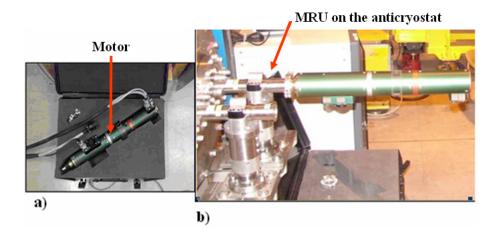

|     |                                                                                            | 24 |

| 2.3 | The MRU unit (a) is attached directly to the magnet anticryostat(b)                        | 25 |

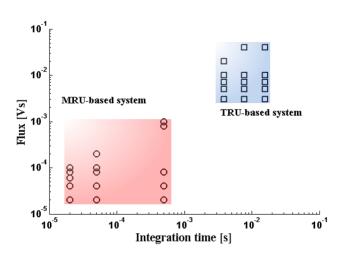

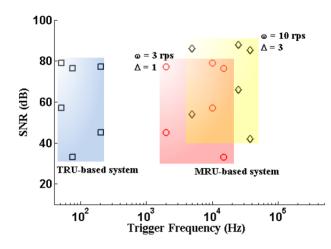

| 3.1 | Comparison between TRU- $(\Box)$ and MRU- $(\circ)$ based systems: flux reso-              |    |

|     | lution as a function of the integration time. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 38 |

| 3.2 | Comparison between TRU- $(\Box)$ and MRU- $(\circ,\diamond)$ based systems: SNR as         |    |

|     | a function of the integration time                                                         | 40 |

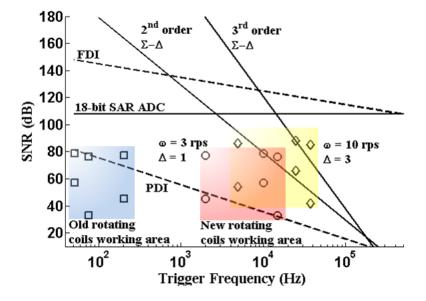

| 4.1 | Theoretical performance limits of state-of-art instruments and FDI com-                    |    |

|     | pared to working areas of old and new generations of rotating coils                        | 42 |

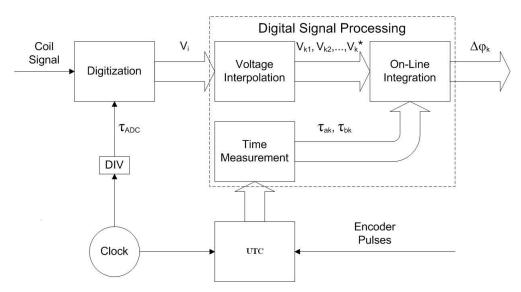

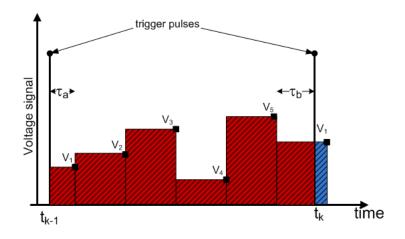

| 4.2 | FDI working principle                                                                      | 43 |

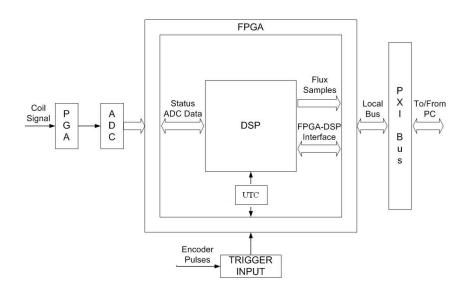

| 4.3 | FDI conceptual architecture.                                                               | 46 |

| 4.4 | Rectangular algorithm.                                                                     | 47 |

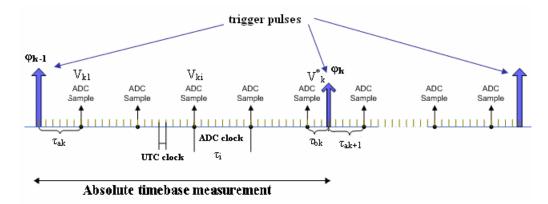

| 4.5 | Time diagram of the FDI measurement                                                        | 47 |

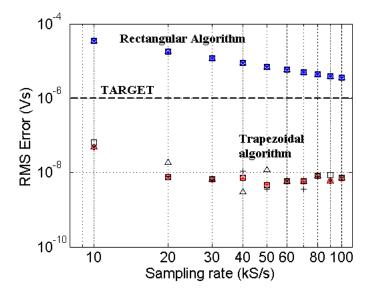

| 5.1                                                                                                                 | Influence on FDI performance of algorithm type, ADC sampling rate,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|                                                                                                                     | and flux sampling rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54                                                                                                         |

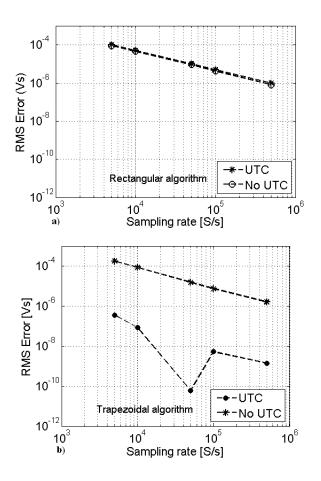

| 5.2                                                                                                                 | UTC influence on FDI performance: RMS error for (a) rectangular algo-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                            |

|                                                                                                                     | rithm and (b) trapezoidal algorithm. $\ldots$ . $\ldots$ . $\ldots$ . $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 56                                                                                                         |

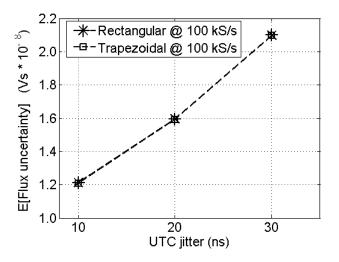

| 5.3                                                                                                                 | Statistical average of the flux uncertainty as function of the UTC jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 57                                                                                                         |

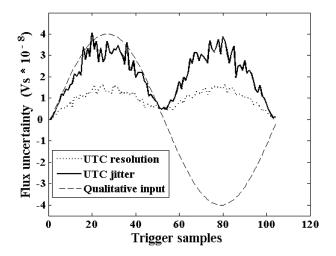

| 5.4                                                                                                                 | Influence of the time-domain uncertainty on the flux uncertainty $\ . \ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58                                                                                                         |

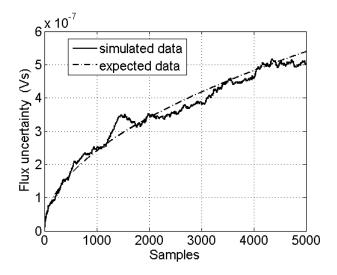

| 5.5                                                                                                                 | Flux uncertainty as function of the time. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 58                                                                                                         |

| 5.6                                                                                                                 | Statistical average of the flux uncertainty as function of the signal input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                            |

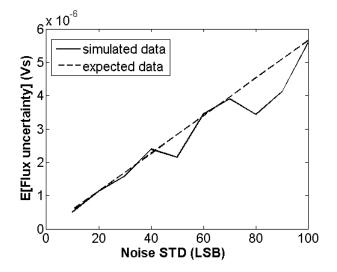

|                                                                                                                     | noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59                                                                                                         |

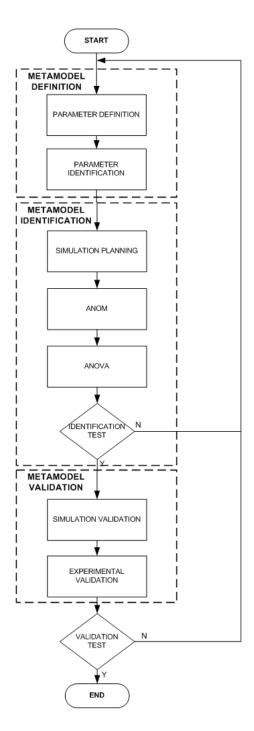

| 5.7                                                                                                                 | Procedure for statistical-based analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63                                                                                                         |

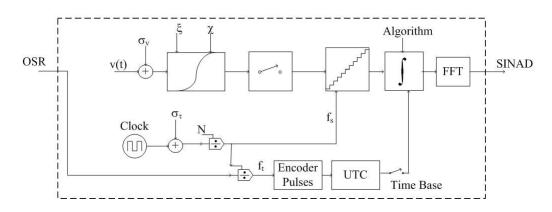

| 5.8                                                                                                                 | FDI model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 68                                                                                                         |

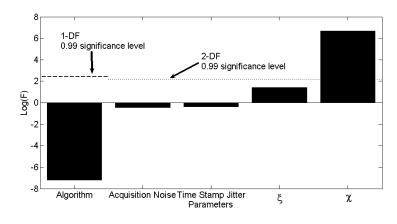

| 5.9                                                                                                                 | Pareto log plot of parameter's variance ratios (DF: degree of freedom). $\ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72                                                                                                         |

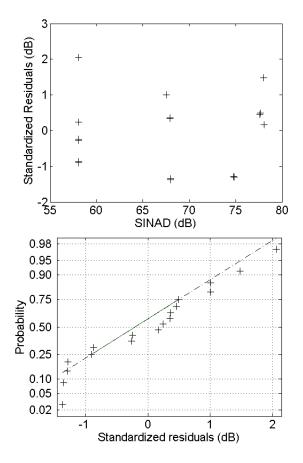

| 5.10                                                                                                                | Plots of ANOVA model standardized residuals: (a) scatter, and (b) nor-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                            |

|                                                                                                                     | mal probability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 73                                                                                                         |

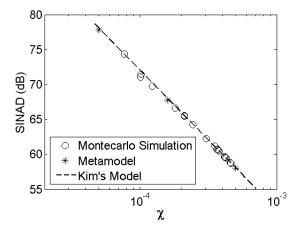

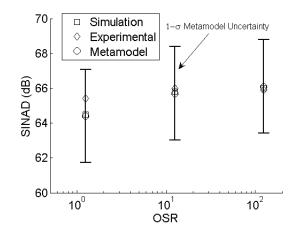

| 5.11                                                                                                                | $\label{eq:comparison} Comparison \ between \ metamodel, \ Monte Carlo \ simulation, \ and \ Kim's \ model.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 75                                                                                                         |

| 5.12                                                                                                                | Comparison among simulated performance $(\Box)$ , experimental performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                            |

|                                                                                                                     | ( $\diamond$ ), and metamodel predictions (o)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75                                                                                                         |

|                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                            |

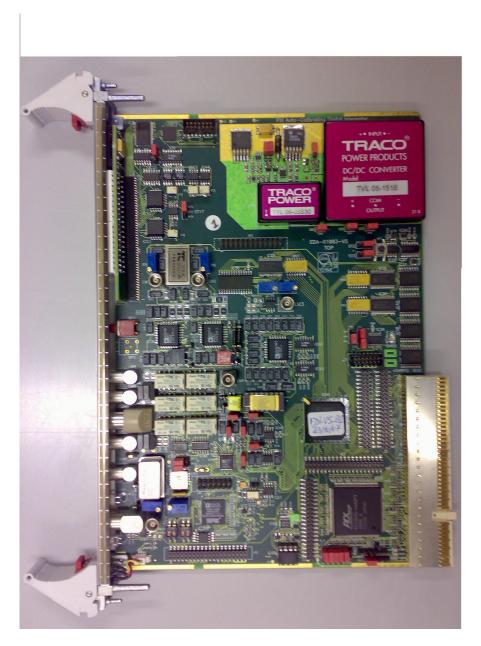

| 6.1                                                                                                                 | The FDI board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 79                                                                                                         |

| $6.1 \\ 6.2$                                                                                                        | The FDI board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 79<br>80                                                                                                   |

| 6.2                                                                                                                 | FDI front-end panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 80                                                                                                         |

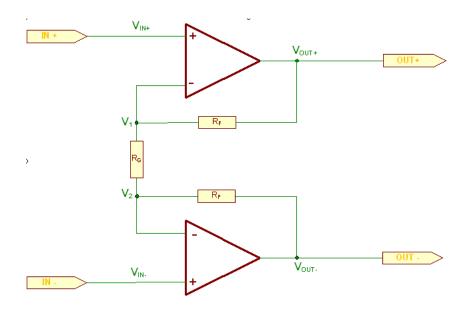

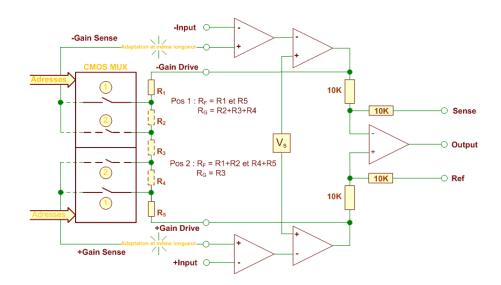

| $6.2 \\ 6.3$                                                                                                        | FDI front-end panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 80<br>81                                                                                                   |

| $6.2 \\ 6.3 \\ 6.4$                                                                                                 | FDI front-end panel.       .       .         FDI instrumentation amplifier.       .       .         Resistor network structure of the FDI instrumentation amplifier.       .       .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 80<br>81<br>83                                                                                             |

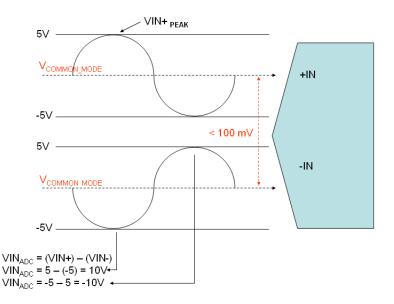

| $6.2 \\ 6.3 \\ 6.4 \\ 6.5$                                                                                          | FDI front-end panel.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 80<br>81<br>83<br>84                                                                                       |

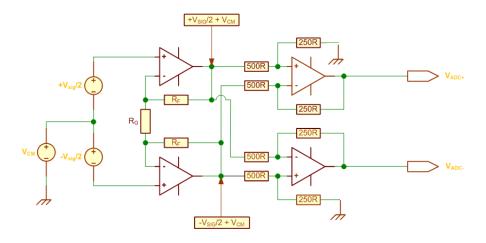

| $6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6$                                                                                   | FDI front-end panel.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 80<br>81<br>83<br>84<br>85                                                                                 |

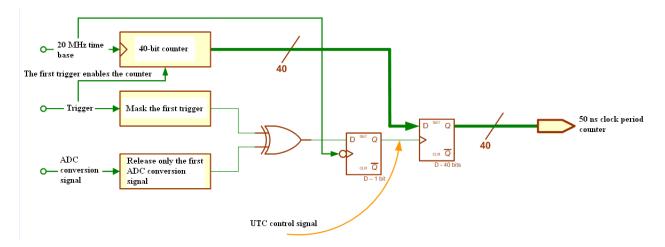

| 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7                                                                              | FDI front-end panelFDI instrumentation amplifierResistor network structure of the FDI instrumentation amplifierDifferential and bipolar input legs of the ADCBuffer circuit to delete the common mode voltageUTC implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 80<br>81<br>83<br>84<br>85<br>88                                                                           |

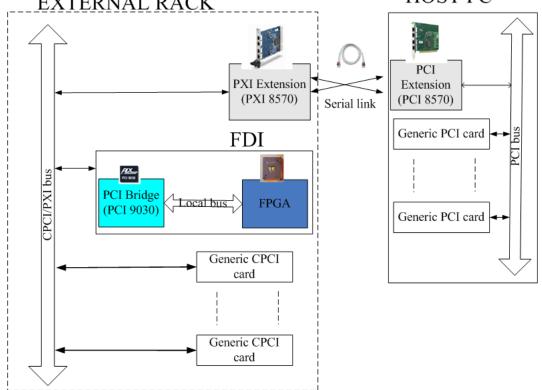

| $\begin{array}{c} 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \end{array}$                                        | FDI front-end panelFDI instrumentation amplifierResistor network structure of the FDI instrumentation amplifierDifferential and bipolar input legs of the ADCBuffer circuit to delete the common mode voltageUTC implementationArchitecture of the PXI-based communication system of the FDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>80</li> <li>81</li> <li>83</li> <li>84</li> <li>85</li> <li>88</li> <li>91</li> </ul>             |

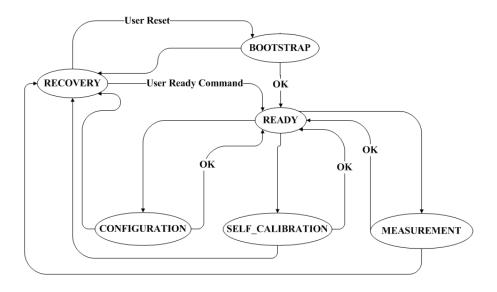

| $\begin{array}{c} 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9 \end{array}$                                 | FDI front-end panelFDI instrumentation amplifierResistor network structure of the FDI instrumentation amplifierDifferential and bipolar input legs of the ADCBuffer circuit to delete the common mode voltageUTC implementationArchitecture of the PXI-based communication system of the FDIThe FDI state machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <ul> <li>80</li> <li>81</li> <li>83</li> <li>84</li> <li>85</li> <li>88</li> <li>91</li> <li>92</li> </ul> |

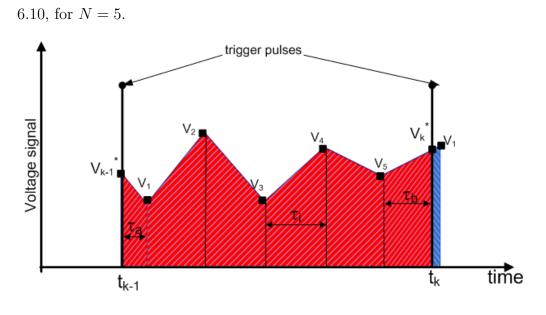

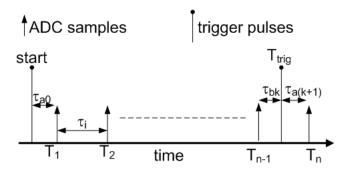

| $\begin{array}{c} 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9 \\ 6.10 \end{array}$                         | FDI front-end panelFDI instrumentation amplifierResistor network structure of the FDI instrumentation amplifierDifferential and bipolar input legs of the ADCBuffer circuit to delete the common mode voltageUTC implementationArchitecture of the PXI-based communication system of the FDIThe FDI state machineTrapezoidal algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 80<br>81<br>83<br>84<br>85<br>88<br>91<br>92<br>96                                                         |

| $\begin{array}{c} 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9 \\ 6.10 \\ 6.11 \end{array}$                 | FDI front-end panelFDI instrumentation amplifierResistor network structure of the FDI instrumentation amplifierDifferential and bipolar input legs of the ADCBuffer circuit to delete the common mode voltageUTC implementationArchitecture of the PXI-based communication system of the FDIThe FDI state machineTrapezoidal algorithmEvaluation of $\tau_{b_k}$ and $\tau_{a_{k+1}}$ by means of the UTC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 80<br>81<br>83<br>84<br>85<br>88<br>91<br>92<br>96<br>97                                                   |

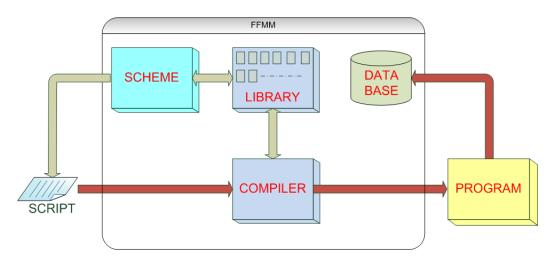

| $\begin{array}{c} 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9 \\ 6.10 \\ 6.11 \\ 6.12 \end{array}$         | FDI front-end panelFDI instrumentation amplifierResistor network structure of the FDI instrumentation amplifierDifferential and bipolar input legs of the ADCBuffer circuit to delete the common mode voltageUTC implementationArchitecture of the PXI-based communication system of the FDIThe FDI state machineTrapezoidal algorithmEvaluation of $\tau_{b_k}$ and $\tau_{a_{k+1}}$ by means of the UTCFFMM conceptual architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 80<br>81<br>83<br>84<br>85<br>88<br>91<br>92<br>96<br>97<br>100                                            |

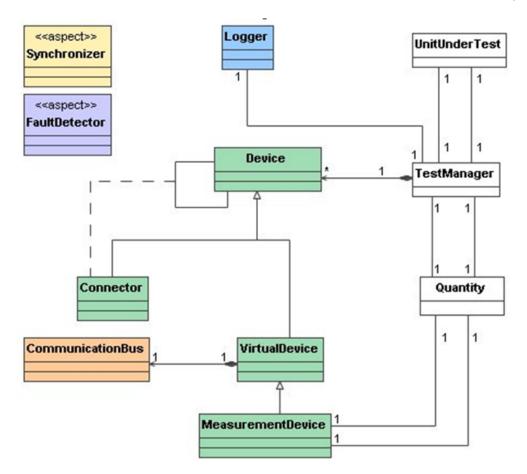

| $\begin{array}{c} 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9 \\ 6.10 \\ 6.11 \\ 6.12 \\ 6.13 \end{array}$ | FDI front-end panelFDI instrumentation amplifierResistor network structure of the FDI instrumentation amplifierDifferential and bipolar input legs of the ADCBuffer circuit to delete the common mode voltageUTC implementationArchitecture of the PXI-based communication system of the FDIThe FDI state machineTrapezoidal algorithmEvaluation of $\tau_{b_k}$ and $\tau_{a_{k+1}}$ by means of the UTCFFMM conceptual architectureArchitecture of the Scheme: class diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80<br>81<br>83<br>84<br>85<br>88<br>91<br>92<br>96<br>97<br>100                                            |

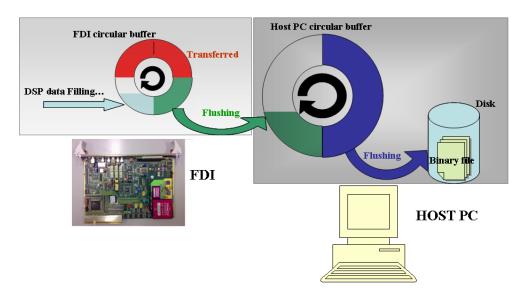

| $\begin{array}{c} 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9 \\ 6.10 \\ 6.11 \\ 6.12 \\ 6.13 \end{array}$ | FDI front-end panelFDI instrumentation amplifierResistor network structure of the FDI instrumentation amplifierDifferential and bipolar input legs of the ADCBuffer circuit to delete the common mode voltageUTC implementationArchitecture of the PXI-based communication system of the FDIThe FDI state machineTrapezoidal algorithmEvaluation of $\tau_{b_k}$ and $\tau_{a_{k+1}}$ by means of the UTCFFMM conceptual architectureFDI data transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 80<br>81<br>83<br>84<br>85<br>88<br>91<br>92<br>96<br>97<br>100                                            |

| $\begin{array}{c} 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9 \\ 6.10 \\ 6.11 \\ 6.12 \\ 6.13 \end{array}$ | FDI front-end panelFDI instrumentation amplifierResistor network structure of the FDI instrumentation amplifierDifferential and bipolar input legs of the ADCBuffer circuit to delete the common mode voltageUTC implementationArchitecture of the PXI-based communication system of the FDIThe FDI state machineTrapezoidal algorithmEvaluation of $\tau_{b_k}$ and $\tau_{a_{k+1}}$ by means of the UTCFFMM conceptual architectureArchitecture of the Scheme: class diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80<br>81<br>83<br>84<br>85<br>88<br>91<br>92<br>96<br>97<br>100                                            |

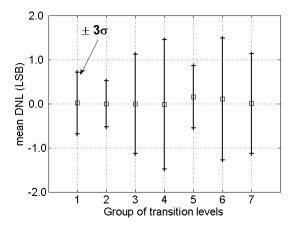

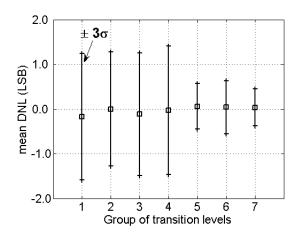

| 7.2  | DNL of FDI in 7 different regions of the input range: mean and standard                 |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | deviation for each transition level group                                               | 109 |

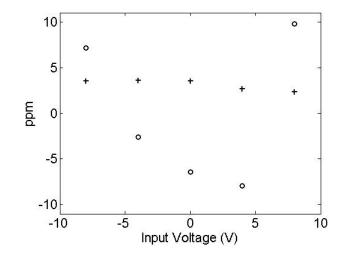

| 7.3  | FDI static nonlinearity errors (o) and $2\sigma$ -uncertainty bands (+), relative       |     |

|      | to full-scale.                                                                          | 110 |

| 7.4  | FDI 24-hours $2\sigma$ -stability bands (o) and $2\sigma$ -repeatability bands (over 30 |     |

|      | minutes) (+), relative to full scale. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$      | 111 |

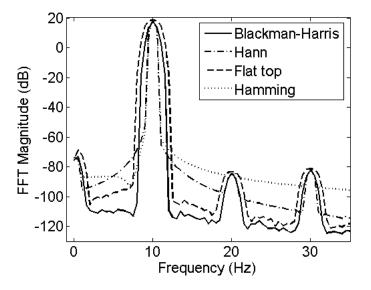

| 7.5  | Comparison of FFT computed by applying different windowing functions.                   | 113 |

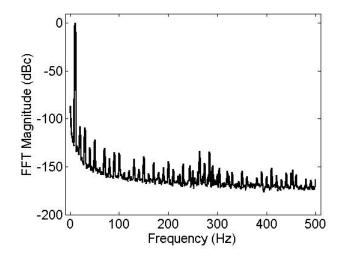

| 7.6  | FFT of the signal integrated by the FDI.                                                | 114 |

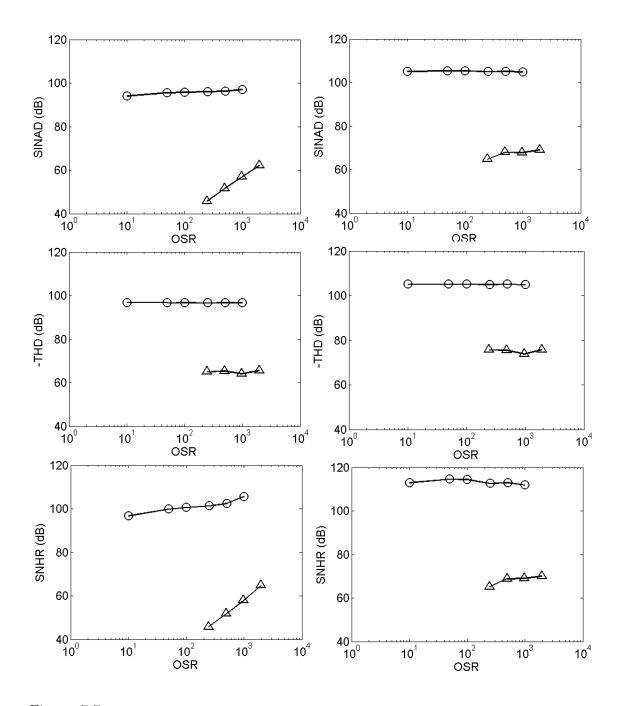

| 7.7  | FDI ( $\circ$ ) and PDI ( $\triangle$ ) dynamic performance vs. oversampling ratio, as  |     |

|      | digitizers (left) and as integrators (right).                                           | 115 |

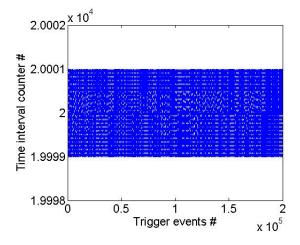

| 7.8  | The time interval counter (a) and the $\tau_a$ (b) values evaluated by the              |     |

|      | 32-bit integer algorithm.                                                               | 116 |

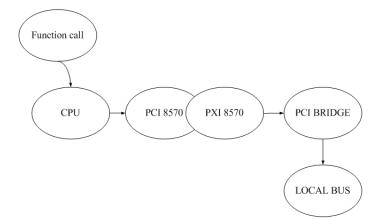

| 7.9  | The PXI initiator-target chain of the FDI                                               | 117 |

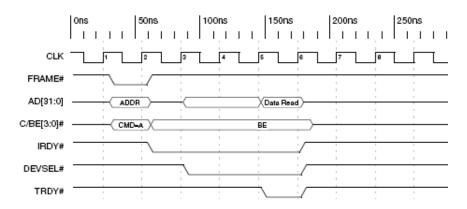

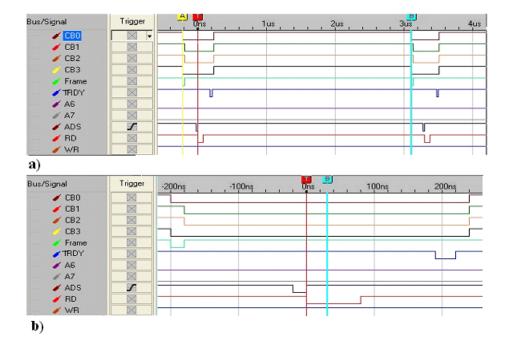

| 7.10 | PCI signals for a single read operation.                                                | 118 |

| 7.11 | Local bus read operation: a) two consecutive reading; b) zoom on the                    |     |

|      | read cycle                                                                              | 119 |

| 7.12 | PCI bus signals (PCI 8570) and extension bus signals (PXI 8570). $\hfill .$ .           | 120 |

| 7.13 | Report analysis of the bus transactions by a PCI analyser                               | 121 |

| 0.1  |                                                                                         | 107 |

| 8.1  | Rotating coil test station                                                              |     |

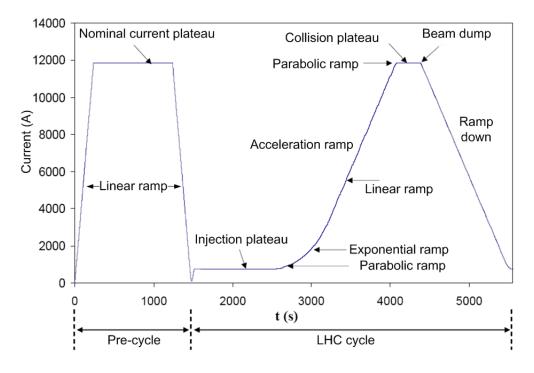

| 8.2  | LHC standard current cycle                                                              |     |

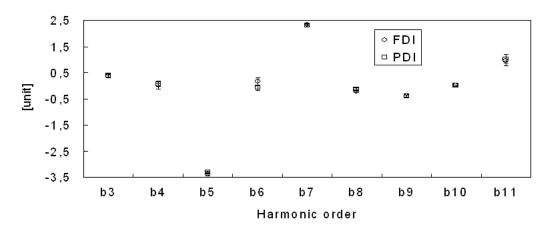

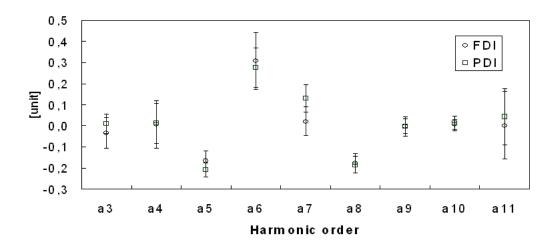

| 8.3  | Average of the normal field harmonics with $\pm 3\sigma$ bar                            |     |

| 8.4  | Average of the skew field harmonics with $\pm 3\sigma$ bar                              | 132 |

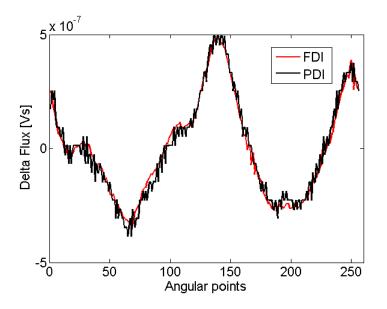

| 8.5  | Flux increments of the compensated coil signal at warm conditions, mea-                 | 101 |

|      | sured by the FDI-based and the PDI-based platforms                                      |     |

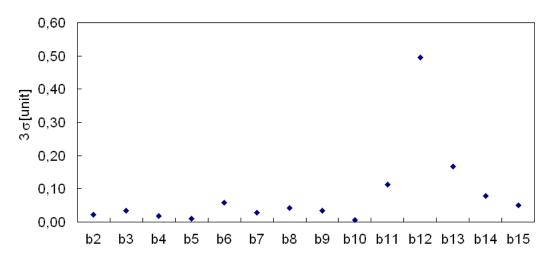

| 8.6  |                                                                                         | 134 |

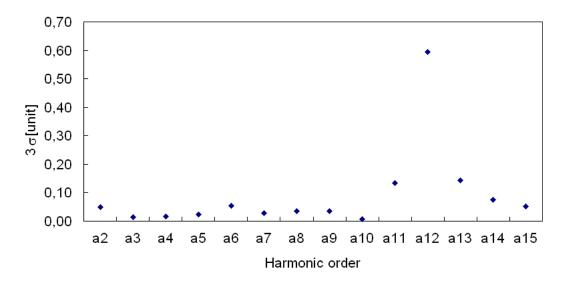

| 8.7  | $\pm 3\sigma$ repeatability band of the skew field harmonics at cold conditions.        |     |

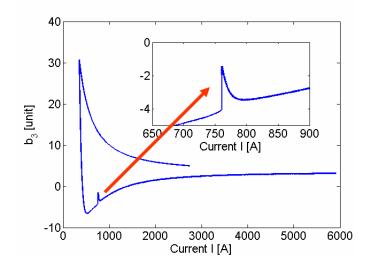

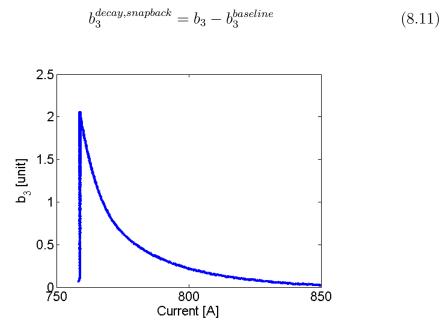

| 8.8  | $b_3$ decay and snapback phenomena                                                      | 136 |

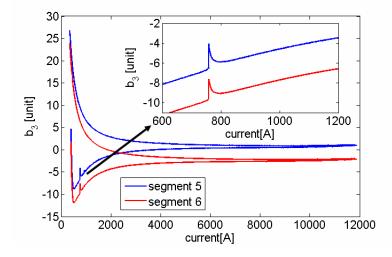

| 8.9  | $b_3$ as a function of the current along a LHC energy cycle on two MRU                  |     |

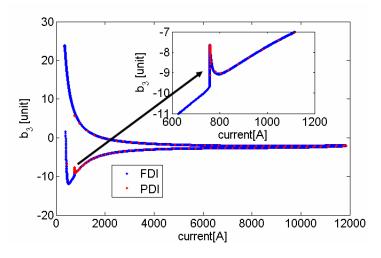

|      | shaft segments(a); highlight of the decay phenomena (b)                                 | 137 |

| 8.10 | Comparison between the new system (FDI) and the previous one (PDI):                     |     |

|      | $b_3$ on the $6^{th}$ segment                                                           |     |

| 8.11 | Decay and snapback of $b_3$                                                             | 138 |

# List of Tables

| 5.1 | Flux uncertainty arising from amplitude domain                                |

|-----|-------------------------------------------------------------------------------|

| 5.2 | Numerical values of the metamodel parameters                                  |

| 5.3 | ANOM results at 1 kHz trigger frequency                                       |

| 5.4 | ANOVA results at 1 kHz trigger frequency                                      |

| 6.1 | AD 625 specifications. $\ldots$ 82                                            |

| 6.2 | FDI gain set                                                                  |

| 6.3 | FDI status register                                                           |

| 6.4 | FDI status register                                                           |

| 7.1 | FDI status register                                                           |

| 7.2 | FDI specifications.                                                           |

|     | $^{\ast}$ The ADC sampling rate are: 500 kS/s, 250 kS/s, 125 kS/s, 62.5 kS/s, |

|     | 31.25  kS/s, 15.625  kS/s, 7.81  kS/s,  and  1  S/s.                          |

|     | ** See Tab. 6.2                                                               |

| 8.1 | $2^{nd}$ order normal and skew harmonics for PDI- and FDI- based system $132$ |

| 8.2 | $\pm 3\sigma$ repeatability band for PDI- and FDI-based systems               |

# List of Acronyms

| AD<br>ADC<br>ADL<br>ANCOVA<br>ANOVA<br>ANOM<br>AOP | <ul> <li>-Antiproton Decelerator</li> <li>-Analog-to-Digital Converter</li> <li>-Advanced Description Language</li> <li>-ANalysis of COVAriance</li> <li>-ANalysis Of VAriance</li> <li>-ANalysis Of Mean</li> <li>-Aspect Oriented Programming</li> </ul> |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AT                                                 | -Accelerator Technology                                                                                                                                                                                                                                    |

| BNL                                                | -Berkeley National Laboratory                                                                                                                                                                                                                              |

| CEA                                                | -Commisariat a l'Energie Atomique                                                                                                                                                                                                                          |

| CERN                                               | -European Organization for Nuclear Research                                                                                                                                                                                                                |

| CLB                                                | -Configurable Logic Blocs                                                                                                                                                                                                                                  |

| CMRR                                               | -Common Mode Rejection Ratio                                                                                                                                                                                                                               |

| CNAO                                               | -National Center of Oncological Hadrontherapy                                                                                                                                                                                                              |

| CNGS                                               | -CERN Neutrino to Gran Sasso                                                                                                                                                                                                                               |

| CPCI                                               | -Compact Peripheral Component Interconnect                                                                                                                                                                                                                 |

|                                                    |                                                                                                                                                                                                                                                            |

| DAI                                                | -Digital Audio Interface                                                                                                                                                                                                                                   |

| DCCT                                               | -Direct Current-Current Transformer                                                                                                                                                                                                                        |

| $\mathrm{DF}$                                      | -Degree of Freedom                                                                                                                                                                                                                                         |

| DFT                                                | -Discrete Fourier Transform                                                                                                                                                                                                                                |

| DMA                                                | -Direct Memory Access                                                                                                                                                                                                                                      |

| DNL                                                | -Differential Non Linearity                                                                                                                                                                                                                                |

| DSP                                                | -Digital Signal Processor                                                                                                                                                                                                                                  |

|                                                    |                                                                                                                                                                                                                                                            |

| EMR                  | -Electron Magnetic Resonance             |

|----------------------|------------------------------------------|

| EMS                  | -Extensible Measurement System           |

| ENOB                 | -Effective Number Of Bit                 |

| EPR                  | -Electron paramagnetic resonance(        |

| ESR                  | -Electron Spin Resonance                 |

| ESRF                 | -European Synchrotron Radiation Facility |

|                      |                                          |

| FAME                 | -FAst Magnetic Equipment                 |

| FDI                  | -Fast Digital Integrator                 |

| FESA                 | -Front-End Software Architecture         |

| $\operatorname{FFT}$ | -Fast Fourier Transform                  |

| FGC                  | -Function Generator Controller           |

| FNAL                 | -Fermi National Accelerator Laboratory   |

| FPGA                 | -Field Programmable Gate Array           |

|                      |                                          |

| HEP                  | -High Energy Physics                     |

|                      |                                          |

| IDP                  | -Input Data Port                         |

| INL                  | -Integral Non Linearity                  |

| ISR                  | -Interrupt Service Routine               |

|                      |                                          |

| LHC                  | Large Hadron Collider                    |

| LSB                  | Least Significant Bit                    |

|                      |                                          |

| MIX                  | -Modular Interface eXtension             |

| MMP                  | -Magnetic Measurement Program            |

| MRU                  | -Micro Rotating Unit                     |

| MS                   | -Mean Square                             |

| MTM                  | Magnet Tests and Measurements            |

|                      |                                          |

| NMR                  | Nuclear Magnetic Resonator               |

| 000                  |                                          |

| OOP                  | Object Oriented Programming              |

|                      |                                          |

| OVXC  | -Oven Controlled Xtal Oscillator              |

|-------|-----------------------------------------------|

| PCI   | -Peripheral Component Interconnect            |

| PDI   | -Portable Digital Integrator                  |

| PELP  | -Parabolic Exponential Linear Parabolic       |

| PGA   | -Programmable Gain Amplifier                  |

| PCG   | -Precision Clock Generator                    |

| PS    | -Proton Synchrotron                           |

| PXI   | -PCI eXtensions for Instrumentation           |

| RF    | -Radio Frequency                              |

| RMS   | -Root Mean Square                             |

| SAR   | -Successive Approximation Register            |

| SINAD | -SIgnal-to-Noise And Distortion               |

| SNHD  | -Signal Non Harmonic Distortion               |

| SNR   | -Signal-to-Noise Ratio                        |

| SPI   | -Serial Port Interface                        |

| SPS   | -Super Proton Synchrotron                     |

| SQUID | -Superconducting QUantum Interference Devices |

| SRS   | -Single Response Surface                      |

| SS    | -Sum of Squares                               |

| SSS   | -Short Straight Section                       |

| SSW   | -Single Stretched Wire                        |

| THD   | -Total Harmonic Distortion                    |

| TRU   | -Twin Rotating Unit                           |

| UDC   | -Up-Down Counter                              |

| UTC   | -Universal Time Counter                       |

| VFC   | -Voltage-to-Frequency Converter               |

| VHDL  | -VHSIC Hardware Description Language          |

| VHSIC | -Very-High Speed Integrated Circuits          |

XML

-eXtensible Markup Language

### Summary

In this work, the Fast Digital Integrator (FDI), conceived for characterizing dynamic features of superconducting magnets and measuring fast transients of magnetic fields at the European Organization for Nuclear Research (CERN) and other high-energy physics research centres, is presented. FDI development was carried out inside a framework of cooperation between the group of Magnet Tests and Measurements of CERN and the Department of Engineering of the University of Sannio.

Drawbacks related to measurement time decrease of main high-performance analog-to-digital architectures, such as  $\Delta - \Sigma$  and integrators, are overcome by founding the design on (i) a new generation of successive-approximation converters, for high resolution (18-bit) at high rate (500 kS/s), (ii) a digital signal processor, for on-line down-sampling by integrating the input signal, (iii) a custom time base, based on a Universal Time Counter, for reducing time-domain uncertainty, and (iv) a PXI board, for high bus transfer rate, as well as noise and heat immunity. A metrological analysis, aimed at verifying the effect of main uncertainty sources, systematic errors, and design parameters on the instrument performance is presented. In particular, results of an analytical study, a preliminary numerical analysis, and a comprehensive multi-factor analysis carried out to confirm the instrument design, are reported. Then, the selection of physical components and the FDI implementation on a PXI board according to the above described conceptual architecture are highlighted. The on-line integration algorithm, developed on the DSP in order to achieve a real-time Nyquist bandwidth of 125 kHz on the flux, is described. C++ classes for remote control of FDI, developed as a part of a new software framework, the Flexible Framework for Magnetic Measurements, conceived for managing a wide spectrum of magnetic measurements techniques, are described.

Experimental results of metrological and throughput characterization of FDI are reported. In particular, in metrological characterization, FDI working as a digitizer and as an integrator, was assessed by means of static, dynamic, and time base tests. Typical values of static integral nonlinearity of  $\pm 7 \ ppm$ ,  $\pm 3 \ ppm$  of 24-h stability, and 108 dB of signal-to-noise-and-distortion ratio at 10 Hz on Nyquist bandwidth of 125 kHz, were surveyed during the integrator working. The actual throughput rate was measured by a specific procedure of PXI bus analysis, by highlighting typical values of 1 MB/s.

Finally, the experimental campaign, carried out at CERN facilities of superconducting magnet testing for on-field qualification of FDI, is illustrated. In particular, the FDI was included in a measurement station using also the new generation of fast transducers. The performance of such a station was compared with the one of the previous standard station used in series tests for qualifying LHC magnets. All the results highlight the FDI full capability of acting as the new de-facto standard for high-performance magnetic measurements at CERN and in other high-energy physics research centres.

# Introduction

At the European Organization for Nuclear Research (CERN), the design and realization of the particle accelerator Large Hadron Collider (LHC) [1] has required a remarkable technological effort in many areas of engineering. In particular, the tests of LHC superconducting magnets disclosed new horizons to magnetic measurements [2], [3].

Standard magnetic measurements on accelerator magnets are mostly based on the integration of a voltage signal in order to get the magnetic flux, according to Faraday's law (such as in rotating coils, fixed coils, stretched wire, and so on)[4], [5], [6], [7], complemented also by other techniques (such as Hall plates) [8].

In last years, several fast transducers have been developed in order to achieve an increase of two orders of magnitude in the bandwidth of harmonic measurements (10 to 100 Hz), when compared to the standard rotating coil technique (typically 1 Hz or less), and still maintaining a typical resolution of 10 ppm [9], [10].

A similar development was performed also in other High-Energy Physics (HEP) laboratories, by achieving typical resolution of few tens of ppm, at rates from 10 to 100 Hz in the measurement of field harmonics for pulsed accelerator magnets [11], [12].

These developments pave the way for a major improvement of the theoretical and experimental analysis of superconducting accelerator magnets. However, at the same time, they push the performance requirements on digital instrumentation for data acquisition.

At CERN, the objectively large R&D effort of the group Accelerator Technolgy/Magnet Test and Measurements (AT/MTM) identified areas where further work is required in order to assist the LHC commissioning and start-up, to provide continuity in the instrumentation for the LHC magnets maintenance, and to achieve more accurate magnet models for the LHC exploitation [13], [14], [15]. Two particularly important topics are directing the medium term planning. The first is an upgrade of the measurement capabilities of rotating coils to cover a bandwidth of 10 Hz, possibly complemented with local analysis by Hall plates probes, in order to extend the frequency reach during specific tests [16]. Provided that the flux induction measurement methods require the integration of the incoming signal, the second topic is the design of a new integrator, whose capability would cover local and integrated field strength, field direction, harmonics and axis for both low and high field conditions.

Therefore, the project FAst Magnetic measurements Equipment (FAME) was launched for renewing the magnetic measurement facilities, making them suitable for the above mentioned new generation of transducers.

The first goal of FAME is the design and the development of a rotating coil system based on a new rotating unit, the Micro Rotating Unit [10], capable of turning at a speed up to  $10 \ rps$ , marking an improvement of about a factor 10 with respect to the previous Twin Rotating Unit (TRU) [17]. Consequently, a new integrator is required in order to fulfill the requirements imposed by

the new rotating coil systems, in terms of bandwidth and accuracy.