Vyas, Bimal H., 2007, "*Study of Various Motherboards*", thesis PhD, Saurashtra University

http://etheses.saurashtrauniversity.edu/id/eprint/678

Copyright and moral rights for this thesis are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the Author.

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the Author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

Saurashtra University Theses Service <u>http://etheses.saurashtrauniversity.edu</u> repository@sauuni.ernet.in

© The Author

### **Study of Various Motherboards**

Thesis Submitted to the Saurashtra University, Rajkot For The Degree of Doctor of Philosophy (Science) (Electronics)

> By Bimal H. Vyas Hardware Support Specialist Alpha and VAX Server Division Hewlett Packard Canada

### **Research Supervisor**

Dr. H. N. Pandya Associate Professor, Department of Electronics Saurashtra University, Rajkot-360005 India

January 2007

Affectionately dedicated to My parents Dr. H. F. Vyas Dr. U. H. Vyas Statement under O. Ph. D. of Saurashtra University

The content of this thesis is my own work carried out under the supervision of Dr. H. N. Pandya and leads to some contribution in Electronics supported by necessary references.

(B. H. Vyas) Hardware Support Specialist Alpha and VAX Server Division Hewlett Packard Canada

This is to certify that the present work submitted by Mr. Bimal H. Vyas for the Ph.D. degree of Saurashtra University, Rajkot, Gujarat, India has been the result of about 5 years of work under my supervision and is a valuable contribution in the field of Electronics.

Dr. H. N. Pandya, Associate Professor, Department of Electronics, Saurashtra University, Rajkot- 360 005

### **Acknowledgement**

I sincerely thank to my research advisor, Dr. Haresh N. Pandya , Head, Department of Electronics, Saurashtra University, Rajkot. He is not only a great scientist with deep vision but also and most importantly a kind person. His trust and scientific excitement inspired me in the most important moments of making right decisions and I am glad to work with him. His guidance and mentorship make my work easy and valuable. Also I got moral support from his wife Mrs. Kiran Pandya and lots of love from his little daughter Miss Shweta Pandya through out my research.

I want to thank all great people of the Department of Electronics. Without their co-operation and kindness this work would not have been successfully completed.

Special thanks go to Mr. Maulin Nanavati who is a great helpful and trustful friend. My words will be short to say thanks to him for being the best co-operative friend. He was always with me in good and bad time during the study.

I am very much thankful to my uncle Arvind Vyas, Aunty Jaishree Vyas, cousins Rushi and Ravi Vyas for moral support through out my study.

My colleagues Mr. Andnd Bhaskar, Dr. Darshan Vyas, and Mr. Harshad Chirutkar made my work running smoothly. My senior, Dr. Kapil Bhatt, from the Department of Electronics, Saurashtra University, Rajkot supported me in my research work. I want to thank him for all their help, support, interest and valuable hints. Also would like to thanks Mr. Rajendrakumar Khar, Mr. Jaipalsinh Zala, Mr. Hemanshu Vachaani and all other friends.

There was a lovely friend Neha Vyas, who provided an additional and joyful dimension to the life mission.

After my migration to Canada, my research is also blessed by Paul Brown, Claudia Caredona Tellisa and Pierre Severney.

I feel a deep sense of gratitude for my father Dr. H. F Vyas and my mother Dr. Usha H. Vyas, who provided me an opportunity to gain a higher level education. I am grateful for my sisters, brother and brother-in-law. Love of my cute nephew and niece was always with me.

| Chapter - 1:                 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                  |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|

|                              | 1.1 Objective of the present work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                  |  |  |

|                              | 1.2 Literature Survey                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                  |  |  |

|                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                  |  |  |

| Chapter - 2:                 | Basics of Motherboard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                  |  |  |

| enupter 21                   | 2.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8                                                                |  |  |

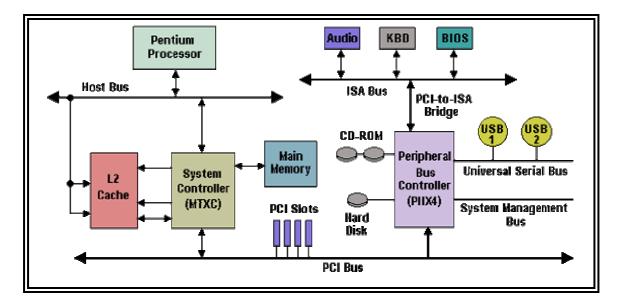

|                              | 2.2 logic block of motherboard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                                |  |  |

|                              | 2.2 logic block of monierboard<br>2.2.1 List of Logic blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                |  |  |

|                              | 2.2.1 East of Logic blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                  |  |  |

|                              | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                  |  |  |

|                              | 2.3 Software - requirement to communicate hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40                                                               |  |  |

| Chanton 2.                   | Single Board Computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                  |  |  |

| Chapter - 3:                 | e i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 42                                                               |  |  |

|                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                  |  |  |

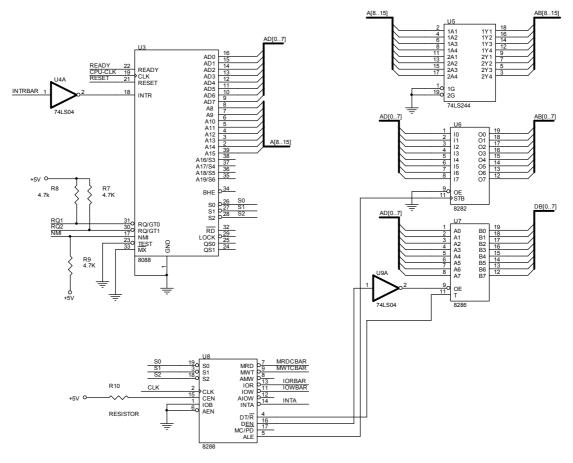

|                              | 3.2 CPU Section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                  |  |  |

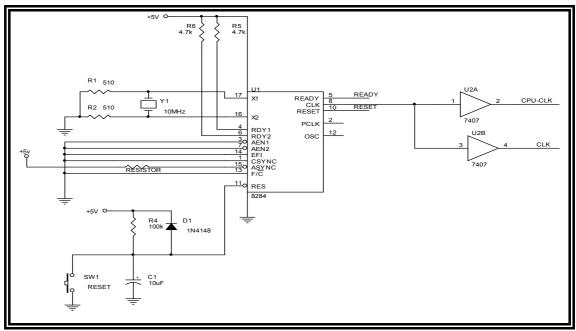

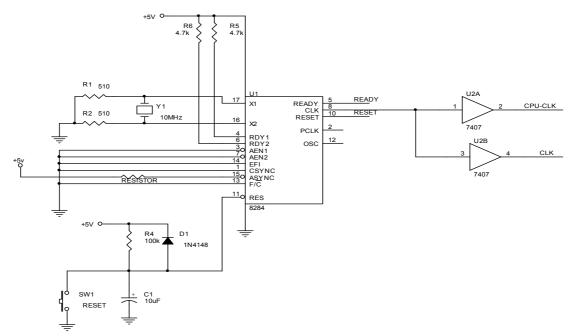

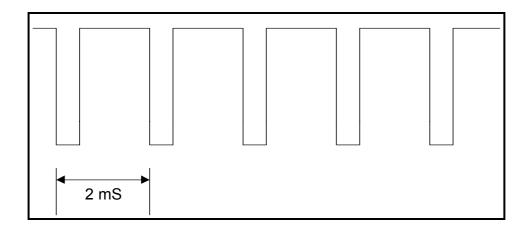

|                              | 3.3 Clock generation Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                  |  |  |

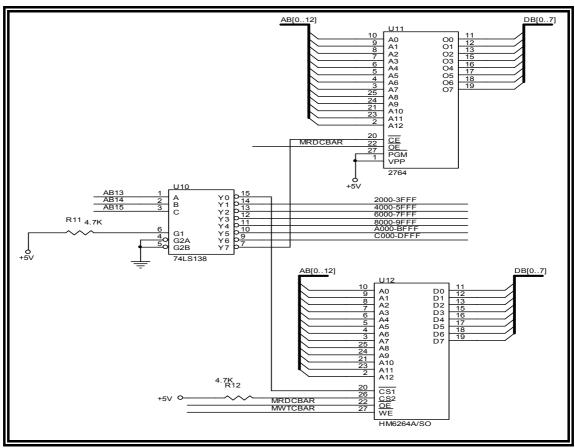

|                              | 3.4 Memory Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45                                                               |  |  |

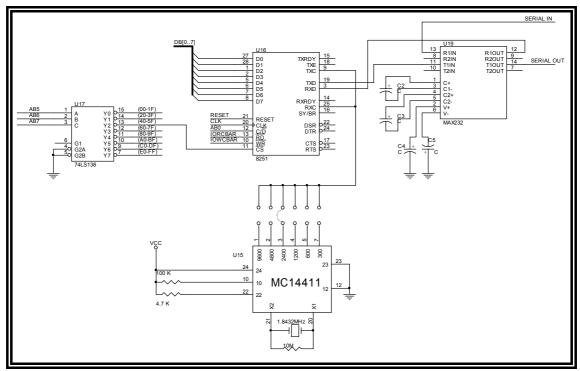

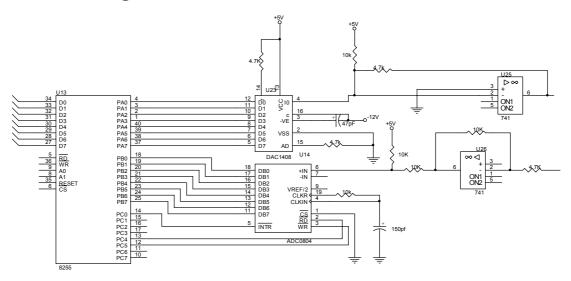

|                              | 3.5 Input output Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                  |  |  |

|                              | 3.5.1 Serial Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 47                                                               |  |  |

|                              | 3.5.2 Parallel Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 48                                                               |  |  |

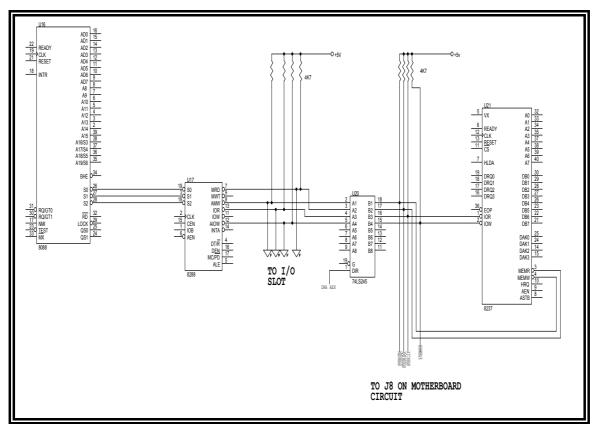

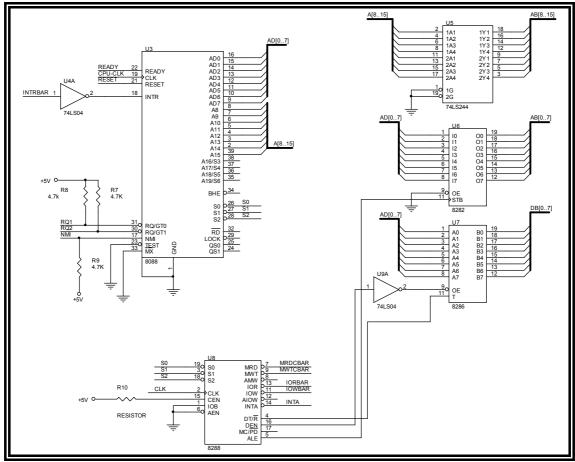

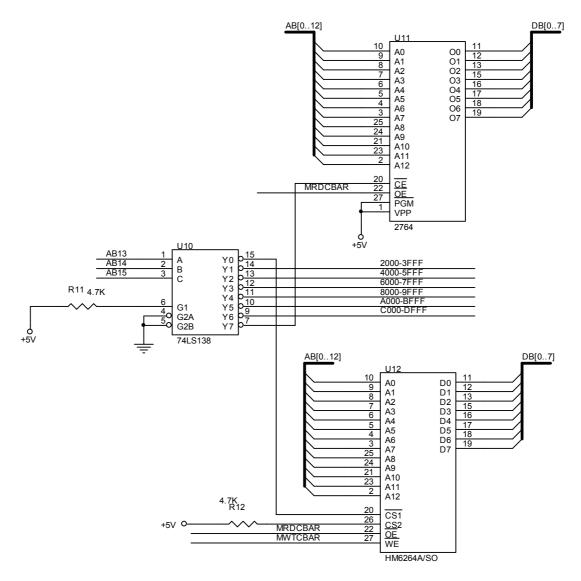

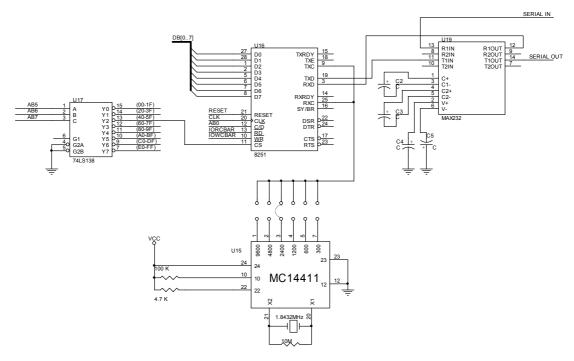

|                              | 3.6 Schematic Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49                                                               |  |  |

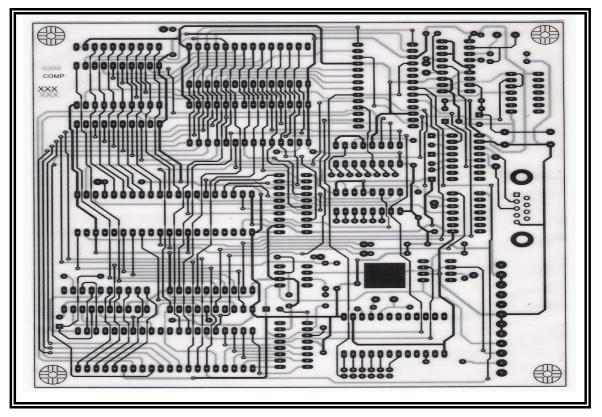

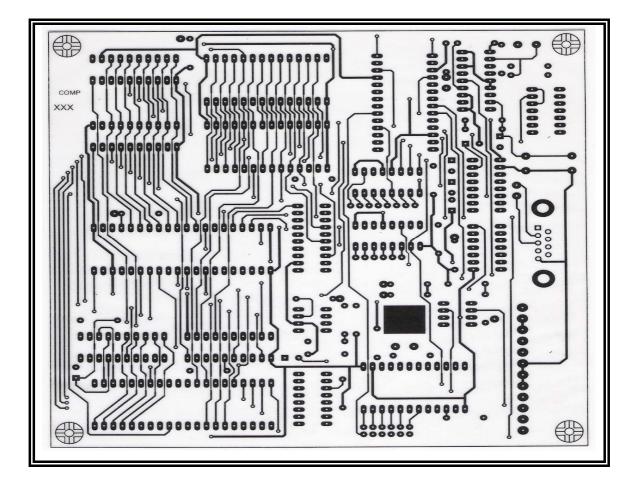

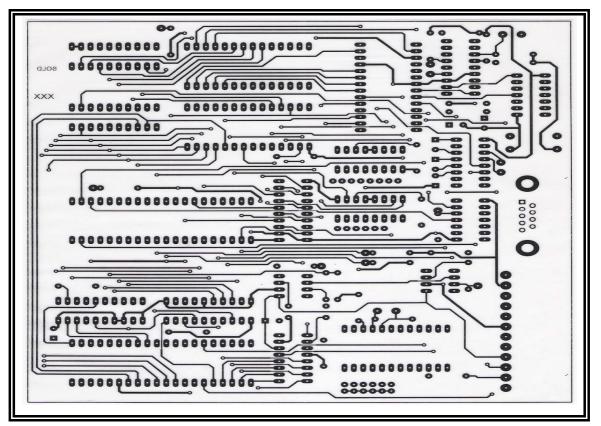

|                              | 3.7 PCB layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52                                                               |  |  |

|                              | 3.8 Software Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 54                                                               |  |  |

|                              | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                  |  |  |

|                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                  |  |  |

| Chapter - 4:                 | Study of New semiconductor Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                  |  |  |

| Chapter - 4:                 | Study of New semiconductor Technology4.1Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 88                                                               |  |  |

| Chapter - 4:                 | 4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                  |  |  |

| Chapter - 4:                 | 4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 88                                                               |  |  |

| Chapter - 4:                 | <ul><li>4.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 88                                                               |  |  |

|                              | <ul><li>4.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 88                                                               |  |  |

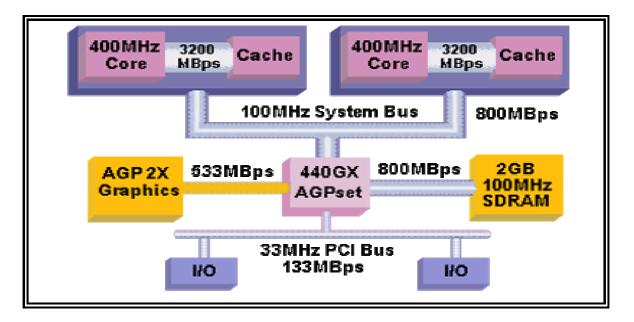

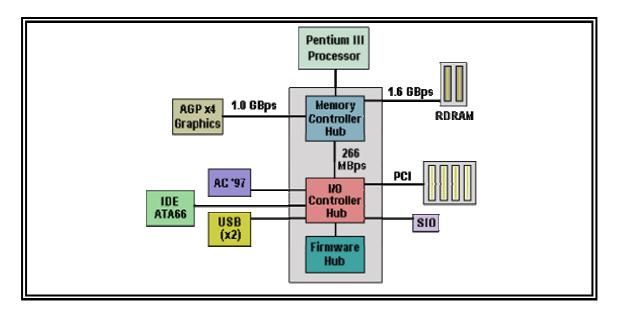

|                              | <ul> <li>4.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88<br>92                                                         |  |  |

|                              | <ul> <li>4.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88<br>92                                                         |  |  |

|                              | <ul> <li>4.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88<br>92<br>118<br>118                                           |  |  |

|                              | <ul> <li>4.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88<br>92<br>118<br>118<br>123                                    |  |  |

|                              | <ul> <li>4.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88<br>92<br>118<br>118<br>123<br>132                             |  |  |

|                              | <ul> <li>4.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88<br>92<br>118<br>118<br>123<br>132<br>156                      |  |  |

|                              | <ul> <li>4.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88<br>92<br>118<br>118<br>123<br>132<br>156                      |  |  |

| Chapter - 5:                 | <ul> <li>4.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88<br>92<br>118<br>118<br>123<br>132<br>156                      |  |  |

| Chapter - 5:                 | <ul> <li>4.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88<br>92<br>118<br>118<br>123<br>132<br>156<br>156               |  |  |

| Chapter - 5:                 | <ul> <li>4.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88<br>92<br>118<br>123<br>132<br>156<br>156<br>198               |  |  |

| Chapter - 5:                 | <ul> <li>4.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88<br>92<br>118<br>123<br>132<br>156<br>156<br>198<br>199        |  |  |

| Chapter - 5:                 | <ul> <li>4.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88<br>92<br>118<br>123<br>132<br>156<br>156<br>198<br>199        |  |  |

| Chapter - 5:<br>Chapter - 6: | <ul> <li>4.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88<br>92<br>118<br>123<br>132<br>156<br>156<br>198<br>199        |  |  |

| Chapter - 5:<br>Chapter - 6: | <ul> <li>4.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88<br>92<br>118<br>123<br>132<br>156<br>156<br>198<br>199<br>226 |  |  |

| Chapter - 5:<br>Chapter - 6: | <ul> <li>4.1 Introduction.</li> <li>4.2 Chipset Technology.</li> <li>4.3 Detail study of Chipsets.</li> <li>Various Motherboards</li> <li>5.1 Introduction.</li> <li>5.2 286 Motherboard.</li> <li>5.3 386 Motherboard.</li> <li>5.4 486 Motherboard.</li> <li>5.5 Celeron Motherboard.</li> <li>5.6 Pentium Motherboard.</li> <li>5.6 Pentium Motherboard.</li> <li>5.6 Pentium Motherboard.</li> <li>6.1 Methods of troubleshooting.</li> <li>6.2 Observation of probe points.</li> <li>6.3 Observation and conclusion of faults</li> </ul> | 88<br>92<br>118<br>123<br>132<br>156<br>156<br>198<br>199<br>226 |  |  |

| Chapter - 5:<br>Chapter - 6: | <ul> <li>4.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88<br>92<br>118<br>123<br>132<br>156<br>156<br>198<br>199<br>226 |  |  |

### Chapter - 8: Result and Discussion

| Chapter - 9: | Conc | lusion                                                      |  |

|--------------|------|-------------------------------------------------------------|--|

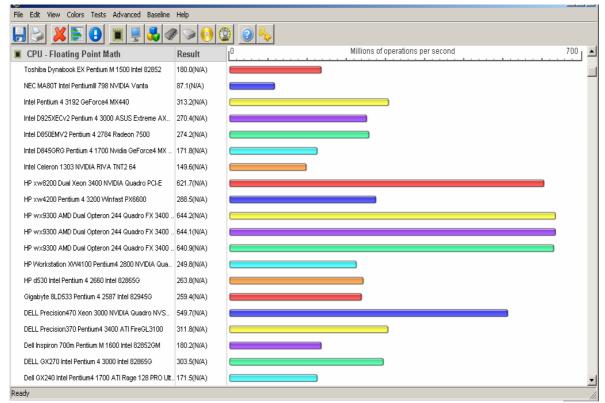

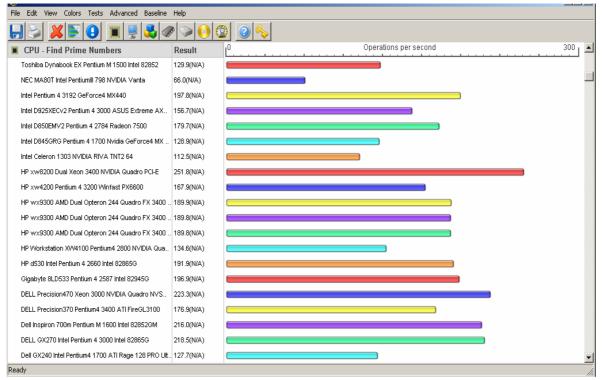

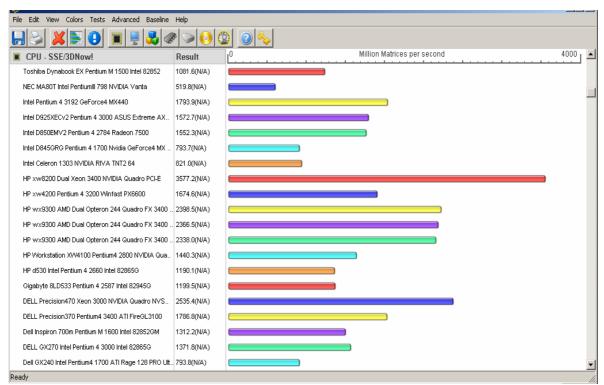

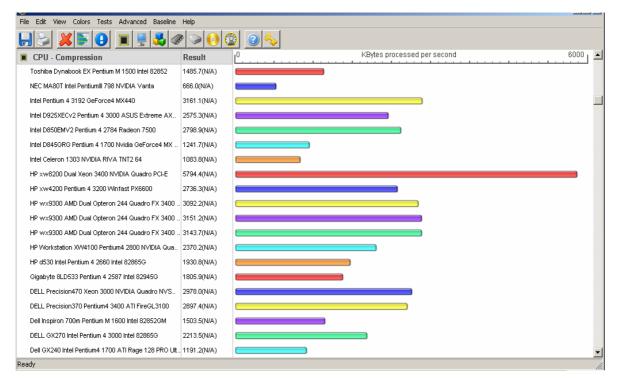

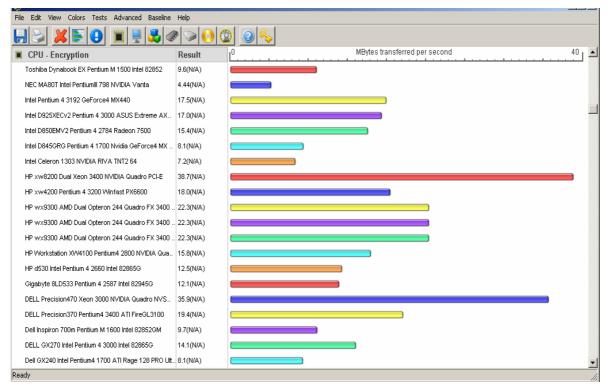

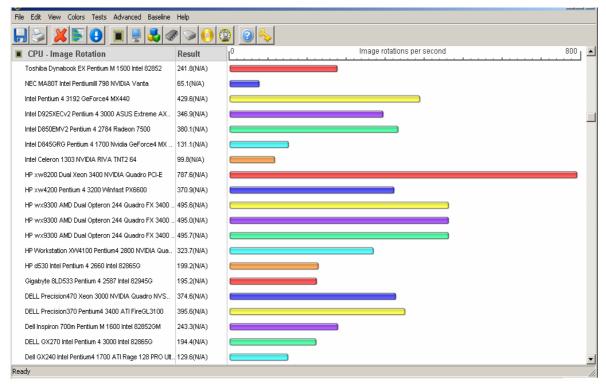

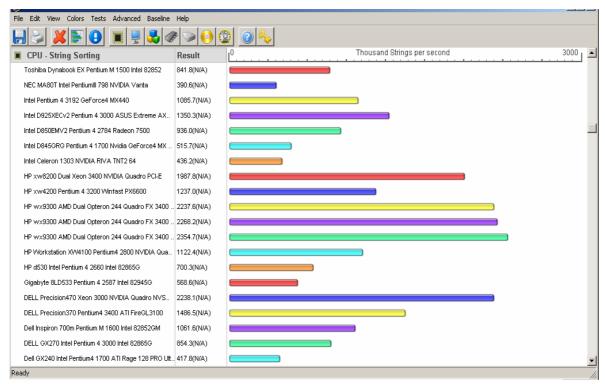

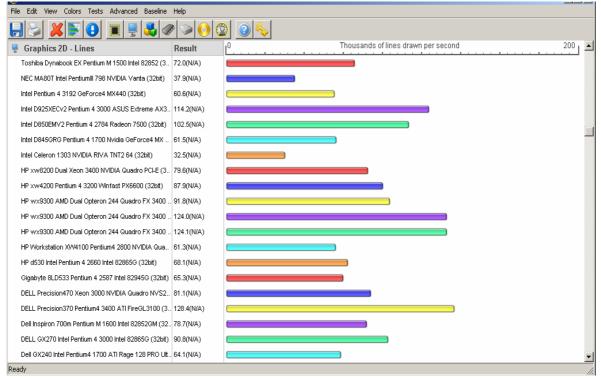

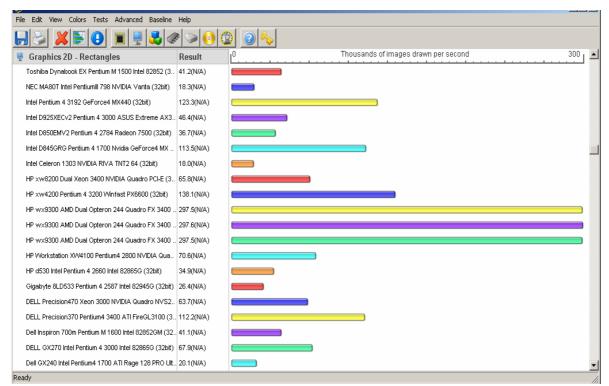

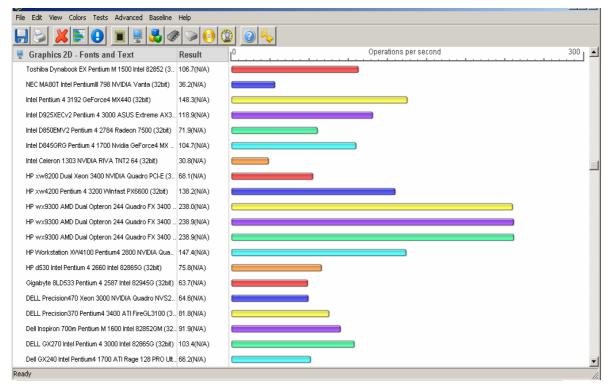

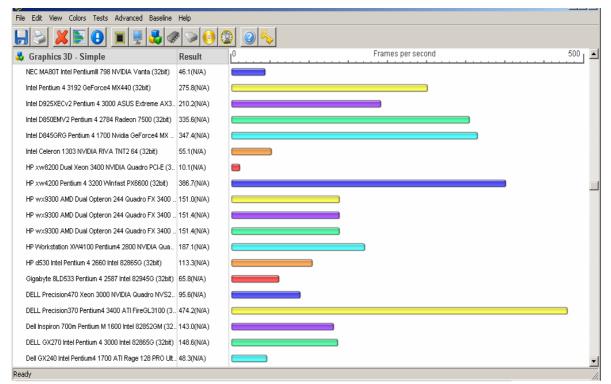

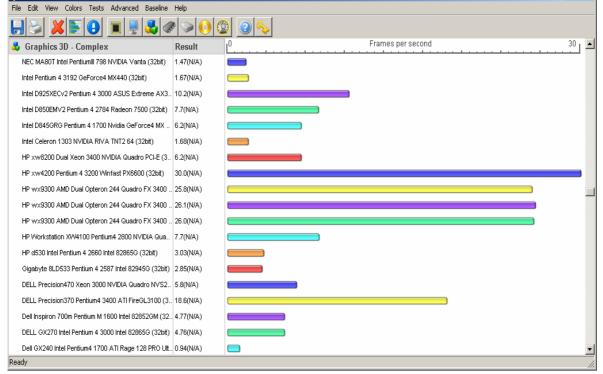

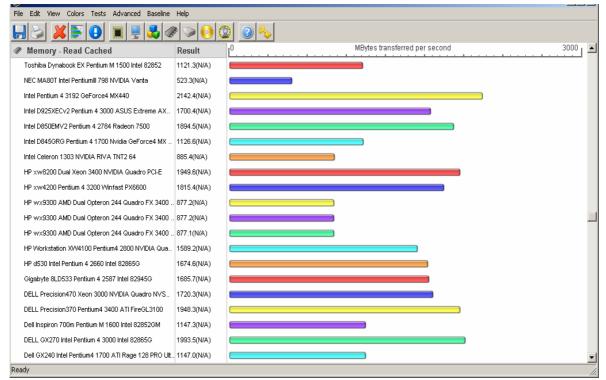

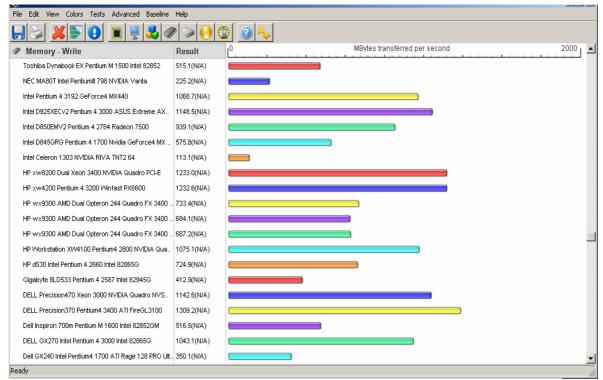

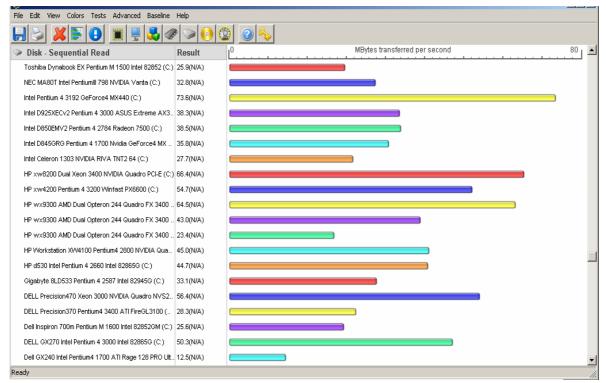

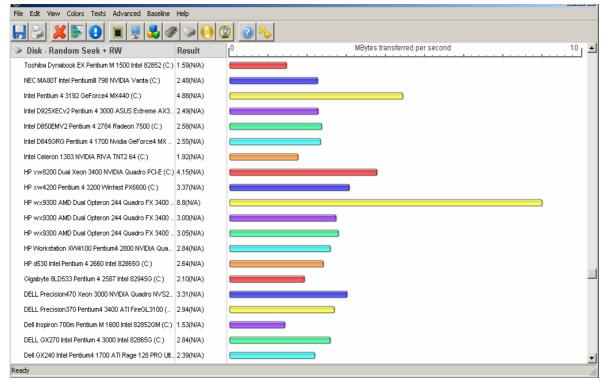

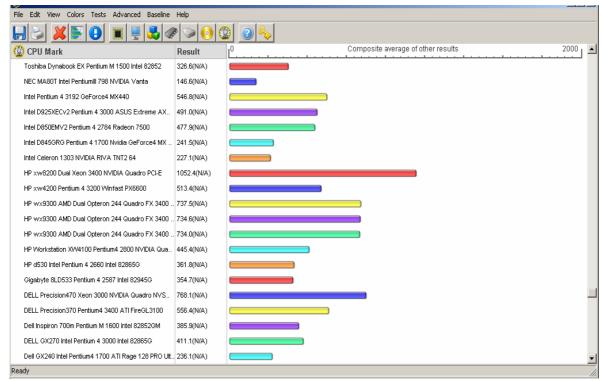

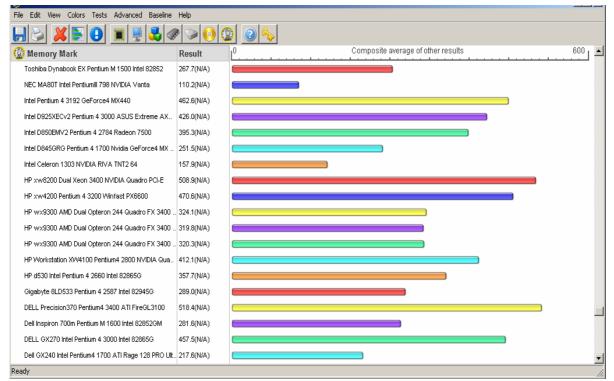

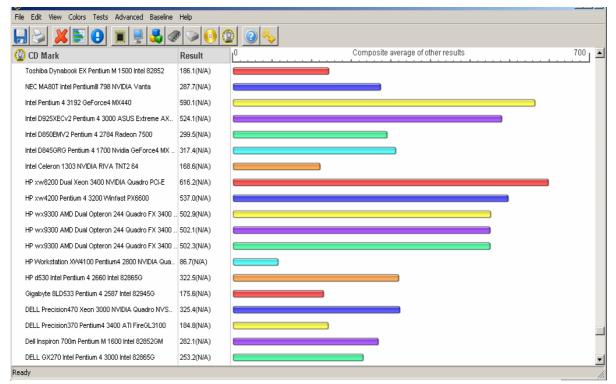

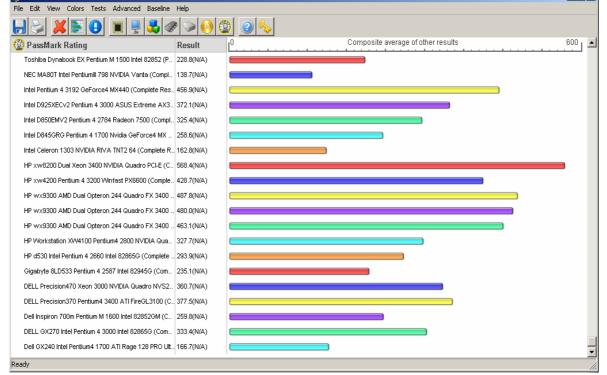

|              | 8.4  | Performance Chart & Comparison of Different<br>Motherboards |  |

|              | 8.3  | Discussion about different test                             |  |

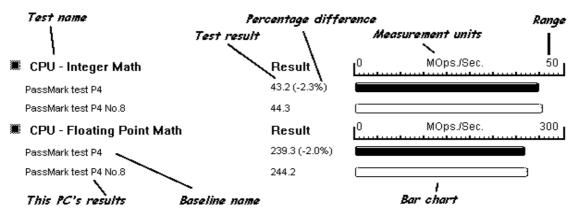

|              | 8.2  | Interpreting the result                                     |  |

|              | 8.1  | Important features of the bench mark software               |  |

# CHAPTER 1 INTRODUCTION

### **1.1 Objective of present work**

At present the society of the whole world is enjoying the fruits of scientific inventions and technological advancement. The very fast growing technology is the computer technology. As in the present age the personal computers and their applications are entering in the routine life, it is quite interesting and inevitable to know and learn about personal computers.

Basically, the essential part of most personal computers is the motherboard. In many PCs the motherboard may be the enter system. The circuitry located on motherboard defines the computer, its capabilities, limitations, and personality. The Motherboard also offers us an excellent introduction to the technologies that underline modern computers. So, we decided to study of various motherboard and basic technology used in earlier motherboards.

Motherboard is the largest circuit board inside the personal computer. A typical motherboard provides attachment points for microprocessors (CPU), memory (RAM & ROM) and various supporting chips for the CPU. To easily extend circuit of the motherboard, it contains many expansion slots on which we can connect smaller circuit boards like, graphic cord, sound card and other application specific cards.

The first product to bear the PC designation was the IBM personal computer introduced in August 1981. The first motherboards to be used in PCs were those of IBM's original personal computer. So we decided to study the earlier motherboards, which gives basic knowledge of different logic blocks. It provided 8 bit XT slots, which always ran at same speed as in XT board CPU support is Intel 8088, Memory support is 640 kilobytes in the form of 16 pin DIP sockets Motherboards varied a lot more from one model to another in those grand old days. The user made heavy use of PC-XT motherboards as personal computer. Of course, the heavy demand for efficient computers gave rise to still advanced microprocessors like 80816, 80286, 80386... up to at present Pentium IV etc. simultaneously supporting motherboards also were designed for CPU.

But to learn basics of motherboard in depth we have decided to use in house facility efficiently and then designed single board based computer. No doubt, with the discrete support circuitry, designing a motherboard was a true engineering challenge becomes it required.

When advanced microprocessor were designed, it required more and more supporting chips, which make motherboard more costly and complicated. As semiconductor firms become more experienced and fabrication technology permitted smaller design rules and denser packaging, however all the diverse support functions inside a motherboard were integrated into few VLSI components individually termed Application specific integrated circuits (ASICs) collectively called a chipset. This integrated approach made the motherboard less expensive. This chipset enhances the performance of advance microprocessor deep understanding of electronic function.

To study various motherboards I took one motherboard from each stage of evolution. Major new features of 286 is ISA Bus, coprocessor interrupt, bi-directional address bus, intelligent keyboard interface, software reset shadow Ram for system BIOS and Video Bios etc.. In 386 features introduced are EISA bus, cache memory, SIMM RAM, MIPS counter etc.. When 486 systems came, a local bus called VESA Bus was introduced to support high-speed transfer to display adaptor. Other than bus it introduced software speed selection, programmable DRAM wait states, PS/2 mouse support and power management. Soon Intel introduced PCI bus, which becomes standard for Pentium systems. Front side Bus has become the system bus due to the dual bus architecture of Pentium pro. And subsequent processors in Pentium family (Pentium IV) have drastically changed the system bus speed to 400 MHz. New version of P-IV offers 533 MHz speed. In practice, many people in this technological field face the fault in motherboards. But it is very difficult to detect the problem and troubleshoot in above motherboards.

Trouble shooting in a motherboard is an intelligent & sophisticated process. To learn trouble shooting in depth, we have selected a trainer, which has discrete support circuitry motherboard (PC-XT motherboards). It gives deep understanding of electronic function of motherboard. To observe various signal status of some important probe sections in motherboard, it provides various points on motherboard. To debug various problems, of motherboards, it consists of various fault analysis test points. Such test points help to troubleshoot motherboard. With the help of above method we can easily get experience to work and prepare our selves to solve problems in advanced motherboards.

Now a day many companies manufacture motherboard like Intel, Mercury, Asus, Gigabyte, etc. Even if though they use the same microprocessor they offer different circuit design. Due to that reason, it gives different performance for same microprocessor (CPU). Mainly this difference is due to different Chipset used in motherboard.

Major motherboard manufacturers design and build motherboard on the basis of requirement of general new product to entice a general user. But they also can manufacture special system for particular use at the lowest possible cost. For that reason we have decided to test various motherboards on fixed platform. To test we have decided used benchmark software and run useful other general soft wares. Fixed platform we have used is as follows.

1) CPU-Intel Pentium IV processor

2) Memory 128MB RAM

3) Hard disk - 40GB Seagate

But, as soon as we have started study it seems to be very interesting for other processors too. So we have also done this benchmark on many different systems and laptop as well.

This study of various motherboards will be helpful to the both the user. This will offer rather detail information on motherboards to the students, teachers and professionals.

### **1.2 Literature survey**

As the subject we have been chosen is very wide. There is no particular book is exactly matches to our research so, we have started getting all information about Microprocessor from 8085 to Pentium. Then studied various applications and advance features of microprocessor. Finally collected and studied books related to circuit designing to implement our ideas into the real format.

After study of all literature we have decided to document all different essential information at one place.

Some of the useful books are listed as follows.

- [1] Microprocessor architecture Programming and applications by R.S.gaonkar

- [2] Microprocessor data handbook, Revised Edition, BPB Publications

- [3] 0000 to 8085 Introduction to microprocessors for engineers and scientists by P.K.Ghosh and P.R.Shridhar, second edition, PHI Publications.

- [4] Printed Circuit Board by Dr. H. N. Pandya, Published by Gujarat Granth Nirman Board, Ahmedabad, India.

- [5] The Indispensable PC Hardware BookBy Hans-Peter Messmer, Third Edition, Eddision Wesley Longman Ltd, England

- [6] All about Motherboard

By Manahar Lotia and Pradeep Nair, Second Revised Edition, BPB Publications, New Delhi, India

- [7] An Introduction to the Intel Family of MicroprocessorsBy James L. Antonakos, Third Edition, Pearson Education, India

- [8] The Pentium ProcessorBy James L. Antonakos, , Pearson Education, India

- [9] Intel Microprocessors 8086/8088, 80186, 80286, 80386, 80486 Pentium, Pentium Pro Processor, Pentium II, Pentium III, and Pentium IV: Architecture, Programming, and Interfacing By Barry B, Brey, Sixth Edition, Pearson Education, India

- [10] Microprocessor and programmed LogicBy Kenneth L. Short, second edition,

- [11] The 80x86 Family: Design, Programming, and Interfacing,By John Uffenbeck, third edition, Pearson Education, India

- [12] PC Quest Magazine October 2004By Cyber Media New DelhiList of few motherboard manufacturers is as follows.

### ABIT Ltd.

Motherboard manufacturer specializing in motherboards for the over clocking and performance market.

### AOpen

A division of Acer corporation that sells primarily to the OEM market. They even make a computer motherboard which has a vacuum tube on it.

### ASUSTek

One of the oldest and most respected motherboard manufacturers on the market.

### Chaintech

Chaintech is one of the newer entries in the US performance motherboard market.

### DFI

Maker of a wide variety of ATX and microATX design PC motherboards.

### **ECS Elite group**

Maker of a wide range of PC motherboards that has recently started selling to the performance market.

### **EPoX** Computer

A relatively new motherboard manufacturer that has many high performance motherboard options.

### FIC Inc.

Manufacturer of a number of different motherboards. Note: This site does not view well outside of Internet Explorer.

### **GigaByte Technology**

Manufacturer of a wide variety of motherboards.

### Intel

The Company most known for its CPUs also develops a line of motherboards based upon its own chipsets and CPUs.

### IWILL

Manufacturer that started out developing SCSI controller cards that has expanded into the PC motherboard market.

### MSI Inc.

Developer of a wide range of well prices motherboards which still contain excellent features.

### **Shuttle Computer Group**

Manufacturer of a wide variety of motherboards including the small form factor X PC line.

### Soltek USA

One of the newest motherboard manufacturers on the market that recently began produce small form factor products.

### **Tyan Computer**

Manufacturer well known for their multiple processor motherboards.

Important web-sites for motherboard manufacturer and microprocessor manufacturers.

| http://www.motherboards.org           | www.intel.com                     |  |

|---------------------------------------|-----------------------------------|--|

| http://www.asus.com/                  | http://www.advantech.com          |  |

| http://www.dell.com/                  | http://www.fica.com/              |  |

| http://www.hp.com/                    | http://www.ibm.com/us/            |  |

| http://www.intel.com/design/motherbd/ | http://www.cpu-world.com/         |  |

| http://www.x86.org                    | http://www.microprocessor.sscc.ru |  |

| http://www.apple.com                  | http://www.2cpu.com/              |  |

# **CHAPTER 2 BASICS OF MOTHERBOARD**

### 2.1 Introduction

PC-XT Motherboard is an old motherboard by today's advance motherboard, but basic functional blocks remain same in even recent motherboards. To understand this functional design we have considered PC-XT motherboard. This chapter describes all functional blocks of PC-XT motherboard.

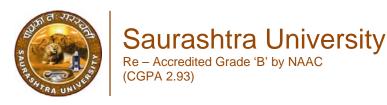

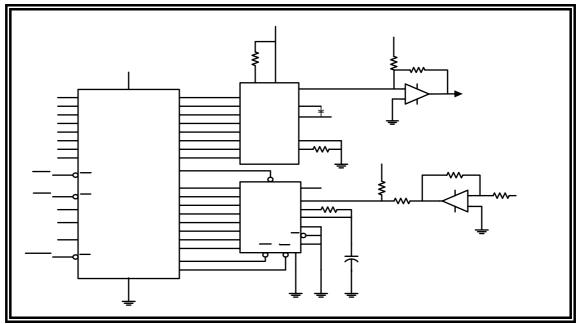

Figure 2.1 Functional block diagram of PC-XT motherboard

Figure 2.1 illustrates functional block diagram of PC-XT motherboard. We divide overall function of motherboard in the following various function.

- Reset Function

- Memory Function

- CPU Function

- Bus Function

- I/O Function

- Interrupt Function

For ease of design the full circuit of motherboard, we focus separate design of functional blocks and logical interconnection of those blocks.

### 2.2 Logic Blocks of motherboard

### 2.2.1 List of logic blocks

To learn functional logic in more details we divide basic function in various functional blocks

- Reset Functional Block

- Memory Function

This logic divided into six internal blocks depends on various memory functions

- RAM functional block

- RAM decode functional block

- RAM parity functional block

- DRAM functional block

- ROM functional block

- ROM logic functional block

- CPU Functional Block

- Co-processor Functional Block

- BUS Function

- BUS arbitration functional block

- Control BUS functional block

- Address BUS functional block

- XT-BUS functional block

- Data BUS functional block

- I/O Function

- I/O codes decode functional block

- Keyboard interface functional block

- Serial Port interface functional block

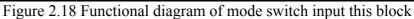

- Mode switch input functional block

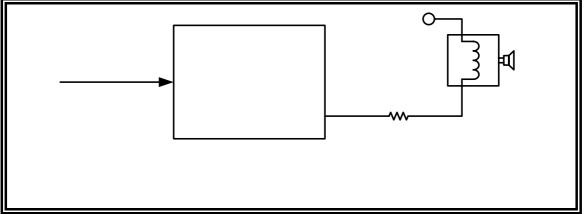

- Speaker functional block

- Time of day functional block

- Interrupt Function

- DMA functional block

- Wait state functional block

- NMI functional block

- Interrupt control functional block

### 2.2.2 Details of logic blocks

Here, I would like to represent above mentioned functional blocks in a sequence.

### **RESET FUNCTIONAL BLOCK**

I would like to begin my explanation of this motherboard with the reset logic block. The reason is, as soon as power to the system is switched on, **reset logic block** is the first logic to be performed. As soon as the Reset signal is generated, all the expansion cards are reset to their initial position.

The reset signal is generated

- When power is switched on to the computer

- When front panel Reset button is pressed

- When Power good signal becomes absent

- When Ctrl, Alt, and Delete keys are pressed simultaneously

### When Power is Switched on to the PC: -

When power to the computer is switched on, the power supply (SMPS) used in the PC generates a Power Good signal for the motherboard.

This Power Good signal is given out by the SMPS only after all the supplies, i.e. Input AC supply and different DC output supplies have stabilized and are within the tolerable limits.

Power Good signal gives the indication to the motherboard that all the supplies are now suitable for use in the system.

Once this initial Power Good signal is received, the Reset Logic Block generates a RESET signal for the CPU. The complete system, including all the daughter cards, is set to initial logic state. This type of resetting is called the Power-Up resetting.

A low going signal is given to the reset pin RES of the clock generator 1C of the motherboard which, in turn, gives resetting signal to the CPU pin no.21.

This resetting signal is also given to the channel 82 of the I/O slots.

When the microprocessor performs the resetting function, all the flags are cleared, all interrupts are disabled, and all registers are emptied. The Power Good signal is typically +5 volts.

### When Reset button is pressed: -

The system can be manually reset to the initial logic state by either pressing the RESET button or by pressing the Ctrl, Alt, and Del keys simultaneously.

When the RESET button is pressed, a low pulse appears at the RES Input of the clock generator pin no. 11, which in turn, gives this information to the CPU.

This makes the complete system to reset to its initial logic state.

This type of resetting is also called Hardware or Manual Resetting.

One of the terminals of Reset switch is connected to the ground, as soon as the front panel reset switch is pressed; it directly connects pin no. 11 of the clock generator with the ground.

When the RESET switch is released the pin no. 11 once again attains high logic state, this generates the required negative pulse at the  $\overline{\text{RES}}$  input of the clock generator.

### When power good signal becomes absent: -

If for any reason, the input AC supply to the SMPS or the output DC supplies given to the motherboard from the SMPS falls low, or becomes too high then the Power good signal becomes low immediately.

A resetting low signal is given to the clock generator, which passes this information to the CPU, and complete system is again reset to its initial logic.

This type of resetting is also called Power-up Resetting.

The system cannot be used until all the supplies have become normal again.

### When Ctrl, Alt, and Delete keys are pressed simultaneously: -

When the Ctrl, Alt and Del keys are pressed simultaneously, Power-On-Self-Test (POST) is executed and system is restarted, but the CPU and the various hardware circuits remain unaffected and are not reset.

This type of resetting is called SOFT RESETTING.

### **RAM FUNCTION:**

I would give next priority to the RAM logic because all the data used by the CPU is first written in the RAM memory and all results are also first given to the RAM.

### RAM FUNCTIONAL BLOCK

ROM logic deals with the different logic blocks of motherboard RAM memory.

RAM logic is very important part of the motherboard as all the data used by the CPU is first written in the RAM memory and all the results are also first given to the RAM. RAM memory on the motherboard is composed of four banks, each containing nine RAM chips.

On a XT motherboard the maximum usable RAM is limited to 640K by the Microsoft DOS environment.

These four memory banks are numbered -Bank O, Bank 1, Bank 2, and Bank 3.

Of these two RAM banks are formed by using the 4164 RAM chips while the other two banks are formed by using the 41256 RAM chips.

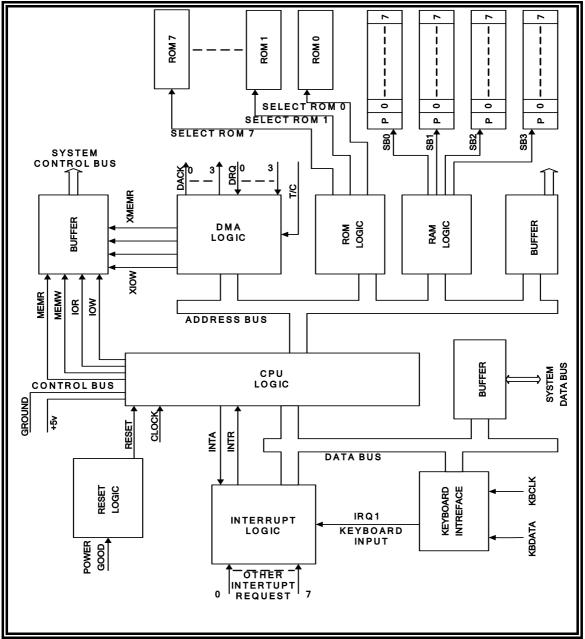

Figure 2.2 Basic RAM function logic

Figure 2.2 shows basic ram function logic. Various types of memory banks used on different versions of 8-Bit motherboards are given below:

- Four banks of 16KB DRAM each total 64KB

- Four banks of 64KB DRAM each total 256KB

- Two banks of 256KB DRAM each, and Two banks of 64KB DRAM each total 640KB

Most of the present 8-Bit motherboards are using either the 256KB or 640KB RAM modules (memory banks).

Selection of the particular RAM bank is done by the RAM Decode Logic Block.

### RAM DECODE FUNCTIONAL BLOCK :

Figure 2.3 Illustrates RAM decode functional block. It is the job of RAM Decode Logic Block to selects the RAM bank containing the memory location corresponding to the 20-Bit address currently on the address bus.

Figure 2.3 RAM decode functional block

Four RAM banks, each containing nine DRAM chips, are generally used on a PC-XT motherboard. All the memory cells in these chips are arranged as rows and columns.

The 20-Bit address to each memory location of the DRAM chips is used for the column address as well as for the row address. Lower Bits of the address represent the row address while higher address Bits represent the column address.

Internal address decoder blocks are built within these memory chips.

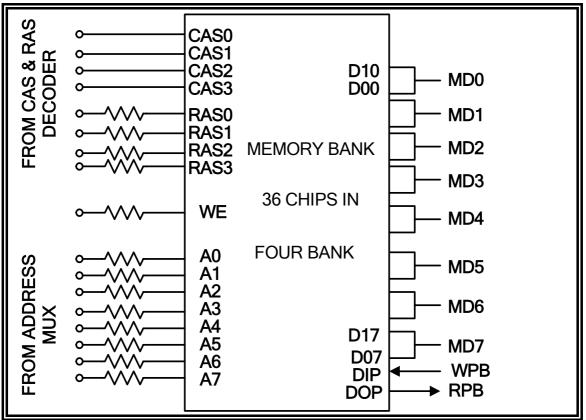

The CAS and RAS decoders and the address multiplexers form the RAM decode logic block.

The Row Address Bits and the Column Address Bits are given to the same input address lines of DRAM chips through an address multiplexer.

A TTL compatible delay line is also formed in the RAM Decoder Logic Block.

To select a particular RAM bank, the  $\overline{\text{MEMW}}$  and  $\overline{\text{MEMR}}$  signals are made low (active) by the control logic block. These are the two inputs to the NAND gate.

$\overline{RAS}$  output of the NAND gate is connected to the input of the delay line and also to one of the inputs of the  $\overline{CAS}$  and  $\overline{RAS}$  decoders.

Second input to the decoders i.e.  $\overline{CAS}$  is given from one of the two outputs of the delay line.

When the MEMW and MEMR signals go low, the RAS input terminal of the decoders goes high.

Now  $\overline{RASO}$ ,  $\overline{RAS1}$ ,  $\overline{RAS2}$ , and  $\overline{RAS3}$  outputs of the decoders, which are connected with the  $\overline{RASO}$ ,  $\overline{RAS1}$ ,  $\overline{RAS2}$ , and  $\overline{RAS3}$  input terminals of the DRAMs are made active low.

During this time, the  $\overline{CASO}$ ,  $\overline{CAS1}$ ,  $\overline{CAS2}$ , and  $\overline{CAS3}$  outputs of the decoders remain high. These outputs are connected with the  $\overline{CASO}$ ,  $\overline{CAS1}$ ,  $\overline{CAS2}$ , and  $\overline{CAS3}$  input terminals of the DRAM chips.

Next, the ADDR SEL output signal of the delay line is made low. This is connected to ADDR SEL input terminal of the address multiplexer.

Address Bits XAO to XA15 are already present at the input address lines of this multiplexer. As the  $\overline{\text{ADD SEL}}$  terminal of this multiplexer is low, it loads the row address Bits on the address input lines of the DRAM chips.

This row address is kept latched in the DRAM chips for as long as necessary. Now, the  $\overline{RAS}$  input to the decoders is made low.

$\overline{CAS}$  input to the decoders is made high by the delay line and the  $\overline{CASO}$ ,  $\overline{CAS1}$ ,  $\overline{CAS2}$ , and  $\overline{CAS3}$  input terminals to the DRAM chips go low while the  $\overline{RASO}$ ,  $\overline{RAS1}$ ,  $\overline{RAS2}$ , and  $\overline{RAS3}$  terminals are made high.

The ADD SEL terminal of the address multiplexer is made high.

Now, the column address Bits get loaded in the DRAMs and the desired memory location is selected.

Since the RAM banks are on the MAO-MA7 line, all the address Bits are loaded on this bus.

### DRAM REFRESH FUNCTIONAL BLOCK:

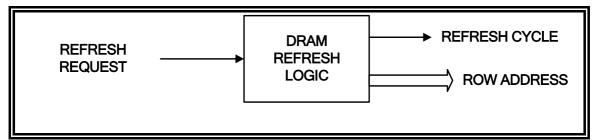

Figure 2.4 Functional block to refresh DRAM Dynamic Memory

Figure 2.4 is functional block to refresh DRAM Dynamic Memory (DRAM). Two basic types of RAM chips used with the motherboard are

- SRAM (Static RAM) and

- DRAM (Dynamic RAM).

Cell of the DRAM memory chip is formed of a single capacitive cell (capacitor). The two logic states of this cell are "charged" (logic- 1), and "discharged" (logic-0).

The capacitors lose its stored charge due to its internal leakage through the dielectric over some time. Thus, if this capacitor is not recharged periodically, the data stored in it will get lost.

This periodical refreshing of DRAM memory is done by the memory refreshing pulse. This refreshing pulse is required every 15 microseconds.

### **ROM FUNCTIONAL BLOCK**

When the power is switched on to the computer system, the Reset Logic becomes active.

Once the system is initialized by the RESET operation, the ROM and RAM logic take over the subsequent actions.

The ROM holds all the instructions necessary for proper startup of the system and to makes it ready for use.

After the RESET operation, the CPU reads the instructions stored in the ROM chips.

The initial instructions stored in the ROM chip immediately perform the Power-On-Self-Test (POST) and initializes all motherboard logic.

Next function performed by the instructions stored in the ROM is to copy the DOS (Disk Operating System) program from the floppy disk or the hard disk into the RAM memory of the motherboard.

DOS must be loaded into the RAM every time the system is powered-on.

This operation is commonly referred to as BOOTING of the system.

The Basic Input/Output System (BIOS) program also remains stored in ROM chips. All the devices interfaced in the system are recognized, sensed, or identified by the CPU using these ROM-BIOS instructions.

Some motherboards also contain an additional ROM chips with a program called the BASIC Interpreter. An interpreter translates the instructions of a high level language into codes, which are executable by the machine.

BASIC (Beginners All Purpose Symbolic Instruction Code) is a high level language, which is not much in use nowadays. Hence, it is not essential that the motherboard contain this interpreter.

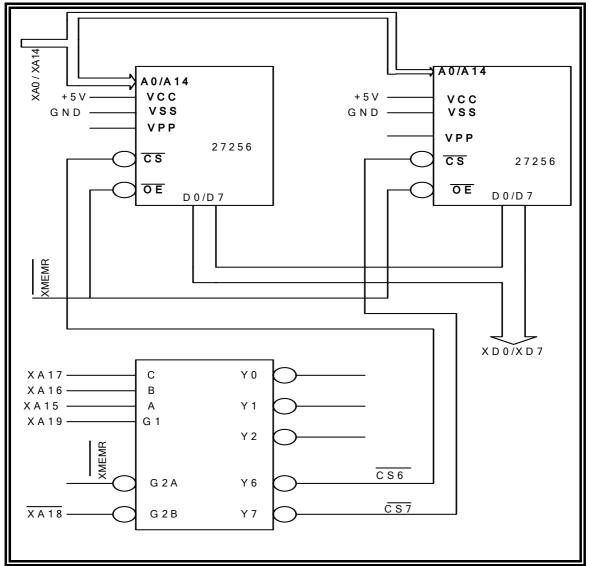

Figure 2.5 Functional block of ROM LOGIC BLOCK

Figure 2.5 shows Functional block of ROM logic block. Some of the popularly used ROM chips on the motherboard of a personal computer are - 2764, 27128, and 27256. All of these ROM chips are 28 pin chips requiring an operating supply voltage of +5 volts.

The ROM memory capacity for a PC motherboard should ideally be 64KB. But even 40KB ROM space is sufficient for executing most of the essential POST, BIOS, and the BASIC interpreter routines.

Even 8KB ROM space is sufficient to hold the POST and the BIOS routines.

Sometimes the Programmable ROM (PROM) 27128 is used on PC motherboards offering a choice of two BIOS options. A DIP switch connected on the motherboard is used for making the selection between these two versions of the BIOS.

No Refreshing Pulses are required in the ROM decode logic since ROM does not lost its content with time, ROM is a Nonvolatile Memory.

Selection of the particular ROM chip from the various chips used on the motherboard is made by the ROM Decode Logic Block.

Many sockets are provided for installing ROM chips on the PC-XT motherboards. ROM Decode Logic Block selects the required ROM chip on the basis of the ROM memory location which is to be read.

### **ROM DECODE FUNCTIONAL BLOCK**

Many ROM chips are used on the motherboard. Data is stored in the numerous memory locations of these ROM chips.

Whenever the CPU executes a program, the memory location containing the relevant data must be accessed.

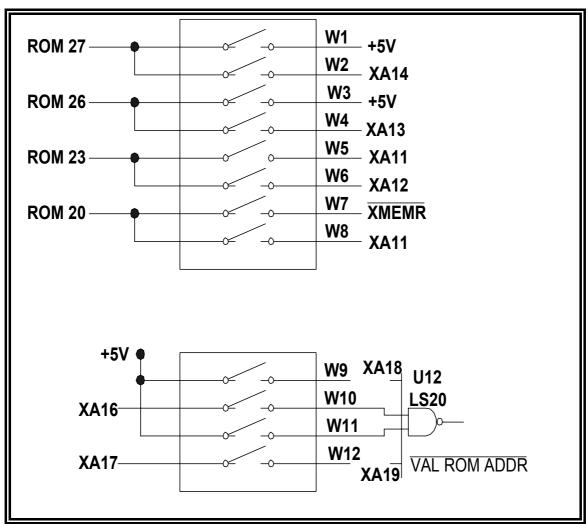

Figure 2.6 Functional block of ROM DECODE LOGIC BLOCK

Figure 2.6 shows Functional block of ROM DECODE LOGIC BLOCK. The ROM Decoder Logic Block performs the task of selecting the particular ROM chip that holds the requisite memory location.

This ROM Decode Logic Block generates ROM Chip Selection control signal.

ROM decoder 1C (1C LS138/U23), used in the ROM Decode Logic Block, is also installed either on the motherboard directly or in a socket provided for it on the motherboard. When some ROM chip is to be selected then this ROM Decode Logic checks the four Most Significant Bits (MSBs) of the 20 address Bits on the address bus and selects the particular ROM chip containing this address.

The ROM logic then generates the appropriate Chip Select signals. Thus, the ROM chip containing the required memory location gets selected.

Different types of ROM chips are used as per the motherboard configuration. Hence, correct jumper settings should be made to match the ROM type so that the ROM Decoder Logic Block generates correct ROM Chip Select signals.

Sometimes the ROM decoder chips are mounted on the motherboard in different positions marked as A, B, and C on the motherboard.

### **CPU FUNCTIONAL BLOCK**

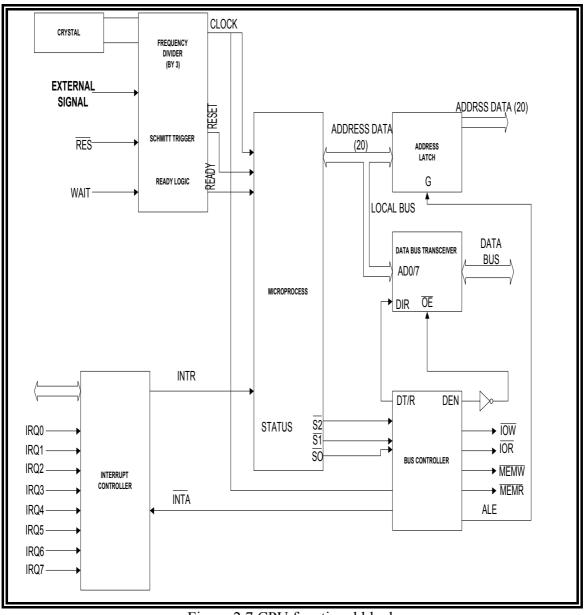

Figure 2.7 illustrates CPU functional block. This is the largest logic block on the motherboard. All major operations related to the CPU are carried out in this logic block.

The operations related to the various support chips on the motherboard are also included in the CPU logic block.

### **CO-PROCESSOR FUNCTIONAL BLOCK**

This optional logic block is installed on the motherboard to increase the efficiency of the CPU. Coprocessor Chip 8087 is used in this logic block. Important operations of this block are

- Execution of Floating Point Instructions

- Assisting the CPU in execution of the instructions of the main program

- Maintaining a parallel instruction queue for the CPU

## Figure 2.7 CPU functional block **DMA FUNCTIONAL BLOCK:**

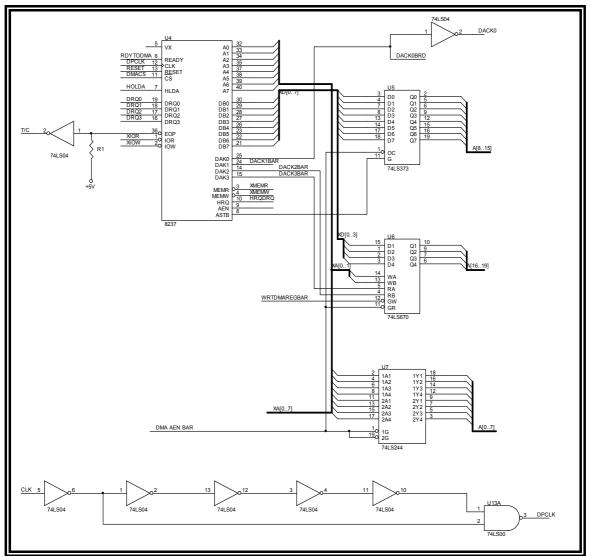

As shown in the figure 2.8 DMA functional blocks. The DMA (Direct Memory Access) Logic block includes the operations of the DMA controller and its supporting chips.

This block performs the function of managing data transfer between the various I/O controllers, Floppy Disc, Hard Disk, and the Memory devices.

It receives the data transfer requests from these devices and generates bus control request to the Bus Arbitration Logic (BAL) block. The BAL block is discussed later in this section.

DMA logic block includes the DMA Controller, Address Buffer, and Address Latch. Various channels formed in the DMA controller are

- Channel O, Channel 1, Channel 2, and Channel 3.

- Channel O: "Dynamic memory refresh cycle": No data transfer takes place in this channel and only the address Bits and control signals are provided on this channel.

Figure 2.8 DMA functional block

- Channel 1: Not used

- Channel 2: Data is transferred between the floppy drives.

- Channel 3: Data is transferred between the hard disk drives on this channel.

DMA controller which is a 16-Bit chip, is capable of transferring 64KB of data in one I/O cycle.

DMA logic continuously checks the DREQ (DRQ) line during every clock cycle (when it is idle). In this condition, the DMA controller also checks the Chip Select signal to determine whether the CPU wants to access its internal registers or not.

When the DREQ signal is sensed active, the DMA logic block generates Hold Requests (HRQ) for the CPU.

DMA logic now manages the data transfer upon receiving an acceptance from the CPU in the form of corresponding HLDA signal.

Data is transferred by the DMA logic block in four manners:

**Single transfer:** Only a single byte of data is transferred and soon afterwards the bus control is returned to the CPU.

If another byte has to be transferred then a fresh HRQ must be made and DMA has to wait for the corresponding HLDA signal.

**Block Transfer:** The DMA returns the control of the bus to the CPU only after complete data transfer has taken place.

**Demand Transfer:** DMA continues to manage the data transfer for as long as the requesting I/O device maintains the DREQ request active.

As soon as the DREQ is removed, DMA transfers the bus control back to the CPU.

**Cascade Transfer:** In case, when more than four DMA channels are required on the motherboard, this cascade mode can be used to install more than one DMA controllers in the DMA logic.

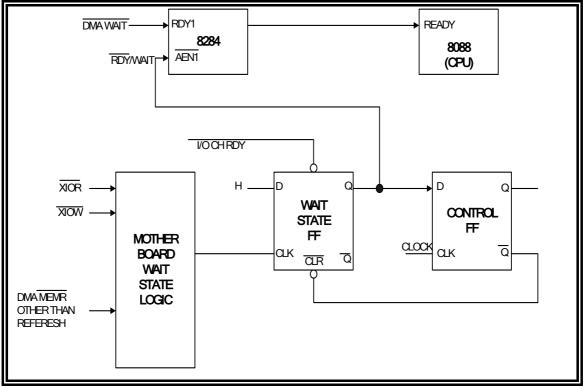

### WAIT STATE FUNCTIONAL BLOCK

Figure 2.9 illustrates the wait state function for CPU and DMA controller. Other than the CPU and the DMA controller, the memory and various interfacing peripheral devices also require use of the system bus.

This Wait State Logic block generates the different Wait State signals for the CPU and the DMA controller. When the CPU or the DMA controller receives these Wait State signals, the system bus gets transferred to some other device.

For example, when the Hard Disc controller generates the DRQ3 signal to the DMA controller then the Wait State Logic (WSL) block senses this signal and sends a Wait signal to the CPU.

Now, the control of the system bus is transferred to the requesting device i.e. to the Hard Disk Controller.

On the other hand, if the CPU has to use the system bus then the WSL block gives the Wait signal to the DMA controller.

Figure 2.9 Wait state function for CPU and DMA controller

The WSL block receives five signals and generates two Wait State signals. The incoming signals are  $\overline{\text{DMA WAIT}}$ ,  $\overline{\text{XIOR}}$ ,  $\overline{\text{XIOW}}$ ,  $\overline{\text{XMEMR}}$ , and I/O CH READY. The DMA WAIT signal is generated from the Bus Arbitration Logic (BAL) block

while the XIOR, XIOW, and XMEMR signals are received from the Control Bus Logic block.

The only signal which is received from the external memory device, or interfacing device installed in the I/O slots (channel A10) is the I/O CH RDY.

$\overline{\text{XIOR}}$ ,  $\overline{\text{XIOW}}$ , and  $\overline{\text{XMEMR}}$  are the control signals generated either by the DMA controller or by the bus controller. Prefix "X" indicates that these signals are buffered. The two output signals generated by Wait State Logic block are  $\overline{\text{RDY}}$ /WAIT, and READY To DMA.

These signals cause a Wait State in the CPU or the DMA controller respectively.

When the DMA WAIT, connected to the input RDY1 of the clock generator, is made low then the clock generator ensures that the READY input of the microprocessor is also made low.

This makes the microprocessor enters the Wait State.

Similarly, when the  $\overline{\text{RDY}}/\text{WAIT}$  signal at the  $\overline{\text{AEN1}}$  input of the clock generator is made high then also the CPU enters the wait state.

The DMA WAIT signal is directly given to the RDY1 input of the clock generator from the BAL block.

A low DMA WAIT transfers the bus to the DMA Controller and the CPU is kept in the wait state until the DMA controller release the control of the bus.

RDY/WAIT signal is made high when any one of the input signals - I/O CH RDY,  $\overline{\text{XIOR}}$ ,  $\overline{\text{XIOW}}$ , or  $\overline{\text{XMEMR}}$ , goes low.

When anyone of these signals goes low, the flip-flop in WSL block is set and output Q i.e.  $\overline{\text{RDY}}/\text{WAIT}$  of this flip-flop goes high.

This flip-flop is controlled by yet another flip-flop, called the Control flip-flop. When the main flip-flop is set then the control flip-flop resets the main flip-flop after one clock cycle and the CPU comes out of the Wait State.

The I/O CH RDY input is received from the expansion cords. If this signal is low for more than one clock cycle, the main flip-flop continues to be in the set state until the I/O CH RDY signal is made high again.

The control flip-flop resets the WS flip-flop at the end of the clock cycle.

The  $\overline{Q}$  outputs of both flip-flops are used for generating the READY To DMA signal. This signal is connected to the READY input of the DMA controller.

A low READY To DMA signal introduces wait state in the DMA controller for one clock cycle.

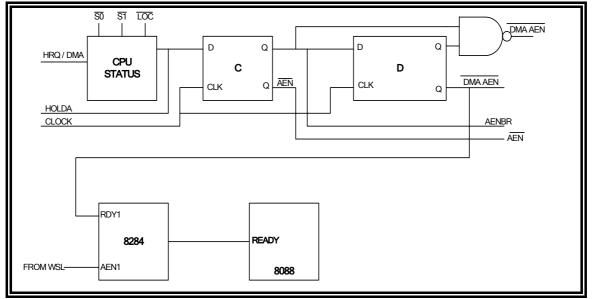

### **BUS ARBITRATION FUNCTIONAL BLOCK:**

Figure 2.10 Bus arbitrations functional block

Figure 2.10 illustrates bus arbitrations functional block. The Bus Arbitration Logic block manages the system bus. This block decides when the CPU should be given control of the bus and when the DMA controller should use the bus.

All the memory devices and the I/O devices generate their respective bus requests in the form of DRQ signals.

The DMA controller receives these bus request signals. As soon as the DMA controller receives any DRQ signal, it immediately generates a HRQ DMA signal for the BAL block.

Figure 2.11 Bus arbitration functional block with wait state

Figure 2.11 shows the functional block diagram of bus arbitration block with wait state functional block. The BAL block continuously monitors the conditions under which the system bus is being used by the CPU through the  $\overline{SO}$  and  $\overline{S1}$  status signals it receives from the microprocessor.

In case, the CPU is actively using the bus and does not want the bus to be transferred to any other device, it pulls the  $\overline{\text{LOCK}}$  signal to low state. This signal is also monitored by the BAL block.

When the BAL block detects that the microprocessor has free bus cycles, it generates HOLDA (HOLD Acknowledgment) signal to inform the DMA controller that its HRQ DMA signal has been acknowledged.

Now the BAL block drives the DMA WAIT signal low. This ensures that the CPU remains in the wait state while the DMA controller is using the bus.

BAL block also makes the AEN BRD signal high in response to a low  $\overline{\text{AEN}}$  signal. These two signals are given to the  $\overline{\text{AEN}}$  and CEN Inputs of the bus controller respectively.

This disables outputs of the bus controller. In this manner, the BAL ensures that no control signals from the bus controller reach the control bus while the DMA controller is using the bus.

The address bus is divided in two groups on the motherboard. One of these, the 4 I/O Slot address bus (A bus) is used with the expansion cards installed in the I/O slots. Second is the System Address Bus (XA bus) which is used for transferring the 1 address Bits between the various logic blocks of the motherboard.

When the DMA controller is using the bus, it becomes necessary to isolate the XA bus from the CPU.

To achieve this, the BAL block generates a high AEN BRD signal to the bus  $\$  address logic block. But if the CPU is using the bus and DMA controller is in the wait state, the BAL block generates a low  $\overline{\text{DMA AEN}}$  signal to the address bus logic block. This isolates the A bus from the DMA controller.

In a similar manner, when the bus is in use by the DMA controller, a high AEN BRD signal is generated from the BAL block to the control bus logic block. This isolates the data bus from the CPU. Thus, all the three buses are isolated from the CPU while the DMA controller is in control of the bus.

These buses are isolated from the DMA controller during the time when CPU is using these. The control of the system bus remains with the DMA controller for as long as the HRQ DMA signal remains active.

When the DMA controller has no more requests for the bus from the memory devices or I/O devices, it deactivates the HRQ DMA line. The BAL block reverts all signals to the previous state and transfers the bus to the CPU.

The BAL block receives DACKO BRD signal whenever a memory refresh cycle is to be completed. The BAL, block disables the wait state during this period because if the memory were not refreshed, all data would be lost.

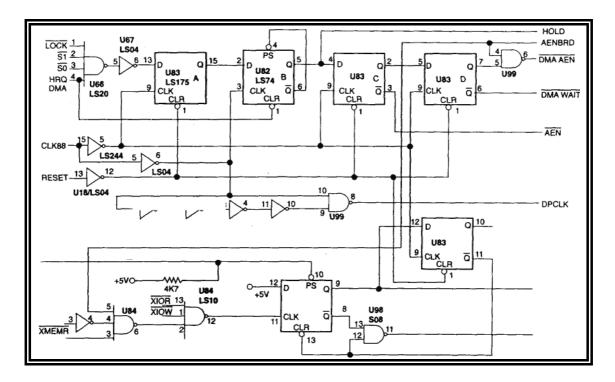

### **CONTROL BUS FUNCTIONAL BLOCK**

Figure 2.12 Functional block of control bus

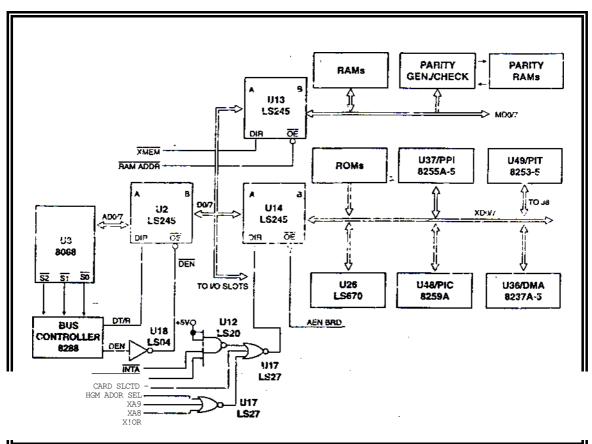

Figure 2.12 illustrate functional block of control bus. This control bus logic block generates control signals required for interfacing various peripheral devices installed at the I/O ports, memory devices and different supporting chips with the microprocessor.

This logic block includes the bus controller chip, clock generator, and the DMA controller for generating the necessary control signals.

The Control Bus Logic block may be divided in following subgroups:

- Control Signal Logic Block, and

- Bus Command Logic Block

The control signal logic block manages or controls the data and address bus connected with the microprocessor by generating the DTR,  $\overline{\text{DEN}}$ , and ALE signals.

When the DTR goes high then data flows from the CPU towards the interfaced device but when this signal is low then the flow of data is reversed and data is transferred from the external device towards the CPU. When the DEN is goes high then the data bus transceiver, which is used as a buffer between the Bus controller and the DMA controller, gets activated. But when the DEN signal goes low then this buffer, becomes disabled.

The transceiver, when enabled, passes the control signals generated by the bus controller or the DMA controller to the I/O slots from one side and also to the various logic blocks of the motherboard from its other side.

Bus Command Logic block generates the MEMW, MEMR, IOW, IOR, and INTA control bus signals. These four bus control signals are buffered by the transceiver and given to the I/O slots from its one side and to the various motherboard logic blocks from its other side.

Transceiver LS245 is used on PC-XT motherboard to perform this function.

Its pin DIR is used to select the control signals generated by the bus controller or by the DMA controller.

When the input signal (DMA AEN) is high, the transceiver selects the control signals generated by the bus controller. When this input is low, the control signals generated by the DMA controller are selected by the transceiver.

Control signals are generated from bus command logic block which are used to bring the CPU in a wait state.

The CPU bus status is recognized by this bus command logic block according to the status of  $\overline{SO}$ ,  $\overline{S1}$ , and  $\overline{S2}$ .

When the status signals  $\overline{SO}$  and  $\overline{SI}$  are high while  $\overline{S2}$  is low, microprocessor enters the wait state but when  $\overline{SO}$ ,  $\overline{S1}$ , and  $\overline{S2}$  are all high, it indicates the end of bus cycle will follow.

These status signals are generated from the microprocessor.

When the bus is being used by the microprocessor, the different control signals are generated by the bus controller, not by the DMA controller.

Other than the four control signals generated from the Control Bus Logic block, three other signals - AEN BRD, AEN, and DMA AEN, also arrive in this logic block from the bus arbitration logic group.

These signals are generally referred to as supervisory signals.

When the CPU is using the bus, the AEN BRD signal goes low while the  $\overline{\text{AEN}}$  and  $\overline{\text{DMA AEN}}$  signals become high. The low AEN BRD signal and high  $\overline{\text{AEN}}$  signal enable the bus controller.

When the bus is with the DMA controller the  $\overline{\text{AEN}}$  signal becomes low while the  $\overline{\text{AEN} \text{ BRD}}$  signal goes high. This disables the bus controller. At the same time,  $\overline{\text{DMA} \text{ AEN}}$  signal becomes low and the transceiver selects the control signals generated by the DMA controller

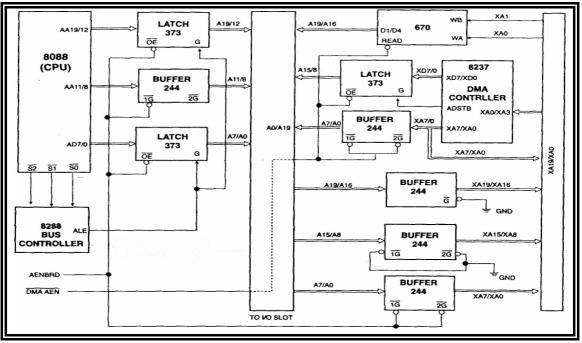

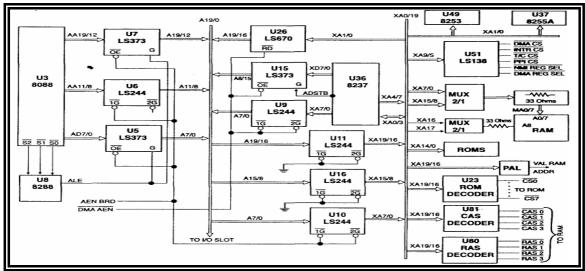

Figure 2.13 (A) Address Bus Functional Block

Figure 2.13 (B) XA Bus Logic Address Bus Distribution

Fig. 2.13 illustrates address bus functional block. Address bus of the motherboard is formed either by the CPU logic block or by the DMA logic block. This is a 20-Bit bus

and it is used for transferring the address Bits between the various logic blocks and the I/O slots.

The address bus is used on the motherboard as

- I/O Slot Address Bus A-Bus

- XABus

A-Bus transfers the address Bits between the I/O slots and the various logic blocks of the motherboard.

On the other hand, the XA bus transfers the address Bits amongst the different logic blocks of the motherboard. Thus, the XA bus does not interact with the devices interfaced at the I/O slots.

All the 20 address lines of the address bus i.e. AO-A19 or XAO-XA19 are routed through latch ICs or buffer ICs.

This process is essential in the motherboard circuitry because when the bus control is with the DMA controller, the address bits of the CPU must be prevented from reaching the A-Bus. Also, when the CPU is using the bus, the address Bits of the DMA controller must not reach the A-Bus.

The AEN BRD and the  $\overline{\text{DMA AEN}}$  signals received from the buffer, BAL block control these buffers and latches.

The 20-Bits of the A-bus from the CPU are grouped as ADO-AD7, AA8-AA11, and AA12-AA19. Latch ICs are used for the Bits ADO-AD7 and AA12-AA19. A Buffer 1C is used for the Bits AA8-AA11.

The Bits AA8-AA11 are not latched but only d or tri-stated while the remaining 16-Bits are routed through the latch ICs.

When the bus control is with the DMA controller, the AEN BRD signal connected to the tri-state logic control terminal  $\overline{OE}$  of these latch ICs is made high by the BAL block.

Now the address Bits ADO-AD7 and AA12-AA19 remain latched as these are not available at the output, i.e. the outputs of the latches are neither low nor high.

This undetermined state of the outputs is normally known as "Tri-State".

Terminal G of the latch IC is given ALE signal from the bus controller logic group.

| OE   | G           | Input          | Output    |

|------|-------------|----------------|-----------|

| High | Ineffective | Tri-stated Low | -         |

| Low  | Low         | Ineffective    | No change |

| Low  | High        | Low            | Low       |

| Low  | High        | High           | High      |

When the AEN BRD signal is high, output will always be tri-stated and the address Bits at the input will be isolated From the A bus. Any change can be made in the output only when AEN BRD signal is made low, and the ALE signal is high. When AEN BRD is low i.e. when CPU is using the bus, and ALE is also low, the address Bit, which is already present at the output, will continue to stay there and it will not change in state even if the CPU changes the address Bit at the corresponding input.