Saurashtra University Re – Accredited Grade 'B' by NAAC (CGPA 2.93)

Vyas, Darshan G., 2005, "Design and fabrication of general purpose 8085 card and develop various interfacing cards useful in education of electronics", thesis PhD, Saurashtra University

http://etheses.saurashtrauniversity.edu/id/eprint/347

Copyright and moral rights for this thesis are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the Author.

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the Author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

Saurashtra University Theses Service http://etheses.saurashtrauniversity.edu repository@sauuni.ernet.in

© The Author

## DESIGN AND FABRICATION OF GENERAL PURPOSE 8085 CARD AND DEVELOP VARIOUS INTERFACING CARDS USEFUL IN EDUCATION OF ELECTRONICS.

*Thesis* Submitted to the Saurashtra University, Rajkot For The Degree of Doctor of Philosophy (Science) (Electronics)

## By

Darshan G. Vyas Lecturer in Physics, Hemchandracharya North Gujarat University, Patan-384265(North Gujarat)

## **Research Supervisor**

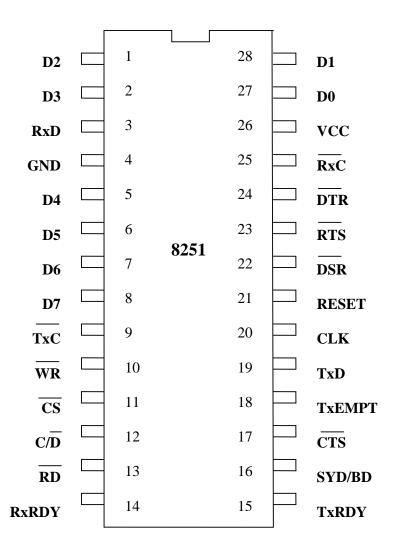

Dr. H. N. Pandya Associate Professor, Department of Electronics / Physics Saurashtra University, Rajkot-360005 India

April 2005

Affectionately dedicated to My parents Retd. Prof. G. P. Vyas & Mrs. Hansaben G. Vyas and my younger brother Dhaval G. vyas

# Statement under O.Ph.D. of Saurashtra University

The content of this thesis is my own work carried out under the supervision of Dr. H. N. Pandya and leads to some contribution in Electronics supported by necessary references.

(D.G.Vyas)

This is to certify that the present work submitted by Mr. Darshan G. Vyas for the Ph.D. degree of Saurashtra University, Rajkot has been the result of about 5 years of work under my supervision and is a valuable contribution in the field of Electronics.

Dr. H. N. Pandya, Associate Professor, Department of Electronics / Physics, Saurashtra University, Rajkot- 360 005

#### **Acknowledgement**

It is impossible to express words of thanks for my 'GURU' Dr.H.N.Pandya, but I am trying to express my sincere thanks to him. The name of Ph.D. student is bound with the name of his guide for lifetime, and it is impossible to obtain this most valuable degree without the proper guidance. Dr.H.N.Pandya helped me everywhere. He not only solved my technical problems but also helped me in the development of my educational carrier. For me and my family this name is unforgettable.

I am highly indebted to my parents Retd. Prof.Ghanshyambhai P.Vyas and Mrs. Hansaben G. Vyas who have brought up me with immense love and helped me to get education to this stage. Their loving care and all time worries have been a main source of my inspiration. My younger brother Dhaval Vyas also boosted my morals and helped me at every stage of this work. During my stay in Rajkot and crucial working hours my friend like elder brother Mr. Jitubhai Vyas has played a key role in helping me and maintain my time schedule by adjusting his work schedule.

In the early stage of my research work the engineer Mr. Maheshbhai Bhatt (Physics Department, Gujarat University, A'bad) has been kind enough in clearing my some of the basic doubts.

I am also thankful to Prof. B.J.Mehta, Prof. N.N.Jani for giving me moral support. I feel happy to say that I got chance to work in the company of Dr.M.N.Jivani and Dr.N.A.Shah.

The moral support and affectionate concern of Mrs. Kiranben H. Pandya in the critical moments of my research work and during my disappointments have soothed my soul and made me to resume my work with eternal enthusiasm.

I am thankful to my colleague Ph.D. students Mr. Bimal Vyas and Mr. Maulin Nanavati for helping me at various stages of my research work. I wish to express my loving thanks to my friends Mr. Manishbhai Pandya and Mr. Taresh Bhatt for sharing all good and "stressed" moment of my work. The help extended by Mr. Bhaskar Anand and Harshad Chirutkar is also appreciated.

I am also thankful to Mr. Pareshbhai M. Patel, Lab. Technician, Physics Department, Hem. N. G. University, Patan for helping me in printing and binding of my thesis. I am also thankful to our respectable Prof. K.N.Patel, Coordinator Physics, Hem. N.G.University, Patan for boosting my enthusiasm.

I am highly thankful to my all professors of Gujarat University, A'bad, for giving me a knowledge and information about the subject.

I am thankful and humbly appreciate the technical help of N.K.Modi and C.K.Panchal, P.R.L., A'bad,

Finally I am thankful to "GOD" and my all well wishers.

## Contents

| Chapter-1 | : | SECTION-IBASIC 8085 CARDIntroduction1.1Objective of the present work1.2Literature survey                                                                         |

|-----------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter-2 | : | Basic understanding of 808505Microprocessor2.12.1The block diagram2.2Interrupts2.3Serial communication                                                           |

| Chapter-3 | : | Instruction set143.1Addressing modes3.2Instruction format3.3All instructions                                                                                     |

| Chapter-4 | : | Interfacing of EPROM and RAM264.1EPROM 2764A4.2Static RAM 62644.3Memory map                                                                                      |

| Chapter-5 | : | I/O interfacing355.1Programmable keyboard display Interface<br>82795.2Programmable peripheral interface 8255                                                     |

| Chapter-6 | : | P.C.B. designing and fabrication706.1Schematic preparation6.2P.C.B. layout preparation6.3P.C.B. fabrication6.4General aspects6.4.1List of components6.4.2costing |

| Chapter-7 | : | Monitor program 79                                                                                                                                               |

| Chapter-8 | : | SECTION-IIInterfacing cardsDigital-to-analog converter1128.1DAC-0808 chip8.2Basic interfacing circuit with P.C.B. aspects8.3Examples                             |

| Chapter-9 | : | Analog-to-digital converter1209.1ADC-0808 chip9.2Basic interfacing circuit with P.C.B. aspects9.3Examples                                                        |

| Chapter-10 | : | 10.1                         | <b>ing Character display</b><br>Understanding basic circuit and P.C.B.<br>aspects<br>Program techniques and examples                                            | 135              |

|------------|---|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Chapter-11 | : | <b>An in</b><br>11.1<br>11.2 | telligent control panel<br>Basic circuit understanding and P.C.B.<br>aspects<br>Examples                                                                        | 155              |

| Chapter-12 | : | witho<br>12.1<br>12.2        | <b>bg voltage measurement</b><br><b>but using ADC</b><br>VFC-331 chip<br>Basic interfacing circuit with P.C.B. asp<br>Examples                                  | 166<br>ects      |

| Chapter-13 | : | 13.1<br>13.2<br>13.3         | <b>controller</b><br>Understanding of basic circuit and P.C.<br>aspects<br>Usage of logic controller card<br>Programming aspect of logic controller<br>Examples | <b>195</b><br>B. |

| Chapter-14 | : | 14.1                         | Interfacing circuits with P.C.B. aspects<br>Programming aspect of 8253                                                                                          | 206              |

| Chapter-15 | : | 15.1                         | Interfacing circuits with P.C.B. aspects                                                                                                                        | 228              |

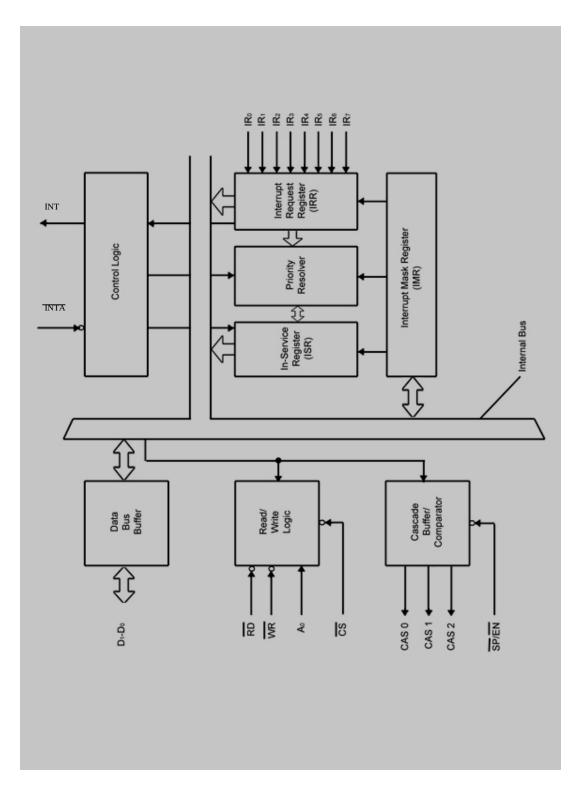

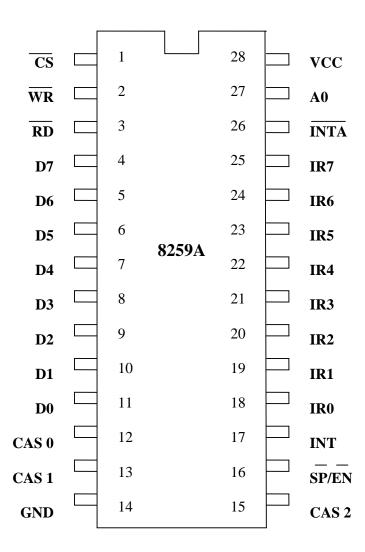

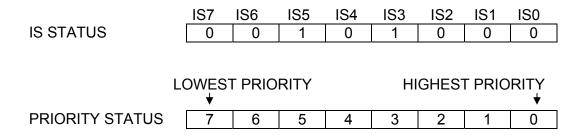

| Chapter-16 | : | 16.1<br>16.2                 | acing PIC 8259<br>Basics of 8259<br>Interfacing circuits with P.C.B. aspects<br>Programming aspects of 8259<br>Examples                                         | 250              |

References

275

#### Abstract

At present in colleges, the universities and other technical institutions the microprocessor as a subject is inevitably taught. A large section of student learners and hobbyists wish to gain in depth knowledge in the field of microprocessor.

We have considered a very versatile Intel microprocessor 8085 for the present work. The designing of the basic microprocessor CPU card is conceived and developed. The complete hardware and related software have been developed. This has culminated into a basic trainer kit. The interfacing aspects of buffer chips, memory chips, I/O chips along with keyboard and display devices have been presented in detail. The P.C.B. designing was also carried out using in-house facility. The detailed assembly language program for this system called monitor program is indigenously developed and successfully run on the system. The monitor program supports all basic features of a typical microprocessor trainer kit. In this kit the commands like Exam memory, Block move, Go and Execute, Single step, Exam register, Next and Previous are included.

We have used 8085A, 8279, 8255, 74373, 74245, 74155, 74138, FNDs, push button switches and few discrete components in the present kit. The system resources can be used for interfacing other circuits by using kit expansion connectors. The present work gives a complete idea of developing 8085 based basic system.

To create various applied types of interfacing gadgets, we have presented a number of interfacing modules. In these, the interfacing design circuits and related softwares have been discussed. This would very helpful to learners to develop their own interfacing modules based on 8085.

Following is the list of the interfacing modules developed by us.

- Digital-to-analog converter

- Analog-to-digital converter

- Running character display

- > An intelligent control panel

- Analog voltage measurement without using ADC

- Logic controller

- Interfacing Timer 8253

- Interfacing USART 8251

- Interfacing PIC 8259

Thus the present work would be very useful to the learners because it represents every hardware detail with the complete radiate software.

# **CHAPTER – 1 INTRODUCTION**

#### 1.1 Objective of the present work.

The present advance technology has made the microprocessors a routine element in the industrial & domestic applications. Today's most of the "Intelligent" electronic devices use microprocessors.

The increasing usage of microprocessor in the society has aroused an atmosphere to know & learn about microprocessors and its applications. This has resulted in the inclusion of detailed study of microprocessors as a part of regular & routine syllabus in the colleges, technical institutions & universities.

Such increasing demand and inquisitiveness among the learners sprouted this work. In essence, we planned to design and fabricate an 8085 based system, which will guide the learners to understand the microprocessors right from the scratch. In addition to this we also planned to present how one can utilize the basic concepts of microprocessor in developing various interfacing circuits through representative interfacing examples.

In sum up, we can say that the objectives of the present work are:

- 1. To design the circuit of 8085 based CPU card.

- 2. To fabricate the 8085 based CPU card as per the above circuit design. This will be consisting of

- ➡ 8085 CPU & Supporting chips.

- Memory made up of EPROM 2764 & RAM 6264.

- $\Rightarrow$  I/O section comprised of 8255.

- Key board & Display interfacing section using 8279.

- 3. To design & fabricate various interfacing modules as follows.

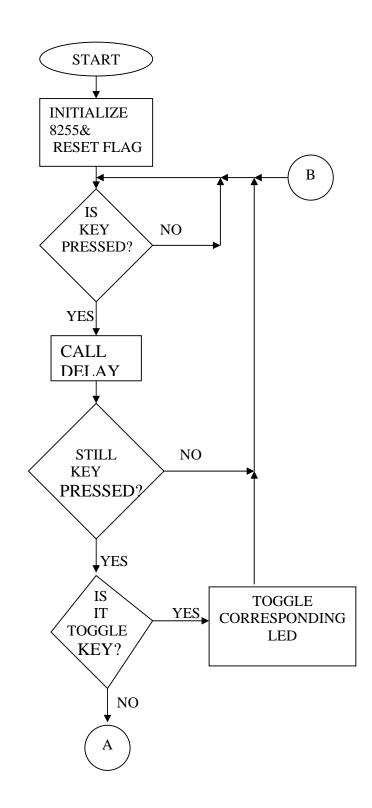

- An intelligent control panel.

- Analog voltage measurement without using ADC.

- Digital to analog converter.

- Analog to digital converter.

- ➡ USART 8251.

- Programmable interval timer/counter 8253.

- $\Rightarrow$  Interrupt controller 8259.

- Logic controller.

- Running character display.

Some times very interesting question arises, as why people go for the 8085 based systems? The answer to this question in our context is as follows.

The reasons of selecting 8085 are as follows.

- 1. It is a chip which includes all basic features of general microprocessors.

- 2. It is very popular.

- 3. Its literature is available in abundance.

- 4. Many colleges and university departments teach 8085.

- 5. Large number of students and learners are interested to gain systematic knowledge of 8085.

## 1.2 Literature survey

There are number of books available serving as a text-book or reference books on the 8085 microprocessors. Also, data books and manuals of various manufacturers are available. The list of manufacturer is as follows.

#### List of manufacturers

- 1. EMM semiconductor Hawthorne, CA 90250, USA

- 2. MOS technology Norristown, PA 19401, USA.

- 3. Texas instruments Houston, TX 77001, USA.

- 4. Mostek Carolton, TX 75006, USA.

- 5. SGS ATES Waltham, MA 02154, USA.

- 6. General Instruments (GI) Hicksville, NY 16002, USA.

- 7. Advanced Micro Devices (AMD) Sunnyvale, CA 94608, USA.

- 8. Rockwell international Anaheim, CA 92803, USA.

- 9. RCA Sommerville, NJ 08876, USA.

- 10. Intel corporation Santa Clara, CA 95051, USA.

- 11. American Microsystem (AMI) Santa Clara, CA 95051, USA.

- 12. Signetics Scottsdale, AZ 85252, USA.

- 13. Fairchild San Jose, CA 95110, USA.

- 14. Western digital corporation Newport Beach, CA 92663, USA.

- 15. Zilog Cupertino, CA 95014, USA.

- 16. Sharp Paramus, NJ 07652, USA.

- 17. Motorola Phoenix, Arizona 85006, USA.

Some of the useful books are listed as follows.

- [1] Microprocessor architecture, programming and applications by R.S.gaonkar

- [2] Microprocessor data handbook, Revised Edition, BPB Publications

- [3] 0000 to 8085 Introduction to microprocessors for engineers and scientists by P.K.Ghosh and P.R.Shridhar, second edition, PHI Publications.

- [4] Printed Circuit Board by Dr.H.N.Pandya, Published by Gujarat Granth Nirman Board, Ahmedabad,India.

The list of research publications is as follows.

- [1] Study of interfacing module to establish communications between a PC and a 8085 based microprocessor kit. LE, Lab Experiments, Volume-4,No-3,September-2004.

- [2] Study of 8255 through experiments using microprocessor kit. LE, Lab Experiments, Volume-4,No-2,June-2004

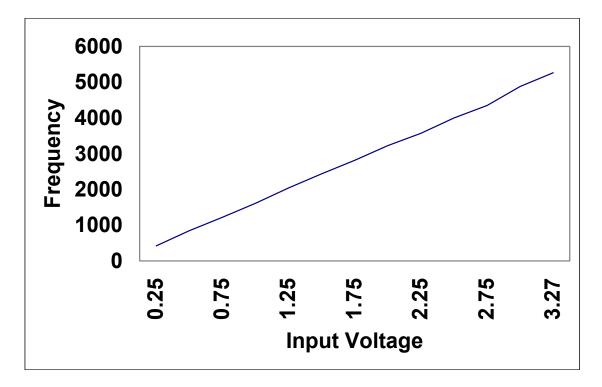

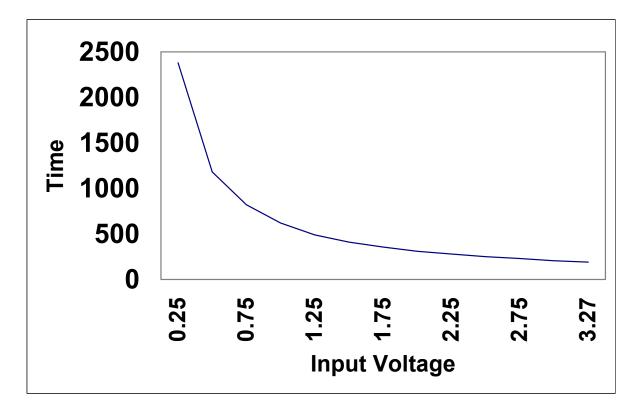

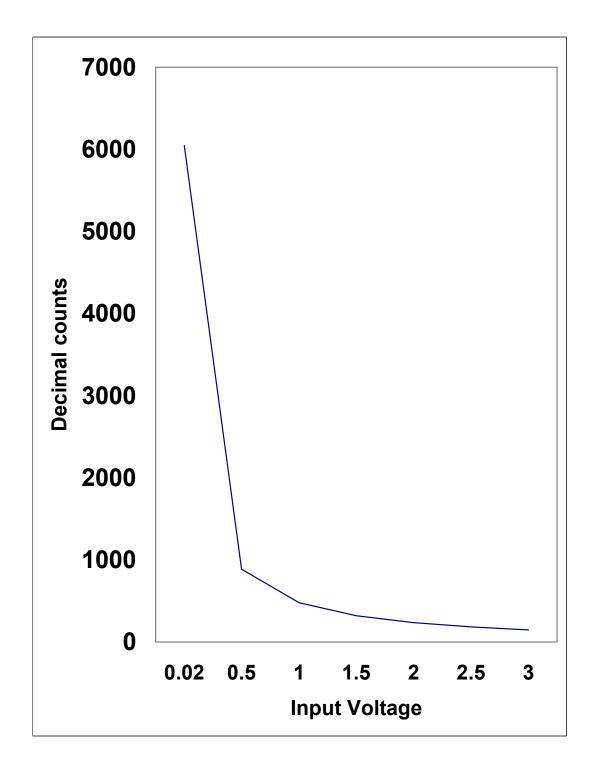

- [3] 8085 based novel software technique for V to F type analog to digital conversion. Electronic Maker, June-2004

- [4] Understanding interrupts of 8085 using Logic Analyzer.

ETA-2004,25<sup>th</sup> & 26<sup>th</sup> FEB.-2004, Computer Department, Saurashtra University,Rajkot.

- [5] Design and construction of analog to digital conversion interfacing module for 8085 microprocessor kit. 18<sup>th</sup> Gujarat Science congress, Physics Department, Saurashtra University, Rajkot dated 13<sup>th</sup> March,2004.

- [6] An intelligent control panel : A novel microprocessor based system. ETA-2003, 11<sup>th</sup> , 12<sup>th</sup> ,13<sup>th</sup> July,2003, Computer Department, Saurashtra University, Rajkot.

- [7] An interfacing module for 8085 based systems for solving Boolean equations".(communicated)

- [8] Demystifying running character display.(communicated)

The list of web-sites of interest is as given below.

- [1] <u>www.standardproducts.philips.com</u>

- [2] <u>www.qsl.net</u>

- [3] <u>www.xs4all.nl</u>

- [4] <u>www.cpu-world.com</u>

- [5] <u>www.pearson.ch</u>

- [6] <u>www.svnit.ac.in</u>

- [7] <u>www.pearsoned.co.uk</u>

- [8] bookweb.kinokuniya.co.jp

- [9] <u>www.ses.co.il</u>

- [10] <u>www.iinf.polsl.gliwice.pl</u>

In the present work the microprocessor manufactured by Intel Corporation is planned to be used. In the present work, the processor of 8085 family is selected.

To design an 8085 based education microprocessor kit, the technical information of the processor 8085 and its family chips are required. This literature is available from the Intel Corporation.

Many industrial microprocessor kits are available, but these kits are having some limitations from educational point of view.

The websites surfed are as given below.

# CHAPTER-2 BASIC UNDERSTANDING OF 8085 MICROPROCESSOR

The Intel corporation launched its 8-bit microprocessor series starting with 8080.[1,2] After 8080, it introduced a series of 8085 microprocessor. This series is available as 8085, 8085A, 8085AH, 8085AH-1, 8085AH-2.

The operating frequencies are 3MHz, 5MHz and 6MHz. Various versions of 8085 differ only in power consumption, speed and in timing signals. To site the difference 8085AH group has following instruction cycle differences.

8085AH - 1.3Microsecond instruction cycle.

8085AH-2 - 0.8Microsecond instruction cycle.

8085AH-1 - 0.67Microsecond instruction cycle.

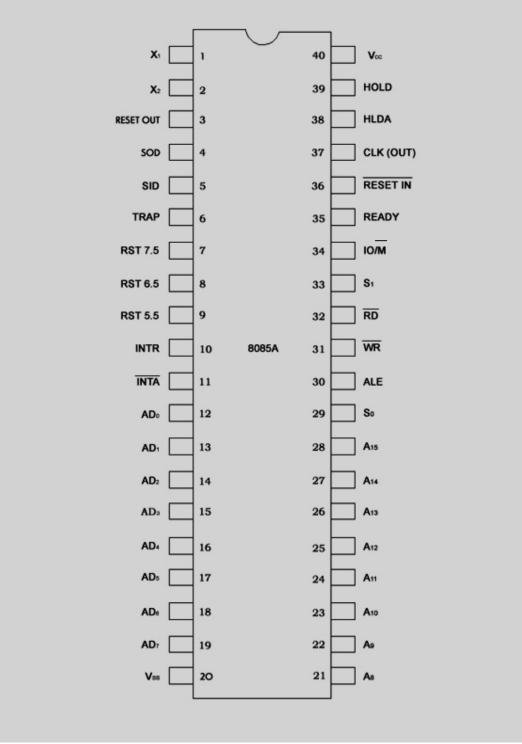

We have concentrated on 8085A. But for all practical purposes the other versions can be used. The salient features of 8085A are as follows.

- 1. It needs only +5V power supply.

- 2. It uses single clock.

- 3. It is a 40-pin device.

- 4. It has a 16-address lines, which are divided into two groups.  $AD_{n}$  to

# AD<sub>7</sub>

and  $A_8$  to  $A_{15}$ . The lower 8-lines  $AD_0$  to  $AD_7$  are multiplexed lines, i.e. at one time they work as address line  $A_0$  to  $A_7$  and at other time they work as data lines  $D_1$  to  $D_7$ .

- 5. It has 8-addressable Registers, A, B, C, D, E, H, L, F and two 16-bit registers SP and PC.

- 6. It has three status lines:  $IO/\overline{M}$ ,  $S_1$ ,  $S_0$  and three control lines:  $\overline{RD}$ ,  $\overline{WR}$  and  $\overline{INTA}$ .

- 7. For DMA operation it provides two lines, HOLD and HLDA.

- 8. Two lines RESET IN and RESET OUT are available for Reset operation.

- 9. It provides five hardware interrupts that is TRAP, RST 7.5, RST 6.5, RST 5.5 and INTR.

- 10. For serial communication two lines SID and SOD are provided.

- 11. For slower devices a synchronizing line READY is available.

## 2.1 The Block diagram

For the general understanding purpose the Intel has provided the internal working details of 8085A in turms of some basic units. We call this pictorial presentation of units as block diagram of 8085A.

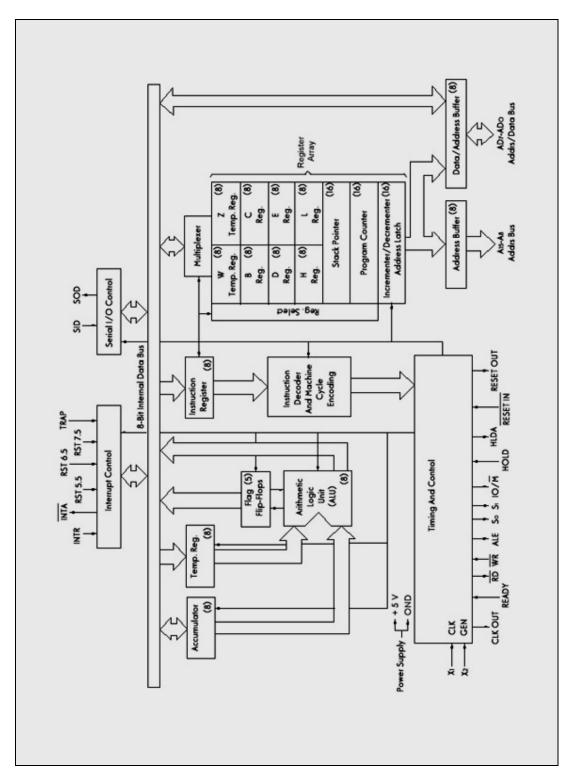

In Figure 2.1.1 details of the block diagram of 8085A is depicted.[3]

Figure-2.1.1 Block diagram of 8085

The block diagram is divided into various groups as follows.

- 1. ALU unit with its family registers.

- 2. Internal Registers.

- 3. Instruction Decoder and Machine cycle encoder along with IR (Instruction Register).

- 4. Timing and control unit with associated pins.

- 5. Interrupt control block.

- 6. Serial I/O control.

- 7. Address Data Buffers.

#### 1. ALU unit with its family registers

The ALU unit that is Arithmetic and Logic unit is an 8-bit unit. It is useful for performing all arithmetic and logical operations. It uses two 8-bit registers accumulator and a temporary register as input registers. The output of this unit generally goes to accumulator through internal bus for certain instructions. It uses flag register to declare the outcome of arithmetic and logical operations by Setting or Resetting the certain flags.

#### 2. Internal Registers

8085A has eight 8-bit registers, these are A, B, C, D, E, H, C and flag. These are used as general purpose registers. They are used to store data temporarily. The flag register has following flag bits.

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

| S  | Z  | Х  | AC | Х  | Р  | Х  | CY |

X means don't care.

#### FIGURE-2.1.2 Flag register bits

#### 1. Carry flag (bit D0)

This is D0 bit of flag register. When arithmetic or logical operations are performed such that they generate Carry, this bit is set, otherwise remains Reset. In other words, for Carry CY=1 and for NO-Carry CY=0.

#### 2. Parity flag (P - Bit D2)

If the number of 1's in accumulator are even, parity flag is set (P=1). If the number of 1's is odd the parity flag is cleared (P=0).

3. Auxiliary Carry (AC - bit - D<sub>4</sub>)

If Carry is generated while adding bit 3 of accumulator, AC is set otherwise reset. This is used in BCD arithmetic.

4. Zero flag (Z - bit - D<sub>6</sub>)

If the result of execution of an instruction is zero this flag is set (Z=1) other wise cleared (Z=0)

#### 5. Sign flag (S - bit - D<sub>7</sub>)

It provides the sign of data. If S = 0 the data is positive and if S = 1 the data is negative.

Note that accumulator is used as one of the default input for arithmetic and logical instructions. It stores the result of such instructions. For IN and OUT instructions ,it used as default destination and source respectively.

The two 16-bit registers SP and PC are special purpose registers. SP takes care of the stack management, while PC always point to the instruction codes in the memory.

In addition to these registers, register unit has a facility to increment or decrement the contents of SP and PC.

# 3. Instruction Decoder and Machine cycle encoder along with IR (Instruction Register)

When the codes of the instructions are fetched from the memory they go first to the instruction register within 8085A, one at a time. After that a series of decoder circuitry "Interprets" the codes. This interpretation will decide how many machine cycles and which types of machine cycles are needed for the instruction under consideration. This information is passed to timing and control unit for proper action.

## 4. Timing and control unit with associated pins

The signals received from instruction decoder and machine cycle encoder are analyzed and proper circuits are activated with reference to the clock and with the use of various control signals to execute the instruction. This unit controls the over all functions of all other units and maintains the timing among them selves. Following pins are directly associated with this unit.

$X_1, X_2$ , CLK OUT, READY,  $\overline{RD}$ ,  $\overline{WR}$ , ALE,  $S_0, S_1$ , IO/ $\overline{M}$ , HOLD, HLDA,  $\overline{RESET IN}$  and RESET OUT.

## 5. Interrupt Control Block

This block controls the over all management of hardware interrupts of 8085. It receives interrupts from TRAP, RST 7.5, RST 6.5, RST 5.5 and INTR. It provides INTA signal to device interrupting on INTR. A better understanding of interrupts can be obtained from the literature. [15]

## 6. Serial I/O Control Block

8085A provides a primary facility to perform serial communication using its SID and SOD pins. Data bits are received on SID and transmitted on SOD. For this 8085A uses SIM and RIM instructions.

## 7. Address Data Buffers

Address on address lines is provided by PC. Before O's and 1's of address appear on address lines they are buffered by address and data / address buffers.

## **PIN Diagram of 8085**

Here each pin has its own importance. But before use of this IC, we must know the function of each pin. The pin diagram of 8085 is shown in Figure-2.1.3.[4]

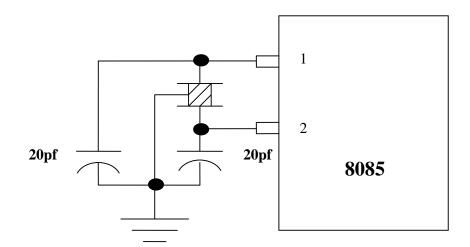

#### Pin No – 1 & 2 : X1 and X2

Generally crystal is connected between these two pins as shown in figure 2.1.4. We can also connect LC or RC network instead of crystal. The external clock source can also be given.

Here 20pf capacitors are required, if crystal frequency is bellow 4MHz. The body of the crystal is also grounded to ground electromagnetic pickup.

This typical value of capacitance given in data book of 8085, and the reason for these capacitors is to assure the oscillator start up at the correct frequency. This is shown in Figure 2.1.4.

#### Pin – 3 : Reset out

This signal is used to reset the peripheral ICs. When microprocessor resets this signal activates.

#### <u>Pin – 4 & 5 : SOD & SID</u>

These two pins are used for serial communication of data. SOD means serial output data and SID means serial Input data. SID is used to get data in and SOD is used to put data out serially.

#### <u> Pin – 6 :TRAP</u>

This trap is a non-maskable interrupt. When low to high transition takes place on this pin and high status is received till interrupt is recognized corresponding interrupt routine will be immediately called.

#### <u>Pin – 7, 8, 9, 10 : RST 7.5, RST 6.5, RST 5.5 and INTR</u>

These all can be considered as maskable interrupt pins but the priority is different.

The priority of Trap is highest then RST 7.5, RST 6.5, RST 5.5 and then INTR. When interrupt signal is received at any interrupt pin & if interrupt is enabled, its corresponding routing will be called.

#### <u>Pin – 11 : INTA</u>

This pin is known as interrupt acknowledge. When high status is received at pin-10 (INTR) the microprocessor sends low signal on this pin. This signal acknowledges that the interrupt is accepted by microprocessor.

##

These eight pins are known as multiplexed address/data lines. Here  $AD_0$  means initially the pin is an address  $A_0$  and after sometime it becomes data  $D_0$ . To use Address and Data, demultiplexing is required, whenever we are going to use 8085 in any system.

#### ✤ Pin – 20 : Vss

This pin should be connected with ground.

Figure 2.1.3 : PIN DIAGRAM OF 8085A

#### FIGURE - 2.1.4 CRYSTAL CONNECTION

Pin 21 to 28 : A<sub>8</sub> to A<sub>15</sub>

These 8-pins are known as upper order address pins.

Address bus is having total 16-bits and these are upper 8-bits, 8-lower bits are available after demultiplexing by the latch.

Pin – 29 : S<sub>0</sub>

This is lower status pin. It is rarely used in system.

✤ Pin – 30 : ALE

The full form of ALE is Address Latch Enable this. ALE signal is used for demultiplexing of  $AD_{0-7}$ .

#### <u>Pin – 31 : WR</u>

This is known as write signal. This pin goes low when something is going to write into either memory or output port.

## <u> Pin – 32 : RD</u>

This is known as Read signal. This pin goes low when something is going to read from either memory or input.

□ <u>Pin – 33 : S</u>1

This is also a status signal. It is rarely used in system.

Pin - 34 : IO/M

This pin is used as input-output or memory selection. When this pin has high logic microprocessor may perform Input or Output port related operation. If this pin has low logic means microprocessor may perform memory related operation. Sometimes it may be in high impedance state means neither high nor low. This high impedance state is also known as tri-state.

The following Table – 1 shows the Status on Status signals IO/M,  $S_1$  and  $S_0$  and status on control signal RD, WR and INTA.

| Operation       | Status | Sign | als | Co    | ntrol Si | ignals |

|-----------------|--------|------|-----|-------|----------|--------|

|                 | IO/M   | S1   | S0  | RD    | WR       | INTA   |

| Opcode<br>Fetch | 0      | 1    | 1   | 0     | 1        | 1      |

| Memory<br>Read  | 0      | 1    | 0   | 0     | 1        | 1      |

| Memory<br>Write | 0      | 0    | 1   | 1     | 0        | 1      |

| Input Read      | 1      | 1    | 0   | 0     | 1        | 1      |

| Output Write    | 1      | 0    | 1   | 1     | 0        | 1      |

| Interrupt       | 1      | 1    | 1   | 1     | 1        | 0      |

| Acknowledge     |        |      |     |       |          |        |

| Halt (Low on    | Tri-   | 0    | 0   | Tri-  | Tri-     | 1      |

| ready)          | state  |      |     | state | state    |        |

| Hold            | Tri-   | Х    | Х   | Tri-  | Tri-     | 1      |

|                 | state  |      |     | state | state    |        |

| RESET           | Tri-   | Х    | Х   | Tri-  | Tri-     | 1      |

|                 | state  |      |     | state | state    |        |

#### <u> Table – 1</u>

#### <u> Pin – 35 : Ready</u>

If this pin is high microprocessor is working normally. But when this pin will be low, microprocessor will go into wait state for integer number of clock pulses.

#### Pin – 36 : Reset in

This is active low pin. When signal on this pin will be low the microprocessor will be reset. On Reset the program counter starts execution from address 0000H.

#### Pin – 37 : CLK -OUT

Internal operating frequency is available on this pin. We can give this signal to any peripheral by using this pin for synchronization.

#### <u> Pin – 38 : HLDA</u>

When HOLD signal is received, an acknowledgement is issued by this pin.

## Pin-39 : HOLD

A high on this pin suspends normal CPU operation, and the CPU relinquishes hold of buses.

## Pin-40 : Vcc

This pin should be connected with +5 volt.

## 2.2 Interrupt

Interrupts are primarily provided to reduce the burden on processor. In this scheme processors are not supposed to continuously check the I/O devices. Whenever I/O device gets ready to communicate with processor, It intimates the same through any of the interrupt lines.8085 has following interrupts.

1. TRAP

2. RST 7.5

3. RST 6.5

4. RST 5.5

#### 5. INTR

They are listed as per their priorities .INTR, RST 5.5 and RST 6.5 are level sensitive, while RST 7.5 is rising edge sensitive. TRAP is sensitive to rising edge and level both.

RST 5.5, RST 6.5 and RST 7.5 are maskable interrupts, while TRAP is non maskable interrupt. The former are affected by EI and DI while letter is not affected by EI and DI.

The vectored addresses of interrupts are as follows.

| Interrupt | ISR address |

|-----------|-------------|

| TRAP      | 0034h       |

| RST 7.5   | 003Eh       |

| RST 6.5   | 0034h       |

| RST 5.5   | 002Ch       |

## 2.3 Serial Communication

We know that in serial communication bits are communicated one by one with every clock pulse. In other words for every clock pulse one bit is communicated. This means either input or output over one channel can be performed.

In 8085A this is achieved in a slightly different manner. Two special pins SID and SOD are provided, for inputting and outputting data respectively. These pins function with the help of execution of special instructions: RIM for inputting the data and SIM for outputting the data. Thus contrary to usual serial communication each bit on SID or SOD is communicated every time when RIM or SIM is executed not with reference to clock.

Whenever RIM instruction is executed the data on SID pin (either '0' or '1') gets transferred to the 7<sup>th</sup> bit of accumulator i.e.  $A_7$ . Similarly, When SIM instruction is executed the data in 7<sup>th</sup> bit of accumulator ( $A_7$ ) gets transferred at SOD pin.

# **CHAPTER-3 INSTRUCTION SET**

Every microprocessor understands a set of predefined command which are nothing but typical combination of 0's and 1's i.e. binary numbers. The collection of all these binary numbers or codes makes a complete set of instructions.

The manufacturers of the microprocessors classify this set into various groups, based on the common functionality of the instructions. The instruction set of 8085A also can be divided into various groups as follows.

- 1. Data transfer group.

- 2. Arithmetic group.

- 3. Branch group.

- 4. Logic group.

- 5. Stack input/output and machine control group.

The instructions of 8085A also can be categorized based on the number of bytes needed for concerned instruction. These categories are

- 1. 1-byte instruction.

- 2. 2-byte instruction.

- 3. 3-byte instruction.

In microprocessors the arithmetic and logical operations are performed on operands which we can call as Data bytes. We know that actual operation is performed in arithmetic and logic unit of microprocessor.

For that operand needed are to be brought to this unit. The operands may be stored at various possible sources, that is they can be in registers of microprocessors or they can be in external memory or they can be in I/O device. Now to bring them to ALU, manufacturers provide different ways (through different instructions). These ways are nothing but different "Addressing modes".

## 3.1 Addressing modes

The 8085A has following five addressing modes.

- 1. Immediate.

- 2. Direct.

- 3. Register.

- 4. Register Indirect.

- 5. Inherent or implied.

## 1. Immediate addressing

In this mode required operand (Data) is available in the memory location "Immediately" after the OP-CODE location in the memory.

## 2. Direct addressing

In this addressing mode address of the operand is provided along with the instruction.

For example LDA 5020H, in this instruction 5020H is addressing memory where required operand is stored.

## 3. Register addressing

In this type of addressing mode operand is contained in the register or register pair. The register or register pair are part of the instruction. For example MOV B,C, INX H etc.

## 4. Register Indirect addressing

In this addressing mode the address of the operand is not given by direct means but indicated indirectly i.e. address of the operand is represented by a pair of registers. For example LDAX B. In this instruction accumulator is to be loaded with the operand which is stored at certain location of the memory, whose address is available in register pair BC.

## 5. Inherent addressing or Implied addressing mode

In this addressing mode no operand is required. The instructions are self sufficient regarding the operations. For example STC. In this instruction it is clearly implied that there is no need of 8-bit operand. But operation is to be performed on a carry bit.

## **3.2 Instruction Format**

In 8085A the general format of instruction can be classified considering the number of bytes needed for a given instruction.

- These are

- 1. One byte instruction.

- 2. Two byte instruction.

- 3. Three byte instruction.

In single byte format the concern byte is an op-code byte. In two byte instruction format, the first byte is an op-code and the next is a data byte. In three byte instruction first byte is op-code byte, second byte is lower address byte of data and third byte is higher address byte of data.

## Tables showing the instruction summary:

| Mnemonics     |    |    |    | Instruc | tion code |    |    |    |

|---------------|----|----|----|---------|-----------|----|----|----|

|               | D7 | D6 | D5 | D4      | D3        | D2 | D1 | D0 |

| MOV R1,<br>R2 | 0  | 1  | D  | D       | D         | S  | S  | S  |

| MVI R         | 0  | 0  | D  | D       | D         | 1  | 1  | 0  |

| LXI B         | 0  | 0  | 0  | 0       | 0         | 0  | 0  | 1  |

| LXI D         | 0  | 0  | 0  | 1       | 0         | 0  | 0  | 1  |

| LXI H         | 0  | 0  | 1  | 0       | 0         | 0  | 0  | 1  |

| STAX B        | 0  | 0  | 0  | 0       | 0         | 0  | 1  | 0  |

| STAX D        | 0  | 0  | 0  | 1       | 0         | 0  | 1  | 0  |

| LDAX B        | 0  | 0  | 0  | 0       | 1         | 0  | 1  | 0  |

| LDAX D        | 0  | 0  | 0  | 1       | 1         | 0  | 1  | 0  |

| STA           | 0  | 0  | 1  | 1       | 0         | 0  | 1  | 0  |

| LDA           | 0  | 0  | 1  | 1       | 1         | 0  | 1  | 0  |

| SHLD          | 0  | 0  | 1  | 0       | 0         | 0  | 1  | 0  |

## • Move, Load and Store instructions

| LHLD | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 |

|------|---|---|---|---|---|---|---|---|

| XCHG | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 |

# • Stack related instructions

| Mnemonics |    |    |    | Instruct | ion code | ;  |    |    |

|-----------|----|----|----|----------|----------|----|----|----|

|           | D7 | D6 | D5 | D4       | D3       | D2 | D1 | D0 |

| PUSH B    | 1  | 1  | 0  | 0        | 0        | 1  | 0  | 1  |

| PUSH D    | 1  | 1  | 0  | 1        | 0        | 1  | 0  | 1  |

| PUSH H    | 1  | 1  | 1  | 0        | 0        | 1  | 0  | 1  |

| PUSH PSW  | 1  | 1  | 1  | 1        | 0        | 1  | 0  | 1  |

| POP B     | 1  | 1  | 0  | 0        | 0        | 0  | 0  | 1  |

| POP D     | 1  | 1  | 0  | 1        | 0        | 0  | 0  | 1  |

| POP H     | 1  | 1  | 1  | 0        | 0        | 0  | 0  | 1  |

| POP PSW   | 1  | 1  | 1  | 1        | 0        | 0  | 0  | 1  |

| XTHL      | 1  | 1  | 1  | 0        | 0        | 0  | 1  | 1  |

| SPHL      | 1  | 1  | 1  | 1        | 1        | 0  | 0  | 1  |

| LXI SP    | 0  | 0  | 1  | 1        | 0        | 0  | 0  | 1  |

| INX SP    | 0  | 0  | 1  | 1        | 0        | 0  | 1  | 1  |

| DCX SP    | 0  | 0  | 1  | 1        | 1        | 0  | 1  | 1  |

# • Jump instructions

| Mnemonics |    |    |    | Instructi | on code |    |    |    |

|-----------|----|----|----|-----------|---------|----|----|----|

|           | D7 | D6 | D5 | D4        | D3      | D2 | D1 | D0 |

| JMP       | 1  | 1  | 0  | 0         | 0       | 0  | 1  | 1  |

| JC        | 1  | 1  | 0  | 1         | 1       | 0  | 1  | 0  |

| JNC       | 1  | 1  | 0  | 1         | 0       | 0  | 1  | 0  |

| JZ        | 1  | 1  | 0  | 0         | 1       | 0  | 1  | 0  |

| JNZ       | 1  | 1  | 0  | 0         | 0       | 0  | 1  | 0  |

| JP        | 1  | 1  | 1  | 1         | 0       | 0  | 1  | 0  |

| JM        | 1  | 1  | 1  | 1         | 1       | 0  | 1  | 0  |

| JPE       | 1  | 1  | 1  | 0         | 1       | 0  | 1  | 0  |

| JPO       | 1  | 1  | 1  | 0         | 0       | 0  | 1  | 0  |

| PCHL      | 1  | 1  | 1  | 0         | 1       | 0  | 0  | 1  |

# • Call instructions

| Mnemonics |    | Instruction code |    |    |    |    |    |    |  |  |

|-----------|----|------------------|----|----|----|----|----|----|--|--|

|           | D7 | D6               | D5 | D4 | D3 | D2 | D1 | D0 |  |  |

| CALL      | 1  | 1                | 0  | 0  | 1  | 1  | 0  | 1  |  |  |

| CC        | 1  | 1                | 0  | 1  | 1  | 1  | 0  | 0  |  |  |

| CNC       | 1  | 1                | 0  | 1  | 0  | 1  | 0  | 0  |  |  |

| CZ        | 1  | 1                | 0  | 0  | 1  | 1  | 0  | 0  |  |  |

| CNZ       | 1  | 1                | 0  | 0  | 0  | 1  | 0  | 0  |  |  |

| CP        | 1  | 1                | 1  | 1  | 0  | 1  | 0  | 0  |  |  |

| СМ  | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

|-----|---|---|---|---|---|---|---|---|

| CPE | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| CPO | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 |

## • Return instructions

| Mnemonics |    |    |    | Instructi | on code |    |    |    |

|-----------|----|----|----|-----------|---------|----|----|----|

|           | D7 | D6 | D5 | D4        | D3      | D2 | D1 | D0 |

| RET       | 1  | 1  | 0  | 0         | 1       | 0  | 0  | 1  |

| RC        | 1  | 1  | 0  | 1         | 1       | 0  | 0  | 0  |

| RNC       | 1  | 1  | 0  | 1         | 0       | 0  | 0  | 0  |

| RZ        | 1  | 1  | 0  | 0         | 1       | 0  | 0  | 0  |

| RNZ       | 1  | 1  | 0  | 0         | 0       | 0  | 0  | 0  |

| RP        | 1  | 1  | 1  | 1         | 0       | 0  | 0  | 0  |

| RM        | 1  | 1  | 1  | 1         | 1       | 0  | 0  | 0  |

| RPE       | 1  | 1  | 1  | 0         | 1       | 0  | 0  | 0  |

| RPO       | 1  | 1  | 1  | 0         | 0       | 0  | 0  | 0  |

# • Restart, Input and output instructions

| Mnemonics |    |    |    | Instructi | on code |    |    |    |

|-----------|----|----|----|-----------|---------|----|----|----|

|           | D7 | D6 | D5 | D4        | D3      | D2 | D1 | D0 |

| RST N     | 1  | 1  | Α  | Α         | Α       | 1  | 1  | 1  |

| IN        | 1  | 1  | 0  | 1         | 1       | 0  | 1  | 1  |

| OUT       | 1  | 1  | 0  | 1         | 0       | 0  | 1  | 1  |

## • Increment and decrement instructions

| Mnemonics | Instruc | tion cod | е  |    |    |    |    |    |

|-----------|---------|----------|----|----|----|----|----|----|

|           | D7      | D6       | D5 | D4 | D3 | D2 | D1 | D0 |

| INR R     | 0       | 0        | D  | D  | D  | 1  | 0  | 0  |

| DCR R     | 0       | 0        | D  | D  | D  | 1  | 0  | 1  |

| INX RP    | 0       | 0        | D  | D  | 0  | 0  | 1  | 1  |

| DCX RP    | 0       | 0        | D  | D  | 1  | 0  | 1  | 1  |

## • Addition and subtraction instructions

| Mnemonics |    |    |    | Instructi | on code |    |    |    |

|-----------|----|----|----|-----------|---------|----|----|----|

|           | D7 | D6 | D5 | D4        | D3      | D2 | D1 | D0 |

| ADD R     | 1  | 0  | 0  | 0         | 0       | S  | S  | S  |

| ADC R     | 1  | 0  | 0  | 0         | 1       | S  | S  | S  |

| ADI       | 1  | 1  | 0  | 0         | 0       | 1  | 1  | 0  |

| ACI       | 1  | 1  | 0  | 0         | 1       | 1  | 1  | 0  |

| DAD RP    | 0  | 0  | D  | D         | 1       | 0  | 0  | 1  |

| SUB R     | 1  | 0  | 0  | 1         | 0       | S  | S  | S  |

| SBB R     | 1  | 0  | 0  | 1         | 1       | S  | S  | S  |

| SUI       | 1  | 1  | 0  | 1         | 0       | 1  | 1  | 0  |

| SBI   1   1   0   1   1   1   1   0 |

|-------------------------------------|

|-------------------------------------|

## • Logical instructions

| Mnemonics |    |    |    | Instructi | on code |    |    |    |

|-----------|----|----|----|-----------|---------|----|----|----|

|           | D7 | D6 | D5 | D4        | D3      | D2 | D1 | D0 |

| ANA R     | 1  | 0  | 1  | 0         | 0       | S  | S  | S  |

| XRA R     | 1  | 0  | 1  | 0         | 1       | S  | S  | S  |

| ORA R     | 1  | 0  | 1  | 1         | 0       | S  | S  | S  |

| CMP R     | 1  | 0  | 1  | 1         | 1       | S  | S  | S  |

| ANI       | 1  | 1  | 1  | 0         | 0       | 1  | 1  | 0  |

| XRI       | 1  | 1  | 1  | 0         | 1       | 1  | 1  | 0  |

| ORI       | 1  | 1  | 1  | 1         | 0       | 1  | 1  | 0  |

| CPI       | 1  | 1  | 1  | 1         | 1       | 1  | 1  | 0  |

## • Rotate instructions

| Mnemonics |    |    |    | Instructi | on code |    |    |    |

|-----------|----|----|----|-----------|---------|----|----|----|

|           | D7 | D6 | D5 | D4        | D3      | D2 | D1 | D0 |

| RLC       | 0  | 0  | 0  | 0         | 0       | 1  | 1  | 1  |

| RRC       | 0  | 0  | 0  | 0         | 1       | 1  | 1  | 1  |

| RAL       | 0  | 0  | 0  | 1         | 0       | 1  | 1  | 1  |

| RAR       | 0  | 0  | 0  | 1         | 1       | 1  | 1  | 1  |

## • Special instructions

| Mnemonics |    |    |    | Instructi | on code |    |    |    |

|-----------|----|----|----|-----------|---------|----|----|----|

|           | D7 | D6 | D5 | D4        | D3      | D2 | D1 | D0 |

| CMA       | 0  | 0  | 1  | 0         | 1       | 1  | 1  | 1  |

| STC       | 0  | 0  | 1  | 1         | 0       | 1  | 1  | 1  |

| CMC       | 0  | 0  | 1  | 1         | 1       | 1  | 1  | 1  |

| DAA       | 0  | 0  | 1  | 0         | 0       | 1  | 1  | 1  |

## • Control instructions

| Mnemonics |    |    |    | Instructi | on code | !  |    |    |

|-----------|----|----|----|-----------|---------|----|----|----|

|           | D7 | D6 | D5 | D4        | D3      | D2 | D1 | D0 |

| EI        | 1  | 1  | 1  | 1         | 1       | 0  | 1  | 1  |

| DI        | 1  | 1  | 1  | 1         | 0       | 0  | 1  | 1  |

| NOP       | 0  | 0  | 0  | 0         | 0       | 0  | 0  | 0  |

| HLT       | 0  | 1  | 1  | 1         | 0       | 1  | 1  | 0  |

| RIM       | 0  | 0  | 1  | 0         | 0       | 0  | 0  | 0  |

| SIM       | 0  | 0  | 1  | 1         | 0       | 0  | 0  | 0  |

Here DDD, SSS, AAA are three binary bits from 000 to 111. DDD shows destination register code and SSS shows source register code. AAA shows interrupt number. DD shows 00 to 11 as destination register pair code.

## 3.3 All Instructions

In this chapter in the beginning we have divided the whole instruction set of 8085A into several groups. We will discuss the instructions of 8085A as per these groups.[5]

## 1. Data Transfer Group

The data can be transferred by the following types of instructions. The flags are not affected by these instructions.

| MVI r1 Data -  | The Data is loaded into register r.                                                                |

|----------------|----------------------------------------------------------------------------------------------------|

| MVI M1 Data -  | The Data is immediately loaded into                                                                |

|                | memory whose address is in HL pair.                                                                |

| MOV r1, r2 -   | The Data of register r2 is transferred into r1.                                                    |

| MOV M, r -     | The Data of register is transferred into<br>memory whose address is given in HL.                   |

| MOV r, M -     | The Data of memory whose address is in HL is transferred into register.                            |

| LXI rp1 Data - | The 16-bit data is immediately loaded into register pair rp.                                       |

| STA address -  | Store content of accumulator at given address.                                                     |

| LDA address -  | Load content into accumulator from given address.                                                  |

| SHLD address - | Store HL register pair directly at the given address and address +1 locations.                     |

| LHLD address - | Load HL register pair directly from the given address and address +1 locations.                    |

| LDAX Rp -      | Load the accumulator with the contents of the memory whose address is given into register pair Rp. |

| STAX Rp -      | Store the content of accumulator into the memory whose address is given into register pair Rp.     |

| XCHG -         | Exchange the contents of register pair HL with DE.                                                 |

## 2. Arithmetic Group

This arithmetic group can be classified into following categories.

- 1. Increment & Decrement group.

- 2. Addition group.

- 3. Subtraction group.

- 4. Decimal Adjust Accumulator group.

- Increment & Decrement group

- INR r The content of register is incremented by one only carry flag is not affected.

- INR M Increment the content of the memory location by one whose address is in HL Register pair only carry flag is not affected.

- INX rp Increment the content of the register pair rp by one. No flags are affected.

- DCR r The content of register is decremented by one only carry flag is not affected.

- DCR M Decrement the content of the memory location by one whose address is in HL Register pair only carry flag is not affected.

- DCX rp Decrement the content of the register pair rp by one. No flags are affected.

## Addition group

- ADD r Addition of the contents of accumulator and register r. The answer is stored into accumulator. All flags are affected.

- ADD M Addition of the contents of accumulator and memory whose address is in HL pair. The answer is stored into accumulator. All flags are affected.

- ADI Data Addition of the contents of accumulator with the Data. The answer is stored into accumulator. All flags are affected.

- ADC r Addition of the carry flag with the contents of accumulator and register. The answer is stored into accumulator. All flags are affected.

- ADC M Addition of the carry flag with the contents of accumulator and memory (whose address is given in HL pair). The answer is stored into accumulator. All flags are affected.

- ACI Data Addition of the carry flag with the content of accumulator and Data. The result is stored into accumulator. All flags are affected.

- DAD rp Addition of the contents of register pair rp with the contents of the HL pair. The result is stored into HL. Only the carry flag is affected.

## • Subtraction group

In this group of instructions borrow is used for carry flag.

SUB r - Subtract the content of register r from accumulator. The result is stored into accumulator. All flags are affected.

SUB M - Subtract the content of memory (whose location is given in HL pair) from accumulator. The result is stored into accumulator. All flags are affected.

SUI Data - Subtract the data from accumulator. The result is stored into accumulator. All flags are affected.

SBB r - Subtract the borrow and content of register r rom the content of accumulator. All flags are affected.

- SBB M Subtract the borrow and the content of memory (whose address is given in HL pair) from the content of accumulator. The result is stored into accumulator. All flags are affected.

- SBI Data Subtract the borrow and the data from the content of accumulator. The result is stored into accumulator. All flags are affected.

## Decimal Adjust group

DAA - A Decimal Adjust Accumulator. This instruction converts the binary content of accumulator into B.C.D. form.

## 3. Branch group

| JMP address -     |               | ion jumps at address<br>ally. All flags are unaffected. |

|-------------------|---------------|---------------------------------------------------------|

| J cond. address - | This instruct | ion jumps at address<br>. The instructions are as given |

|                   | below         | with conditions.                                        |

| JC                | Jump if       | C=1                                                     |

| JNC               | Jump if       | C=0                                                     |

| JP                | Jump if       | S=0                                                     |

| JM                | Jump if       | S=1                                                     |

| JPE               | Jump if       | P=1                                                     |

| JPO               | Jump if       | P=0                                                     |

| JZ                | Jump if       | Z=1                                                     |

| JNZ               | Jump if       | Z=0                                                     |

All flags remain unaffected.

| PCHL-             |                             |                                   | pies the contents of HL pair<br>emain unaffected.                    |

|-------------------|-----------------------------|-----------------------------------|----------------------------------------------------------------------|

| CALL address -    | uncondition                 | ally, aft                         | Is the subroutine<br>er storing content of<br>ags remain unaffected. |

| C cond. address - | This instruct conditionally | tions ca<br>/, after<br>ne instru | all the subroutine<br>storing content of PC<br>uctions are as given  |

| CC -              | Call                        | if                                | C=1                                                                  |

| CNC-              | Call                        | if                                | C=0                                                                  |

| CP-               | Call                        | if                                | S=0                                                                  |

| CM-               | Call                        | if                                | S=1                                                                  |

| CPE-              | Call                        | if                                | P=1                                                                  |

| CPO-              | Call                        | if                                | P=0                                                                  |

| CZ-               | Call                        | if                                | Z=1                                                                  |

| CNZ-              | Call                        | if                                | Z=0                                                                  |

|                   |                             |                                   |                                                                      |

All flags remain unaffected.

Return

| RET - | This instruction returns from the subroutine       |

|-------|----------------------------------------------------|

|       | unconditionally. The address is retrieved from the |

|       | stack. All flags remain unaffected.                |

|       |                                                    |

R cond - This instruction returns from the subroutine conditionally. The address is retrieved from the stack. All flags remain unaffected.

These conditional return instructions are as given below with conditions.

| RC  | Return | if | C=1 |

|-----|--------|----|-----|

| RNC | Return | if | C=0 |

| RP  | Return | if | S=0 |

| RM  | Return | if | S=1 |

| RPE | Return | if | P=1 |

| RPO | Return | if | P=0 |

| RZ  | Return | if | Z=1 |

| RNZ | Return | if | Z=0 |

RST n - This instruction is similar to a call instruction for fixed address.

The fixed address are as given below.

Instruction Destination Address

| RST 0-  | 0000H |

|---------|-------|

| RST 1 - | 0008H |

| RST 2 - | 0010H |

| RST 3 - | 0018H |

| RST 4 - | 0020H |

| RST 5 - | 0028H |

| RST 6-  | 0030H |

| RST 7 - | 0038H |

|         |       |

## 4. Logic group

The logical operations can be performed by using the following instructions.

- ANA r The content of accumulator is logically ANDed with content of register r. The result is stored into accumulator. All flags are affected. The carry will be cleared and the auxiliary carry will be set.

- ANA M The content of accumulator is logically ANDed with content of memory (whose address is given in HL pair). The result is stored into accumulator. All flags are affected. The carry flag is cleared and the auxiliary carry will be set.

- ANI Data The content of accumulator is logically ANDed with Data. The result is stored into accumulator. All flags are affected. The carry flag is cleared and the auxiliary carry will be set.

| XRA r -    | The content of accumulator is logically exclusive 0Red with the content of register r. The result is    |

|------------|---------------------------------------------------------------------------------------------------------|

|            | stored into accumulator. All flags are affected.<br>The carry and auxiliary carry flags are reset.      |

| XRA M -    | The content of accumulator is logically exclusive                                                       |

|            | 0Red with the content of memory (location in HL                                                         |

|            | pair). The result is stored into accumulator. All                                                       |

|            | flags are affected. The carry and auxiliary carry                                                       |

|            | flags are reset.                                                                                        |

| XRI Data - | The content of accumulator is logically                                                                 |

|            | exclusive ORed with the data. The result is stored into accumulator. All flags are affected.            |

|            | The carry and auxiliary carry flags are reset.                                                          |

| ORA r -    | The content of accumulator is logically ORed                                                            |

| 01011      | with the content of register r. The result is stored                                                    |

|            | into accumulator. All flags are affected. The carry                                                     |

|            | and auxiliary carry flags are reset.                                                                    |

| ORA M -    | The content of accumulator is logically 0Red                                                            |

|            | with the content of memory (whose address is                                                            |

|            | given in HL pair). The result is stored into                                                            |

|            | accumulator. All flags are affected. The carry and auxiliary carry flags are reset.                     |

| ORI Data - | The content of accumulator is logically ORed                                                            |

| or a Data  | with the data. The result is stored into                                                                |

|            | accumulator. All flags are affected. The carry                                                          |

|            | and auxiliary carry flags are reset.                                                                    |

| CMP r -    | This instruction compares the content of                                                                |

|            | accumulator with content of register r. If both are                                                     |

|            | same zero flag is set. If content of accumulator is less then content of register so carry flag is set. |

|            | All fags are affected.                                                                                  |

| CMP m -    | This instruction compares the content of                                                                |

|            | accumulator with content of memory (whose                                                               |

|            | address is given in HL pair). If both are same                                                          |

|            | zero flag is set. If content of accumulator is less                                                     |

|            | then content of memory carry flag is set. All                                                           |

|            | flags are affected.                                                                                     |

| CPI Data - | This information compares the content of accumulator with data. If both are same so zero                |

|            | flag is set. If the content of accumulator is less                                                      |

|            | then Data, so carry flag is set. All flags are                                                          |

|            | affected.                                                                                               |

| STC -      | The carry flag can be set by this instruction.                                                          |

| CMC -      | The carry flag is complimented by this instruction.                                                     |

| CMA -      | The content of accumulator is complimented by this                                                      |

|            | instruction.                                                                                            |

| Rotate     |                                                                                                         |

RLC - Rotate content of accumulator left by one position. The content of carry flag is lost.

٠

- RRC Rotate content of accumulator right by one position. The content of carry flag is lost.

- RAL Rotate content of accumulator left by one position through carry.

- RAR Rotate content of accumulator right by one position through carry.

#### 5. Stack, I/O and machine control Instructions

- PUSH rp This instruction pushes(copies) the content of register pair on the stack. The content of stack pointer is decremented by two. Flags are unaffected.

- PUSH PSW- The content of accumulator and flags(PSW means Program Status Word) are pushed on the stack. The content of stack pointer is decremented by two. Flags are unaffected.

- POP Rp The data from the top of stack is retrieved into register pair Rp. The stack pointer is incremented by two. Flags are unaffected.

- POP PSW The contents of accumulator and flags are retrieved from top of the stack. The stack pointer is incremented by two. Flags are unaffected.

- XTHL -The data at locations pointed by SP and<br/>SP+1 are exchanged with registers L and<br/>H respectively. Flags are unaffected.

- SPHL The content of register pair H gets copied into stack pointer. Flags are unaffected.

- Input / Output

| IN Port - | This instruction receives 8-bit data from port and stores |

|-----------|-----------------------------------------------------------|

|           | into accumulator Flags are unaffected.                    |

| OUT Port- | This instruction puts 8-bit data from Accumulator to the  |

|           | port. Flags are unaffected.                               |

## Machine Control

| EI -  | This instruction sets the internal interrupt flip-flop                                                |

|-------|-------------------------------------------------------------------------------------------------------|

|       | of microprocessor. Flags are unaffected.                                                              |

| DI -  | This instruction resets the internal interrupt flip-<br>flop of microprocessor. Flags are unaffected. |

| NOP - | This instruction is not doing anything. It is also                                                    |

|       | known an No-Operation. Flags are unaffected.                                                          |

| HLT - | The microprocessor halts by this instruction. It                                                      |

|       | will be restarted by interrupt or reset. Flags are unaffected.                                        |

| SIM - | The full form of this instruction is Set Interrupt                                                    |

|       | Mask. This instruction works with the content of                                                      |

accumulator. The meaning of all eight bits of accumulator is given below.

- D0,D1 and D2 mask RST 5.5,RST 6.5 and RST 7.5 respectively. '1' means mask and '0' means unmask.

- \* D3 should be '1' to make D0,D1 and D2 effective.

- \* D4 resets RST 7.5 flip-flop.

- \* D5 is not used.

- \* D6 is serial output enable. It should be '1' to enable serial output data.

- D7 bit transfers at SOD pin if D6 is '1'.

- RIM The full form of this instruction is Read Interrupt Mask. The status is copied into accumulator. The meaning of all eight bits of accumulator is as given below.

- \* D0,D1 and D2 set if RST 5.5,RST 6.5 and RST 7.5 respectively are masked.

- \* D3 sets if IE(interrupt enable)flag is set.

- \* D4,D5 and D6 set if RST 5.5,RST 6.5 and RST 7.5 respectively are pending.

- \* D7 reads the logic at SID(serial input data)pin.

# CHAPTER-4 INTERFACING OF EPROM AND RAM

The 8085A processor has only a few internal register which can store data. In real life any user's program cannot be accommodated in such internal register memory. Hence 8085A requires external memory.

Processor alone cannot make a useful system. It requires memory and input output facility. To be a useful microprocessor based system certain user's commands are to be a remembered permanently, so that every time system is initialized it can perform execution of few user defined commands.

For this system has to employ a sort of memory which can permanently store these commands, EPROM is such type of memory. Hence, it becomes very interesting to know that how one can interface such EPROMs with the processors.

On the other hand microprocessor based system (e.g. microprocessor trainer kit) does not required to remember permanently users program. For this purpose it requires some temporary memory which can perform read write operation, in order to execute user programs. This type of memory is available as RAM memory. So it is also interesting to know how to interface such memory chips with processor.

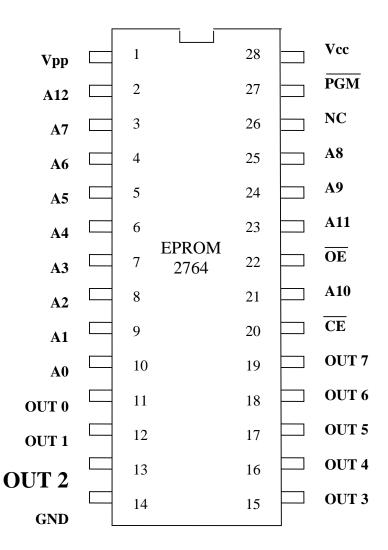

#### 4.1 EPROM 2764A

It is a 8-bit wide memory. In the number 2764A, 64 indicates that it has total 64 Kbit memory, In bytes, it becomes 8Kx 8 memory size.[4]

#### 4.1.1 BLOCK DIAGRAM AND FUCTIONAL DESCRIPTION

The block diagram of 2764A is shown in Figure 4.1.1.1.

The heart of the chip is a cell matrix of 65536 bits. This cell matrix is internally so arranged that it gives us 8KX8 memory. The 8K bytes require total 13-address lines. In 2764A this lines are  $A_0$  to  $A_{12}$ . These address lines are internally applied to Y-decoder and X-decoder, which select the particular cell of cell matrix. The output of the selected cells is passed to output buffers. These buffers are again controlled by output enable pin. When  $\overline{OE}$  is low the output buffers send the data on the output pins,  $O_0$  to  $O_7$ .

The chip 2764A has four special pins  $V_{PP}$ ,  $\overline{OE}$ ,  $\overline{PGM}$  and  $\overline{CE}$ .

The functions of above pins together decides the various modes of the operation of 2764A. Table-4.1.1.1. describes the detail of various modes of 2764A.

|             | Pins            |     |                 |                 |          |          |

|-------------|-----------------|-----|-----------------|-----------------|----------|----------|

| Mode        |                 |     |                 |                 |          |          |

|             | CE              | OE  | PGM             | $V_{PP}$        | $V_{CC}$ | Output   |

| Read        | VIL             | VIL | V <sub>IH</sub> | V <sub>CC</sub> | 5.0V     | D out    |

| Output      | VIL             | VIH | VIH             | V <sub>CC</sub> | 5.0V     | High – Z |

| disable     |                 |     |                 |                 |          | _        |

| Stand by    | V <sub>IH</sub> | Х   | Х               | V <sub>CC</sub> | 5.0V     | High – Z |

| Programming | VIL             | VIH | V <sub>IL</sub> | 12V             | 5.0V     | D In     |

| Program     | VIL             | VIL | VIH             | 12V             | 5.0V     | D out    |

| verify      |                 |     |                 |                 |          |          |

| Program     | V <sub>IH</sub> | Х   | Х               | 12V             | 5.0V     | High – Z |

| inhibit     |                 |     |                 |                 |          |          |

Table-4.1.1.1

$O_0 TO 0_7$ Vcc -GND -Vpp OUTPUT ENABLE OE CHIP ENABLE PGM **OUTPUT BUFFERS** AND PROG LOGIC CE Y Y-GATING DECODER A0 65,536 BIT TO Х CELL MATRIX A12 DECODER

Figure 4.1.1.1 INTERNAL BLOCK DIAGRAM OF EPROM 2764A

In above table  $V_{IL}$  is the input low level voltage and  $V_{IH}$  is the input high level voltage.

$(V_{IL} - 0.1V \text{ to } 0.8V \text{ and } V_{IH} = 2V \text{ to } + V_{CC})$

To program the 2764A we have to select the chip (CE =  $V_{IL}$ ), inhibit the reading operation. (OE =  $V_{IH}$ ), and PGM =  $V_{IL}$ . At the same time  $V_{PP}$  should be given +12V supply and  $V_{CC}$  should be given +5V.

Figure 4.1.1.2. shows the pin diagram of 2764A.

#### 4.1.2 INTERFACING OF 2764A IN THE PRESENT SYSTEM

In the present microprocessor system design 8K byte of EPROM was considered sufficient to store the monitor program.

For interfacing 2764A with the 8085A a decoder 74155 and a latching IC 74L5373 are used. The interfacing circuit for the same is shown in Figure 4.1.2.1. Note that this circuit is a part of the detailed circuit diagram of the microprocessor trainer kit designed by us.

IC 74373 demultiplexes the AD0 to AD7 lines of 8085A, when ALE becomes high and it enables IC 74L5373 through its pin no.11(G), to latch the address A0 to A7. Active low enable pin no.1, that is OC of IC 74373 is permanently grounded. The output Q0 to Q7 of IC 74L5373 (i.e. A0 to A7 address lines.) are connected with the address lines A0 to A7 of EPROM 2764A. The rest of the address lines of 2764A, that is A8 to A12 address lines of 8085A.

The EPROM IC has a pin named  $\overline{OE}$  which helps to read data out. This  $\overline{OE}$  pin is directly connected with the RD of 8085A. Its PGM and Vpp are tied up with Vcc

Figure 4.1.1.2 PIN DIAGRAM OF EPROM 2764A

The chip selection is controlled by the decoder 74155. In the present system design this 74155 is used to select the memory chips 2764A, 6264, and I/O chips 8279 and 8255.

To separate the memory and I/O devices the output pins of 74155 are divided into two groups that is 1Y0, 1Y1, 1Y2 and 1Y3 are for I/O device selection and 2Y0, 2Y1, 2Y2 and 2Y3 are for memory chip selection.

74155 has four enable pins out of which three are active low and one active high. Out of three active low pins two are permanently grounded. The remaining two (where one is active low and another is active high) are connected with  $IO/\overline{M}$  pin of 8085A. Here active high is connected with enabling of outputs of internal decoder 1 of 74155. While active\_low is

connected with the internal decoder-2 of 74155. Hence whenever IO/M pin of 8085A is high, I/O devices are selected, and when IO/M is low, memory chips are selected.

Now the differentiation of I/O devices and memory chips is done through the input lines A and B of 74155, these A and B input lines of 74155 are directly connected with the A14 and A15 address lines of 8085A respectively. Following Table-4.1.2.1 explains the I/O device and memory chips selection details.

| IO/M | A<br>(A14) | B<br>(A15) | Selection      |

|------|------------|------------|----------------|

| 0    | 0          | 0          | EPROM 2764A    |

|      |            |            | (2Y0)          |

| 0    | 0          | 1          | Unused (2Y2)   |

| 0    | 1          | 0          | RAM 6264 (2Y1) |

| 0    | 1          | 1          | Unused (2Y3)   |

| 1    | 0          | 0          | PPI 8255 (1Y0) |

| 1    | 0          | 1          | External card  |

|      |            |            | (1Y1)          |

| 1    | 1          | 0          | KDI 8279 (1Y1) |

| 1    | 1          | 1          | Unused (1Y3)   |

TABLE-4.1.2.1

Figure: 4.1.2.1 CONNECTION OF EPROM WITH 8085

## 4.2 STATIC RAM 6264

It is 8-bit wide read/write memory. Its capacity is 8KX8 bits.[4]

# 4.2.1 BLOCK DIAGRAM AND FUCTIONAL DESCRIPTION OF 6264

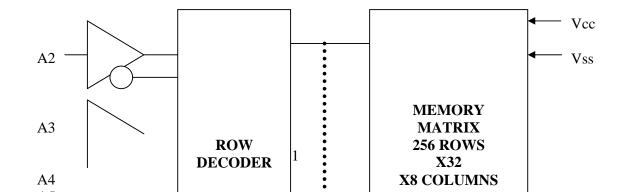

Figure 4.2.1.1 shows the internal block diagram of 6264 RAM chip. It has total 13-address lines i.e. A0 to A12.

As shown in the block diagram the 65536 bits are arranged in three dimensions as 8 Matrices of 256 X 32 rows & columns respectively. The address lines A<sub>2</sub>, A<sub>3</sub>, A<sub>4</sub>, A<sub>5</sub>, A<sub>7</sub>, A<sub>8</sub>, A<sub>9</sub> and A<sub>11</sub> drive the row decoder while A<sub>0</sub>, A<sub>1</sub>, A<sub>6</sub>, A<sub>10</sub> and A<sub>12</sub> drive the column decoder. There is unit called input data control which accepts 8-bit input on the lines DQ<sub>0</sub> to DQ<sub>7</sub> under the control of  $\overline{E_1}$ ,  $\overline{E_2}$  and  $\overline{W}$ . The reading of the chip is done under the control of  $\overline{E_1}$ ,  $\overline{E_2}$ ,  $\overline{W}$  and  $\overline{G}$ .

Table 4.2.1.2. explains the various modes of the chip MCM 6264C.

| E1 | E2 | G | × | Mode               | Output   |

|----|----|---|---|--------------------|----------|

| Н  | Х  | Х | Х | Not<br>selected    | High - Z |

| X  | L  | Х | Х | Not<br>selected    | High - Z |

| L  | Н  | Н | Н | Output<br>disabled | High - Z |

| L  | Н  | L | L | Read               | D out    |

| L  | Н  | Х | Х | Write              | High - Z |

| Table – 4.2.1.2 |

|-----------------|

|-----------------|

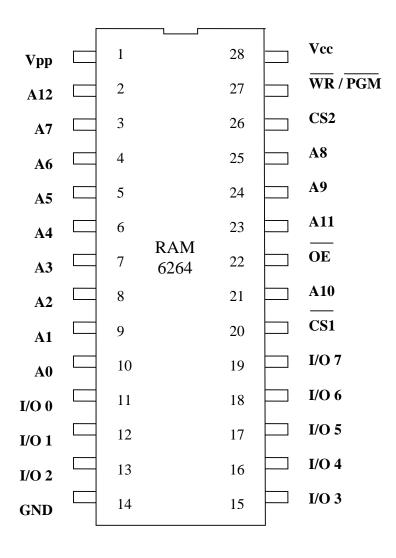

Figure 4.2.1.2. shows the pin assignment of the 6264C.

#### 4.2.2 INTERFACING OF 6264 IN THE PRESENT SYSTEM

In the present system, the interfacing circuit for RAM 6264 involves 74LSs373 and 74155 and 8085. ICs 74373 and 74155 are having the same connection details with the 8085A as discussed in section 4.1.2. The only difference in this one is that the A and B input lines of 74155 selects 6264 through output pin 2Y, by accepting A15, A14=0,1.

The detailed circuit diagram is shown in Figure 4.2.2.1 Note that since this is Read/Write memory one should connect RD and WR pins with 6264. In the present design WR is connected with WR and RD is connected with OE of 6264. 6264 has two chips select lines. CS1, and CS2. CS1 is driven by 74155 while CS2 is connected with +5volt.

Figure 4.2.1.1 INTERNAL BLOCK DIAGRAM OF RAM 6264

Figure 4.2.1.2. The pin assignment of the 6264

Figure 4.2.2.1 : CONNECTION OF RAM WITH 8085

## CHAPTER – 5 I/O INTERFACING

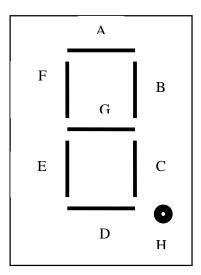

For a given microprocessor system to execute the user's program, there should be a provision to allow the user to store these programs into microprocessor system's memory. This is generally done by interfacing a hex key pad with the microprocessor. User also needs to check the results of the execution of his program, for this purpose output device is used. Generally seven segment LEDs or LCD display are used in microprocessor trainer kits.

8085A based system is not just a calculating machine. It is also used for control applications. For this some I/O port lines are needed to communicate the control signals to and fro between microprocessor and the device.

Such interfacing of input device, output device and I/O port lines with the processors is called I/O interfacing.

In the present work the keyboard and display controller chip 8279 is used for interfacing the hex keyboard and seven segment display. Also the programmable peripheral interface chip 8255 is employed for interfacing I/O port lines with 8085A.

## 5.1 Programmable keyboard display interface 8279

This chip is useful to interface the keyboard and display with 8085 microprocessor. It has been introduced by Intel. [6]

The advantage of interfacing 8279 with 8085A over other techniques are as follows.

- It relives microprocessor from scanning keyboard & refreshing displays.

- It also takes care about debouncing of key and blanking display while scanning.

- It can perform simultaneous keyboard display operation.

- The scan time for display is programmable.

- It can operate in different modes.

## 5.1.1. Block diagram of 8279

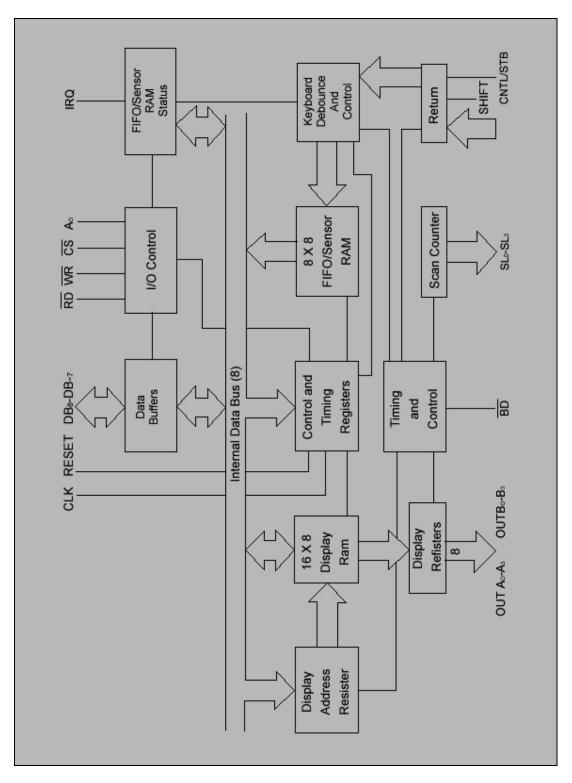

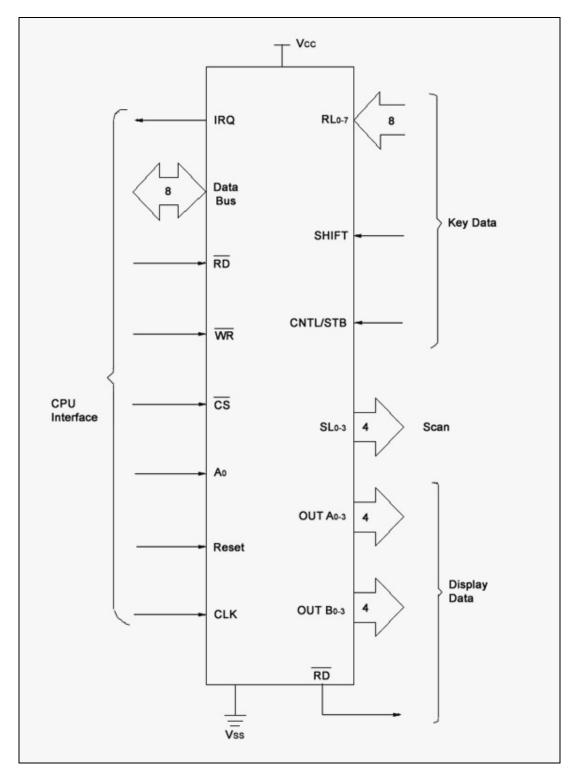

Block diagram of 8279 is shown in Figure 5.1.1. The block diagram is divided into following units.

- 1. Data buffer.

- 2. I/O control.

- 3. FIFO/sensor RAM status.

- 4. Display address Registers.

- 5. 16X8 Display RAM.

- 6. 8X8 FIFO/sensor RAM.

- 7. Scan counter.

- 8. Return.

- 9. Keyboard Debounce & control.

- 10. Display registers.

- 11. Control & Timing registers.

- 12. Timing & Control.

Figure 5.1.1 Block Diagram of 8279

## 1. Data buffer

This block interfaces the data lines of 8279 with the system data bus. It takes control words from 8085A to 8279 as well as data to and fro. It is represented by directional arrow.

## 2. I/O control

In this unit the pins  $\overline{CS}$ ,  $A_0$ ,  $\overline{RD}$  and  $\overline{WR}$  are associated. The combinations of low or high status of these signals determine the direction of data to and fro between 8085A and 8279.

Following Table 5.1.1. explains the various conditions of input output data communication between 8085A and 8279.

| CS | A <sub>0</sub> | RD | WR | Meaning          |

|----|----------------|----|----|------------------|

| 0  | 0              | 0  | 0  | No meaning       |

| 0  | 0              | 0  | 1  | System data      |

|    |                |    |    | bus $\leq D_0 -$ |

|    |                |    |    | D7 of 8279       |

| 0  | 0              | 1  | 0  | No meaning       |

| 0  | 0              | 1  | 1  | No meaning       |

| 0  | 1              | 0  | 0  | Status word      |

|    |                |    |    | => system        |

|    |                |    |    | data bus         |

| 0  | 1              | 0  | 1  | Control words    |

|    |                |    |    | from system      |

|    |                |    |    | data bus =>      |

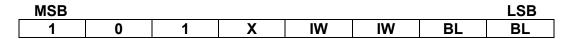

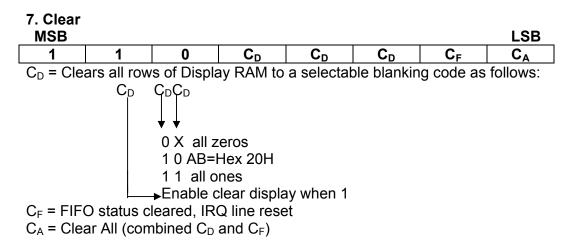

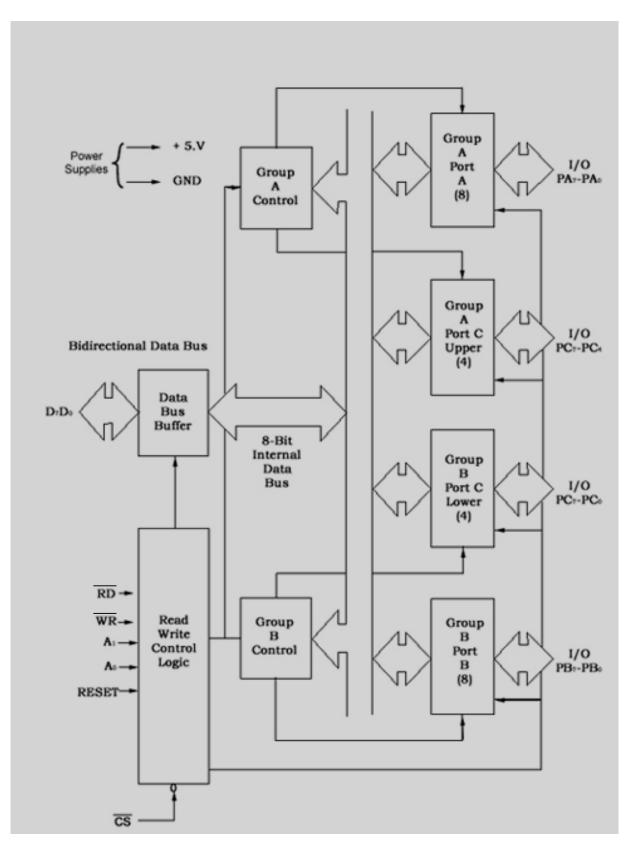

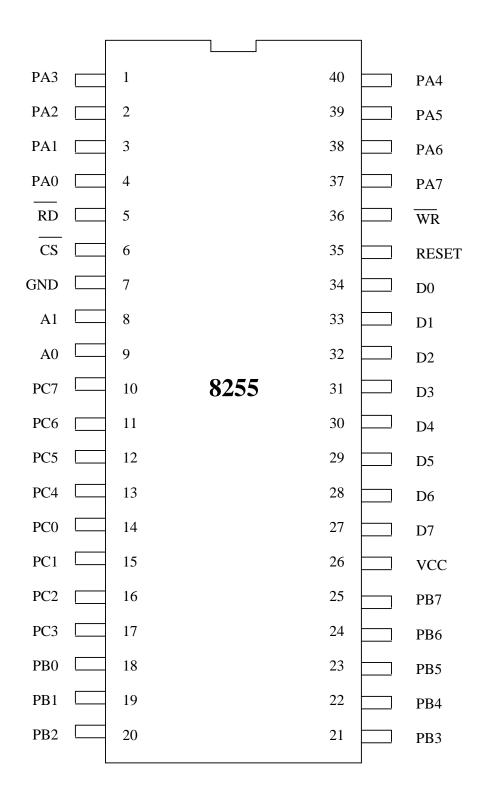

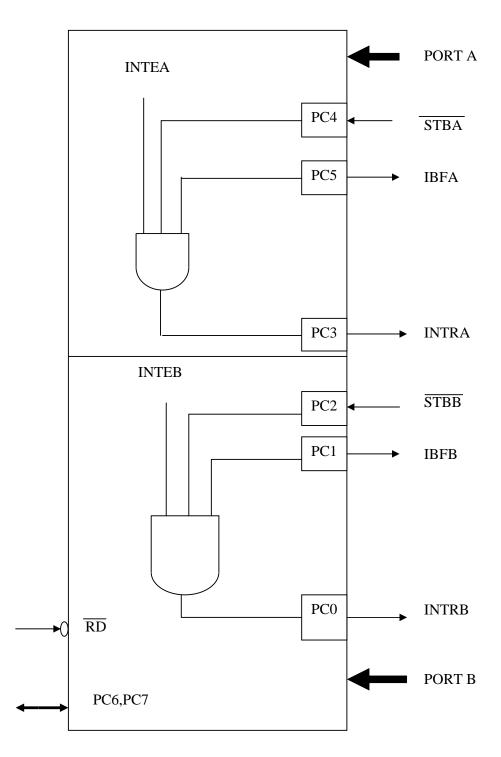

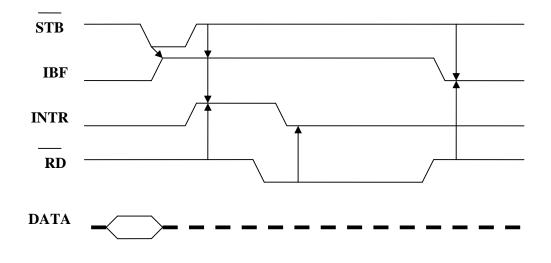

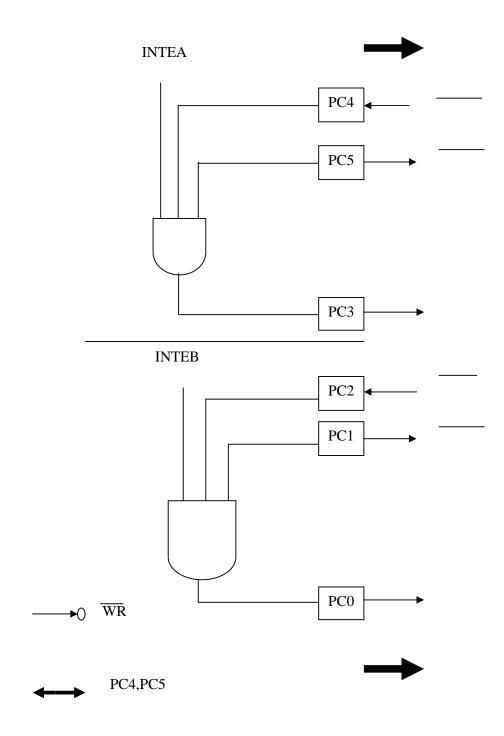

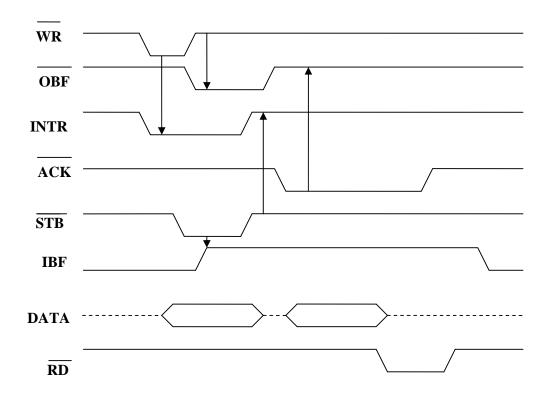

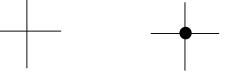

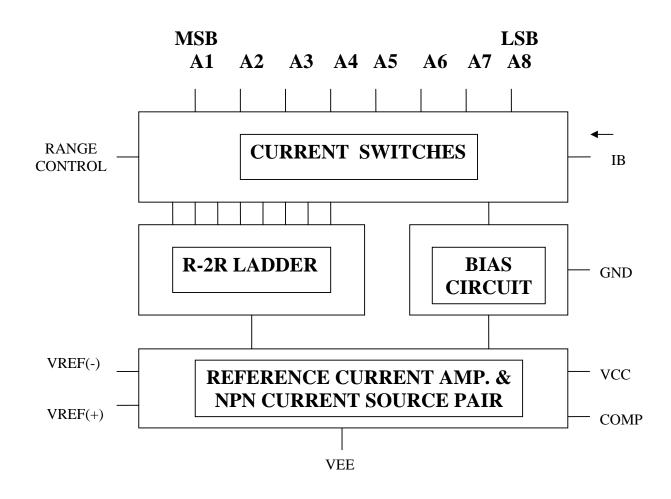

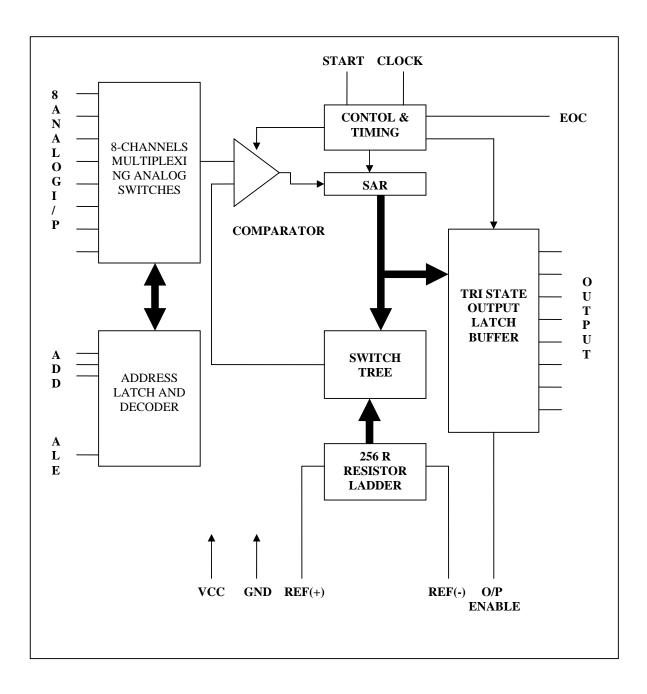

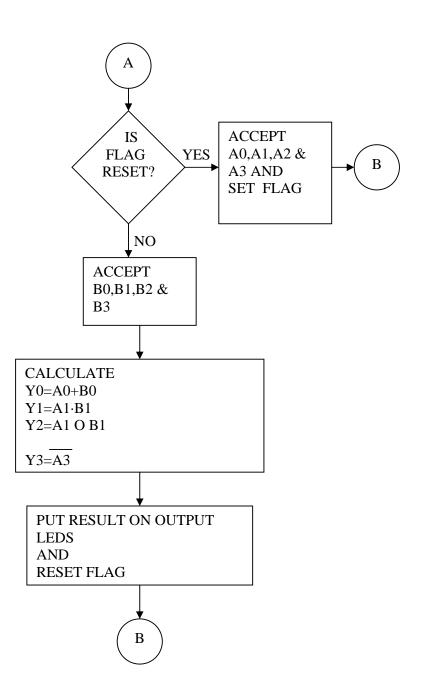

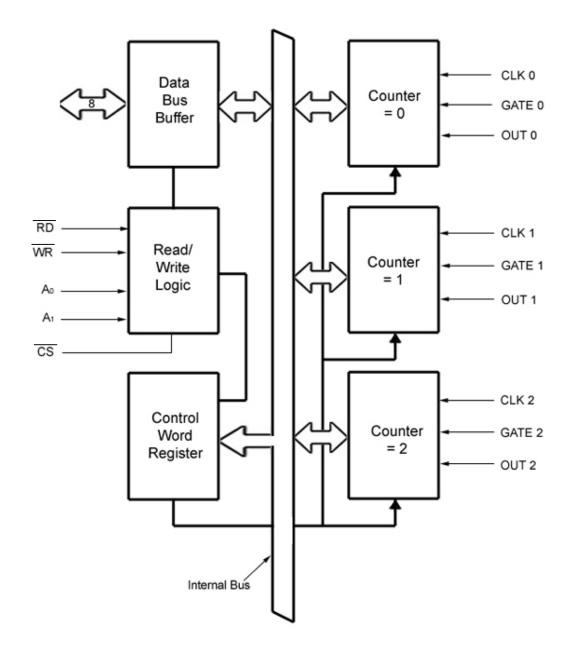

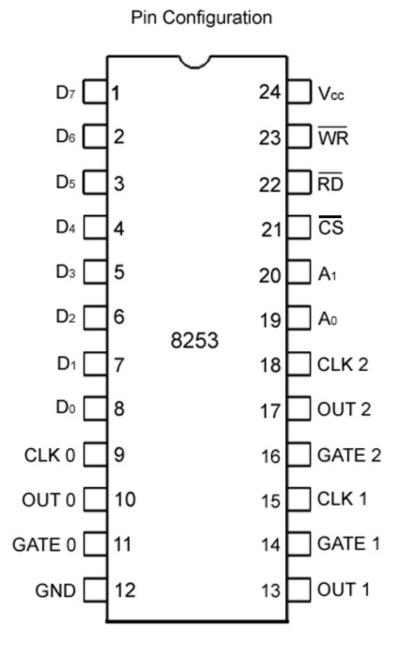

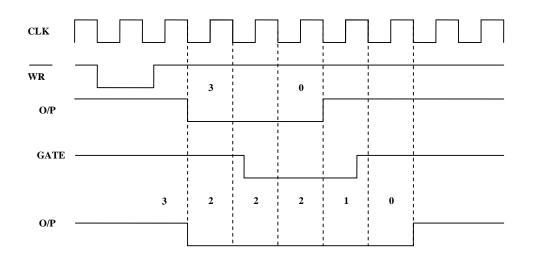

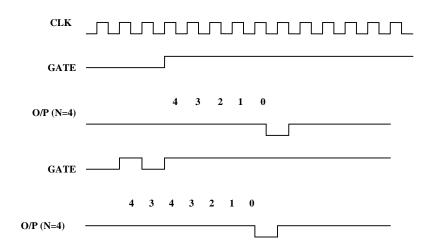

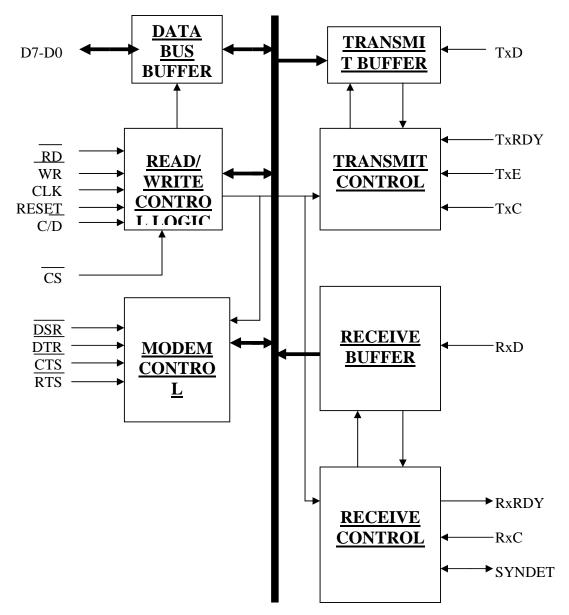

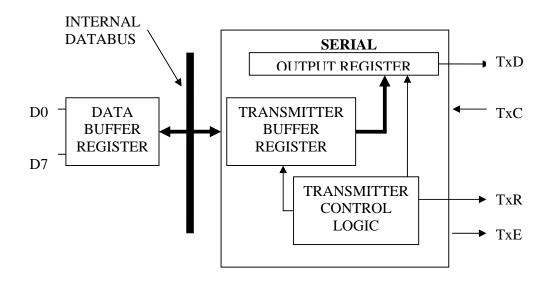

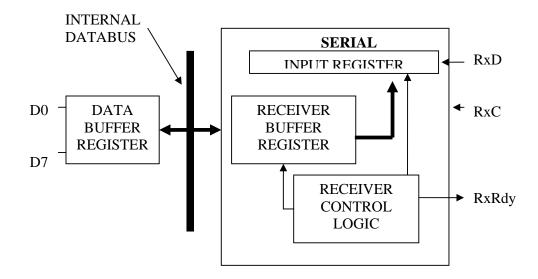

|    |                |    |    | $D_0 - D_7$ of   |