### Soft-error Tolerant Quasi Delay-insensitive Circuits

Thesis by Wonjin Jang

In Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

California Institute of Technology Pasadena, California

2008

(Defended September 11, 2007)

© 2008

Wonjin Jang

All Rights Reserved

## Acknowledgments

The journey at Caltech was an incredible experience to me, for its people, its traditions, and its enormous accumulated wealth of scientific knowledge. Lots of people have helped me to finish the journey. Obviously things would have been different without them.

First of all, I would like to thank my advisor Alain J. Martin for being my mentor. He has taught me the importance of choosing right research problems, which are not trivial but not intractable; he helped me to choose a right problem and to solve the problem, which is all about this thesis. Mika Nyström, a former post-doc of the Asynchronous VLSI Group at Caltech, has urged me to write everything succinctly and correctly not only in logic but also in English. He is the best critic for me. Most of chapters owe much of their clarity to Mika's demands. Remaining errors are mine. In addition to that, I wish to thank the members of the Friday morning meeting for many insightful discussions: Sean Keller, Chris Moore, Niki Mehta, Karl Papadantonakis, Jonathan Dama, and Piyush Prakash.

Byung-Jun Yoon at Caltech, has always been supportive of me in every aspect. I cannot imagine my life at Caltech without him; we have shared happiness and bitterness of graduate-student life together. I am lucky to meet such a friend during my life time. Juneseuk Shin, my high-school buddy, has kept me from taking a compromising answer for life. Even when I was frustrated by gap between reality and expectation, he encouraged me not to give up my faith on life and people. Moreover, he always shares his acute observation on life while he introduce insightful books and beautiful works of music. As he is my life-time resourceful friend, I hope to inspire him intellectually and religiously. Certainly I remember many delightful conversations with Jina Choi, Wonhee Lee, Ji Hun Kim, Hyunjoo Lee, Chihoon Ahn, Seung-yub Lee, and Nayoung Ko, who have helped me to survive here in different ways.

I owe a lot of my life-time learning to Rev. Byung-Joo Song, Rev. Dong Hwan Kim and Jung-Suk Kim, whom I have met in my church and in the Monday bible-study meeting.

They have shared with me their understanding, passion and love for God and people. I appreciate that I could meet these spiritual mentors, who have enriched my life, and have made me pursue what God tells us to do throughout life. Additionally, I would like to thank the undergraduate members of the bible-study meeting for their devotion to the meeting and Him: Hwan-seung Yeo, Jinwoo Lee, and Eui Woong Lee.

My uncle, Ki-young Kim, and my cousins, Moon-suk Kim, and Moon-sun Kim give me a warm welcome whenever I visit Korea. I am very glad to have a chance to say my appreciation to them.

Last, this thesis is dedicated to my parents, who started all this; I would like to give all my thanks to my parents for their supports and their love, hoping that my achievement comforts my mother, who have had hard time to take care of my lovely little sister, Moonjung Jang. Although all I have come from theirs, especially I have learned sincerity from my mother and curiosity from my father, which are precious assets for me. I am sad to say that my father did not live to see me finish this thesis, but I am sure that he sees this in the Heaven.

I know that I have failed to follow His way many times, but I still admit that I cannot finish this without the belief that Jesus Christ is the way, the truth, and the life. Now I embark upon a new journey, through which I wish to be one step closer to Him.

### Abstract

A hard error is an error that damages a circuit irrevocably; a soft error flips the logic states without causing any physical damage to the circuit, resulting in transient corruption of data. They result in transient, inconsistent corruption of data.

The soft-error tolerance of logic circuits is recently getting more attention, since the soft-error rate of advanced CMOS devices is higher than before. As a response to the concern on soft errors, we propose a new method for making asynchronous circuits tolerant to soft errors. Since it relies on a property unique to asynchronous circuits, the method is different from what is done in synchronous circuits with triple modular redundancy. Asynchronous circuits have been attractive to the designers of reliable systems, because of their clock-less design, which makes them more robust to variations on computation time of modules. The quasi delay-insensitive (QDI) design style is one of the most robust asynchronous design styles for general computation; it makes one minimal assumption on delays in gates and wires. QDI circuits are easy to verify, simple, and modular, because the correct operation of a QDI circuit is independent of delays in gates and wires.

Here, we shall overview how to design a QDI circuit, and what will happen if a soft error occurs on a QDI circuit. Then the crucial components of the method are shown: (1) a special kind of duplication for random logic (when each bit has to be corrected individually), (2) special protection circuitry for arbiter and synchronizer (as needed for example for external interrupts), (3) reconfigurable circuits using a special configuration unit, and (4) error correcting for memory arrays and other structures in which the data bits can be self-corrected. The solution of protecting random logic is compared with alternatives, which use other types of error correcting codes (e.g., parity code) in a QDI circuit. It turns out that the duplication generates efficient circuits more commonly than other possible constructions. Finally, the design of a soft-error tolerant asynchronous microprocessor is detailed and testing results of the soft-error tolerance of the microprocessor are shown.

## Contents

| A  | ckno           | wledgr  | nents                                                     | ii |

|----|----------------|---------|-----------------------------------------------------------|----|

| A  | bstra          | act     |                                                           | v  |

| Li | st of          | Figur   | es                                                        | ix |

| Li | st of          | Table   | ${f s}$                                                   | хv |

| 1  | Inti           | roduct  | ion                                                       | 1  |

| 2  | Des            | signing | Quasi Delay-insensitive (QDI) Circuits                    | 4  |

|    | 2.1            | Comm    | nunicating Hardware Processes                             | 4  |

|    | 2.2            | Hands   | Shaking Expansion                                         | 5  |

|    | 2.3            | Produ   | ction Rule Set and PRS Computation                        | 6  |

|    | 2.4            | Exam    | ple of QDI Circuits: Buffer                               | 8  |

| 3  | Sof            | t Erroi | rs in QDI Circuits                                        | 12 |

|    | 3.1            | Errors  | s on Circuits                                             | 12 |

|    | 3.2            | Digita  | l Model of Soft Errors                                    | 14 |

|    | 3.3            | Analo   | g Model of Soft Errors                                    | 17 |

| 4  | $\mathbf{Rel}$ | ated V  | Vork                                                      | 20 |

| 5  | $\mathbf{Pro}$ | tectin  | g QDI Circuits from Soft Errors by Design                 | 23 |

|    | 5.1            | Dupli   | cating QDI Circuits with Cross-coupled C-elements         | 24 |

|    |                | 5.1.1   | Duplicated Double-checking QDI Circuit                    | 24 |

|    |                | 5.1.2   | Comparing Reliability of QDI Circuits and DD QDI Circuits | 31 |

|    |                | 5.1.3   | Simulation Results of Duplicated Double-checking Buffer   | 35 |

|   |                        | 5.1.4   | Summary                                                                             | 40  |

|---|------------------------|---------|-------------------------------------------------------------------------------------|-----|

|   | 5.2                    | Arbite  | er with Mutual Excluders                                                            | 40  |

|   |                        | 5.2.1   | Overview                                                                            | 40  |

|   |                        | 5.2.2   | Designing Error Tolerant Arbiter for DD Circuits                                    | 43  |

|   |                        | 5.2.3   | ${\bf Mutual\ Exclusion\ of\ Outputs\ of\ Duplicated\ Error\ Tolerant\ Arbiter\ .}$ | 49  |

|   |                        | 5.2.4   | Simulation Results of Error Tolerant Arbiter                                        | 52  |

|   |                        | 5.2.5   | Summary                                                                             | 52  |

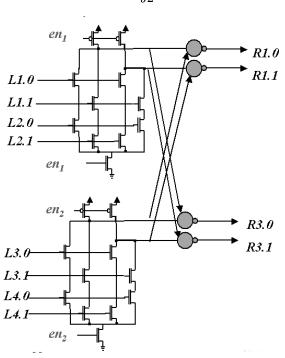

|   | 5.3                    | Dupli   | cated FPGA Using Self-correcting Programmable Bits                                  | 54  |

|   |                        | 5.3.1   | Overview                                                                            | 54  |

|   |                        | 5.3.2   | Designing Error Tolerant FPGA Cells                                                 | 54  |

|   |                        | 5.3.3   | Summary                                                                             | 57  |

|   | 5.4                    | Self-co | orrecting Memory and Hamming-coded Memory                                           | 57  |

|   |                        | 5.4.1   | Overview                                                                            | 57  |

|   |                        | 5.4.2   | Error Tolerant Memory Using Self-correcting Memory Cells                            | 60  |

|   |                        | 5.4.3   | Error Tolerant Memory Based on Hamming Code                                         | 62  |

|   |                        | 5.4.4   | Simulation Results of Error Tolerant Memory                                         | 72  |

|   |                        | 5.4.5   | Summary                                                                             | 74  |

| 6 | $\mathbf{Q}\mathbf{D}$ | I Circ  | uits using Error Detecting Delay-insensitive Codes                                  | 76  |

|   | 6.1                    | Error   | Detecting Delay-insensitive (EDDI) Code                                             | 76  |

|   |                        | 6.1.1   | Definition of Delay-insensitive Codes                                               | 76  |

|   |                        | 6.1.2   | Definition of Error Detecting Delay-insensitive Codes                               | 77  |

|   |                        | 6.1.3   | Error Detecting Delay-insensitive Code Based on Linear Code                         | 79  |

|   | 6.2                    | Basic   | Component of QDI Circuit: Function Block and Completion Checker                     | 82  |

|   | 6.3                    | Error   | Tolerant Function Block for Linear DI Code                                          | 84  |

|   |                        | 6.3.1   | Designing Error Tolerant Precharging-Evaluating Logic                               | 85  |

|   |                        | 6.3.2   | Simplifying Based on Symmetry of Repetition Codes                                   | 89  |

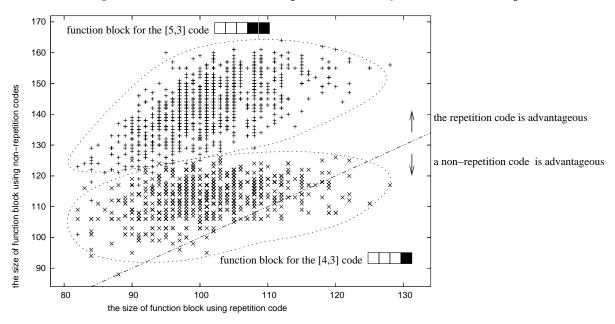

|   |                        | 6.3.3   | Comparing Size of Function Blocks for Different Linear DI Codes                     | 91  |

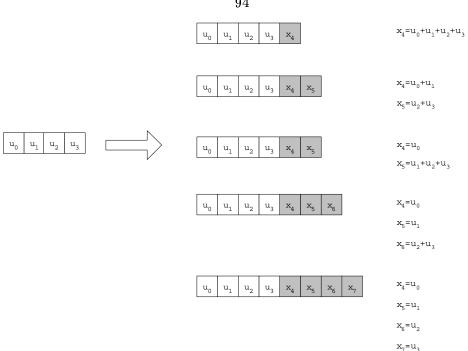

|   |                        | 6.3.4   | Function Blocks Using $r$ -error Linear DI Codes                                    | 94  |

|   | 6.4                    | Error   | Tolerant Completion Checker for Linear DI Code                                      | 97  |

|   | 6.5                    | Cost    | of Error Tolerant QDI Circuits for Different Linear DI Codes                        | 101 |

|   |                        | 6.5.1   | Size                                                                                | 102 |

|         |       | $6.5.2  Et^2  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 103         |

|---------|-------|--------------------------------------------------------------------------------|-------------|

|         | 6.6   | Simulation Results of QDI Circuits for Linear DI Codes                         | 108         |

|         | 6.7   | Summary                                                                        | 110         |

| 7       | Des   | sign Example: Soft-error Tolerant Asynchronous Microprocessor                  | 115         |

|         | 7.1   | Overview                                                                       | 115         |

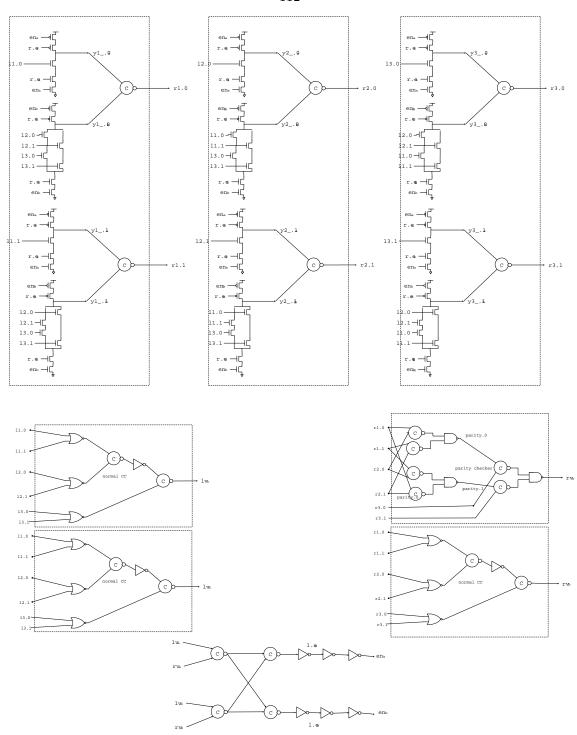

|         | 7.2   | Designing Soft-Error Tolerant PCUNIT from CHP Description to Layout $$ .       | 118         |

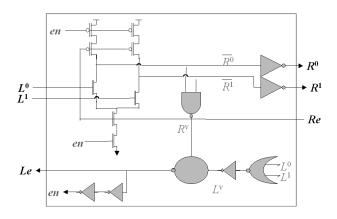

|         |       | 7.2.1 Implementing Arbitrated Branch                                           | 120         |

|         |       | 7.2.2 Implementing Body of PCUNIT                                              | 122         |

|         | 7.3   | Evaluating Soft-error Tolerant Asynchronous Microprocessor in Simulations      | 126         |

|         |       | 7.3.1 Verifying Soft-error Tolerance                                           | 126         |

|         |       | 7.3.2 Performance                                                              | 128         |

|         |       | 7.3.3 Comparing Overhead of Error Tolerance                                    | 130         |

|         | 7.4   | Summary                                                                        | 133         |

| 8       | Cor   | nclusion                                                                       | 134         |

|         | 8.1   | Lessons Learned                                                                | 134         |

|         | 8.2   | Future Work                                                                    | 135         |

| A       | Acr   | onym Glossary                                                                  | 136         |

| В       | Cor   | ntroller in Memory Unit                                                        | 138         |

| C       | Upp   | per Bound of the Size of Code                                                  | 141         |

| D       | Mir   | nimizing Decomposed Function Block                                             | <b>14</b> 4 |

| ${f E}$ | STA   | AM Architecture                                                                | 148         |

| F       | Arb   | pitrated Branch                                                                | 152         |

| G       | Des   | signing CHP Process Using Synthesis Tool Flow                                  | <b>15</b> 4 |

| н       | Che   | ecking Error Tolerance of PRS                                                  | 159         |

| Bi      | bliog | graphy                                                                         | 162         |

# List of Figures

| 1.1 | Pipeline of Buffers                                                                             | 1  |

|-----|-------------------------------------------------------------------------------------------------|----|

| 2.1 | Handshake Expansion of a Synchronization Channel                                                | 6  |

| 2.2 | Circuit and Environment.                                                                        | 8  |

| 2.3 | Transition Diagram of Precharged Half Buffer. Each state represents the                         |    |

|     | $values \ of \ (L.i,L.e,R.i,R.e). \ The \ double-circled \ state \ is \ the \ initial \ state.$ | 10 |

| 2.4 | Circuit Diagram of Precharged Half Buffer                                                       | 10 |

| 2.5 | Circuit Diagram of C-element and its Gate Diagram                                               | 11 |

| 3.1 | Interaction of a Particle and Silicon Substrate.                                                | 13 |

| 3.2 | Examples of Erroneous Computations Caused by Soft Error                                         | 15 |

| 3.3 | Transition Diagram of PCHB with Soft Error on L.e. The dotted circles                           |    |

|     | indicate invalid states, and the dotted edges indicate erroneous transitions                    |    |

|     | caused by an error on L.e                                                                       | 16 |

| 3.4 | Example of Normal Execution Path of Firings in PCHB                                             | 16 |

| 3.5 | Transition Diagram of Buffer with Soft Error on L.e. The dotted circles                         |    |

|     | indicate invalid states, and the dotted edges indicate erroneous transitions                    |    |

|     | caused by an error on L.e                                                                       | 17 |

| 3.6 | Pipeline of Buffers                                                                             | 19 |

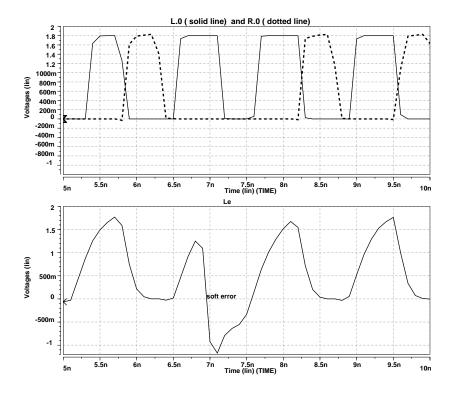

| 3.7 | $Wave forms\ of\ Input-channel\ Variable\ L.0\ and\ Output-channel\ Variable\ R.0,$             |    |

|     | and Input-channel Acknowledgment Variable L.e. A soft error on L.e at 7 ns                      |    |

|     | $causes\ premature\ acknowledgment\ of\ an\ input\ communication\ on\ L\ before\ an$            |    |

|     | output communication on $R$ is generated                                                        | 19 |

| 4.1  | TMR QDI Circuit. It cannot tolerate a soft error, because a soft error can             |    |

|------|----------------------------------------------------------------------------------------|----|

|      | abort the communication of data, which is hard to detect in an asynchronous            |    |

|      | system.                                                                                | 21 |

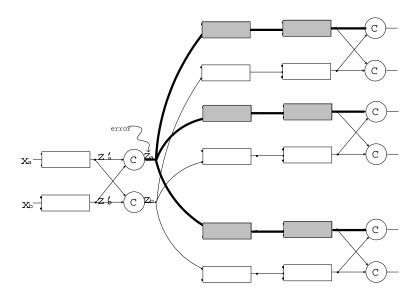

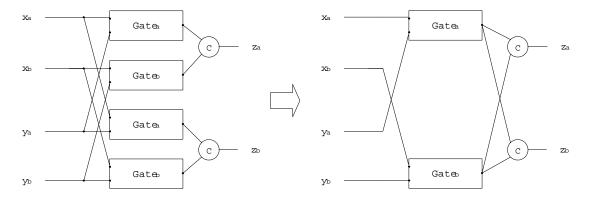

| 5.1  | Gate in Original Circuit and its Corresponding DD Gate in DD Circuit                   | 25 |

| 5.2  | Circuit and its Corresponding DD Circuit                                               | 25 |

| 5.3  | Soft Error on CO Variable. The propagation of an error is blocked by the               |    |

|      | next DD gates                                                                          | 29 |

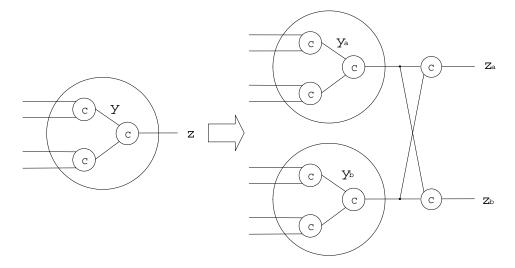

| 5.4  | DD Gate with weak C-elements. It can correct a corrupted CI variable in a              |    |

|      | state-holding state                                                                    | 30 |

| 5.5  | Tree of C-element and its corresponding DD Tree. The DD tree of C-elements             |    |

|      | requires cross-coupled C-elements only for the primary outputs                         | 31 |

| 5.6  | Precharged Half Buffer                                                                 | 36 |

| 5.7  | DD PCHB                                                                                | 38 |

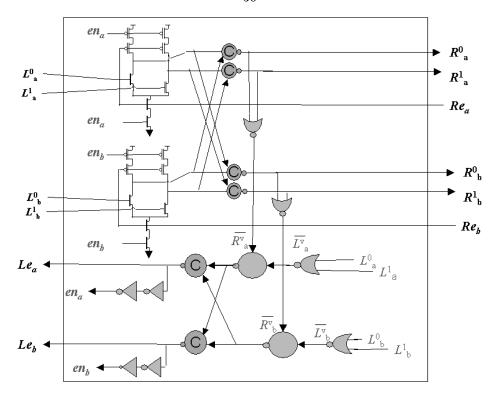

| 5.8  | $Wave forms\ of\ Inputs-channel\ Variable\ L0_a\ and\ Output-channel\ Variable\ R0_a,$ |    |

|      | and Input-channel Acknowledgment Variable $Le_a$ of DD One-bit Buffer. A               |    |

|      | soft error on Le <sub>a</sub> at 10 ns merely causes delay on an input communication   |    |

|      | on the input channel, which does not affect the correction of computation in           |    |

|      | a QDI circuit                                                                          | 39 |

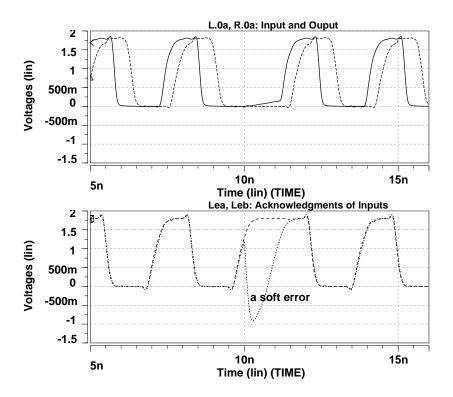

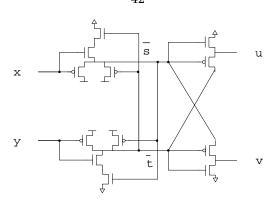

| 5.9  | Basic Arbiter. When all inputs $(x,y)$ are assigned to be 1 simultaneously, it         |    |

|      | provides the outputs of either $(1,0)$ or $(0,1)$ non-deterministically                | 42 |

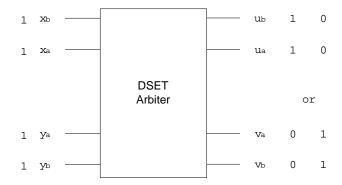

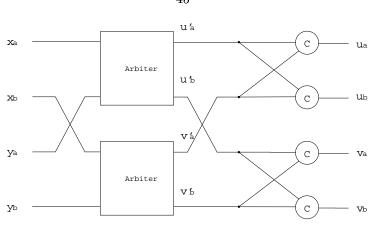

| 5.10 | Duplicated Soft-error Tolerant Arbiter. When all inputs are assigned to be 1           |    |

|      | simultaneously, it provides the outputs of either $(1,1,0,0)$ or $(0,0,1,1)$ non-      |    |

|      | deterministically                                                                      | 43 |

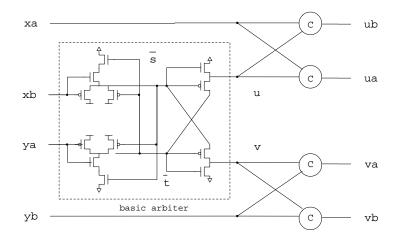

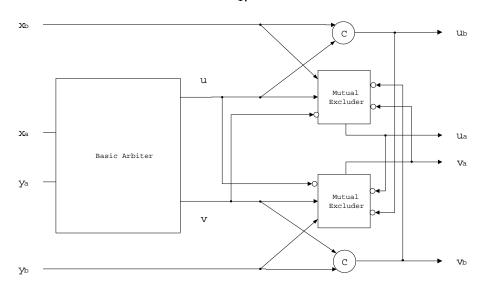

| 5.11 | DD Arbiter (does not work)                                                             | 45 |

| 5.12 | Arbiter with Double-checking C-elements (does not work)                                | 46 |

| 5.13 | Block Diagram of Soft-error Tolerant Arbiter                                           | 47 |

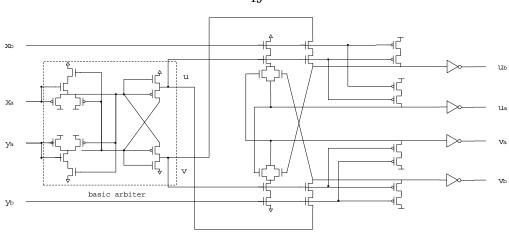

| 5.14 | Pass-gate Soft-error Tolerant Arbiter                                                  | 49 |

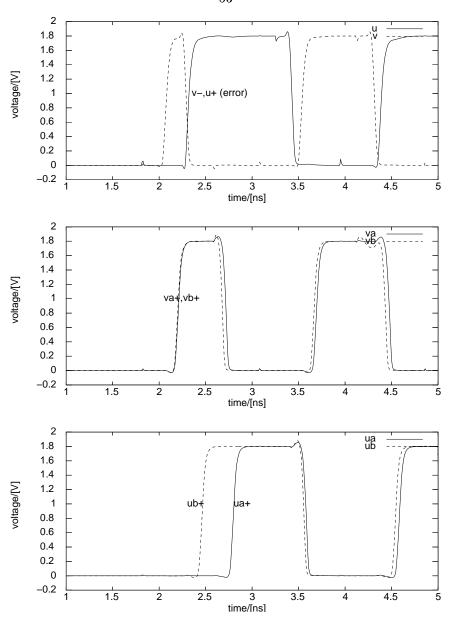

| 5.15 | Waveforms for Nodes in DSET Arbiter. After the duplicated inputs arrive                             |    |

|------|-----------------------------------------------------------------------------------------------------|----|

|      | simultaneously, an error in the basic arbiter at 2.2 ns causes $v\downarrow$ and $u\uparrow$ (i.e., |    |

|      | the result from a basic arbiter is flipped). Although the transition of one of                      |    |

|      | the duplicated output $u_b \uparrow$ occurs, the transition of the other output $u_a \uparrow$ does |    |

|      | not occur until the previous arbitration (i.e., $v_a \uparrow$ , $v_b \uparrow$ ) is acknowledged   | 53 |

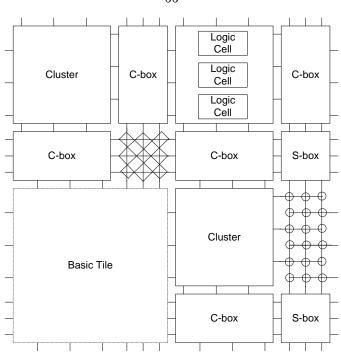

| 5.16 | FPGA Architecture                                                                                   | 55 |

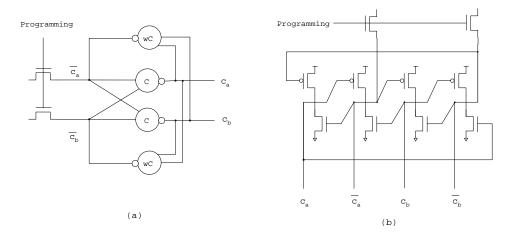

| 5.17 | (a) Double-checked Programmable Bit (b) Programmable Bit based on Dual                              |    |

|      | Interlocked Cell                                                                                    | 56 |

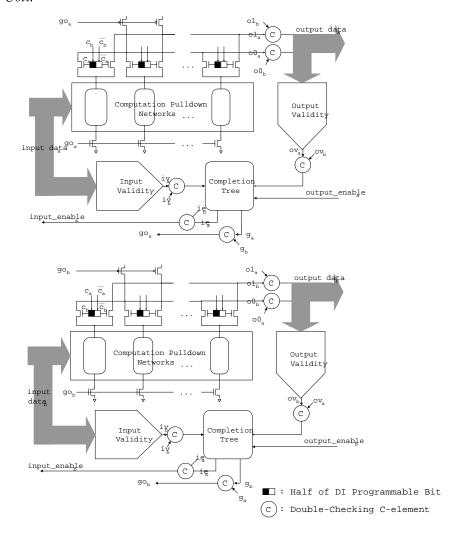

| 5.18 | Block Diagram of Soft-error Tolerant FPGA Logic Cell                                                | 56 |

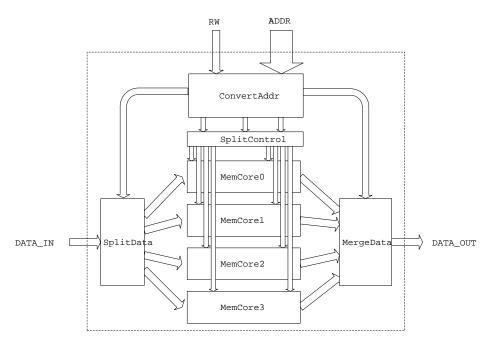

| 5.19 | Decomposition of Memory Unit                                                                        | 59 |

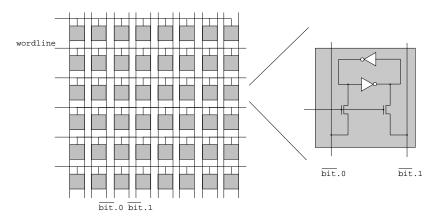

| 5.20 | Array of Storage Elements                                                                           | 60 |

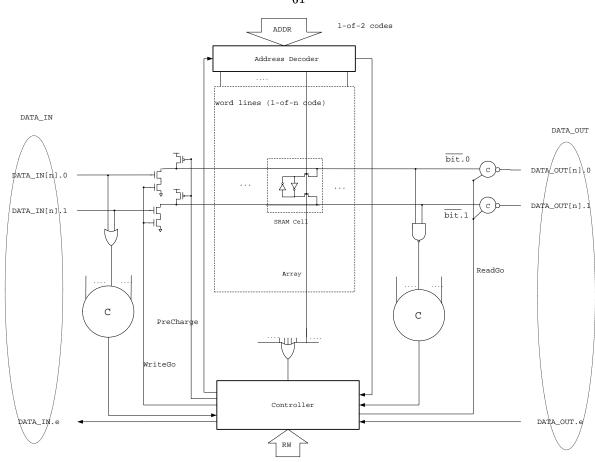

| 5.21 | Circuit of Mermoy Core                                                                              | 61 |

| 5.22 | Calin's Dual Interlocked Cell (DICE)                                                                | 62 |

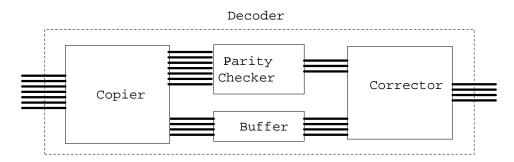

| 5.23 | Decomposition of [7,4] Hamming-code Decoder. Each solid line represents a                           |    |

|      | one-of-two code channel                                                                             | 65 |

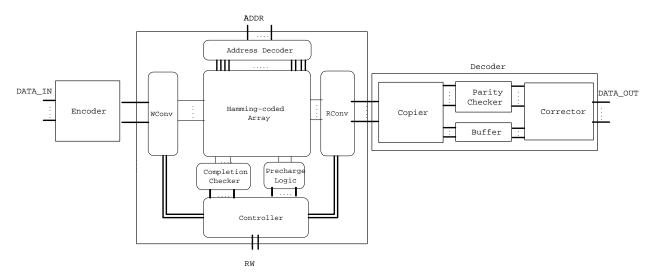

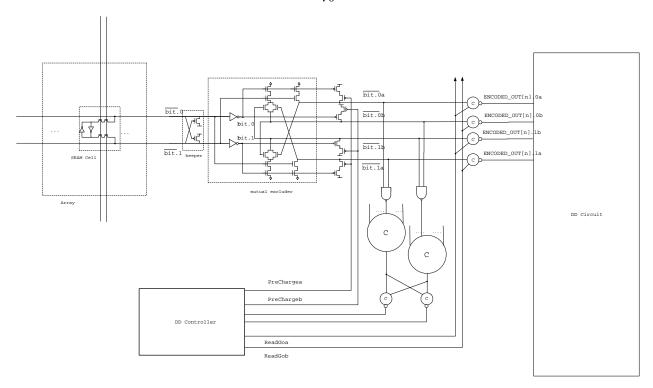

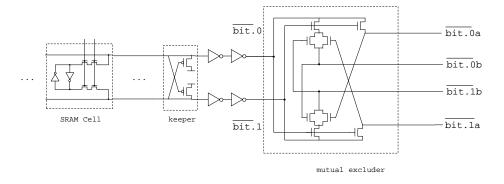

| 5.24 | Block Diagram of Memory Core Using Hamming Code                                                     | 65 |

| 5.25 | Converting a Duplicated Codeword into a Hamming Codeword                                            | 66 |

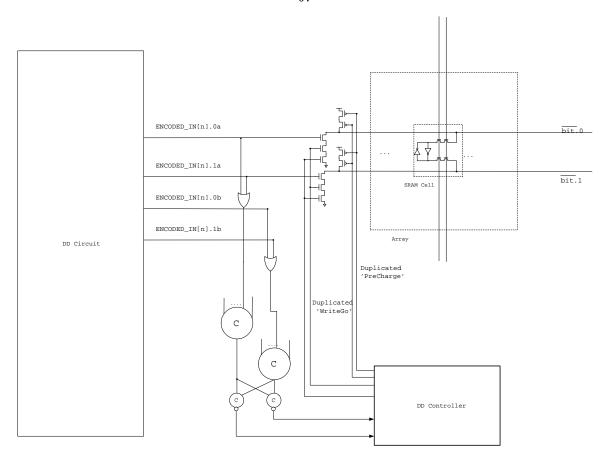

| 5.26 | Interface Between DD Circuit and Input Side of Memory Unit                                          | 67 |

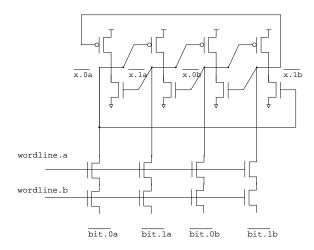

| 5.27 | Copying the Bit Lines of the Array (does not work)                                                  | 68 |

| 5.28 | Copying the Bit Lines with Filter (does not work)                                                   | 68 |

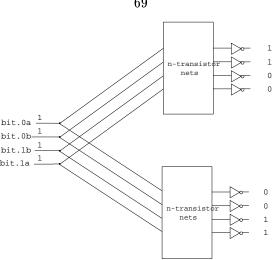

| 5.29 | Problematic Case of Invalid Bit Lines                                                               | 69 |

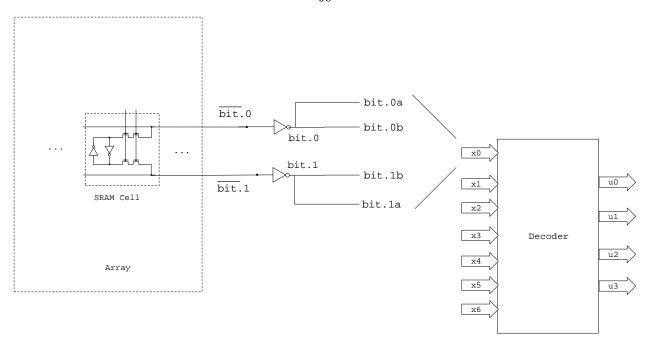

| 5.30 | Interface Between Output Side of Memory Unit and DD Circuit                                         | 70 |

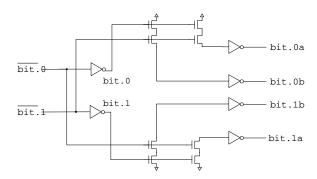

| 5.31 | Mutual Excluder Based on Pass-gate Transformation.                                                  | 70 |

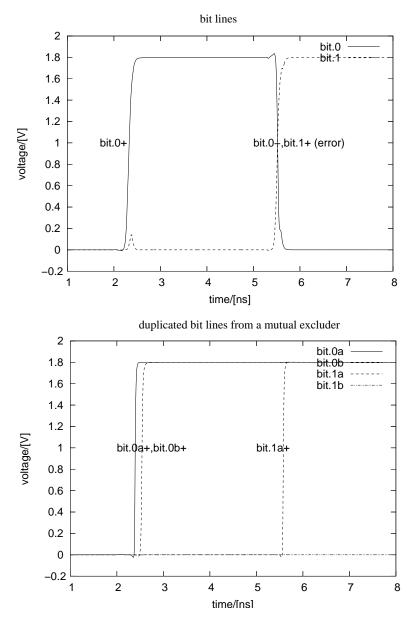

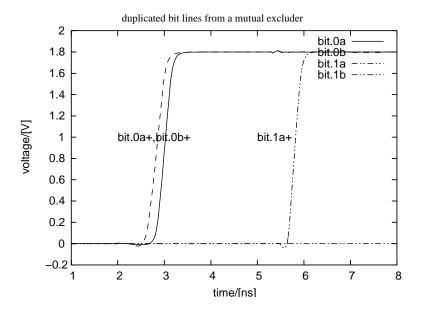

| 5.32 | Waveforms for Bit Lines and Duplicated Bit Lines from Mutual Excluder.                              |    |

|      | Although two bit lines are flipped simultaneously, only one of the duplicated                       |    |

|      | bit lines is flipped, owing to a mutual excluder.                                                   | 71 |

| 5.33 | Waveforms for Duplicated Bit Lines from Pass-gate Mutual Excluder. An                               |    |

|      | error, which flips bit lines, occurs at 5.5 ns                                                      | 72 |

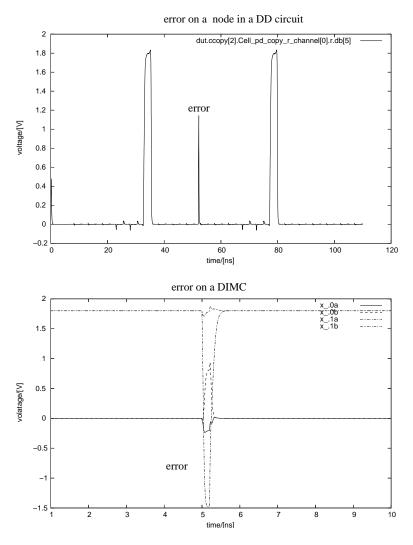

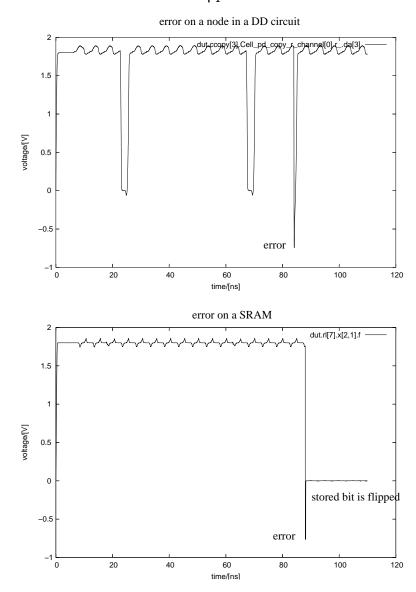

| 5.34 | Soft Errors on Register File Using DICE. An error in the regfile is corrected                       |    |

|      | quickly                                                                                             | 73 |

| 5.35 | Soft Errors on a Hamming-coded Memory. An error in a DD circuit is corrected quickly, but an error on an SRAM in a Hamming-coded array remains |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | uncorrected                                                                                                                                    | 74  |

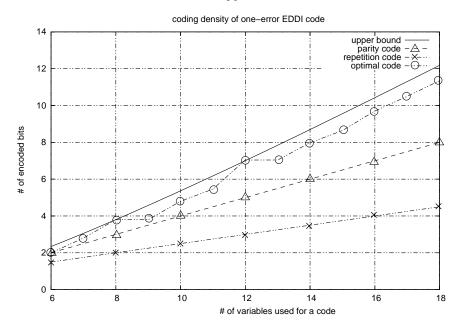

| 6.1  | One Error Detecting Delay-insensitive Codes and their Upper Bounds                                                                             | 80  |

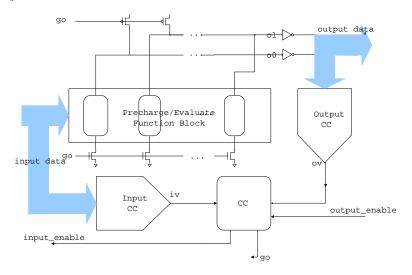

| 6.2  | Block Diagram of PCHB                                                                                                                          | 82  |

| 6.3  | Block Diagram of WCHB                                                                                                                          | 82  |

| 6.4  | Example of Delay-insensitive Minterm Logic (Adder)                                                                                             | 83  |

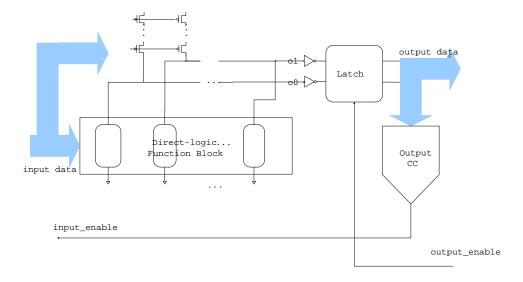

| 6.5  | Example of Direct Logic (Adder)                                                                                                                | 83  |

| 6.6  | Example of Precharging-evaluating Logic (Adder)                                                                                                | 84  |

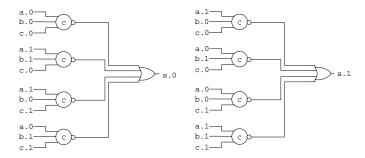

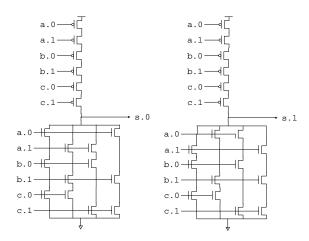

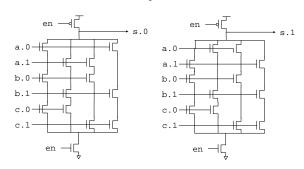

| 6.7  | Part of Function Block of Buffer for [3,2] Parity Code                                                                                         | 89  |

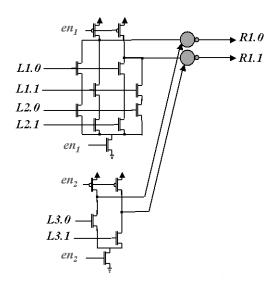

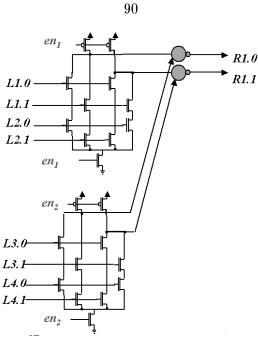

| 6.8  | Part of Function Block of Buffer for [4,2] Repetition Code                                                                                     | 90  |

| 6.9  | Function Block for Repetition Code and its Simplified Function Block. Re-                                                                      |     |

|      | dundant gates of an original function block are removed                                                                                        | 91  |

| 6.10 | Simplified Function Block for Repetition Code. The DD scheme, which du-                                                                        |     |

|      | plicates a gate and adds cross-coupled C-elements, leads to the same design.                                                                   | 92  |

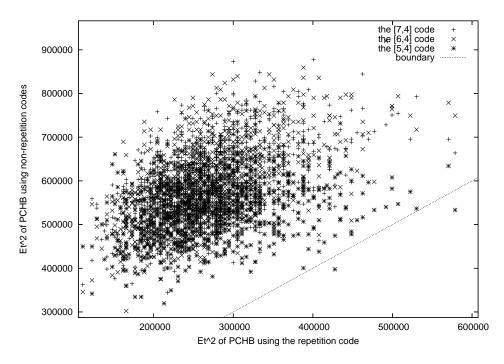

| 6.11 | One-error Detecting Linear Codes for Four-Bit Message                                                                                          | 94  |

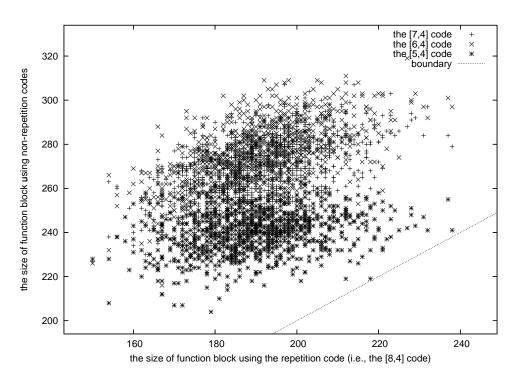

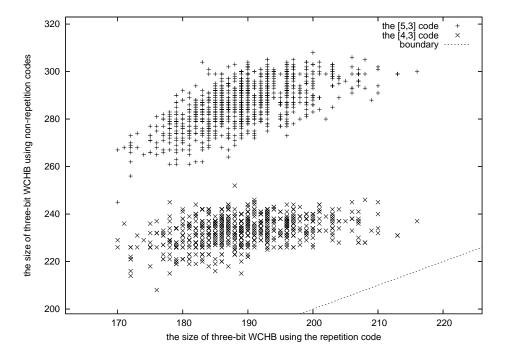

| 6.12 | Three-bit Function Blocks based on Repetition Codes vs Non-repetition Codes.                                                                   |     |

|      | The x-coordinate and the y-coordinate of each point correspond to the size of                                                                  |     |

|      | a function block using the repetition code, and the size of a function block                                                                   |     |

|      | using a non-repetition code (e.g., the [4,3] code and the [5,3] code)                                                                          | 94  |

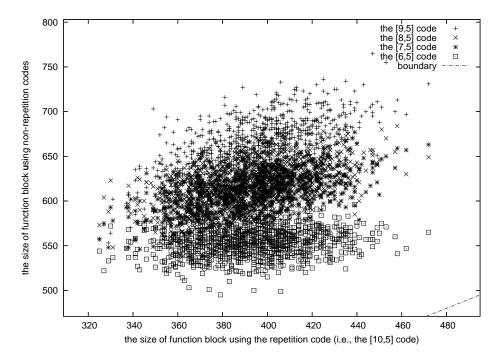

| 6.13 | Four-bit Function Blocks based on the Repetition Codes vs Non-repetition                                                                       |     |

|      | Codes.                                                                                                                                         | 95  |

| 6.14 | $Five-bit\ Function\ Blocks\ based\ on\ the\ Repetition\ Codes\ vs\ Non-repetition\ Codes.$                                                    | 95  |

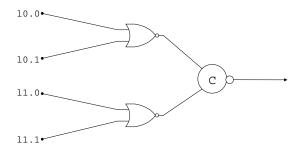

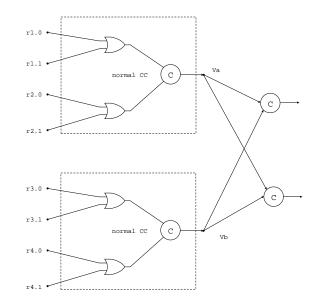

| 6.15 | CC for Concatenation of Two One-of-two Codes                                                                                                   | 97  |

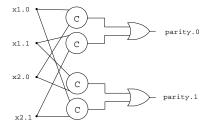

| 6.16 | Two-input Parity Checker                                                                                                                       | 99  |

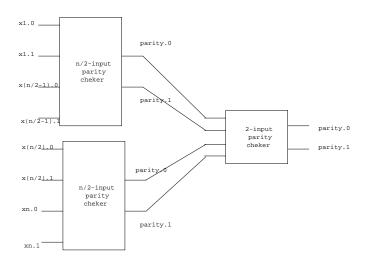

| 6.17 | Parity Decomposition                                                                                                                           | 99  |

| 6.18 | CC for the [3,2] code                                                                                                                          | 100 |

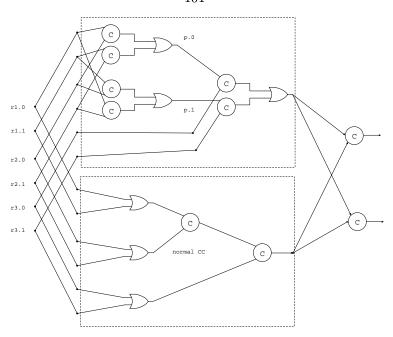

| 6.19 | Simplified CC for the [3,2] code                                                                                                               | 101 |

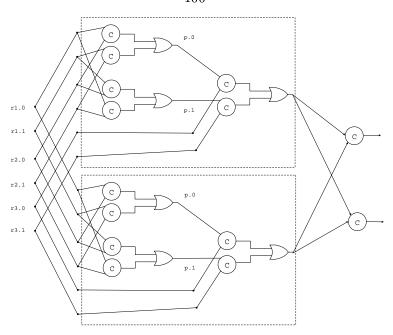

| 6.20 | CC for the [4,2] Code                                                                                                                          | 101 |

| 6.21 | Size Comparison of Three-bit WCHB Processes                                                                                                    | 102 |

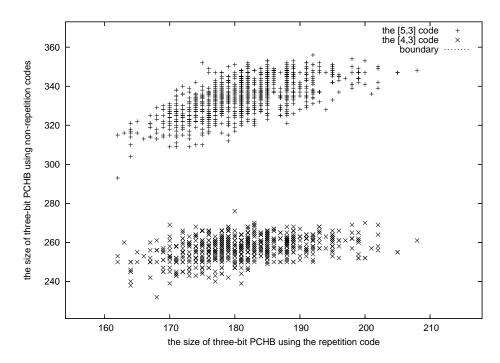

| 6.22 | Size Comparison of Three-bit PCHB Processes. The PCHB using a repetition        |     |

|------|---------------------------------------------------------------------------------|-----|

|      | code is always smaller than the PCHB using a non-repetition code, so that       |     |

|      | the boundary is located outside the range of the figure.                        | 103 |

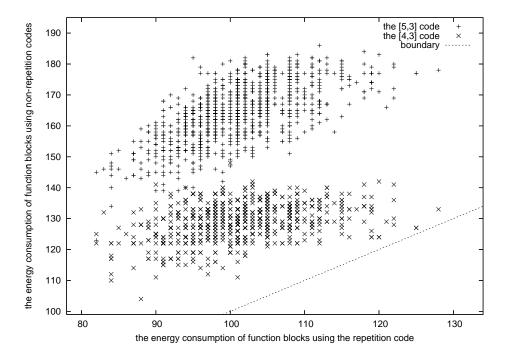

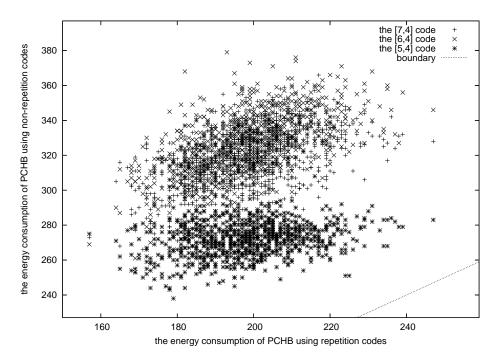

| 6.23 | Energy Distribution of Three-bit Function Blocks                                | 106 |

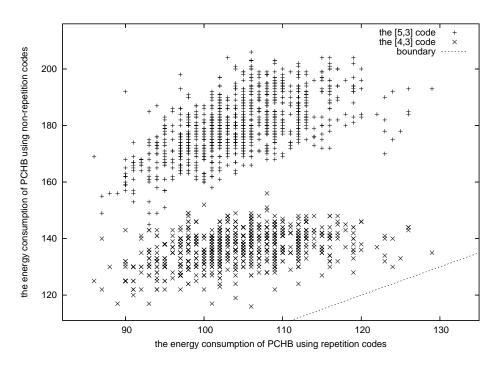

| 6.24 | Energy Distribution of Three-bit PCHB Processes                                 | 107 |

| 6.25 | Energy Distribution of Four-bit PCHB Processes                                  | 107 |

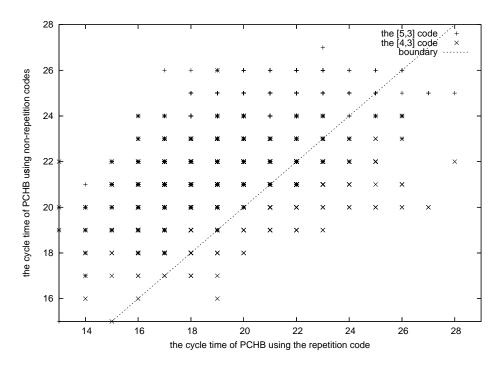

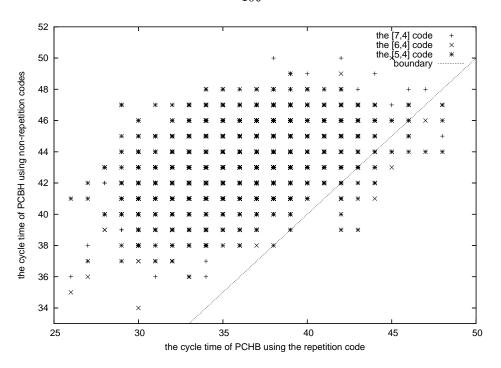

| 6.26 | Distribution of Cycle Time of Three-bit PCHB Processes                          | 108 |

| 6.27 | Distribution of Cycle Time of Four-bit PCHB Processes                           | 109 |

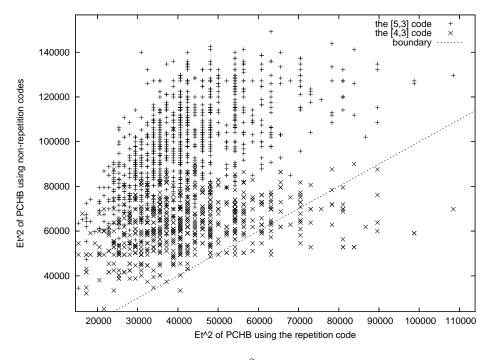

| 6.28 | Distribution of $Et^2$ of Three-bit PCHB Processes                              | 109 |

| 6.29 | Distribution of $Et^2$ of Four-bit PCHB Processes                               | 110 |

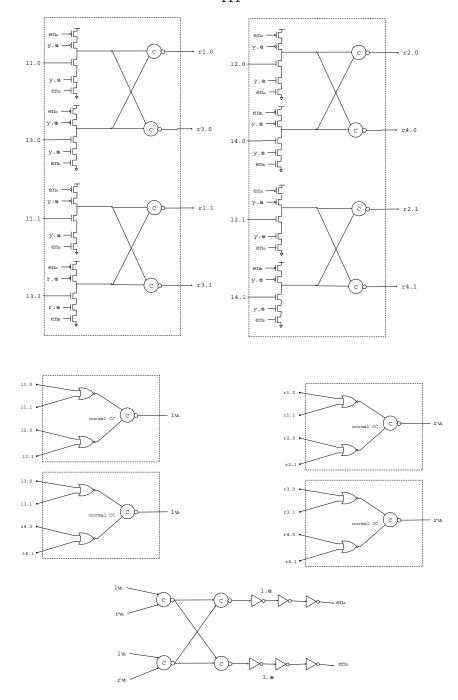

| 6.30 | PCHB based on the [4,2] Repetition Code. It is equivalent to the DD circuit     |     |

|      | of a 2-bit normal PCHB                                                          | 111 |

| 6.31 | PCHB based on the [3,2] Parity Code                                             | 112 |

| 6.32 | Waveforms of Input and Output Channel Nodes of PCHB based on the [3,2]          |     |

|      | Parity Code. Until an error on the first bit of the input channel is corrected, |     |

|      | all transitions of output-channel nodes are delayed                             | 113 |

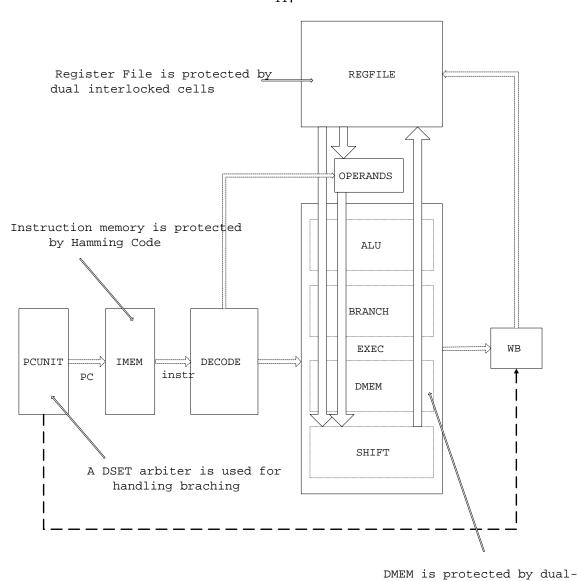

| 7.1  | Decomposition of the STAM. The dotted arrows denote control flows, and          |     |

|      | block arrows denote data flows. Most of the units are protected by the DD       |     |

|      | scheme.                                                                         | 117 |

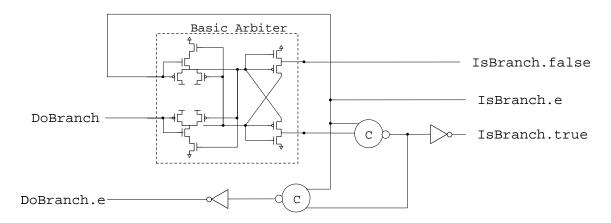

| 7.2  | Circuit for Probing Branch. If there is a pending communication on the          |     |

|      | channel DoBranch, then the value of the channel IsBranch is assigned to be      |     |

|      | true. If not, the value is assigned to be false.                                | 122 |

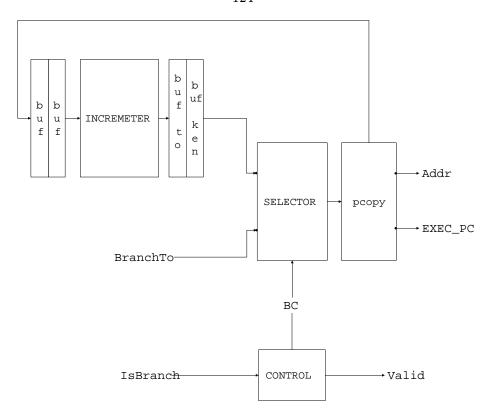

| 7.3  | Process Graph of PCUNIT_NOARB                                                   | 124 |

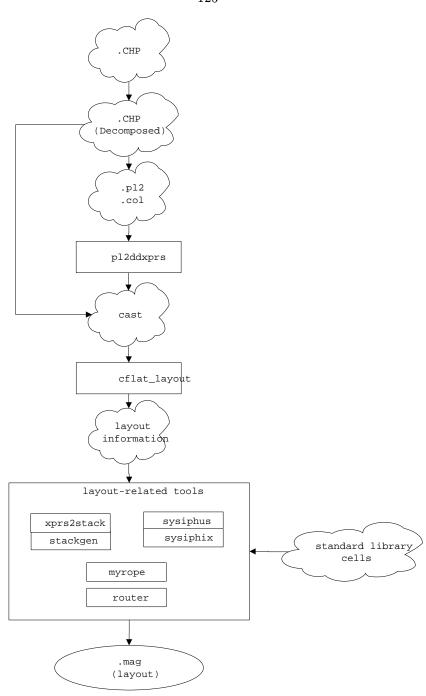

| 7.4  | Synthesis Flow from CHP Description to Layout. A box represents a tool,         |     |

|      | and a cloud shape represents an input description for a program                 | 125 |

| 7.5  | Floor Plan of the STAM and Locations of Flipped Nodes during Digital Sim-       |     |

|      | ulation of the STAM. Each dot represents the location of a flipped node, and    |     |

|      | a box represents the bounding box of a circuit of a decomposed small process,   |     |

|      | which includes a few hundred transistors.                                       | 128 |

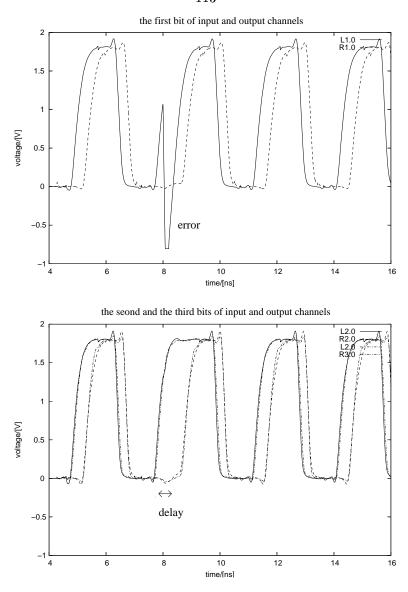

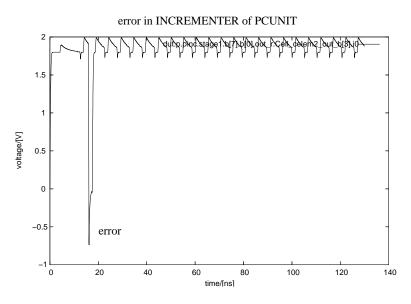

| 7.6  | Waveform of One Corrupted Node in PCUNIT. An error occurs at 12 ns,             |     |

|      | and the corrupted node is restored quickly                                      | 128 |

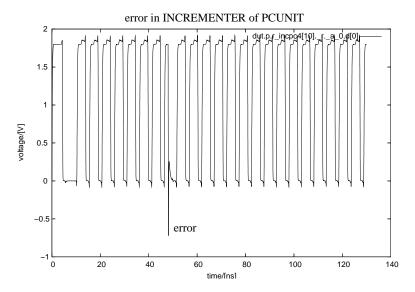

| 7.7 | Waveform of One Corrupted Node in PCUNIT. An error occurs at 44 ns,            |     |

|-----|--------------------------------------------------------------------------------|-----|

|     | which causes a premature transition, but it does not affect the correctness of |     |

|     | computation, because cross-coupled C-elements of the DD scheme prevent the     |     |

|     | propagation of the premature firing                                            | 129 |

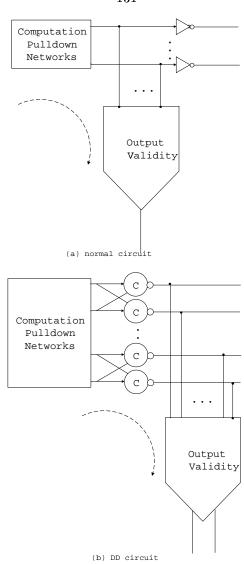

| 7.8 | Compared with a Non-DD Circuit, a DD Circuit Requires More Transitions in      |     |

|     | a Computation Cycle. A circuit for output-channel validity takes its inputs    |     |

|     | from function blocks, but a corresponding DD circuit takes its inputs from     |     |

|     | cross-coupled C-elements after function blocks                                 | 131 |

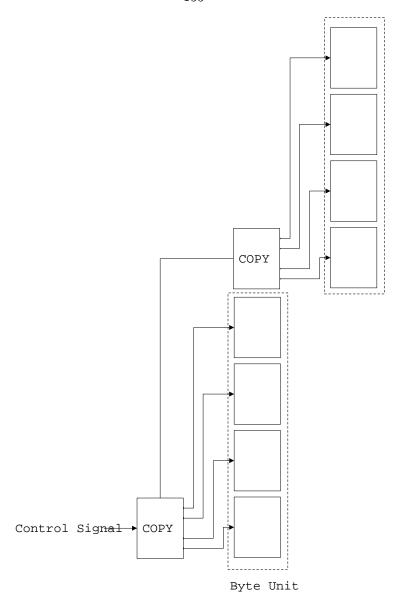

| G.1 | Byte-skewed Distribution of Control Signals                                    | 155 |

## List of Tables

| 2.1 | C-element Truth Table                                                    | 11  |

|-----|--------------------------------------------------------------------------|-----|

| 5.1 | State Table of DD Gate                                                   | 26  |

| 5.2 | Performance Figures of PCHB and DD PCHB                                  | 38  |

| 6.1 | Size of Two-bit Input/Ouput Precharging-evaluating Function Block        | 93  |

| 6.2 | Performance Figures of PCHB for $[4,2]$ Code and PCHB for $[3,2]$ Code   | 110 |

| 7.1 | Performance Comparison between Simple Asynchronous Microprocessor and    |     |

|     | Its Corresponding Soft-error Tolerant Simple Asynchronous Microprocessor | 132 |

| 7.2 | Performance Comparison with Synchronous Competitors                      | 132 |

| C 1 | One-error Detecting Delay-insensitive Code                               | 143 |

## Chapter 1

## Introduction

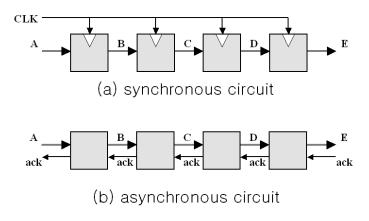

There are two circuit-design paradigms: synchronous circuits and asynchronous circuits. In synchronous circuits, there is a single global clock signal to which all actions are synchronized; a clock signal is fed into each computation module. Each module must finish its computation in a clock period. If something delays the computation, the correctness of the computation cannot be guaranteed.

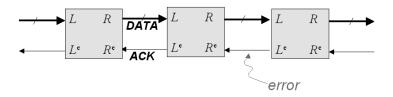

On the other hand, asynchronous circuits operate without a clock signal. The correctness of asynchronous computation is independent of the computation time of modules, because the computation is based on local communications by handshaking protocol. Figure 1.1 shows a synchronous and an asynchronous pipeline.

Figure 1.1: Pipeline of Buffers.

The quasi delay-insensitive (QDI) design style proposed in the 80s is one of the most robust asynchronous design styles for general computation [1]. The QDI style has one minimal assumption on delays in gates and wires: an electric signal occasionally must be copied to multiple destinations in such a way that the maximum difference in arrival time of

the signal at the destinations is small compared to the gate delays. In practice, QDI-circuit designers can easily ensure that the assumption is not violated. Then the correct operation of a QDI circuit is independent of delays in gates and wires, so that QDI circuits are simple, modular, and easy to verify. The recent design of a sub-nanojoule microprocessor has demonstrated that QDI circuits can be very energy-efficient, because only active parts of the system draw power, and the energy spent by the clock is saved [2].

A system of QDI circuits can adapt itself to variations of physical parameters such as supply voltage, fabrication, temperature, doping, and so on. The effect of the variations on synchronous circuits can be severe, but QDI circuits are more robust to the variations, which cause changes in timing of the components. These features make QDI circuits attractive to the designers of reliable systems.

Besides the issues of variation, the tolerance of soft errors is getting even more attention as technology scaling advances. A *soft error* is defined as the erroneous switching of a node when the electrical charges that encode the boolean value of the node are erroneously changed by radiation or other noise sources. Unlike manufacturing defects, a soft error can be corrected by applying the proper charges to the node. The International Technology Roadmap of Semiconductors (ITRS) warns that the continuation of the established semiconductor roadmap is seriously threatened by the increasing occurrence of failures in chip operation [3]. As the feature size of circuits gets smaller, circuits experience more failures of devices and interconnects. To compensate for the inevitable increase of failures, the ITRS urges circuit designers to include error tolerance in their designs, especially for soft (transient) errors caused by radiation or other noise effects.

As a response to the concern, a new method, which is applied entirely at the logic level, is proposed for making QDI circuits tolerant to soft errors. Several soft errors can be simultaneously corrected provided they do not happen too close to each other in space and in time. The method has been demonstrated by designing a simple asynchronous microprocessor.

In the following two chapters, first we shall overview how to design a QDI circuit, and what will happen if a soft error occurs in a QDI circuit. In Chapter 4, we shall briefly review some soft-error tolerant methods for synchronous circuits and asynchronous circuits. In Chapter 5, the crucial components of the method are shown: (1) a special kind of duplication for random logic (when each bit has to be corrected individually), (2) special protection

circuitry for arbiter and synchronizer (as needed for example for external interrupts), (3) reconfigurable circuits using a special configuration unit, and (4) error correcting for memory arrays and other structures in which the data bits can be self-corrected. In Chapter 6, the solution of protecting random logic is compared with alternatives which use other types of error correcting codes (e.g., parity code) in a QDI circuit. It turns out that the duplication generates efficient circuits more commonly than other possible constructions. Finally, the design of a soft-error tolerant asynchronous microprocessor (STAM) is detailed, and testing results of the soft-error tolerance of the STAM are shown in Chapter 7.

It is worth mentioning that a QDI circuit by itself is able to handle more malicious analog effects than a synchronous circuit. For example, radiation hitting a chip can change the charges on a node, not enough to make the bit flip, but enough to make a transition on the node much slower. On the other hand, radiation-dose effects accumulate in the chip substrate and slowly change the threshold voltages, affecting the timing. Both effects change the physical parameters of the system but do not switch a node. The changes in timing may be catastrophic for a synchronous system but can be completely transparent to a QDI system. In this way, soft-error tolerant QDI circuits can be suitable for applications where soft-error tolerance, combined with the advantages of QDI circuits (e.g., robustness to variations and low power), is needed.

### Chapter 2

## Designing Quasi Delay-insensitive (QDI) Circuits

One way of designing QDI circuits involves first writing a high-level description of a system, which is a sequential program in the communicating hardware processes (CHP) language. The sequential program is decomposed into concurrent small CHP processes that are small enough to be easily compiled into the intermediate handshaking expansion (HSE) language. The HSE description is subsequently transformed into a production rule set (PRS) that is the canonical representation of a QDI circuit and is the lowest-level description in the synthesis method. These compilation steps allow for the design of a transistor-level circuit which correctly implements a given high-level specification of a system.

#### 2.1 Communicating Hardware Processes

A CHP program consists of one or more concurrent processes, each of which is a sequential program. There are no shared variables between concurrent processes; they communicate via *channels* that connect two processes.

For example, a CHP process in a CHP program is as follows:

$$P \equiv *[A?a, B?b; ...; F!f(a, b, ...), G!g(a, b, ...); ...; Z; ....]$$

\*[S] means "repeat S forever." S1; S2 means a sequential execution of S1 and S2. The process P receives messages from channel A and channel B, and sends out computation results to channel F and channel G. Then it waits for the action of channel E, which is a synchronization channel between processes. And if the sending-side process sends messages E times as well to channel E, the receiving-side process will receive messages E times from

channel A and vice versa. If the process on one end of a channel is not yet ready to send or receive, the process on the other end will stay waiting.

In the CHP program, there are other processes that send out messages to channel A and channel B, receive messages from channel F and channel G, and synchronize with channel Z, as follows:

$$\begin{split} Q &\equiv & *[...;A!0;...;F?f;...] \\ R &\equiv & *[...;B!1;...;G?g;...] \\ S &\equiv & *[...;Z;...] \end{split}$$

#### 2.2 Handshaking Expansion

We can transform a CHP description into a HSE description, where everything is described in boolean notation. Before compiling a CHP description into a HSE description, we decompose a big CHP process into a set of small concurrent processes for simple circuit-level implementation later.

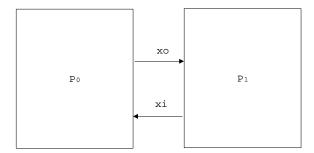

Let us consider a synchronization channel X without data communication between two processes:

$$P_0 \equiv *[...; X; ...]$$

$P_1 \equiv *[...; X; ...]$

If  $P_0$  encounters the channel action X, then it will wait until  $P_1$  reaches to the channel action X and vice versa. The communication channels with neighboring processes are replaced with elementary actions such as waiting and assignment of boolean variables. The elementary actions are specified by a protocol such as a four-phase handshaking protocol. For example,  $P_0$  sets one boolean variable  $x_o$  to let  $P_1$  know that  $P_0$  initiates the communication;  $P_1$  sets the other variable  $x_i$  to let  $P_0$  know that  $P_1$  acknowledges the communication initiated by  $P_o$ . Then the two variables are reset. This is the four-phase handshaking protocol. In the process  $P_0$ , channel X is implemented as follows:

$$x_o \uparrow$$

;  $[x_i]$ ;  $x_o \downarrow$ ;  $[\neg x_i]$

which is called *active*. And channel X in the process  $P_1$  is implemented as follows:

$$[x_o]$$

;  $x_i \uparrow$ ;  $[\neg x_o]$ ;  $x_i \downarrow$

which is called *passive*.  $x_o \uparrow$  is equivalent to  $x := \mathsf{true}$  and  $[x_i]$  means that the process waits until  $x_i$  becomes  $\mathsf{true}$ . Thus the sequence of events during a channel communication is as follows:

$$x_o \uparrow$$

;  $[x_o]$ ;  $x_i \uparrow$ ;  $[x_i]$ ;  $x_o \downarrow$ ;  $[\neg x_o]$ ;  $x_i \downarrow$ ;  $[\neg x_i]$

We introduce an alternative form of active implementation, called *lazy active*, which is more amenable to implementation:

$$[\neg x_i]; x_o \uparrow; [x_i]; x_o \downarrow;$$

The four-phase handshake protocol uses one variable for initialization and the other variable for acknowledgment. For data communication, a variable is replaced with a set of variables, which implements a delay-insensitive code such as one-of-n code. (The details of a delay-insensitive code are explained in Chapter 6.) For brevity, the variables used in the implementation of a channel are called *channel variables*, which consist of *channel code variables* and a *channel acknowledgment variable*.

Figure 2.1: Handshake Expansion of a Synchronization Channel.

#### 2.3 Production Rule Set and PRS Computation

A HSE description is transformed into a production rule set (PRS), which has no explicit sequencing. A PRS is a concurrent composition of production rules, and the execution of a PRS is a concurrent execution of the production rules in the set. Each production rule (PR) has the form  $G \to S$ , where G is a boolean expression of boolean variables called the guard of the PR, and S is a boolean assignment. The assignment is written as  $z \uparrow$  or  $z \downarrow$ , which corresponds to z := true or z := false. An execution of a PR  $G \to S$  is an unbounded sequence of firings. A firing of  $G \to S$  when G is true amounts to the execution of S, and

a firing with G false amounts to a skip. If the firing of a PR does change the value of any variable, the firing is called *effective*. For brevity, we shall refer to all effective firings simply as firings.

A PR  $G \to S$  in a PRS is said to be *stable* if whenever G becomes true it remains true until the assignment S is completed.  $G1 \to z \uparrow$  and  $G2 \to z \downarrow$  are non-interfering if and only if  $\neg G1 \lor \neg G2$  holds in every execution. Stability and non-interference guarantee that the execution result of PRS is deterministic. In physical implementation, an unstable PR can generate a glitch, which may cause a QDI circuit to malfunction. The interference manifests itself as a short circuit, which consumes power excessively, may damage the circuit physically, and also leads to indeterminate logic values.

The two complementary PRs that set and reset the same variable, such as

$$G1 \rightarrow z \uparrow$$

$$G2 \rightarrow z\downarrow$$

,

comprise a gate. The variables in the guards are the *inputs* of the gate and the variable in the assignment is the *output* of the gate. If  $G1 \neq \neg G2$  holds, then z is a state-holding variable, and the gate is a state-holding gate; if  $G1 = \neg G2$  holds, then z is a non-state-holding variable, and the gate is a combinational gate. (These variables correspond to electrical nodes in the physical implementation.)

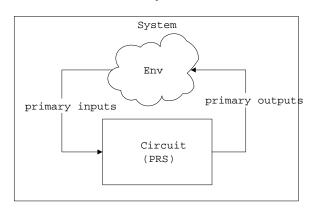

A QDI circuit is an interconnection of gates, interacting with its environment. Each input of a gate is either connected to the output of another gate, or to an environment. The output of a gate may be connected to any number of inputs of other gates, as well as to the environment. An input of a gate that is connected to the environment is a *primary input*; an output of a gate that is connected to the environment is a *primary output*.

The environment of a QDI circuit sets values of primary inputs by reacting to values of primary outputs of the circuit. A pair of a circuit and an environment, like Figure 2.2, is called a *system*.

If a PRS uses boolean variables  $x_1, x_2, ..., x_n$  for guards and assignments, then the state of the PRS can be represented as an n-tuple of boolean values. Interchangeably we shall use '0' for false and '1' for true. And  $s[x_k]$  is the value of  $x_k$  in the state s. A PR P in the state s is called enabled if and only if the guard of P is true in the state s. A PR P is called effective in the state s if and only if the firing of P in state s changes the value of a

Figure 2.2: Circuit and Environment.

variable. An execution path of a PRS is a trace of firings of PRs from an initial state, which is described as  $\langle P_1, ..., P_{m-1}, P_m \rangle$ , where  $P_i$  is a PR. An execution-path set of a PRS is the set of every possible execution path from an initial state of the PRS.

A PRS computation (PRSC) is defined as follows:

- Two disjoint sets:  $\Sigma_{Env}$ , called the environment, and  $\Sigma_{Circuit}$ , called the circuit, whose elements are PRs. ( $\Sigma \stackrel{\text{let}}{=} \Sigma_{Env} \cup \Sigma_{Circuit}$ .)

- An initial state  $s_0 \in \{0,1\}^n$ . (n is the number of distinct variables in  $\Sigma$ .)

- An execution-path set *EP*.

An environment path of an execution path is a projection of the execution path onto  $\Sigma_{Env}$ . A finite set  $S_v$  is called a valid-state set if its elements are states reachable from  $s_0$  by firing of PRs in  $\Sigma$ . A PRS computation can be represented as a transition diagram. The vertices of the diagram correspond to the valid states in  $S_v$ . If a production rule P is effective in a state s, and the state s is turned into a state s' due to the firing of the production rule, then there is an edge labeled P from s to s' in the transition diagram.

#### 2.4 Example of QDI Circuits: Buffer

The CHP description of a buffer, which is an essential component of an asynchronous system, is \*[L; R]. Two boolean variables L.i and L.e implement the input synchronization channel L of the buffer, and likewise two variables R.i and R.e implement the output synchronization channel R. The corresponding HSE is

\*

$$[[L.i]; L.e\downarrow; [\neg L.i]; L.e\uparrow; [R.e]; R.i\uparrow; [\neg R.e]; R.i\downarrow;],$$

where L is passive, and R is lazy-active. A direct implementation of the HSE description produces an inefficient circuit, which requires extra variables and, ultimately, extra transistors. Instead, it is better to permute parts of the HSE to reduce the amount of sequencing and the number of extra variables. The transformation is called reshuffling, which is the source of significant optimization opportunities. Although there are several possible reshufflings, three reshufflings are commonly used:  $precharged\ full\ buffer\ (PCFB)$ ,  $precharged\ half\ buffer\ (PCHB)$  and  $weak\text{-}conditioned\ half\ buffer\ (WCHB)\ [4]$ .

For example, the HSE based on the PCHB template is

\*

$$[R.e \land L.i]$$

;  $R.i\uparrow$ ;  $L.e\downarrow$ ;  $[\neg R.e]$ ;  $R.i\downarrow$ ;  $[\neg L.i]$ ;  $L.e\uparrow$ ].

A corresponding PRS is

$$\begin{array}{cccc} L.e \wedge R.e \wedge L.i & \rightarrow & R.i \uparrow \\ \neg L.e \wedge \neg R.e & \rightarrow & R.i \downarrow \\ L.i \wedge R.i & \rightarrow & L.e \downarrow \\ \neg L.i \wedge \neg R.i & \rightarrow & L.e \uparrow. \end{array}$$

If the PRS of the environment is

$$\begin{array}{ccc} L.e & \rightarrow & L.i \uparrow \\ \neg L.e & \rightarrow & L.i \downarrow \\ R.i & \rightarrow & R.e \downarrow \\ \neg R.i & \rightarrow & R.e \uparrow, \end{array}$$

and the initial state is (L.i, L.e, R.i, R.e) = (0, 1, 0, 1), then the PRSC for the PCHB system is

- $\Sigma_{Env} = \{L.e \rightarrow L.i \uparrow, \neg L.e \rightarrow L.i \downarrow, R.i \rightarrow R.e \downarrow, \neg R.i \rightarrow R.e \uparrow\},$   $\Sigma_{Circuit} = \{L.e \land R.e \land L \rightarrow R.i \uparrow, \neg L.e \land \neg R.e \rightarrow R.i \downarrow, L.i \land R.i \rightarrow L.e \downarrow, \neg L.i \land \neg R.i \rightarrow L.e \uparrow\}$

- Initial state  $s_0 = (0, 1, 0, 1)$

- The execution-path set EP is as follows:  $\{\langle L.i\uparrow\rangle, \langle L.i\uparrow, R\uparrow\rangle, \langle L.i\uparrow, R\uparrow, R.e\downarrow\rangle, \langle L.i\uparrow, R\uparrow, L.i\downarrow\rangle, \langle L.i\uparrow, R\uparrow, L.i\downarrow\rangle, \langle L.i\uparrow, R.e\downarrow\rangle, \ldots\}.$

Accordingly the environment-path set of the PRSC is as follows:

$$EnvP = \{ \langle L.i\uparrow \rangle, \langle L.i\uparrow, R.e\downarrow \rangle, \langle L.i\uparrow, L.i\downarrow \rangle, \langle L.i\uparrow, L.i\downarrow, R.e\downarrow \rangle, \ldots \}.$$

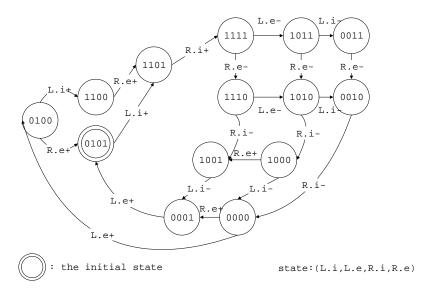

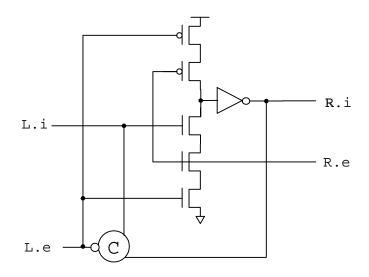

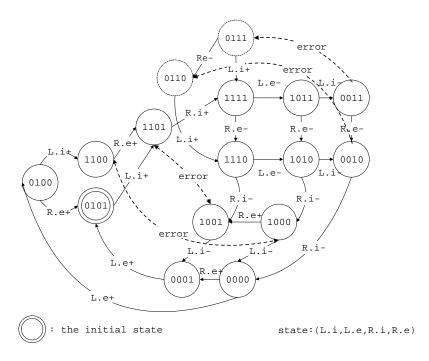

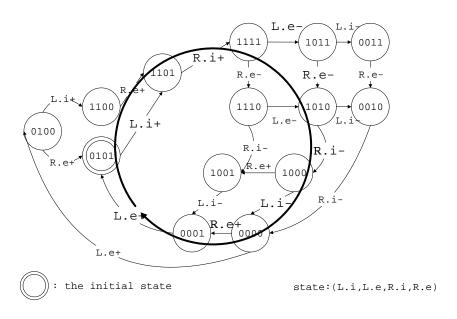

The transition diagram of the PCHB is shown in Figure 2.3, and a circuit diagram of the PCHB in CMOS technology is shown in Figure 2.4.

Figure 2.3: Transition Diagram of Precharged Half Buffer. Each state represents the values of (L.i, L.e, R.i, R.e). The double-circled state is the initial state.

Figure 2.4: Circuit Diagram of Precharged Half Buffer.

Note that in the circuit diagram, a C-element, which was introduced by David E. Muller, is represented as a circle with the letter 'C', which is a commonly used asynchronous logic

Table 2.1: C-element Truth Table

| X | у | Z                       |

|---|---|-------------------------|

| 0 | 0 | 0                       |

| 1 | 1 | 1                       |

| 0 | 1 | previous value retained |

| 1 | 0 | previous value retained |

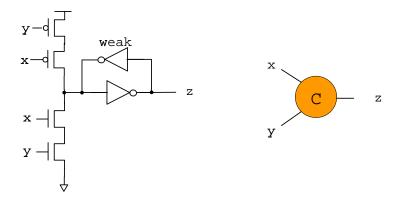

component. The output of a C-element reflects the inputs when the values of all inputs match. One possible CMOS implementation of a C-element is shown in Figure 2.5, and its truth table is shown in Table 2.1.

Figure 2.5: Circuit Diagram of C-element and its Gate Diagram.

## Chapter 3

## Soft Errors in QDI Circuits

In this chapter, different types of errors are overviewed first, and a digital model and an analog model of soft errors are shown. Then the effects of soft errors in QDI circuits are examined.

#### 3.1 Errors on Circuits

Failures of a system at the circuit level can be broadly categorized as either manufacturing defects or operational errors. Manufacturing defects such as single stuck-at faults arise from a range of processing problems during fabrication. For example, improper doping in the channel of a transistor may cause a change in the threshold voltage and timing of the transistor, and may make the transistor unusable. Therefore testing methods for detecting manufacturing defects have been extensively studied. Commonly used testing methods involve adding extra test circuits to the system. While the test circuits are transparent in normal operations, the circuits are activated to detect defects in a special mode [5]. The method of testing QDI circuits has been also studied, which shows that defects in QDI circuits are testable [6].

While defects occur in manufacturing processes, operational errors happen unpredictably during the lifetime of a circuit. Operational errors can be subdivided into two types: hard (permanent) errors and soft (transient) errors. A hard error is an error that damages a circuit irrevocably. For example, when a high-energy particle activates a parasitic transistor to trigger a positive feedback, the current caused by the positive feedback can exceed the device's maximum specification and can destroy the device [7]. In addition to incident high-energy particles, there are other types of destructive causes such as electro-

migration [8].

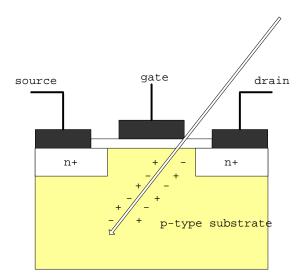

On the other hand, soft errors deposit sufficient charges on the nodes of a circuit to flip the logic states without causing any physical damage to the circuit. They result in transient, inconsistent corruption of data. One of the main causes of soft errors is alpha particles from IC packages [9, 10]. A positively charged alpha particle from radioactive decay travels through a circuit and disturbs the distribution of electrons, as shown in Figure 3.1. If the disturbance is large enough, the value of a node can change from false to true or vice versa. In addition to alpha particles from the package, other types of radiation such as cosmic rays from space can also cause soft errors [11]. Many different particles are present in cosmic rays, but a major cause of soft errors is known to be neutrons. Since neutrons are uncharged, they cannot disturb electron distribution on their own, but they can undergo neutron capture by the nucleus of an atom in the circuit, generating an unstable isotope that produces an alpha particle when it decays. Computers operated at high altitudes or in aircraft experience an order of magnitude higher rate of soft errors compared to sea level, because the flux of cosmic ray depends on altitude. This is in contrast to alpha-particle decay from package, which does not change with location. Other than the radiation effects, soft errors can also be caused by random noise such as inductive or capacitive crosstalk, power supply noise, charge sharing, leakage noise, and so on [12, 13, 14].

Figure 3.1: Interaction of a Particle and Silicon Substrate.

Soft-error tolerance of logic circuits has recently been receiving more attention, since the soft-error rate of advanced CMOS devices is higher than before [15]. For the past three decades, dense memories, including DRAM and SRAM, have been known to be more susceptible to soft errors than logic circuits. For example, the typical soft-error rate for SRAM circuits for 90 nm is reported to be about 1000 kFIT/Mbit, and a soft-error rate for logic circuits for 90 nm is reported to be about 100 kFIT/Mbit [16]. (Failure in time (FIT) is defined as the number of errors per one billion hours.) But it is anticipated that the soft-error rate for logic circuits will increase by nine orders of magnitude between 1992 to 2011, at which point it will be comparable to the soft-error rate for unprotected memory elements [17].

#### 3.2 Digital Model of Soft Errors

A soft error is modeled as flipping the value of a single variable in a PRS; a PRS Computation (PRSC) with a soft error is defined as follows:

- Two disjoint finite sets  $\Sigma_{Env}$ , called the environment, and  $\Sigma_{Circuit}$ , called the circuit, whose elements are PRs. ( $\Sigma \stackrel{\text{let}}{=} \Sigma_{Env} \cup \Sigma_{Circuit}$ .)

- An initial state  $s_0 \in \{0,1\}^n$ . (n is the number of distinct variables in  $\Sigma$ .)

- A soft-error execution-path set  $EP_{error}$ .

A soft-error execution path can include a symbol  $error_{x_i}$  representing an error on  $x_i$ . For example, a soft-error execution path is  $\langle P_1, ..., P_{k-1}, error_{x_i}, P_{k+1}..., P_{m-1}, P_m \rangle$ , which infers that a soft error occurs on  $x_i$  after the firing of the PR  $P_{k-1}$ , and the value of  $x_i$  is flipped. Elements of the valid-state set S are states reachable from the initial state  $s_0$  only by firing of PRs in  $\Sigma$ ; elements of the invalid-state set Q are states reachable only with a soft error on a variable. The vertices of the transition diagram correspond to states in S or Q. If  $s[x_i] \neq s'[x_i]$  and  $s[x_j] = s'[x_j]$  for all  $j \neq i$ , then there is a two-way edge labeled error between s and s' in the transition diagram, because an error on  $x_i$  flips s to s' and vice versa.

There are two types of erroneous computations that may be caused by an error. (For brevity, sometimes we will refer to soft errors as simply errors.)

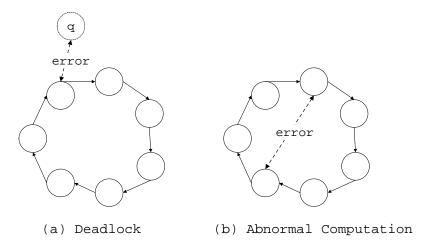

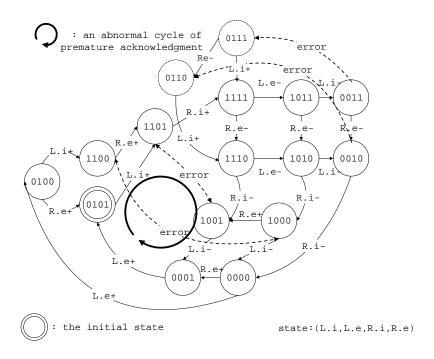

**Deadlock** An error may put a system into an invalid state such as the state q, as shown in Figure 3.2 (a). The invalid state cannot be reached in a normal execution. If no PR is effective in the invalid state, deadlock occurs.

Abnormal Computation An error may cause a transition from a valid state to another valid state. Or an error may put a system into an invalid state where some PRs are effective, and a system is put into a valid state after firings of PRs. Meanwhile some states are possibly skipped or revisited; the corresponding firings of PRs are skipped or repeated due to the abnormal transition, as shown in Figure 3.2 (b). In this case, data can be missed or can be generated accidentally.

Figure 3.2: Examples of Erroneous Computations Caused by Soft Error.

As an example of a PRSC with a soft error, let us consider a soft error on L.e in the buffer from the previous chapter. The PRSC with a soft error on L.e is as follows:

- $\Sigma_{Env}$  and  $\Sigma_{Circuit}$  are the same as before.

- An initial state  $s_0 = (0, 1, 0, 1)$ .

- $EP_{error} = \{ \langle error_{L.e} \rangle, \langle L.i \uparrow \rangle, ..., \langle L.i \uparrow, error_{L.e}, L.i \downarrow, L.e \uparrow, L.i \uparrow \rangle, ..., \}.$

The transition diagram, including transitions caused by the error, is shown in Figure 3.3. In a normal computation, there are the same number of transitions on output variable R.i as on input variable L.i from the specification of a buffer. (Strictly speaking, the number of output transitions of a buffer can be fewer or the same. But in the shown implementation, the next input set assignment (i.e.,  $L.i \uparrow$ ) cannot start until the output reset assignment (i.e.,  $R.i \downarrow$ ) is done.) But an error on L.e can cause premature acknowledgment of the communication on the channel L before an output communication on the channel R is generated. That is, compared to the normal execution cycle as shown in Figure 3.4, the

erroneous cycle (i.e.,  $(L.i\uparrow, error, L.i\downarrow, L.e\uparrow)$ ) skips transitions such as  $R.i\uparrow$ , as shown in Figure 3.5.

Figure 3.3: Transition Diagram of PCHB with Soft Error on L.e. The dotted circles indicate invalid states, and the dotted edges indicate erroneous transitions caused by an error on L.e.

Figure 3.4: Example of Normal Execution Path of Firings in PCHB.

Figure 3.5: Transition Diagram of Buffer with Soft Error on L.e. The dotted circles indicate invalid states, and the dotted edges indicate erroneous transitions caused by an error on L.e.

#### 3.3 Analog Model of Soft Errors

We can also identify the erroneous computation in SPICE simulation of a linear pipeline (an array of L-R buffers), as shown in Figure 3.6. A PRS of a one-bit PCHB is as follows:

$$\begin{array}{cccc} en \wedge R.e \wedge L.0 & \rightarrow \_r.0 \downarrow \\ \neg en \wedge \neg R.e & \rightarrow \_r.0 \uparrow \\ en \wedge R.e \wedge L.1 & \rightarrow \_r.1 \downarrow \\ \neg en \wedge \neg R.e & \rightarrow \_r.1 \uparrow \\ \_r.0 & \rightarrow R.0 \downarrow \\ \neg \_r.0 & \rightarrow R.0 \uparrow \\ \_r.1 & \rightarrow R.1 \downarrow \\ \neg \_r.1 & \rightarrow R.1 \uparrow \end{array}$$

Variables L.0, L1 encoding a one-of-two code and an acknowledgment variable L.e implement the input data channel L. Likewise variables R.0, R.1, and R.e implement the output data channel R.

SPICE simulations of the pipeline have been done in TSMC 0.18- $\mu$ m CMOS technology and at an operating voltage of 1.8 V. A soft error can be modeled in SPICE as a current pulse [18]. If the current pulse is short enough, compared to the response time of the gates, the specific shape of the pulse is not critical to the response of the circuit to the charge injection, so that we can model a soft error as a square current pulse for simplicity.

If the buffer works correctly, there should be the same number of transitions on output variable R.0 as on input variable L.0: the number of rising and falling signals on R.0 is the same as that of rising and falling signals on L.0. However when a charge is injected at the node L.e at 7.0 ns, the assignment  $R.0\uparrow$  is missed: there is no output signal between 7 ns and 8 ns, as shown in the upper panel of Figure 3.7. Since one variable is used to acknowledge communications between modules (buffers), an error on this variable can have catastrophic results.

Figure 3.6: Pipeline of Buffers.

Figure 3.7: Waveforms of Input-channel Variable L.0 and Output-channel Variable R.0, and Input-channel Acknowledgment Variable L.e. A soft error on L.e at 7 ns causes premature acknowledgment of an input communication on L before an output communication on R is generated.

## Chapter 4

## Related Work

In order to cope with soft errors in a circuit, several approaches have been explored. At the device level, the silicon-on-insulator (SOI) process technology helps to increase the resistance of circuits to soft errors, especially those caused by radiation, because of reduced charge collection depth [19].

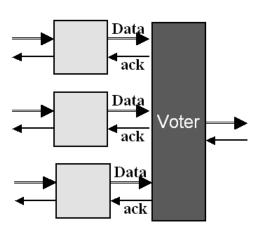

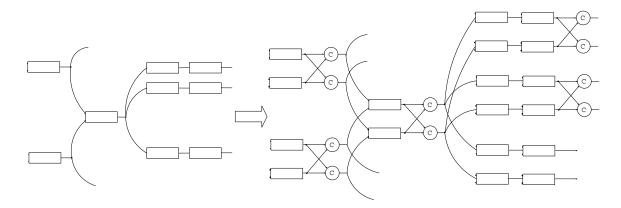

Traditional techniques for providing soft-error tolerance at the logic level rely on triple modular redundancy (TMR), in which a given circuit is triplicated, and a majority voting circuit is used to determine the final output [20]. Sometimes a voting circuit is also triplicated to tolerate an error on the voting circuit itself. Although TMR is a straightforward solution for synchronous circuits, it cannot readily be applied to QDI circuits. A TMR version of a QDI circuit is shown in Figure 4.1. The QDI voting circuit of the design waits for input data communications from three copies of a component. Since an error on one of the triple copies of a QDI circuit results in aborting the communication of the data, the voting circuit possibly waits indefinitely for the delivery of aborted data. Unlike clocked systems, a QDI component may deadlock in the presence of a soft error. Since there is no notion of time in QDI circuits, it is not trivial to adapt the TMR scheme to QDI circuits.

Error correcting codes (ECCs) are also widely used. Except for repetition codes (e.g., duplication and triplication), ECCs are rarely used for control logic because circuits based on ECCs tend to be complex. On the other hand, ECCs are mostly suitable for a large memory array, where we can exploit the density of a complex ECC, and can minimize the cost of decoding and encoding by having just one encoder and decoder for a whole memory [21]. An example of applying a Hamming code to the instruction memory of a 8051 microprocessor has been demonstrated [22].

When an ECC is applied to an array of SRAMs, the decoder corrects data later when the

Figure 4.1: TMR QDI Circuit. It cannot tolerate a soft error, because a soft error can abort the communication of data, which is hard to detect in an asynchronous system.

data are accessed. On the other hand, self-correcting memory cells correct an error locally, even though the cells require more transistors than an SRAM. A self-correcting memory cell, which stores data in two different locations within the cell, restores corrupted data with an appropriate feedback. There exist several styles of self-correcting memory cells, and each style organize the feedback transistors differently [23, 24]. We shall adapt one of these self-correcting memory cells in order to design a soft-error tolerant asynchronous memory.

Besides the approaches based on TMR and ECCs (namely, space redundancy), approaches based on time redundancy have been also explored. For example, one circuit-level approach employs time-domain TMR, which samples the result of combinational gates multiple times [25]. Due to a larger sampling window, the approach incurs a performance overhead. The other approach for mitigating soft errors uses delay elements, which prevent malicious current pulse from spreading to latches, but it assumes short delays in restoring a soft error [26].

We can apply the time redundancy not to hardware but to software. There are several software-based schemes that execute duplicated instructions over duplicated data and compares the results to check their integrity, called rollback recovery [27, 28, 29]. Although the software-based approaches do not require much hardware modification, they incur speed penalty. Evaluation of the cost of these approaches for four different benchmark programs shows a speed penalty varying 110% to 354% [30]. Multithreading is another software-based transient fault detection and recovery approach that reduces memory and speed cost

by exploiting the capabilities of modern processors to execute multiple threads of computation [31]. However these software-based approaches are limited to microprocessors.

A variety of soft-error tolerant schemes for synchronous circuits has been studied and compared [32, 33]. Meanwhile, a few error-detection methods and error-tolerance techniques for QDI circuits have been proposed. A duplication method has been employed to provide an indication of an error in asynchronous circuits, but the duplication method can fail to detect an error, since it assumes the maximum delay between an output from one circuit and an output from its counterpart circuit [34]. Although the approaches can improve the robustness of QDI circuits, these methods require significant timing assumptions to detect errors, and do not always guarantee the error tolerance of a QDI circuit [35, 36]. On the contrary, exploiting the stability of a QDI circuit, we can make a duplicated QDI circuit soft-error tolerant by adding cross-coupled C-elements, which will be demonstrated in the following chapter.

A reconfiguration method for designing a soft-error tolerant asynchronous circuit is presented, which is different from the above approaches [37]. In the reconfiguration method, by forcing an asynchronous circuit to stall in the case of an error, specific self-reconfiguration logic is activated by a detector of the stalling (e.g., watchdog timer). Then the array circuit is reconfigured around the faulty components and consequently the system recovers from errors. This approach incurs large overheads and is suitable for specific structures such as an adder.

# Chapter 5

# Protecting QDI Circuits from Soft Errors by Design

The key idea for protecting a system from an error is adding redundancy. We shall show how to make a QDI circuit soft-error tolerant by (1) detecting a soft error with duplicated gates and (2) preventing the propagation of an error with cross-coupled C-elements. This method is called the *duplicated double-checking* (DD) scheme. Although duplication by itself is not enough to correct an error, the duplicated QDI circuit with cross-coupled C-elements can correct an error by exploiting the stability property of QDI circuits. That is, if an error occurs on the output of one of duplicated gates, the cross-coupled C-elements prevent the corrupted output from propagating to the environment; the stable inputs eventually restore the proper outputs while the computation of QDI circuits is delayed. Since additional delay is transparent to QDI circuits, the result of the computation is not affected.

The DD scheme is general enough to be applied to most parts of a QDI system. However, arbiters and synchronizers, which are required for handling interrupts and interfacing a synchronous domain and an asynchronous domain, need special protection circuits, called mutual excluders, because of their non-deterministic feature. In addition, arrays of bitstorage units in a memory do not rely on the DD scheme for error tolerance. In bitstorage units such as SRAMs, the stability property cannot be used to restore the value of a corrupted variable. Once data is written in a storage unit, the inputs that triggered the writing do not persist. Hence, solutions based on error correcting codes are applied in memories instead of the DD scheme.

In the following sections, we first show that a QDI circuit based on the DD scheme is capable of tolerating an error. Then we show how to design a soft-error tolerant arbiter, field programmable gate arrays (FPGA), and memory.

### 5.1 Duplicating QDI Circuits with Cross-coupled C-elements

#### 5.1.1 Duplicated Double-checking QDI Circuit

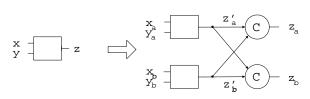

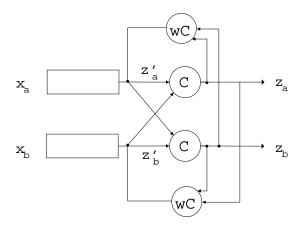

In the duplicated double-checking (DD) scheme, all gates in the original circuit are duplicated, and then state-holding variables are double-checked, which means that two cross-coupled C-elements are placed on state-holding variables. The reason cross-coupled C-elements for non-state-holding variables are inessential, is explained at the end of the proof of Theorem 1.

A DD gate consists of two plain gates and two cross-coupled C-elements, called double-checking C-elements, as shown in Figure 5.1. The C-elements share the inputs  $z'_a$ ,  $z'_b$ , called checked-in (CI) variables, whose outputs are  $z_a$  and  $z_b$ , called checked-out (CO) variables. A set of CI variables and CO variables, such as  $z_a$ ,  $z_b$ ,  $z'_a$ , and  $z'_b$ , are called cross-coupled variables. A gate in PRS is

$$G_p(...,x,...) \rightarrow z \uparrow$$

$G_n(...,x,...) \rightarrow z \downarrow$ ,

and a corresponding DD gate is

$$G_p^a(..., x_a, ...) \rightarrow z_a' \uparrow$$

$$G_p^b(..., x_b, ...) \rightarrow z_b' \uparrow$$

$$G_n^a(..., x_a, ...) \rightarrow z_a' \downarrow$$

$$G_n^b(..., x_b, ...) \rightarrow z_b' \downarrow$$

$$z_a' \wedge z_b' \rightarrow z_a \uparrow, z_b \uparrow$$

$$\neg z_a' \wedge \neg z_b' \rightarrow z_a \downarrow, z_b \downarrow.$$

(For brevity, two PRs  $G \to x \uparrow$  and  $G \to y \uparrow$  are written as  $G \to x \uparrow$ ,  $y \uparrow$ .) The variables  $x_a$  and  $x_b$  are copies of the variable x, and the variables  $z_a$  and  $z_b$  are copies of the variable z, and so forth.

A DD circuit consists of duplicated gates and DD gates. Figure 5.2 shows a circuit and its corresponding DD circuit. If the PRS of a circuit is stable and non-interfering, then the PRS of its corresponding DD circuit is also stable and non-interfering. As a matter of fact, the DD PRS has a *strong stability*: whenever a guard (e.g.,  $G_p^a$ ) becomes true, it remains

Figure 5.1: Gate in Original Circuit and its Corresponding DD Gate in DD Circuit.

true until both assignments of duplicated variables (e.g.,  $z_a \uparrow$ ,  $z_b \uparrow$ ) are completed. The inputs of duplicated gates, which cause the transitions of the duplicated outputs, persist until the transitions propagate to the environment. The rationale behind the error tolerance of DD circuits that have the strong stability, is explained in the following theorem.

Figure 5.2: Circuit and its Corresponding DD Circuit.

**Theorem 1** If a QDI circuit is stable and deadlock-free, then its corresponding DD QDI circuit can tolerate a soft error: neither deadlock nor abnormal computations are caused by a soft error.

*Proof:* In a DD circuit, duplicated variables are cross-coupled by C-elements whose outputs reflect the inputs when the values of all inputs match; an error corrupts only half of a DD circuit. As a result, the only erroneous computation, if incurred, is deadlock when an error causes inputs of cross-coupled C-elements (i.e., CI variables) to mismatch. Hence, in order to show the error tolerance of a DD circuit, it is enough to show that an error cannot cause deadlock: a mismatch between the inputs of cross-coupled C-elements, caused by an error, can be resolved eventually, or the mismatch does not stop expected assignments of CO variables by disabling effective PRs.

There are three kinds of variables in a DD circuit: a CI variable, a CO variable, and

Table 5.1: State Table of DD Gate

| $G_n^a$ | $G_n^b$ | $G_p^a$ | $G_p^b$ | $z'_a$ | $z_b'$ | $z_a$ | $z_b$ |     |

|---------|---------|---------|---------|--------|--------|-------|-------|-----|

| D       | D       | D       | D       | 0      | 0      | 0     | 0     | (a) |

|         |         | E       | D       | 0      | 0      | 0     | 0     | (b) |

|         |         |         |         | 1      | 0      | 0     | 0     | (c) |

|         |         | D       | Ε       | 0      | 0      | 0     | 0     | (d) |

|         |         |         |         | 0      | 1      | 0     | 0     | (e) |

|         |         | E       | Ε       | 0      | 0      | 0     | 0     | (f) |

|         |         |         |         | 1      | 0      | 0     | 0     | (g) |

|         |         |         |         | 0      | 1      | 0     | 0     | (h) |

|         |         |         |         | 1      | 1      | 0     | 0     | (i) |

|         |         |         |         | 1      | 1      | 1     | 0     | (j) |

|         |         |         |         | 1      | 1      | 0     | 1     | (k) |

|         |         |         |         | 1      | 1      | 1     | 1     | (1) |

|         |         | D       | Е       | 1      | 1      | 1     | 1     | (m) |

|         |         | E       | D       | 1      | 1      | 1     | 1     | (n) |

| $G_n^a$      | $G_n^b$      | $G_p^a$ | $G_p^b$ | $z'_a$ | $z_b'$ | $z_a$ | $z_b$ |      |

|--------------|--------------|---------|---------|--------|--------|-------|-------|------|

| D            | D            | D       | D       | 1      | 1      | 1     | 1     | (a') |

| $\mathbf{E}$ | D            |         |         | 1      | 1      | 1     | 1     | (b') |

|              |              |         |         | 0      | 1      | 1     | 1     | (c') |

| D            | E            |         |         | 1      | 1      | 1     | 1     | (d') |

|              |              |         |         | 1      | 0      | 1     | 1     | (e') |

| $\mathbf{E}$ | $\mathbf{E}$ |         |         | 1      | 1      | 1     | 1     | (f') |

|              |              |         |         | 0      | 1      | 1     | 1     | (g') |

|              |              |         |         | 1      | 0      | 1     | 1     | (h') |

|              |              |         |         | 0      | 0      | 1     | 1     | (i') |

|              |              |         |         | 0      | 0      | 0     | 1     | (j') |

|              |              |         |         | 0      | 0      | 1     | 0     | (k') |

|              |              |         |         | 0      | 0      | 0     | 0     | (1') |

| D            | Е            |         |         | 0      | 0      | 0     | 0     | (m') |

| E            | D            |         |         | 0      | 0      | 0     | 0     | (n') |

<sup>\*</sup> E stands for enabled, and D stands for disabled