# SMARTANTENNA DESIGN (REKA BENTUK ANTENNA PINTAR)

THAREK ABD.RAHMAN REZA ABDOLEE

RESEARCH VOTE NO: 79029

FAKULTI KEJURUTERAAN ELEKRIK UNIVERSITI TEKNOLOGI MALAYSIA

2008

The lord has blessed me with a family to whom this research project report is dedicated.

# **ACKNOWLEDGEMENTS**

This project is sponsored by Ministry of Science, Technology and Innovation of Malaysia under the Escience Fund with VOT number 79029.

#### **ABSTRACT**

#### **SMART ANTENNA DESITGN**

(Keywords: Smart antennas, digital beamforming, DSP and FPGA implementation)

Smart antenna technologies are emerging as an innovative way to meet the growing demand for more powerful, cost-effective and highly efficient wireless communication systems. In this project, from broad category of smart antenna techniques, the switch beam digital-beamforming technique in the downlink is deployed to improve the fidelity and performance of WiMax application. In this regards, the designed system forms and steer the beam according to the user location which is known to the system. In addition, the system performs sidelobe cancellation base on the chebyshev algorithm to optimize the antenna radiation pattern. The design and implementation steps are as follow: the system is firstly modeled by MATLAB software. After modeling, the algorithm is implemented in DSP by using C and Code Composer Studio. After DSP hardware implementation, the signal management is performed in DSP before transmission to the FPGA board. This management is necessary, in order to make processed signal in DSP suitable for channel separation process in FPGA. FPGA is deployed to split the data stream into sixteen channels corresponding to number of antenna elements. Next, the FPGA and DSP are integrated together to form the baseband switch beam smart antenna system. After integration process, the hardware is tested; the results prove that the system functions properly as we expected from simulation model. In this project, lastly, the initial design of IF, RF-front-end and their necessary circuits are also portrayed to be used in the next smart antenna research project.

# **Key researchers:**

Prof.Tharek Abd Rahman Dr.Razali Ngah Reza Abdolee Vida Vakilian

Email: tharek@fke.utm.my

Tel.No: 07-5536601

Vote No: 79029

#### Reka Bentuk Antenna Pintar

Teknologi antena pintar telah muncul sebagai satu inovasi untuk memenuhi permintaan sistem yang berkuasa tinggi, kos berpatutan dan berkecekapan tinggi dalam system perhubungan tanpa wayar. Bagi projek ini, dari pelbagai kategori dalam teknik antenna pintar, teknik suis alur berdigital rangkaian bawah telah digunakan untuk memperbaiki kualiti dan mutu dalam penggunaan WiMax. Dengan itu, sistem direkabentuk bagi membentuk alur dan dipandu ke kedudukan pengguna yang telah diketahui oleh sistem. Sebagai tambahan untuk mendapatkan bentuk sinaran antena yang optima, pembatalan cuping sisi dilakukan berdasarkan kepada algoritma chebyshev. Langkah-langkah bagi merekabentuk dan perlaksanaan projek ini adalah seperti berikut: Pada mulanya, perisian MATLAB digunakan untuk mendapatkan model bagi sistem tersebut dan seterusnya algoritma dilakukankan dalam DSP menggunakan bahasa C and 'Code Composer Studio'. Setelah perkakasan DSP dilaksanakan, adalah perlu memastikan pengurusan isyarat dibuat sebelum signal ini dihantar ke papan FPGA. Ini adalah perlu untuk membolehkan data yang sesuai sahaja yang akan di hantar ke papan FPGA tersebut. Setelah itu, saluran perlu dipisahkan kepada enam belas unsur tatasusunan antenna menggunakan papan FPGA. Berikutnya adalah menyatukan FPGA dengan DSP bersama-sama untuk menghasilkan jalur asas alur suis sistem antenna pintar. Perkakasan hasil dari penyatuan diatas telah diuji dan keputusan menunjukkan sistem telah berfungsi dengan baik seperti yang dijangkan dari penyelakuan model. Diakhir projek ini, rekabentuk awal bagi IF, RF 'front-end' dan litar yang bersesuaian telah diberikan bagi tujuan untuk penggunaan penyelidikan antenna pintar di masa hadapan.

# **Key researchers:**

Prof.Tharek Abd Rahman Dr.Razali Ngah Reza Abdolee Vida Vakilian

Email: tharek@fke.utm.my

Tel.No: 07-5536601

Vote No: 79029

# **Table of Contents**

| CHAPTER | TITLE                               | PAGE |

|---------|-------------------------------------|------|

|         | DEDICATION                          | ii   |

|         | ACKNOWLEDGEMENT                     | iii  |

|         | ABSTRACT                            | iv   |

|         | ABSTRAKT                            | V    |

|         | TABLES OF CONTENTS                  | vi   |

|         | LIST OF TABLES                      | ix   |

|         | LIST OF FIGURES                     | X    |

|         | LIST OF ABBREVIATIONS               | xii  |

|         | LIST OF APPENDICES                  | xiii |

| 1       | INTRODUCTION                        |      |

|         | 1.1 Introduction                    | 1    |

|         | 1.2 Objective                       | 2    |

|         | 1.3 Scope of Research Project       | 3    |

|         | 1.4 Report Outline                  | 3    |

| 2       | SMART ANTENNA SYSTEMS               |      |

|         | 2.1 Introduction                    | 5    |

|         | 2.2 Smart Antenna Definition        | 6    |

|         | 2.3 Smart Antenna Operation         | 7    |

|         | 2.4 Classification of Smart Antenna | 9    |

|         | 2.4.1 Switched Beam Systems         | 10   |

|         | 2.4.2 Adaptive Array System         | 11   |

|         | 2.5 Advantages of Smart Antennas    | 12   |

|         | 2.6 Disadvantages of Smart Antennas | 14   |

|   |                                                           | vii |

|---|-----------------------------------------------------------|-----|

|   | 2.7 Smart Antenna design in wireless Communication Center | 15  |

|   | 2.8 Design of downlink smart antenna system               | 17  |

|   | 2.9 Expansion board design                                | 18  |

|   | 2.9.1 The possible designs for expansion board            | 19  |

|   | 2.9.1.1 Interfacing a DAC8534 with a TMS320C6713B         | 21  |

| 3 | DIGITAL BEAMFORMING WITH DSP BOARD                        |     |

|   | 3.1 Introduction                                          | 24  |

|   | 3.2 Beamforming                                           | 25  |

|   | 3.3 DSP Design (Beamforming and sidelobe cancellation)    | 27  |

|   | 3.4 DSP system design                                     | 28  |

|   | 3.5 DSP speed and real time constraints                   | 30  |

|   | 3.6 DSP implementation of smart antenna system            | 32  |

|   | 3.7 Beamforming matrix                                    | 33  |

|   | 3.8 Sidelobe cancellation by using DSP                    | 34  |

| 4 | CHANNEL SEPARATION WITH FPGA BOARD                        |     |

|   | 4.1 Introduction                                          | 36  |

|   | 4.2 Field Programmable Gate Arrays (FPGAs) Overview       | 36  |

|   | 4.2.1Applications of FPGAs                                | 37  |

|   | 4.2.2 FPGAs Architecture                                  | 37  |

|   | 4.3 Altera Excalibur development board                    | 39  |

|   | 4.4 FPGA Programming                                      | 42  |

| 5 | INTERGRATION OF DIGITAL SIGNAL                            |     |

|   | PROCESSOR AND FPGA BOARD                                  |     |

|   | 5.1 Introduction                                          | 44  |

|   | 5.2 System model                                          | 44  |

|   | 5.3 Integration of DSP and FPGA                           | 45  |

|   | 5.4 Summary                                               | 48  |

| 6              | IF AND RF FRONT-END DESIGN FOR SMART                          |    |

|----------------|---------------------------------------------------------------|----|

|                | ANTENNA                                                       |    |

|                | 6.1 Introduction                                              | 49 |

|                | 6.2 Baseband glue circuit                                     | 50 |

|                | 6.3 Quadrature-modulator                                      | 52 |

|                | 6.4 local oscillators for 2.4GHz signal                       | 54 |

|                | 6.5 Wilkinson power divider                                   | 56 |

|                | 6.6 Balun Circuits                                            | 56 |

|                | 6.7 Temperature compensated crystal oscillator (TCXO)         | 57 |

|                | 6.8 linear RF and IF amplifier                                | 58 |

|                | 6.9 Second up-converter                                       | 59 |

| 7              | ANTENNA ARRAY DESIGN AND FABRICATION                          |    |

|                | 7.1 Introduction                                              | 62 |

|                | 7.2 Uniformly Spaced Linear Array                             | 63 |

|                | 7.3 Antenna array design and fabrication                      | 67 |

| 8              | SIMULATION AND MEASUREMENT RESULTS AND                        |    |

|                | CONCLUSION                                                    |    |

|                | 8.1 Introduction                                              | 71 |

|                | 8.2 Result of digital beamforming by using DSP                | 72 |

|                | 8.3 Sidelobe cancellation                                     | 73 |

|                | 8.4 Antenna array radiation and sidelobe cancellation results | 75 |

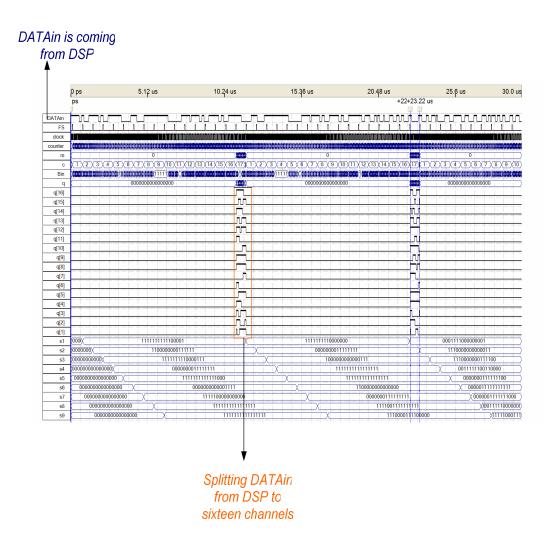

|                | 8.5 Channel separation and synchronization by using FPGA      | 79 |

|                | 8.6 Integration of DSP and FPGA board                         | 80 |

|                | 8.7 Summary and conclusion                                    | 82 |

|                | 8.8 Future works                                              | 82 |

| REFERENCES     |                                                               | 84 |

| Appendices A-D |                                                               |    |

|                |                                                               |    |

# LIST OF TABLES

| NO  | TITLE                                 | PAGE |

|-----|---------------------------------------|------|

| 4.1 | Flash Memory Configuration of FPGA    | 41   |

| 6.1 | Simulation parameters for beamforming | 72   |

# LIST OF FIGURES

| NO   | TITLE                                                         | PAGE |

|------|---------------------------------------------------------------|------|

| 2.1  | Block Diagram of a Smart Antenna System                       | 7    |

| 2.2  | Block diagram of smart antenna implementation                 | 8    |

| 2.3  | Omnidirectional and smart antennas based cellular system      | 12   |

| 2.4  | Linear Array Structure                                        | 16   |

| 2.5  | First design                                                  | 17   |

| 2.6  | second design                                                 | 17   |

| 2.7  | third design                                                  | 18   |

| 2.8  | baseband daughter card                                        | 19   |

| 2.9  | functional block diagram of DAC8534                           | 20   |

| 2.10 | pin configuration of DAC8534                                  | 20   |

| 2.11 | interfacing a DAC8534 with a TMS320C6713B                     | 21   |

| 2.12 | quadruple bus buffer gate "SN74LVC125A"                       | 22   |

| 2.13 | typical connection of DAC8830                                 | 22   |

| 2.14 | typical connection of DAC8560                                 | 23   |

| 3.1  | A narrowband beamformer                                       | 26   |

| 3.2  | Functional block and CPU (DSP core) diagram                   | 28   |

| 3.3  | simplified DSP system design                                  | 29   |

| 3.4  | software development process diagram                          | 30   |

| 3.5  | the predefined antenna beam direction                         | 32   |

| 3.6  | the beamforming flow                                          | 33   |

| 3.3  | The flowchart of phase manipulation and sidelobe cancellation |      |

| 3.6  | The digital beamforming model                                 |      |

| 4.1  | Internal structure of an FPGA                                 | 38   |

| 4.2  | The Excalibur Development Board                               | 39   |

| 4.3  | The Nios Embedded Processor                                   | 40   |

| 4.4  | Pin assignment of FPGA                                        | 43   |

| 5.1  | Smart antenna system model                                    | 45   |

| 5.2  | Integration of DSP and FPGA                                   | 46   |

| 5.3<br>6.1 | Transferring from DSP and FPGA IF and RF front end design                                       | 48<br>50 |

|------------|-------------------------------------------------------------------------------------------------|----------|

|            |                                                                                                 |          |

| 6.2        | Connecting the single ended signal to balanced input of TRF3702                                 | 51       |

| 6.3        | Glue circuit connecting the DAC5687 to TRF3702                                                  | 52       |

| 6.4        | TRF3702 pin arrangement                                                                         | 53       |

| 6.5        | TRF3702 functional block diagram                                                                | 53       |

| 6.6        | Generating the LO signal for TRF3702 using TRF3750                                              | 54       |

| 6.7        | The typical layout for" MAX2750"                                                                | 55       |

| 6.8        | The pin configuration for" MAX2750"                                                             | 55       |

| 6.9        | Balun circuit before ICML5824, CAC=0.1 $\mu$ f RG=120K $\Omega$                                 | 56       |

| 6.10       | Balun circuit configurations at 2.4 GHz                                                         | 57       |

| 6.11       | low profile TCXO-514 frequency range 1.2 to 100MHz                                              | 57       |

| 6.12       | ML5824 top-views                                                                                | 58       |

| 6.13       | HMC315 linear amplifier frequency range up-to 7 GHZ (C block=0.1micro, Rbias=5k)                | 59       |

| 6.14       | AD8353 amplifier (frequency range 1 MHZ up-to 2700 GHZ)                                         | 59       |

| 6.15       | Ml5824 functional block diagram                                                                 | 60       |

| 6.16       | ML5824 glue circuits                                                                            | 61       |

| 7.1        | linear array antenna                                                                            | 64       |

| 7.2        | Front-view of linear antenna array (CST)                                                        | 67       |

| 7.3        | Back-view of linear antenna array (CST)                                                         | 68       |

| 7.4        | The radiation pattern in direction of o degree                                                  | 68       |

| 7.5        | The 3D radiation pattern in direction of o degree                                               | 69       |

| 7.6        | The simulation results for return loss                                                          | 69       |

| 7.7        | Fabricated linear antenna array                                                                 | 70       |

| 8.1        | The DSP and MATLAB arrangement by PC                                                            | 72       |

| 8.2        | Digital beamforming with DSP board                                                              | 73       |

| 8.3        | Comparisons between the software simulation results (a) and hardware implementation results (b) | 74       |

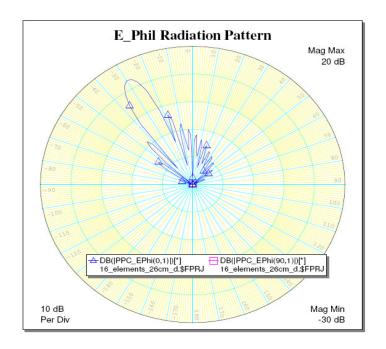

| 8.4a       | 16-elemets zero phase, without weighting                                                        | 75       |

| 8.4b       | 16-elemets zero phase, Kaiser weighting α=3                                                     | 76       |

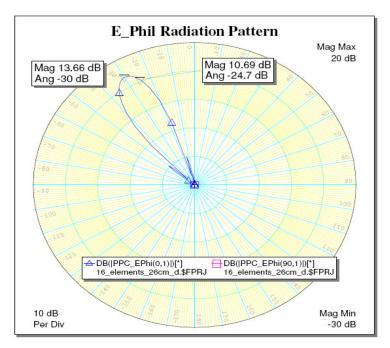

| 8.5a       | 16-elemets -30 phase, without weighting                                                         | 77       |

| 8.5b       | 16-elemets -30 phase, Kaiser weighting $\alpha$ =4                                              | 77       |

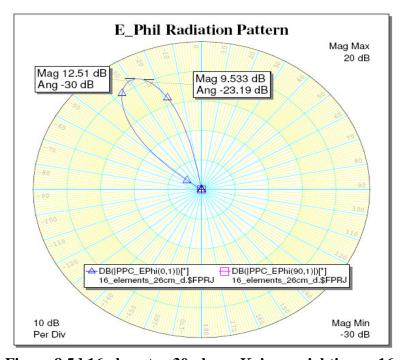

| 8.5c       | 16-elemets, Kaiser weighting for $\alpha$ =8 theta=-30                                          | 78       |

| 8.5d       | 16-elemets, -30 phase, Kaiser weighting $\alpha$ =16                                            | 78       |

| 8.6        | Channel separation and synchronization with FPGA                                                | 80       |

| 8.7        | Connection between DSP and FPGA                                                                 | 81       |

# LIST OF ABBREVIATION

| Symbol | Definition                                      |

|--------|-------------------------------------------------|

| WLAN   | wireless local area networks                    |

| WiMax  | Worldwide Interoperability for Microwave Access |

| DSP    | Digital signal processor                        |

| FPGA   | Field-programmable gate array                   |

| FS     | Frame synchronization                           |

| SDRAM  | synchronous DRAM                                |

| EDMA   | Enhanced direct memory access                   |

| McBSP  | Multi channel buffer serial port                |

| PLD    | programmable logic device                       |

| CPLD   | Complex programmable logic device               |

| DIP    | dual in-line package                            |

| LED    | Light-emitting diode                            |

# LIST OF APPENDICES

| APPENDIX | TITLE                                            | PAGE |

|----------|--------------------------------------------------|------|

| A        | Digital beamforming C source code                | 86   |

| В        | Channel separation using VHDL code               | 92   |

| C        | Channel separation using Verilog code            | 96   |

| D        | Source code for digital beamforming using MATLAB | 98   |

#### **CHAPTER 1**

# **INTRODUCTION**

# I. Introduction

The demand of smart antenna for mobile communications is increased recently and the main purpose for applying smart antennas is feasibility for increasing in capacity and efficiency. The application of smart-antenna arrays has been suggested for mobile-communication systems, to overcome the problem of limited channel bandwidth, satisfying a growing demand for a large number of mobiles on communications channels. Smart antennas, when used appropriately, help in improving the system performance by increasing channel capacity and spectrum efficiency, extending range coverage, steering multiple beams to track many mobiles, and compensating electronically for aperture distortion. They also reduce delay spread, multipath fading, co-channel interference, system complexity, bit error rate (BER).

# 1.2 Objectives

Base on which we have stated in submitted proposal to Ministry of Science, the main objective of the project is to design and fabricate high gain directive antenna with beamforming capability. The methodology to achieve this objective was to use left-handed material to implement the antenna. Unfortunately, after doing some research, we have found out that this methodology is impractical in the current situation. The reasons are outline here. Firstly, these materials are very expensive to build due to expensive manufacturing devices. Second, these areas of research presently are academic and they have a wide room to find the place for practical implementation, so the output of this kind of research would just be a laboratory scale. Therefore, we had preferred to design this antenna with different methodology. So we have chosen the signal processing technique instead of left-handed material to form and optimize the antenna radiation pattern. To achieve this objective we define three steps. The first step is implementation of the digital beamforming by using the digital signal processor. More precisely, in the first step the aim is to implement the switched beam smart antenna for downlink transmission. According to the algorithm, the beam can steer from 0 to 180 degree in azimuth angle base on user direction with any resolution. Second step of the project is to manage the processed signals in DSP board after digital beamforming and sidelobe cancellation to transmit them to the expansion board. Third and main step of the project is to design and implement of baseband channel separation and synchronization by using FPGA board. By completing these steps, the main objective of the project will be achieved.

# 1.3 Scope of research project

The project involves both of software modeling and hardware implementation. In the first phase of the project, the TMS320C6713B DSP board is used for beamforming. C and Code Composer Studio software is applied for programming this board. Also MATLAB software is chosen for modeling because of some facilities provided, including a Link for Code Composer Studio Development Tools and signal processing blocksets and toolbox. By using this links, transferring information to and from Code Composer Studio is possible. In the second phase of the project FPGA board is applied for performing the channel separation and synchronization and Quartus II software is used to program this board. In the third phase of the project integration of DSP and FPGA is done by programming the EDMA and McBSP of DSP.

# 1.4 Report outline

This report is organized as follows. In Chapter 2, background information and basic principle in smart antenna system is explained. In addition, the project structure and block diagram are discusses as well. In Chapter 3, digital beamforming by using DSP board is fundamentally discussed. Moreover, the hardware structure of DSP board shortly reviewed. Also, the model for beamforming is illustrated. In Chapter 4, after FPGA hardware description, channel separation for the project is explained. In this respect, FPGA programming and pin assignment are reviewed as well. In Chapter 5,

integration of DSP and FPGA is discussed and also the system model used in this project is given. The IF and RF-front-end design are reviewed in chapter 6. The antenna array design and implementation are presented in chapter 7. Lastly, in Chapter 8, simulation results for digital beamforming and the channel separation are discussed. In this chapter a comparison between hardware and software simulation results is made between DSP and MATLAB software. At the end of this chapter, final conclusion of the work is presented, and some possible future works are suggested.

#### **CHAPTER 2**

# **SMART ANTENNA SYSTEMS**

#### 2.1 Introduction

The receiver and transmitter antennas are one of the most critical components in the design of wireless communication systems. A good design of the antenna can relax system requirements, improve overall system performance and greatly reduce the infrastructure costs [1]. It has been demonstrated that using a beamforming antenna instead of an omni-directional antenna in the wireless communication systems can increase the system capacity and improve the overall system performance [2]. This performance enhancement is due to the reduction in the interference by attenuating the interference signals which have different directions of arrivals than the desired signal direction of arrival at the receiver antenna site. This is called spatial processing because the direction of arrival is related to the mobile location.

The system performance can be further improved by exploiting the delay spread of the received signals. The signal of each mobile arrives to the base station antenna in multi-path form. Each path usually has its own delay and direction of arrival. Using the smart antenna alone means that we receive (ideally) only one path and ignore the others.

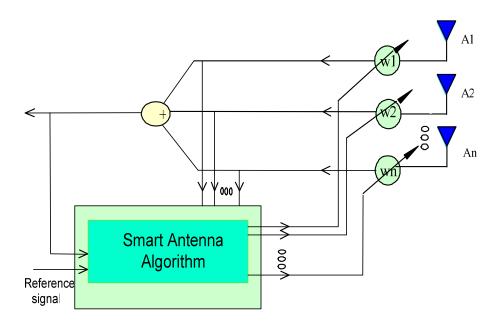

#### 2.2 Smart Antenna Definition

A smart antenna is defined as an array of antennas with a digital signal processing unit that can change its pattern dynamically to adjust to noise, interference and multipaths. The conceptual block diagram of a smart antenna system is shown in Figure 2.1. The following three main blocks can be identified: (i) array antenna (ii) complex weights and (iii) adaptive signal processor. The array antenna comprises of a Uniform Linear Array (ULA) or Uniform Circular Array (UCA) of antenna elements [3]. The individual antenna elements are assumed to be identical, with omni-directional patterns in the azimuth plane. The signals received at the different antenna elements are multiplied with the complex weights and then summed up. The complex weights are continuously adjusted by the adaptive signal processor which uses all available information such as pilot or training sequences or knowledge of the properties of the signal to calculate the weights. Such a configuration dramatically enhances the capacity of a wireless link through a combination of diversity gain, array gain, and interference suppression. Increased capacity translates to higher data rates for a given number of users or more users for a given data rate per user. This is done so that the main beam tracks the desired user and/or nulls are placed in the direction of interferers and/or side lobes

towards other users are minimized. It should be noted that the term "smart" refers to the whole antenna system and not just the array antenna alone.

Figure-(2.1) Block Diagram of a Smart Antenna System

# 2.3 Smart Antenna Operation

The smart antenna works as follows; assume that there is a user sending a signal to the base station. Then each element of smart antenna array in the base station will receive the signal but at different time instance since the distance between the user and each element of array is different from other elements. By using this time delay and the distance between antenna elements the location of the user can be calculated. Therefore, the transmitter can send a

signal to the exact location of that user. This strategy can be applied for the system with multiple users as well. A smart antenna receiver can suppress the interference by using this strategy. The smart antenna is able to process the signals received by the array or transmitted by the array using suitable array algorithms to improve wireless system performance. An antenna array consists of a set of distributed antenna elements (dipoles, monopoles or directional antenna elements) arranged in certain geometry (e.g., linear, circular or rectangular grid) where the spacing between the elements can vary. The signals collected by individual elements are coherently combined in a manner that increases the desired signal strength and reduces the interference from other signals. Hence a smart antenna can be viewed as a combination of "regular or conventional" antenna elements whose transmit or received signals are processed using "smart" algorithms.

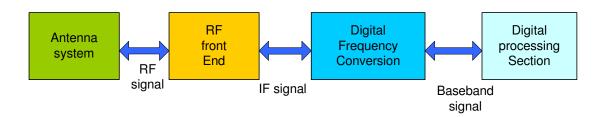

Figure-(2.2) Block diagram of smart antenna implementation

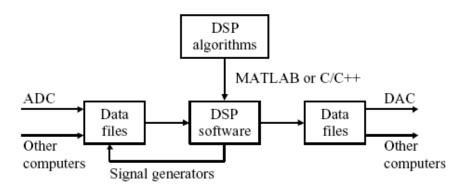

Figure-(2.2) shows a generic implementation of smart antenna system. As shown in this figure, the antenna arrays have input or output as RF signals in the analog domain. These signals are passed to/from the Radio Frequency (RF) analog front end which usually consists of low noise amplifiers, mixers and analog filters. In the receive mode, the RF signals are converted to digital domain by analog to digital converters (ADCs) and in transmit mode, the baseband digital signals are converted to RF using digital to analog converters

(DACs). The down conversion from RF to baseband or up conversion from baseband to RF can involve the use of IF signals. The baseband signals received from each antenna is then combined using the "smart" algorithms in a digital processing section. Each antenna element hence has a RF chain going from the antenna element to RF front end to digital conversion for receiver and vice-versa for transmitter. The digital processing section can be implemented on a microprocessor or a DSP or FPGA. Hence the "smart" algorithm implementation usually is a software code unless implemented in an ASIC or FPGA.

#### 2.4 Classification of Smart Antenna

The fundamental idea behind a smart antenna is not new but dates back to the early sixties when it was first proposed for electronic warfare as a counter measure to jamming [4]. Until recently, cost barriers have prevented the use of smart antennas in commercial systems. Thus in existing wireless communication systems, the base station antennas are either omni-directional which radiate and receive equally well in all azimuth directions, or sector antennas which cover slices of 60 or 90 or 120 degrees [4]. However, the advanced of low cost Digital Signal Processors (DSPs), Application Specific Integrated Circuits (ASICs) and innovative signal processing algorithms have made smart antenna systems practical for commercial use [5]. The smart antenna systems for cellular base stations can be divided into two main categories. These are (i) switched beam system and (ii) adaptive arrays systems. Smart antennas are a solution to capacity and interference problems [4]-[6]. This technology is often described as dynamic sectorization, (i.e. the

cells are Sectorized to reduce interference levels but in a way to enhance the capacity of the cell) or as an adaptive antenna. In either case, most smart antennas form narrow beams directed to each particular user in order to enhance the received signal strength (RSS) and/or signal-to-noise ratio (SNR). Smart antennas can be classified into two types i.e. Switched Beam Systems and Adaptive Array Systems.

# **2.4.1** Switched Beam Systems

A switched beam antenna system consists of several highly directive, fixed, pre-defined beams which can be formed by means of a beamforming network [7] e.g., the Butler 1.2. Smart Antennas for CDMA Cellular System [8, 9] which consists of power splitters and fixed phase shifters. The system detects the signal strength and chooses one beam, from a set of several beams that gives the maximum received power. A switched beam antenna can be thought of as an extension of the conventional sector antenna in that it divides a sector into several micro-sectors [7]. It is the simplest technique and easiest to retro-fit to existing wireless technologies. However switched beam antenna systems are effective only in low to moderate co-channel interfering environments owing to their lack of ability to distinguish a desired user from an interferer, e.g. if a strong interfering signal is at the center of the selected beam and the desired user is away from the center of the selected beam, the interfering signal can be enhanced far more than the desired signal with poor quality of service to the intended user [7].

# 2.4.2 Adaptive Array System

In an adaptive array, signals received by each antenna are weighted and combined using complex weights (magnitude and phase) in order to maximize a particular performance criterion e.g. the Signal to Interference plus Noise Ratio (SINR) or the Signal to Noise Ratio (SNR). Fully adaptive system use advanced signal processing algorithms to locate and track the desired and interfering signals to dynamically minimize interference and maximize intended signal reception [10]. The main difference between a phased array and an adaptive array system is that the former uses beam steering only, while the latter uses beam steering and nulling. For a given number of antennas, adaptive arrays can provide greater range (received signal gain) or require fewer antennas to achieve a given range [11]. However the receiver complexity and associated hardware increases the implementation costs.

Through beamforming, a smart antenna algorithm can receive predominantly from a desired direction (direction of the desired source) compared to some undesired directions (direction of interfering sources). This implies that the digital processing has the ability to shape the radiation pattern for both reception and transmission [12] and to adaptively steer beams in the direction of the desired signals and put nulls in the direction of the interfering signals. This enables low co-channel interference and large antenna gain to the desired signal.

Beamforming systems can be implemented in two ways; fixed beamforming systems or fully adaptive systems. A fixed beamforming system has a beamforming network (BFN) followed by RF switches which operate in the RF/analog domain. The switches are controlled by a control logic which selects a particular beam. Here the processing required is minimal as the

control logic has to choose one of the predetermined set of weights to select a beam. In adaptive beamforming, the antenna gains or weights are chosen adaptively through running array algorithms in the digital domain.

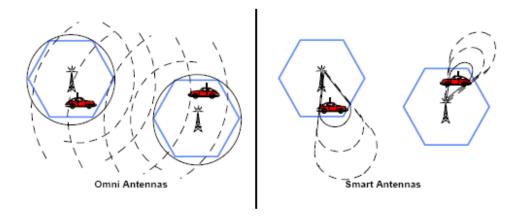

# 2.5 Advantages of Smart Antennas

Primarily smart antennas were used at base stations in a cellular network to improve user capacity. Capacity here refers to the number of subscribers that can be simultaneously serviced in a system. Usage of omnidirectional antennas causes co-channel interference when two users use the same band of frequency that eventually limits the user capacity in a system. Since smart antennas can focus their beams towards desired user reducing interference to other users using the same frequency band, the user capacity in a system can be improved using spatial division multiple access (SDMA). Figure-(2.3) shows this advantage of SDMA compared to the omnidirectional case, which can reduce co-channel interference using beamforming.

Figure-(2.3) Omnidirectional and smart antennas based cellular system

Other advantages as seen from various types of smart antennas studied include robustness against multipath fading and co-channel interference which improves reliability of received signal; reduced power consumption for handsets; low probability of interception and detection; enhanced location estimates and enhanced range of reception. Because there are obstacles and reflectors in the wireless propagation channel, the transmitted signal arrivals at the receiver from various directions over a multiplicity of paths. Such a phenomenon is called multipath. It is an unpredictable set of reflections and/or direct waves each with its own degree of attenuation and delay. Recent studies on use of smart antennas in mobile terminals have also shown to improve network capacity in ad-hoc networks.

Smart antenna systems can improve link quality by combating the effects of multipath propagation or constructively exploiting the different paths, and increase capacity by mitigating interference and allowing transmission of different data streams from different antennas. More specifically, the benefits of smart antennas can be summarized as follows [16]. Some of the advantages of the smart antenna are as follows:

# (i) Increased range/coverage

The *array* or *beamforming gain* is the average increase in signal power at the receiver due to a coherent combination of the signals received at all antenna elements. It is proportional to the number of receive antennas and also allows for lower battery life.

#### (ii) Lower power requirements and/or cost reduction

Optimizing transmission toward the wanted user (transmit beamforming gain) achieves lower power consumption and amplifier costs.

# (iii) Improved link quality/reliability

Diversity gain is obtained by receiving independent replicas of the signal through independently fading signal components. Based on the fact that it is highly probable that at least one or more of these signal components will not be in a deep fade, the availability of multiple independent dimensions reduces the effective fluctuations of the signal.

# (iv) Increased spectral efficiency

Precise control of the transmitted and received power and exploitation of the knowledge of training sequence and/or other properties of the received signal (e.g., constant envelope, finite alphabet, cyclostationarity) allows for *interference reduction/ mitigation* and increased numbers of users sharing the same available resources (e.g., time, frequency, codes) and/or reuse of these resources by users served by the same base station/ access point.

# 2.6 Disadvantages of Smart Antennas

One of the major existing disadvantages of smart antennas is in their design and implementation in hardware. Multiple RF chains can increase the cost and make the transceiver bulkier. Most of the baseband processing requires coherent signals. This means that the entire mixer Local Oscillators and Analogue to Digital Converter clocks (ADCS) need to be derived from same sources. This can present significant design challenges. The phase characteristics of RF components can change over time. These changes are relatively static and hence need calibration procedures to account for phase differences.

Most of the devices such as mixers amplifiers and ADCS used are non-linear devices. Using smart antennas can increase the number of such components used. This can affect the performance of the array if not checked periodically. Further more since antenna arrays use more than one source of signal the data bandwidth required for digital processing increases linearly with number of antenna elements used. This can limit data rates for different applications. Note that the technological challenges in terms of hardware and processing load can be satisfactorily met by resorting to present-day miniaturized RF components and faster and low power processors.

The accommodation of the antenna array, itself within a small factor device however remains a challenge. Base stations can easily host antenna arrays of four or more elements but with existing microstrip or patch antenna technology, up to three elements can be fitted in a handset form-factor. The wrapping of the hand around a handheld device may diminish the performance of a handheld smart antenna system.

# 2.7 Smart Antenna design in wireless Communication Center (WCC)

Base on the importance of smart antenna system in any wireless communication system, Wireless Communication Centre (WCC), Universiti Teknologi Malaysia started working at this project at the beginning of this year. This centre is targeting to implement two types of smart antenna systems. The first project is "Downlink switch beam smart antenna" for WiMax application and second project would be the same system for uplink transmission.

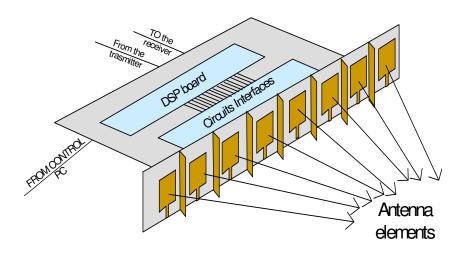

The smart antenna structure for phase one is similar to Figure-(2.4). The antenna elements consist of 16 microstrip antenna elements with

rectangular shape. The algorithm are programmed by computer using C and Code Composer Studio and then loaded in DSP board.

Figure-(2.4) Linear Array Structure

DSP has a main role in smart antenna system. The DSP is used just for forming and steering the beam using the calculated weights in the SDRAM base on the user direction. The location of the user can be identified using one of the directions of arrival algorithm. However, in this research we assume that the location of user is known to the system.

For this project the microstrip antenna array is used. Basically, scanning and shaping the beam is highly depend on array elements pattern. However, any type of antenna such as dipole, monopole, horns, reflectors, loops, aperture depend on application can be used. Compared with other type

of antenna, microstrip antenna for wireless mobile communication could be the best option. The reason is due to its low price, ease of design and fair efficiency rather than other types of antenna.

# 2.8 Design of downlink smart antenna system in WCC

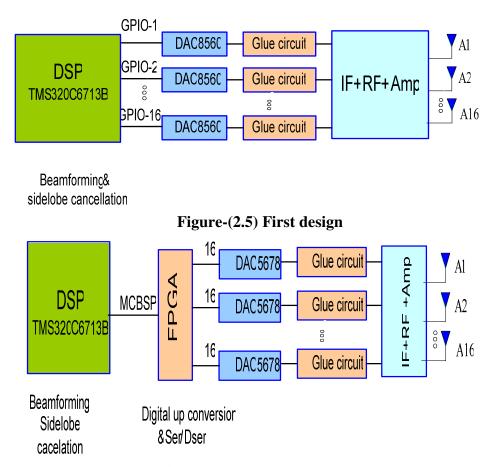

Technically, there are three possible designs which can be considered for this project as shown in Figures-(2.5), (2.6) and (2.7). However, we designed and implement the second structure due to its versatility and performance.

Figure-(2.6) second design

Figure-(2.7) third design

# 2.9 Expansion board design

The difference between abovementioned designs is on the extension or daughter cards. The expansion board design is affected by customer application. Different application has different requirement and constraints. For more throughput and data rate the high sample rate DAC must be used. Technically, the high speed DAC have parallel data inputs, as an example DAC5687 is parallel input DAC with sampling rate up-to 500MS/s. base on these facts, the required expansion board for such an application is different. Therefore some sort of interface matching is needed. The matching can be achieved using FPGA programming. Other than that, sometimes in order to decrease the price, one level of up-conversion is performed in digital domain instead of analog domain. Of course by doing digital up-conversion, the high speed DAC with high sampling rate must be used. Because, DAC must transform the IF digital signal to analog and therefore base on Nyquist criteria sampling frequency increases to double time of higher IF frequency.

Base on these facts, for this project the second option design for the expansion board is chosen Figure-(2.6). In this design, high sampling data rate DAC such as DAC5678 could be connected to FPGA board. We will explain this configuration in detail in FPGA chapter. The next section gives a picture of the third design.

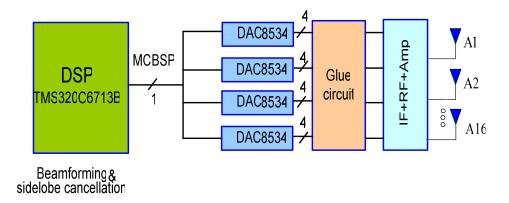

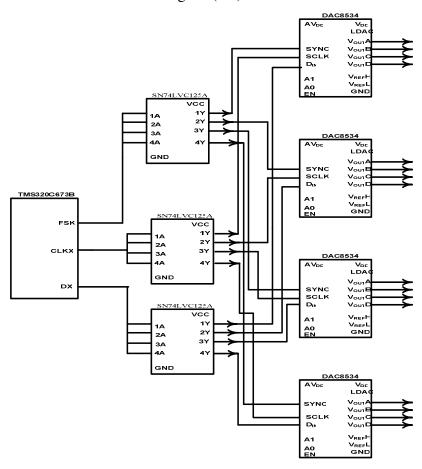

# 2.9.1 The third design using programmable DAC

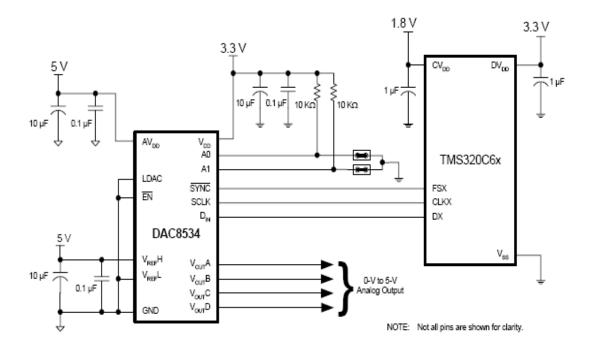

In third design, the daughter card can be designed by using 4 unit of DAC 8534 from TI as shown in Figure-(2.8).

Figure-(2.8) baseband daughter card

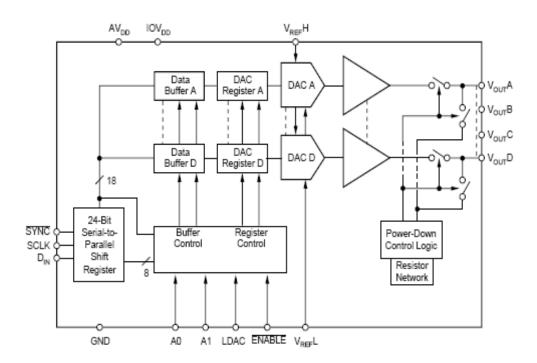

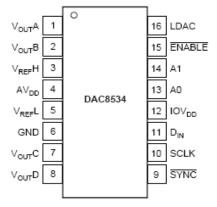

These four D/A are 3-wire standard serial D/A which can be connected to MCBSP through quadruple bus buffer gate "SN74LVC125A". It means they will share the serial channel and they can be synchronized through software programming. The functional block diagram and pin configuration of DAC8534 is shown in Figure-(2.9) and (2.10).

Figure-(2.9) functional block diagram of DAC8534

Figure-(2.10) pin configuration of DAC8534

Figure-(2.11) interfacing a DAC8534 with a TMS320C6713B

# 2.9.1.1 Interfacing a DAC8534 with a TMS320C6713B

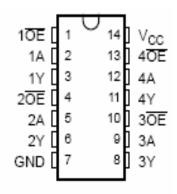

As it can be seen each DAC8534 is able to support four channels, therefore we need to interface 4 unit of DAC8534. Of course we need to amplify the output signal of TMS before connecting to DAC. Therefore, quadruple bus buffer gate "SN74LVC125A" is used to drive 4 unit of DAC. So, the baseband daughter card can be designed as shown in Figure-(2.6). VCC for SN74LVC125A can be up-to 3.6v. This buffer can accept the signal level of up-to 5 volt, the output current of this buffer is around 20mA. The pin configuration of this IC is shown in figure-(2.12).

Figure-(2.12) quadruple bus buffer gate "SN74LVC125A"

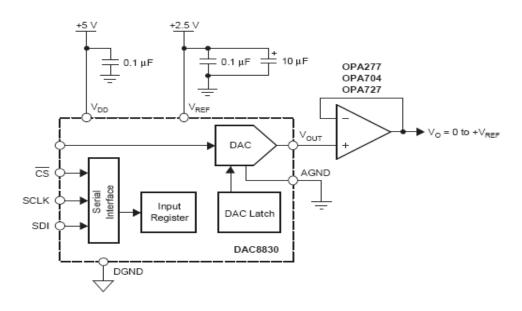

The first possible option for expansion board is much simpler than the other types. For voice application which they need low sampling rate in compare to data communication the possible design could be Figure-(2.4). In this case we need to have 16 number of serial single channel DAC which can directly connect to McASP. The DAC in this case can be DAC8830 shown in Figure-(2.13) which can support up to 50Mb/s.

Figure-(2.13) typical connection of DAC8830

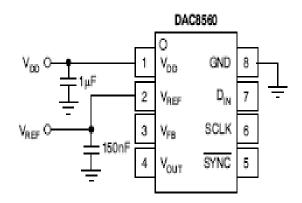

Another DAC option for this case could be DAC8560 shown in Figure-(2.14) which can be clocked at 30MHz. The difference between these two is in control part, DAC8560 can be selected using a chip-select pin, however DAC8830 is enabled by SYNCH pin, also there is some sort of control in input serial data.

Figure-(2.14) typical connection of DAC8560

#### **CHAPTER 3**

## DIGITAL BEAMFORMING WITH DSP BOARD

## 3.1 Introduction

The digital beamforming is integration between antenna technology and digital technology. DBF is based on converting signals into two streams of binary baseband I and Q signals, which represent the amplitudes and phases of signals. The beamforming is carried out by weighting these digital signals, thereby adjusting their amplitudes and phases such that when added together they form the desired beam. In this chapter the digital beamforming by using DSP board is briefly explained fundamentally. First, a general overview on beamforming theory is provided then the DSP board used in this project is introduced. Finally the algorithm of digital beamforming is explained.

## 3.2 Beamforming

Beamforming is one type of processing used to form beams to simultaneously receive a signal radiating from a specific location and attenuate signals from other locations [17]. Systems designed to receive spatially propagating signals often encounter the presence of interference signals. If the desired signal and interference occupy the same frequency band, unless the signals are uncorrelated, e. g., CDMA signals, the temporal filtering often cannot be used to separate signal from interference. However, the desired and interfering signals usually originate from different spatial locations. This spatial separation can be exploited to separate signal from interference using a spatial filter at the receiver. Implementing a temporal filter requires processing of data collected over a spatial aperture.

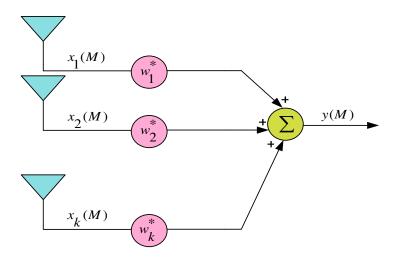

A beamformer is a processor used in conjunction with an array of antennas to provide a versatile form of spatial filtering. The antenna array collects spatial samples of propagating wave fields, which are processed by the beamformer. Typically a beamformer linearly combines the spatially sampled time series from each antenna to obtain a scalar output time series in the same manner that an FIR filter linearly combines temporally sampled data. There are two types of beamformers, narrowband beamformer, and wideband beamformer. A narrowband beamformer is shown in Figure-(3.2).

In Figure-(3.1), the output at time M, y (M), is given by a linear combination of the data at the K sensors at time M:

$$y(M) = \sum_{i=1}^{K} w_i^* x_i(M)$$

(3.16)

Where \* denotes complex conjugate [18]. Since we are now using the complex envelope representation of the received signal, both  $w_i$  and  $x_i(M)$  are complex. The weight  $w_i$  is called the complex weight.

Figure-(3.1) A narrowband beamformer

In this project, for any directions weights are computed for sixteen antenna arrays. In consequence, there are  $7 \times 16 = 112$  weights for seven directions. These weights are complex number, so they can change the phase and amplitude of the original signal. The weights can be expressed as:

$$w_k = e^{-j[(k-1)\frac{2\pi}{\lambda}d\sin\theta]}$$

(3.17)

With replacing the  $d = \frac{\lambda}{2}$ , the equation (3.17) is became:

$$w_k = e^{-j[(k-1)\pi\sin\theta]}$$

(3.18)

For example for DOA=30°, weights can be computed as below:

$$\begin{split} w_1 &= \exp(-j * \pi * (1-1) * \sin(30)) = 1 \\ w_2 &= \exp(-j * \pi * (2-1) * \sin(30)) = -j \\ w_3 &= \exp(-j * \pi * (3-1) * \sin(30)) = -1 \\ &\vdots \\ w_{16} &= \exp(-j * \pi * (16-1) * \sin(30)) = -j \end{split}$$

The matrix of weights for  $\theta = 30^{\circ}$ :

$$\begin{bmatrix} W_{1} \\ W_{2} \\ W_{3} \\ W_{4} \\ \vdots \\ W_{16} \end{bmatrix} = \begin{bmatrix} 1 \\ -j \\ -1 \\ j \\ \vdots \\ -j \end{bmatrix}$$

$$(3.19)$$

## 3.3 DSP Design (Beamforming and sidelobe cancellation)

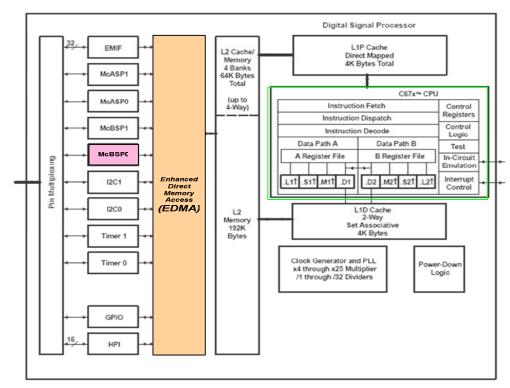

Digital signal processor can be considered as the brain of smart antenna systems. In the other words, the smartness of smart antenna system is originated from this part. For this project 225 MHz DSP, built on the SDK

TMS320C6713B Figure-(3.2) is considered to use. For academicals and researches purposes usually the SDK module (Starter Development Kit) which is a unified kit consists of CPU, memories modules with some extension connector is technically adequate. The dominant advantages of the SDK version over the EVM (evaluation Module) is that the JTAG emulator is built onboard therefore the overall system cost decreases. Although SDK DSP board is designed to ease the academicals researches, it needs to be extended for the desired specific application.

Figure-(3.2) Functional block and CPU (DSP core) diagram

## 3.4 DSP system design

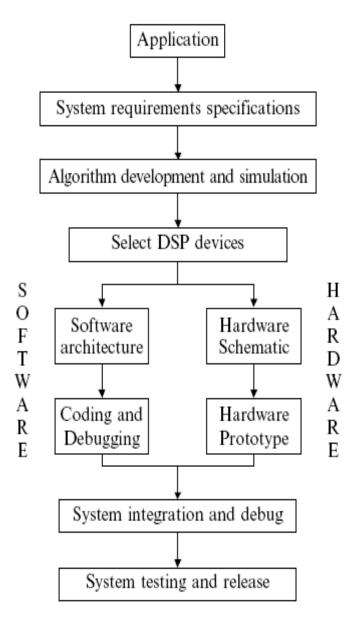

Real time DSP system design is very challenging engineering task. The different group of specialist must work together in order to design the professional DSP system to apply in the real world application. In wide category, the implementation process is divided into software and hardware sections. These two sections as shown in the Figure-(3.3) must progress in parallel.

## DSP SYSTEM DESIGN

Figure-(3.3) simplified DSP system design

The block diagram of software development process of DSP design is given in Figure-(3.4).

Figure-(3.4) software development process diagram

As it is cleared from the Figure-(3.4), firstly the algorithm is designed according to beamforming and sidelobe cancellation algorithms. Then the algorithms are implemented using MATLAB source code, and then these codes are converted to C language code. In the next step using code composer studio which is software capable of generating assembly code will do the rest of process for DSP programming. Then the digital input signal after ADC come to the system and it save as an input file. The loaded program in DSP manipulates the incoming digital signal. Finally, the results save in the output buffer or memory to be ready to send in the next step which is usually digital to analog transformation.

## 3.5 DSP speed and real time constraints

A limitation of DSP systems for real time application is that the bandwidth of the system is limited by the sampling rate. The processing speed determines the rate at which the analog signal can be sampled. For example, a real-time DSP system demands that the signal processing time, tp, must be less

than the sampling period T, in order to complete the processing task before the new sample comes in. That is,

$$t_p < T$$

This real time constraint limits the highest frequency signal can be processed by a DSP system. This is given

$$f_{\scriptscriptstyle M} < \frac{f_{\scriptscriptstyle s}}{2} < \frac{1}{2t_{\scriptscriptstyle n}}$$

It is clear that the longer the processing the lower the signal bandwidth. Or in the other word to perform the wideband signal we need the high speed DSP processor with small amount of processing time for each sample of incoming data. However, this problem can be solved partially using rate converter or CIC filter as long as the quality of the processing is acceptable for that specific application. The DSP processor used for this project is from 6000 series. The specification is given as below:

- 1. Floating point processor

- 2. 2000 million instructions per second (MIPS) at 225 MHz

- 3. One analogue input/output

- 4. Memory module expansion

- 5. Host port interface (HPI)

- 6. Peripheral expansion

- 7. Embedded USB JTAG controller with plug and play drivers, USB cable included

- 8. TI TLV320AIC23 codec

- 9. 16MB SDRAM

- 10. 512K bytes of on board Flash ROM

- 11. On board IEEE 1149.1 JTAG connection

## 3.6 DSP implementation of smart antenna system

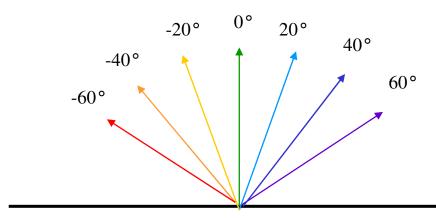

In smart antenna DSP perform just two functions, DOA estimation and beamforming. However, in this project to simplify the implementation process, it is assumed that the direction of the user has been identified before. So, we just need to perform the beamforming process for known direction. By having this assumption in mind, to steer the beam to pre-calculate user direction, the multiplication process of baseband signal to complex number is technically adequate enough. In addition the system is just able to produce one beam toward one single user. It means that to support multiple users simultaneously, the system must produce multiple beams which is out of the project scope. Moreover, to demonstrate the concept of digital beamforming in smart antenna, it is assumed that the application requires having seven beams at the seven desired angle shown in Figure-(3.5) each with 20 degree apart.

Figure-(3.5) the predefined antenna beam direction

By using computer programming, the antenna can steered the beam to these directions at predefined time interval called T. The radiation pattern of the system is optimized by conventional Chebyshev window weighting. By doing so, the side lobes are minimized and also the radiated power toward the desired

user is maximized. It means the total system interference is minimized therefore the SNR increases.

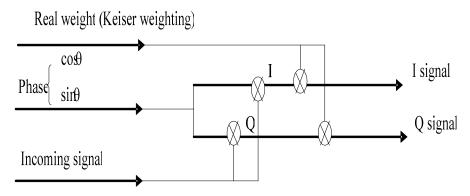

After this introduction, now it is clear that the main important task in baseband processing is just multiplication process of coming signal from conventional wireless transmitter to complex weights. This process is shown in Figure-(3.6).

Figure-(3.6) the beamforming flow

## 3.7 Beamforming matrix

For each direction, there are  $2\times2\times16=64$  multiplication operations. This can be simplified by calculating beamforming matrix before applying in the program. It means that the multiplication process for phase and amplitude is manually performed for each direction before programming. Then the results are stored in the memory called lookup table. It means for the direction of  $\theta$  we would have following operation.

Wkaiser  $\times COS\theta = Wreal$ ; for 7 directions  $7 \times 16$  matrix

Wkaiser  $\times$  SIN $\theta$  = Wimag ; for 7 directions  $7 \times 16$  matrix

If  $A=[Wreal]_{7\times 16}$  and  $B=[Wimag]_{7\times 16}$  then beamformer matrix=[A;B] , therefore it can be saved at the onboard SDRAM on the starter kit (DSK6713), So the RAM expansion is not needed.

## 3.8 Sidelobe cancellation by using DSP

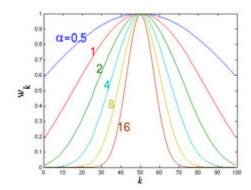

The Kaiser window is a window function  $w_k$  used for digital signal processing, and is defined by the formula:

Kaiser Window function for N=100 and  $\alpha=0.5,1,2,4,8,16$

$$w_k = \begin{cases} \frac{I_0\left(\pi\alpha\sqrt{1-(\frac{2k}{N}-1)^2}\right)}{I_0(\pi\alpha)} & \text{if } 0 \le k \le N \\ 0 & \text{otherwise} \end{cases}$$

Where  $I_0$  is the zeroth order modified Bessel function of the first kind,  $\alpha$  is an arbitrary real number that determines the shape of the window, and the

integer N gives the length of the window (N+1 point).By construction, this function peaks at unity for k = N/2, i.e. at the center of the window, and decays exponentially towards the window edges.

The larger the value of  $|\alpha|$ , the narrower the window becomes;  $\alpha = 0$  corresponds to a rectangular window. Conversely, for larger  $|\alpha|$  the width of the main lobe increases in the Fourier transform of  $w_k$ , while the side lobes decrease in amplitude. Thus, this parameter controls the tradeoff between main-lobe width and side-lobe area, as is illustrated in the plot of the frequency spectra below. For large  $\alpha$ , the shape of the Kaiser window (in both time and frequency domain) tends to a Gaussian curve. The Kaiser window is nearly optimal in the sense of its peak's concentration around  $\omega$ =0 (Oppenheim *et al.*, 1999).

Frequency spectra of Kaiser Windows for  $\alpha$ =2 and  $\alpha$ =4.

The sharp minima in the side lobes are places where the amplitude goes all the way to zero, but does not here because of the finite plotting resolution.

#### **CHAPTER 4**

#### CHANNEL SEPARATION WITH FPGA BOARD

#### 4.1 Introduction

In this chapter the channel separation for smart antenna project is briefly explained. First, a general overview on FPGA board is provided then channel separation is shortly discussed.

## 4.2 Field Programmable Gate Arrays (FPGAs) Overview

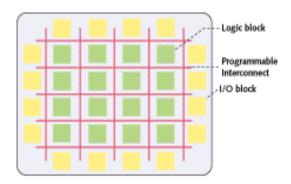

A field-programmable gate array (FPGA) is an integrated circuit (IC) that can be programmed in the field after manufacture. It is containing programmable logic components called "logic blocks", and programmable interconnects. Logic blocks can be programmed to perform the function of basic logic gates such as AND, and XOR, or more complex combinational functions

such as decoders or simple mathematical functions. In most FPGAs, the logic blocks also include memory elements, which may be simple flip-flops or more complete blocks of memories. DSP algorithms may also be implemented using field-programmable gate arrays (FPGAs).

## Advantages of FPGAs:

- **1.** A shorter time to market

- **2.** Ability to re-program in the field to fix bugs

- **3.** Lower non-recurring engineering costs.

## **4.2.1Applications of FPGAs**

Applications of FPGAs include digital signal processor DSP, softwaredefined radio, aerospace and defense systems, ASIC prototyping, medical imaging, computer vision, speech recognition, cryptography, bioinformatics, computer hardware emulation and a growing range of other areas.

#### 4.2.2 FPGAs Architecture

There are three key parts of its structure: logic blocks, interconnect, and I/O blocks. Figure-(4.1) illustrates a typical FPGA architecture. The I/O blocks form a ring around the outer edge of the part. Each of these provides individually selectable input, output, or bi-directional access to one of the general-purpose I/O pins on the exterior of the FPGA package.

Inside the ring of I/O blocks lies a rectangular array of logic blocks. And connecting logic blocks to logic blocks and I/O blocks to logic blocks is the programmable interconnect wiring.

Figure-(4.1) internal structure of an FPGA

The logic blocks within an FPGA can be as small and simple as the macrocells in a Programmable Logic Devices (PLD) or larger and more complex (coarse-grained). However, they are never as large as an entire PLD, as the logic blocks of a Complex Programmable Logic Devices (CPLDs) are. Remember that the logic blocks of a CPLD contain multiple macrocells. But the logic blocks in an FPGA are generally nothing more than a couple of logic gates or a look-up table and a flip-flop.

Because of all the extra flip-flops, the architecture of an FPGA is much more flexible than that of a CPLD. This makes FPGAs better in register-heavy and pipelined applications. They are also often used in place of a processor-plus-software solution, particularly where the processing of input data streams must be performed at a very fast pace. In addition, FPGAs are usually denser (more gates in a given area) and cost less than their CPLD cousins, so they are the de facto choice for larger logic designs.

## 4.3 Altera Excalibur development board

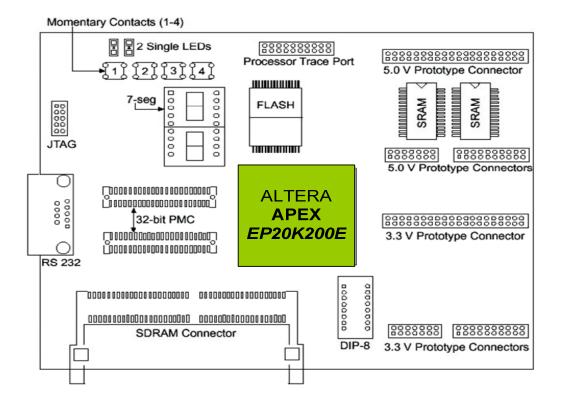

In this project the Altera Excalibur development board is used. . It contains an APEX EP20K200E FPGA, 8Mbits (512K x 16) of internal Flash RAM, two 1Mbit (64K x 16) internal SRAM devices, an RS-232 communication port, a JTAG port, a parallel port, multiple expansion ports, two LEDs, two 7-Segment displays, and miscellaneous other switches and components [19]. Figure 4.2 shows a diagram of the Excalibur board.

Figure-(4.2) the Excalibur Development Board

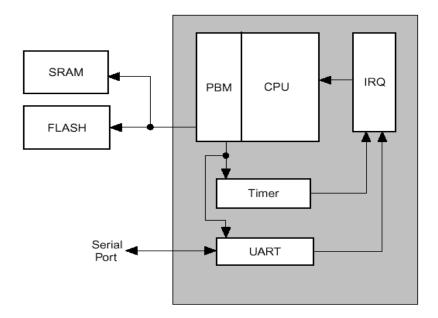

Contained within the APEX EP20K200E device is a Nios embedded processor. This soft core processor contains a 16 bit instruction set and is

capable of operating with a 16 or 32 bit data bus. It can perform 50 million instructions per second with one instruction per clock cycle. With a Nios processor added to the EP20K200E device (as well as a Fast Fourier Transform block), there are still 150K spare gates of the 200K total gates available for use [19]. The structure of the Nios processor resembles Figure 4.3:

Figure-(4.3) the Nios Embedded Processor

The memory on the Excalibur board is set up as follows. The two internal SRAM devices can be used with 16 or 32 bit applications, but if the Nios processor is operating at 16 bits, only one of the two SRAM devices can be used. A 144 pin SODIMM memory expansion socket is also provided on the board if needed. Both the Nios processor and the APEX device share the flash memory [19].

The flash memory is organized as follows:

| Flash Address       | Size       | Comments                                    |

|---------------------|------------|---------------------------------------------|

| 0x1C0000 – 0x1FFFFF | 256 Kbytes | Factory-default APEX Configuration          |

| 0x180000 - 0x1BFFFF | 256 Kbytes | User-defined                                |

| APEX                |            | Configuration data                          |

| 0x100000 – 0x17FFFF | 512 Kbytes | Nios instruction and Nonvolatile data Space |

|                     |            | Space                                       |

Table 4.1 – Flash Memory Configuration of FPGA

A factory programmed controller chip is contained on the board, a MAX7064 device that loads data from the flash and clocks it into the APEX device. It is possible to use user defined configurations by shorting J2 (normally open), and also to reprogram the device, but it is not recommended as it can result in an unusable board. The beginning address for the factory default is 0x1C0000, and for user defined configurations, the starting address is 0x180000 [19].

For expansion purposes, the Excalibur board provides 5 volt and 3.3 volt daughter cards. For 5 volt cards, a 40 pin connector (JP11), a 20 pin connector (JP13), and a 14 pin connector (JP12) are provided. The same applies to 3.3 volt cards, using JP8, JP10, and JP9, respectively [19]. In this project the JP8 is used for transferring data from the DSP to FPGA board. Also, JP10 is used for clock and frame synchronization signals from DSP to FPGA.

There are three devices available for programming on the Excalibur board: the APEX device, the configuration controller, and the PMC (devices for JNC1 and JNC2). The ability to program each is determined by SW8, SW9, and SW10, respectively. If a switch is positioned to the left (marked connect on the board), then the corresponding device is added to the JTAG chain; each switch positioned to bypass will remove the device from the chain [19].

There are seven remaining switches on the board. SW1 is an eight pin user defined DIP switch. SW2 is a special button for resetting the board. Upon a reset, the configuration controller reloads the flash memory into the APEX device. SW3 is the clear function, which is defined by the configuration controller (a CPU reset by factory default). SW4-SW7 is user defined and may perform any function necessary. When pressed, the signals provided are logic zero [19].

There are two clocks for use on the Excalibur board. The first one is a 33.3333MHz signal provided by an onboard oscillator. The second one utilizes the phase locked loop circuitry on the board so the user can create their own clock [19]. In this research, the external clock which is come from DSP board is used.

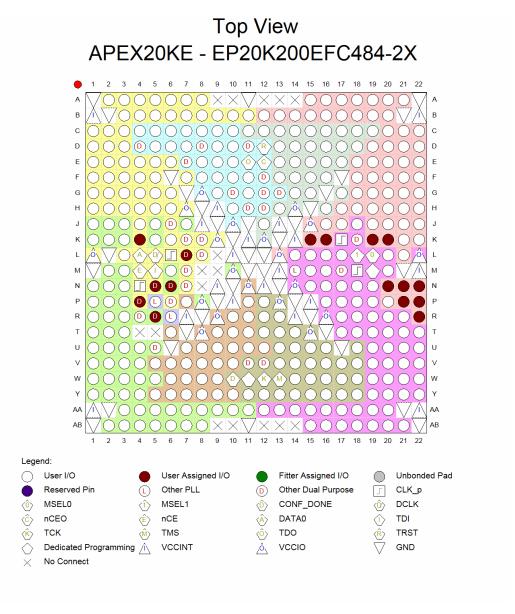

## 4.4 FPGA programming

In this project, the Quartus II software is used for programming the FPGA. This program is written by verilog. After programming the pins of FPGA must be assigned for transferring data to the next part. Figure-(4.4) shows the pins assignment of FPGA.

Figure-(4.4) Pin assignment of FPGA

#### **CHAPTER 5**

# INTERGRATION OF DIGITAL SIGNAL PROCESSOR AND FPGA BOARD

#### 5.1 Introduction

One of the limitations of DSP board is the number of high data rate output port. This board only has two high data rate ports called Multi channel Buffer Serial Port (McBSP). Because of this limitation, the expansion board is needed. In this project, FPGA board is used as an expansion board.

## 5.2 System design

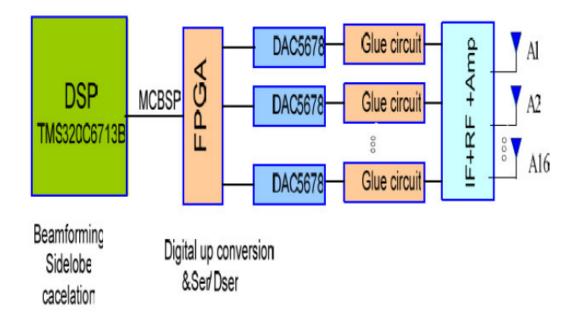

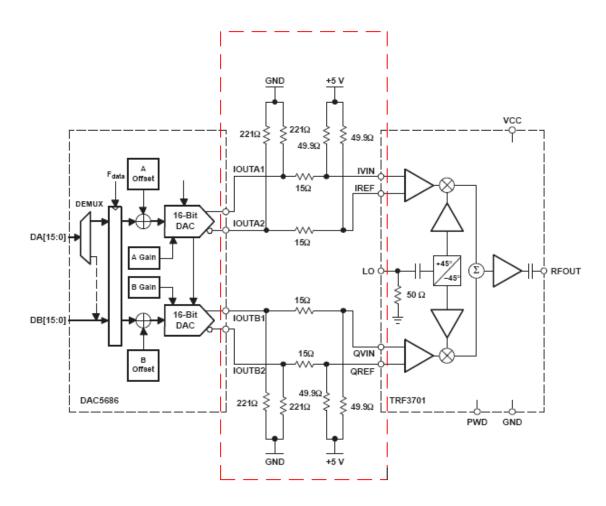

Figure-(5.1) shows the design for the expansion board is chosen for this project. In this design, high sampling data rate DAC such as DAC5678 can be connected to FPGA for digital to analog conversion.

Figure-(5.1) Smart antenna system model

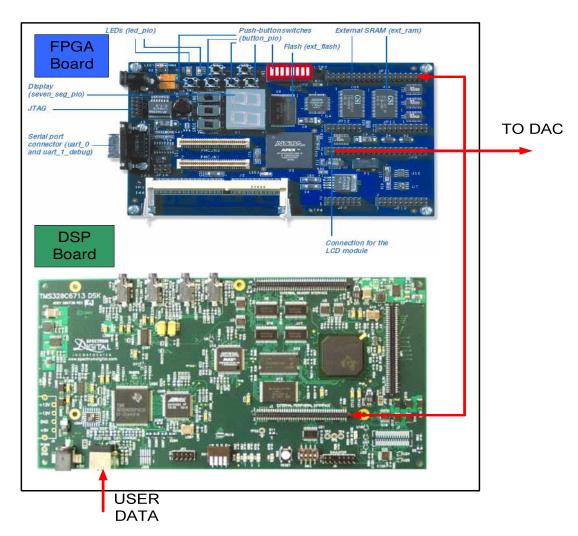

## 5.3 Integration of DSP and FPGA

For connecting the DSP to FPGA, the TMS320C6713 DSK supports three expansion connectors that follow the Texas Instruments interconnection guidelines. The expansion connector used in this project is called Peripheral Expansion Connector (Figure-5.2). It is an 80 pin 0.050 x 0.050 inches connector. This connector provides both +12V and -12V to the daughter card [20].

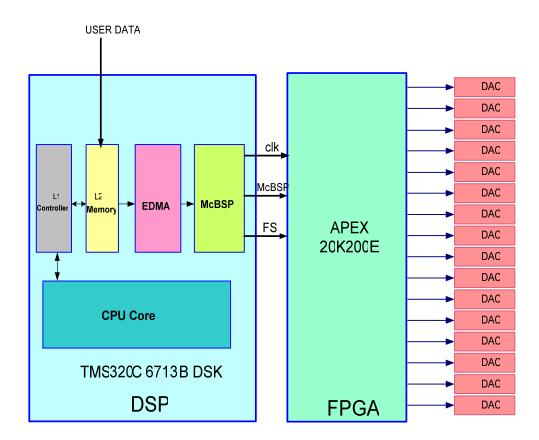

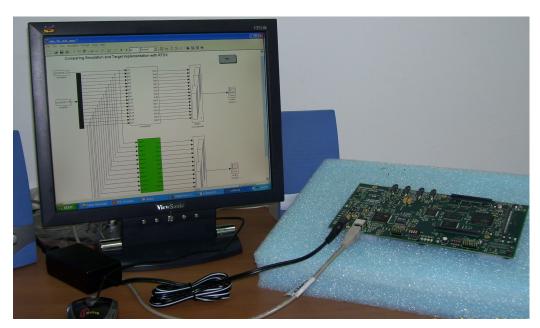

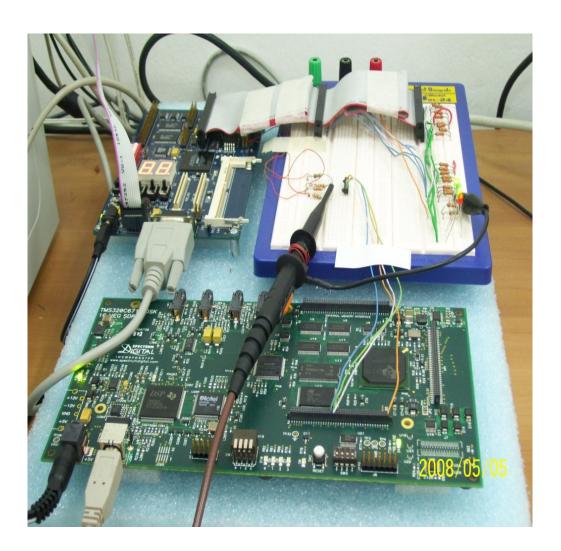

Figure-(5.2) Integration of DSP and FPGA

In this research, firstly for transferring data to device peripherals, EDMA and MCBSP must be programmed. The enhanced DMA (EDMA) controller of the TMS320C6713B device is a highly efficient data transfer engine, capable of maintaining up to 1200 Mbytes per second (MB/s) of data throughput during operation. The EDMA handles all data movement between the level-two memory and the device peripherals (in this project is FPGA), including cache-servicing, non-cacheable memory accesses, user-programmed data transfers, and host accesses (Figure-5.3).

Another part used for transferring data to the FPGA is McBSP ((Figure 5.3). This part provides the following functions:

- Full-duplex communication

- Double-buffered data registers

- Independent framing and clocking for receive and transmit

- External shift clock or an internal

Figure-(5.3) Transferring from DSP and FPGA

# **5.4 Summary**

In this chapter, the integration of DSP and FPGA is explained. For providing this connection, the EDMA and McBSP must be programmed. And these programming is done by using the code composer studio software.

## **CHAPTER 6**

## IF AND RF FRONT-END DESIGN FOR SMART ANTENNA

## **6.1 Introduction**

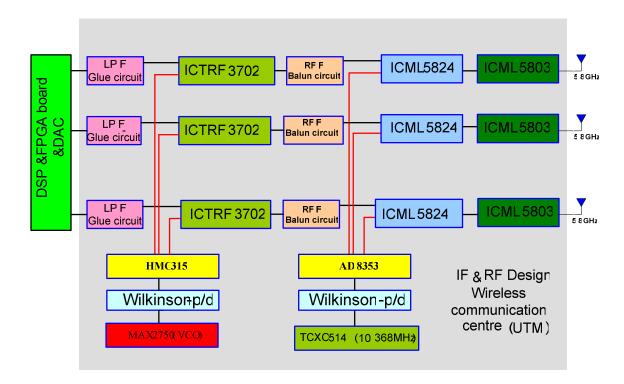

In all above three designs which are discussed in chapter two, we need to have our own design for the IF and RF part because there is no on-the-shelf device RF chain for smart antenna. Although some companies have fabricated IF and RF part, it is very costly and in addition there is no 16 channel IF and RF part! A 16-channel IF and RF chain can be designed as shown in Figure-(6.1).

Figure-(6.1) IF and RF front end design

This RF-front-end can transform the baseband data to 5.8GHz RF signal. This design is integration of TI and Micro linear devices companies. The single channel IF part comes from TI and the single channel RF part is designed by Micro linear company.

## 6.2 Baseband glue circuit

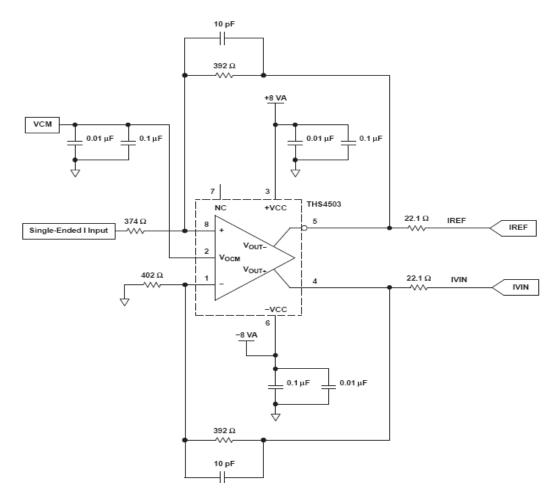

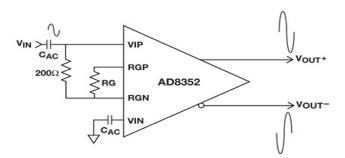

The design is started from multi-channel baseband data which come to the glue circuit in the first step. The data then transform to balanced type using this circuit shown in Figure-(6.2). By using differential signal the noise effect in the IF part can be highly mitigated. This circuit is necessary since the IF transformation is done by TRF3702 is balanced input device.

Figure-(6.2) connecting the single ended signal to balanced input of TRF3702

The glue circuit for the second expansion board shown in Figure-(2.10) can be similar to Figure-(6.3) because in this case we do not need to design Balun circuit. Therefore, the Glue circuit as shown in dash-line in Figure-(6.3) could be very simple.

Figure-(6.3) glue circuit connecting the DAC5687 to TRF3702

# **6.3 Quadrature-modulator**

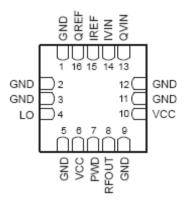

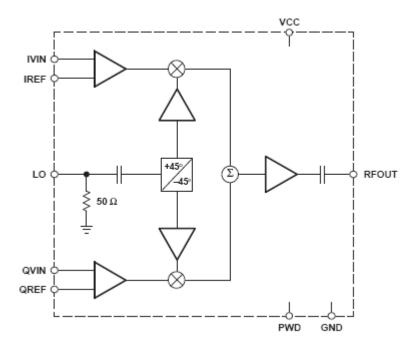

TRF3702 is an IF to RF up-converter, the pin arrangement shown in Figure-(6.4) this IC can up-convert the baseband or IF signal to 2.4GHz signals.

Figure-(6.4) TRF3702 pin arrangement

The functional block diagram of the TRF3702 is shown in Figure-(6.5). This component is able to work with I and Q signals. However, in our project the signal is just real signal therefore the Q signal must be grounded.

Figure-(6.5) TRF3702 functional block diagram

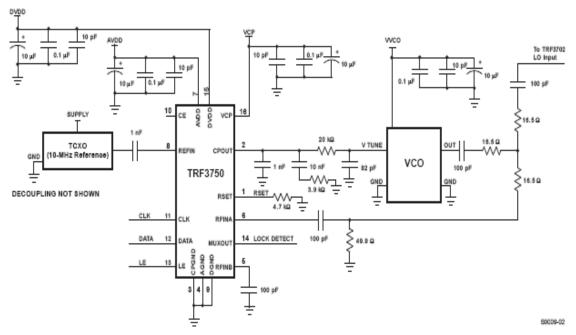

Figure-(6.6) Generating the LO signal for TRF3702 using TRF3750

## 6.4 local oscillators for 2.4GHz signal

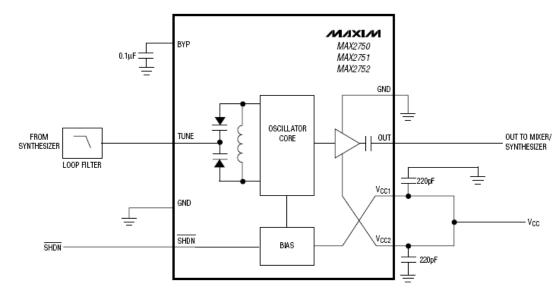

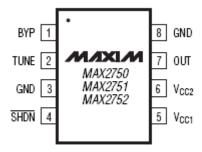

If the modulator need to works with multi carrier system, the TRF3750 shown in Figure 4.6, can be used as a frequency synthesizer. This PLL can generate different frequency components for the system. However, in our system the single RF frequency at is needed. Therefore, we can use a VCO to generate 2.4 RF sin frequencies. The VCO is considered for this project is "MAX2750" from MAXIM Company.

Figures 6.7 and 6.8 are shown the typical layout and pin configurations of for MAX2750. The MAX2750/MAX2751/MAX2752 VCOs are implemented as an LC oscillator topology, integrating all of the tank components on-chip. This fully monolithic approach provides an extremely easy-to-use VCO, equivalent

to a VCO module. The frequency is controlled by a voltage applied to the TUNE pin, which is internally connected to a varactor.

Figure-(6.7) the typical layout for" MAX2750"

The VCO core uses a differential topology to provide a stable frequency versus supply voltage and improve the immunity to load variations. In addition, there is a buffer amplifier following the oscillator core to provide added isolation from load variations and to boost the output power.

Figure-(6.8) the pin configuration for" MAX2750"

## 6.5 Wilkinson power divider

A 2.4GHz and 10.368 MHz Wilkinson power divider also need to be designed to equally divide the LO and reference frequency of IF and RF part to their counterparts.

## **6.6 Balun Circuits**

Since, the output of TRF3702 is single ended, the either Balun circuit of in Figure 3.13 by using AD8352 or a Balun chip shown in Figure 6.9 circuit can be used. The Balun prior to ML5824 circuit is needed since the input of ML5824 is differential input.

Figure 6.9 Balun circuit before ICML5824, CAC=0.1μf RG=120KΩ

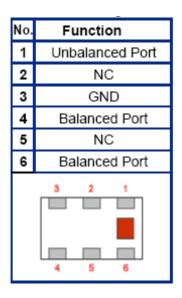

This Balun figure 6.10 circuit functions at 2GHZ, the better choice could be 2450BL15B200 from Ceramic solution which is simple solution for this purpose at the frequency of 2.4. The pin configuration can be seen in figure below.

Figure 6.10 Balun circuit configurations at 2.4 GHz

## **6.7** Temperature compensated crystal oscillator (TCXO)

The Temperature compensated crystal oscillator (TCXO 514) from Oscillant Company can be used in RF part as a reference frequency. The value of reference RF reference frequency value is 10.368MHz.

Figure-(6.11) low profile TCXO-514 frequency range 1.2 to 100MHz

The oscillator for the RF part is a built in oscillator which is built on ML 5824. However, for the IF part the oscillator is voltage controlled oscillator (VCO).

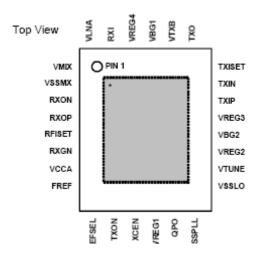

Figure-(6.12) ML5824 top-views

## 6.8 linear RF and IF amplifier

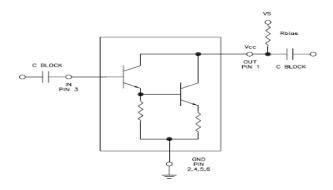

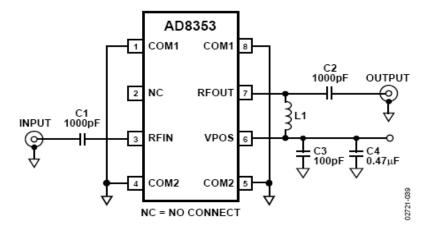

The Wilkinson power divider divide the power in 16 branch, therefore power amplification is necessary prior to LO in TRF3702. Either of amplifiers in figure 6.13 and 6.14 can be used for this project for the 2.4GHz. However, for the second power Wilkinson AD8353 should be used.

Figure-(6.13) HMC315 linear amplifier frequency range up-to 7 GHZ (C block=0.1micro, Rbias=5k)

Figure-(6.14) AD8353 amplifier (frequency range 1 MHZ up-to 2700 GHZ)

## 6.9 Second up-converter

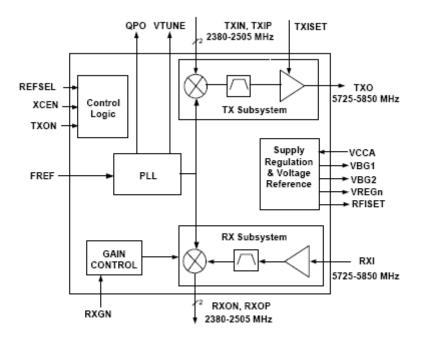

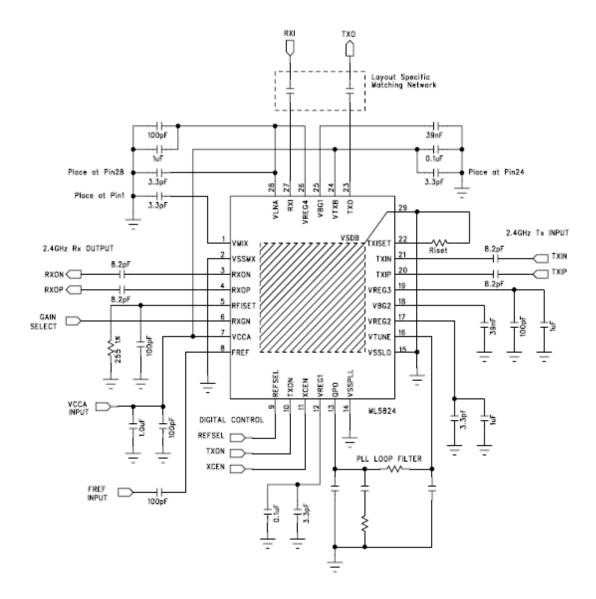

The Ml5824 is a cost effective solution to up-convert 2.4 signals to 5.8 RF signals, in this project to simplify the RF design we used, this IC following by ML5803 a power amplifier. The functional block diagram of ML5824 is shown in figure 6.15.

Figure-(6.15) Ml5824 functional block diagram

Figure-(6.16) ML5824 glue circuits

#### **CHAPTER 7**

#### ANTENNA ARRAY DESIGN AND FABRICATION

#### 7.1 Introduction

An antenna array consists of a set of antenna elements that are spatially distributed at known locations with reference to a common fixed point [21]. By changing the phase and amplitude of the exciting currents in each of the antenna elements, it is possible to electronically scan the main beam and/or place nulls in any direction.

The antenna elements can be arranged in various geometries, with linear, circular and planar arrays being very common. In the case of a linear array, the centers of the elements of the array are aligned along a straight line. If the spacing between the array elements is equal, it is called a uniformly spaced linear array. A circular array is one in which the centers of the array elements lie on a circle. In the case of a planar array, the centers of the array elements lie on

a single plane. Both the linear array and circular array are special cases of the planar array. Arrays whose element locations conform to a given non-planar surface are called conformal arrays.

The radiation pattern of an array is determined by the radiation pattern of the individual elements, their orientation and relative positions in space, and the amplitude and phase of the feeding currents. If each element of the array is an isotropic point source, then the radiation pattern of the array will depend solely on the geometry and feeding current of the array, and the radiation pattern so obtained is called the array factor. If each of the elements of the array is similar but non-isotropic, by the principle of pattern multiplication, the radiation pattern can be computed as a product of the array factor and the individual element pattern [22].

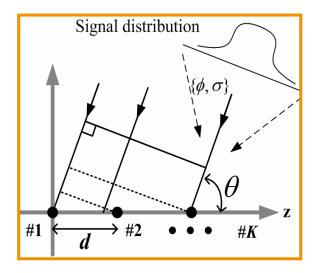

### 7.2 Uniformly Spaced Linear Array

Consider a K-element uniformly spaced linear array which is illustrated in Figure-(7.1). In Figure-(7.1), the array elements are equally spaced by a distance d, and a plane wave arrives at the array from a direction  $\theta$  of the array broadside. The angle  $\theta$  is called the *direction-of-arrival* (DOA) or *angle-of-arrival* (AOA) of the received signal, and is measured clockwise from the broadside of the array [23]. The received signal at the first element may be expressed as:

$$y_1(t) = m(t)\cos wt \tag{7.1}$$

$$y_1(t) = m(t)\cos(2\pi f_C t)$$

(7.2)

Figure-(7.1) linear array antenna

Where the carrier frequency of the modulated signal is  $f_c$  and m(t) is the amplitude of the signal. The complex envelope of y1(t) is given by:

$$y_1(t) = m(t)e^{jwt} (7.3)$$

And the received signal of the second element may be expressed as

$$y_2(t) = m(t - \tau)\cos w(t - \tau) \tag{7.4}$$

If the carrier frequency  $f_c$  is large compared to the bandwidth of the signal ( $\tau \ll t$ ), then the modulating signal in above equation reduces to:

$$y_2(t) = m(t)\cos w(t - \tau) \tag{7.5}$$

The complex envelope of y2(t) is therefore given by

$$y_{2}(t) = m(t)e^{jw(t-\tau)} = m(t)e^{j(wt-w\tau)}$$

$$y_{2}(t) = m(t)e^{j(2\pi f_{c}t - 2\pi f_{c}\tau)}$$

$$y_{2}(t) = m(t)e^{j(2\pi f_{c}t - 2\pi f_{c}\tau)}$$

$$y_{2}(t) = m(t)e^{j(2\pi f_{c}t - 2\pi f_{c}\tau)}$$

$$(7.6)$$

Comparing (7.6) with (7.3):

$$y_2(t) = y_1(t)e^{-j2\pi f_c \tau}$$

(7.7)

We have used the relation between c and  $f_c$ , that is,  $f_c = \frac{c}{\lambda}$

$$y_2(t) = y_1(t)e^{-j\frac{2\pi c}{\lambda}\tau}$$

$$(7.8)$$

The signal arrives at second element after  $d \sin \theta$  compare to first element so, the time delay is given by

$$\tau = \frac{d\sin\theta}{c} \tag{7.9}$$

The received signal, at the second element is written as equation (7.10)

$$y_{2}(t) = y_{1}(t)e^{\left(-j\frac{2\pi c}{\lambda}\frac{d\sin\theta}{c}\right)}$$

$$y_{2}(t) = y_{1}(t)e^{-j\left(\frac{2\pi}{\lambda}d\sin\theta\right)}$$

$$y_{2}(t) = y_{1}(t)e^{-j\left(\frac{2\pi}{\lambda}d\sin\theta\right)}$$

(7.10)

Similarly, for element i, the complex envelope of the received signal may be expressed as

$$y_{i}(t) = y_{1}(t)e^{-j(\frac{2\pi}{\lambda}(i-1)d\sin\theta)}$$

$$i = 1,...,k.$$

(7.11)

Adding all the element outputs together gives what is commonly referred to as array factor F:

$$F(\theta) = y_1 + y_2 e^{-j\frac{2\pi}{\lambda}d\sin\theta} + \dots = \sum_{k=1}^{k} y_k e^{-j\frac{2\pi}{\lambda}(k-1)d\sin\theta}$$

(7.12)

The equation (7.12) can be expressed in terms of vector inner product:

$$F(\theta) = y(t)v(\theta) \tag{7.13}$$

Where

$$H_C(z) = 1 - z^{-RM} (7.14)$$

$$v(\theta) = \begin{pmatrix} 1 \\ -j\frac{2\pi}{\lambda}d\sin\theta \\ \vdots \\ -j\frac{2\pi}{\lambda}(k-1)d\sin\theta \end{pmatrix}$$

(7.15)

The vector  $F(\theta)$  is often referred to as the array input data vector, and  $v(\theta)$  is called the steering vector. In the equation (7.15), the signal is assumed to be narrowband.

### 7.3 Antenna array design and fabrication for smart antenna project

The required linear array antenna firstly designed by Microwave software. However, the software were not able to calculate return loss for 16 linear patches properly although it is able to calculate the radiation pattern correctly. Therefore, the CST software with higher reliability is used for array designs.

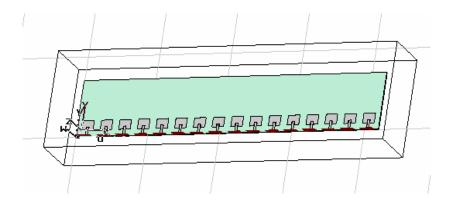

Figure-(7.2) front-view of linear antenna array (CST)

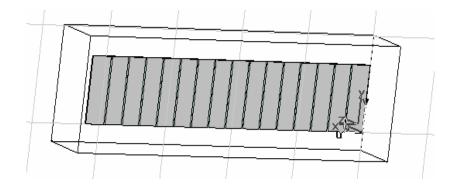

Figure-(7.3) back-view of linear antenna array (CST)

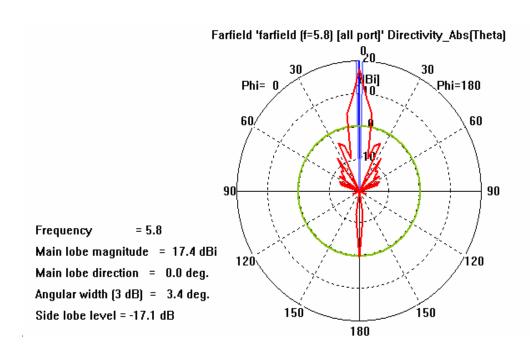

Figure-(7.4) the radiation pattern in direction of o degree

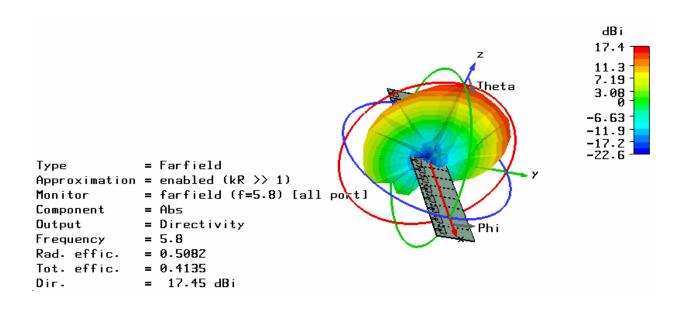

Figure-(7.5) the 3D radiation pattern in direction of o degree

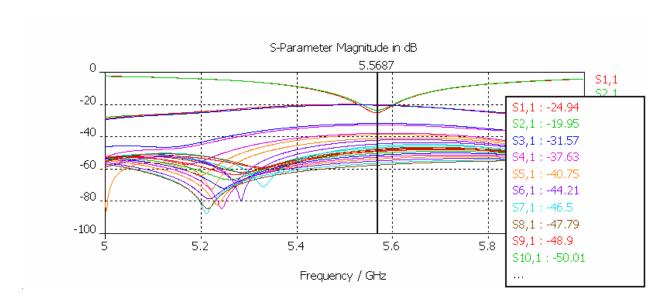

Figure-(7.6) the simulation results for return loss

Figure-(7.7) fabricated linear antenna array

The experimental results for return loss for each patch are around 21dB which is not exactly the same as simulation results. However, it can work well in real situation.

#### **CHAPTER 8**

#### SIMULATION RESULTS

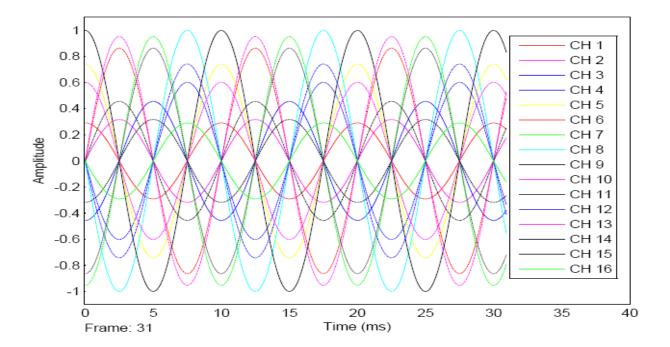

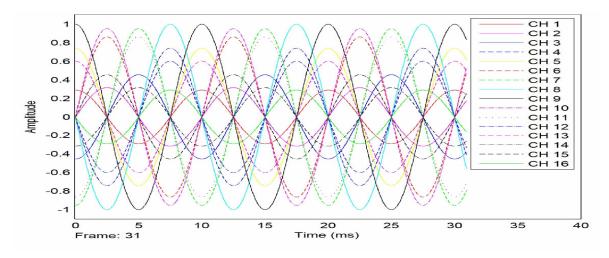

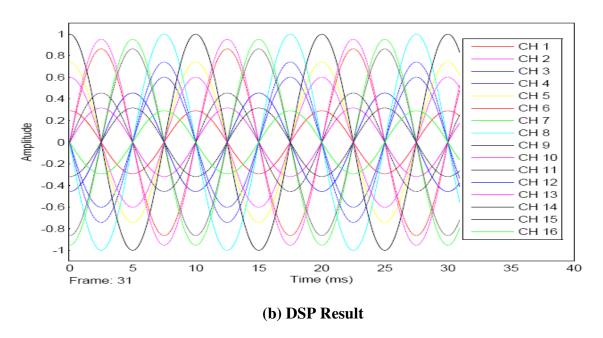

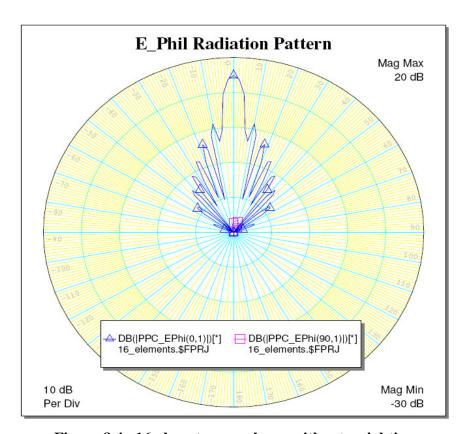

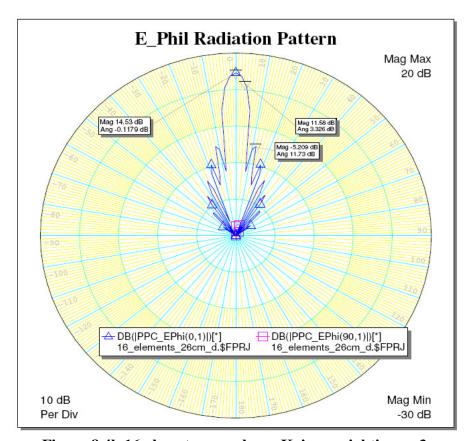

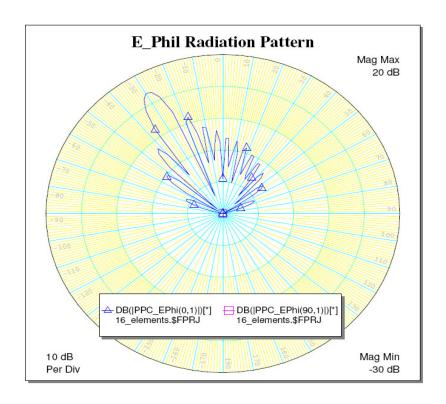

#### 8.1 Introduction