# Design of Power Stage and Controller for DC-DC Converter Systems Using PSPICE

N. D. Muhamad, M. R. Sahid, A. H. M. Yatim, N. R. N. Idris, and M. S. Ayob

Power Electronic Research Group (PERG)

Faculty of Electrical Engineering

Universiti Teknologi Malaysia

81310 UTM Skudai, Johor

Malaysia.

nikd@fke.utm.my

Abstract—A complete set of SPICE-compatible design equations for design buck converter system is developed in this paper. In this approach, the power stage and controller design equations are programmed in PSPICE. For this purpose, an option available in PSPICE called Analog Behavioral Modeling (ABM) is used. In this manner, the parameter of power stage and the component values of the error amplifier can be easily obtained by means of PSPICE bias point analysis. The obtained parameters can be passed to other circuit models to perform frequency response and transient analysis. The methodology of development is presented in details. A design example is included to demonstrate the effectiveness of the proposed approach in designing DC-DC converter systems.

Keywords-DC-DC Converter, Computer-aided design, PSPICE, Control loop design, Small-signal model

# I. INTRODUCTION

In designing DC-DC converter systems, there are two requirements to be satisfied: steady-state and dynamics. The steady-state requirements can be satisfied by properly choosing the parameters of the power stage. The dynamic requirements can be met by using an appropriate controller. There are a number of well-documented techniques and guidelines available for designing DC-DC converter systems [1-6]. Today, most DC-DC converter system design is carried out with the aid of a computer-aided circuit analysis program such as PSPICE. There are many SPICE-based models developed for simulating DC-DC converters. In general, three types of model can be identified: the detailed model, the large-signal averaged model, and the small-signal model. All three models are useful in analysis and design of DC-DC converter systems. The small-signal model is required to design the control system of a DC-DC converter. However, the use of PSPICE is limited to validation of circuit designs. A DC-DC converter design usually needs some theoretical analysis and calculation. This makes calculation software, such as Mathcad, often used along with PSPICE in the process of design. The use of software in addition to PSPICE causes the process of design to be somewhat inconvenient and inefficient.

In this paper we demonstrate that PSPICE alone can be used to design DC-DC converter systems. The design equations can be programmed in compact form in PSPICE. For this purpose, an option available in PSPICE called Analog Behavioral Modeling (ABM) is used. Both steady-state and dynamic design equations are programmed. A set of design equations is made as a subcircuit model and stored in PSPICE's library. In this manner, the subcircuit of design equations can be treated as a library component, making it easy to use. The presence of this type of subcircuit in PSPICE makes a new approach to using PSPICE simulator in process of design. This approach includes both design as well as simulation tools thus making extensive use of PSPICE in DC-DC converter design cycle. Moreover, both the flexibility and capability of PSPICE as a stand-alone program can be enhanced. This approach will facilitate the design of DC-DC converter systems in PSPICE and it will make the design more convenient and efficient.

Throughout this paper, a buck converter with voltage mode control is used as an example to develop and verify the design procedure. The general procedure, however, can still be readily extended to include other converters with different control schemes provided that their transfer functions and design equations are available.

# II. DESIGN PROCESS

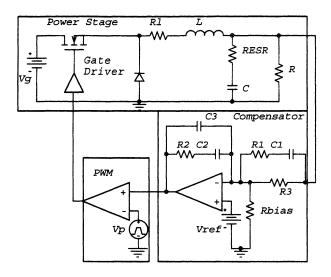

The buck converter with voltage mode control is shown in Fig. 1. This converter is used to illustrate the design process and demonstrate its feasibility for DC-DC converters design. The converter system comprises the power stage, the compensator and the pulse-width modulator (PWM). The converter is assumed to be in continuous conduction mode (CCM) of operation.

## A. Power Stage, PWM modulator and Controller

Using the averaging and linearization techniques, the control-to-output transfer function of the buck converter including PWM, can be obtained as

$$\frac{\hat{v}_o}{\hat{v}_c} = g_{co} \frac{\left(1 + \frac{s}{\omega_{zESR}}\right)}{1 + \frac{s}{Q\omega_o} + \frac{s^2}{\omega_c^2}} \tag{1}$$

where

$$g_{co} = \frac{V_g}{V_p}$$

,  $\omega_o = \frac{1}{\sqrt{LC}}$ ,  $\omega_{zESR} = \frac{1}{R_{ESR}C}$ , and  $Q = \frac{R}{\omega_o L}$

Figure 1. Buck converter with voltage mode control

For the circuit in Figure 1 the power stage has the following parameters:  $V_g = 12V$ ,  $V_0 = 5V$ ,  $R = 1.25~\Omega$ ,  $Rl = 50m\Omega$ . The power stage design parameters are inductance Lf, capacitance, Cf and ESR of capacitor,  $R_{ESR}$ . The peak value of PWM,  $V_p$ , is assumed to be 3 V. The compensator network consists of R1, R2, R3,  $R_{bias}$ , C1, C2, C3 and Vref. We assume that the value of  $V_{ref}$  is 2. 5V,  $R_{bias}$  is 10 k $\Omega$  and the rest are design parameters.

#### B. Power Stage Design Equations

The values of L, C, and  $R_{ESR}$  determine CCM of operation and a prespecified peak-to-peak output voltage ripple. For a given switching frequency, power stage components L, C, and  $R_{ESR}$  may be selected to meet the following criteria:

$\it I)$  The value of inductance is chosen to assure CCM. To maintain CCM down to one-fifth output current  $\it I_o$ , the minimum value for L is

$$L_{\min} = \frac{2.5(V_g - V_o)D}{f_s \frac{V_o}{R}}$$

(2)

where V<sub>o</sub>, f<sub>s</sub>, R, and D are the output voltage, switching frequency, load resistance and steady state duty ratio respectively.

2) Capacitance C is determined from maximum allowable peak-to-peak output ripple voltage  $V_{pp} = \Delta v_c$  considerations:

$$\Delta v_c \le \Delta v_{c,c} + \Delta v_{c,ESR}$$

where  $\Delta v_{c,c}$  is the AC component of the voltage across the R<sub>ESR</sub> and  $\Delta v_{c,ESR}$  is the AC component voltage across the filter capacitance, C. However, it is known that the peak-to-peak ripple voltage is independent of the voltage across the filter capacitance [7] and is determined only by the ripple voltage of the R<sub>ESR</sub> if

$$C \ge C_{\min} = \max\left(\frac{1 - D_{\min}}{2R_{ESR}f_s}, \frac{D_{\max}}{2R_{ESR}f_s}\right)$$

(3)

3) The peak-to-peak voltage ripple,  $\Delta v_c$ , is usually given as a percentage of the output voltage, typically equal to or less than 1%. If the condition described by (3) is satisfied,  $R_{ESR}$  for the prespecified peak-to-peak voltage ripple is

$$R_{ESR} \le \frac{\Delta v_c f_s L}{V_o (1 - D_{\min})} \tag{4}$$

## III. COMPENSATOR DESIGN EQUATIONS

The loop shaping approach is simple and effective for dealing with the plants having complex dynamic behavior. Among popular loop shaping method in power electronic applications is K-factor approach, introduced in [4]. The main feature of K-factor approach is that the circuit component values can be obtained without trial-and-error. This is one of the reasons why the K-factor approach is widely accepted by many researchers [9-12]. Since the analysis of the control loop design equations using K-factor approach in PSPICE has been published earlier [6] we repeat here, for the sake of brevity, only the essential.

The type-3 error amplifier is commonly used for compensation of buck, boost and buck-boost circuits due to its ability to provide the phase boost, \$\phi\$boost:

$$0 \le \phi_{hoost} \le 180^{\circ} \tag{5}$$

The transfer function of the type-3 error amplifier is given by

$$G_c(s) = \frac{\frac{\omega_{co}}{A_{co}K} \left(\frac{\sqrt{K}}{\omega_{co}}s + 1\right)^2}{s \left(\frac{s}{\sqrt{K}\omega_{co}} + 1\right)^2}$$

(6)

where  $\omega_{co}$  is the desired crossover frequency, K is the pole frequency and zero frequency control factor. The value of K can be adjusted depending on the phase boost  $(\phi_{boost})$  required to make the phase compensation. To use the K-factor approach, the crossover frequency,  $f_{co}$ , must be chosen, and then the gain,  $A_{co}$  and the phase,  $\phi_{co}$ , of power stage at  $\omega_{co}$  must be found. In short, the computation procedures of K-factor approach are as follows:

1) Calculate the gain,  $A_{co}$  and the phase,  $\phi_{co}$ , of power stage at  $\omega_{co}$ :

$$A_{co} = \left| \frac{v_o}{v_c} \right| = \frac{G_{co} \sqrt{1 + \left(\frac{\omega_{co}}{\omega_{zesr}}\right)^2}}{\sqrt{\left(1 - \left(\frac{\omega_{co}}{\omega_o}\right)^2\right) + \left(\frac{\omega_{co}}{Q\omega_o}\right)^2}}$$

(7)

$$\phi_{co} = \tan^{-1} \frac{\omega_{co}}{\omega_{zesr}} - \tan^{-1} \frac{\frac{\omega_{co}}{Q\omega_o}}{1 - \left(\frac{\omega_{co}}{\omega_o}\right)^2}$$

(8)

2) By knowing  $A_{co}$ , and  $\phi_{co}$ , and specifying the phase margin, PM, the phase boost required can be calculated as

$$\phi_{hoost} = PM - 90^{\circ} - \phi_{co} \tag{9}$$

3) Then, K-factor is calculated as

$$K = \tan^2 \left( \frac{\phi_{boost}}{4} + 45^{\circ} \right) \tag{10}$$

4) The two poles of the compensator are located at

$$\omega_{p12} = \frac{\omega_{co}}{\sqrt{K}} \tag{11}$$

5) The two zeros of the compensator are located at

$$\omega_{z12} = \sqrt{K}\omega_{co} \tag{12}$$

6) The integrator gain of the compensator is

$$\omega_i = \frac{\omega_{co}}{A_{co}K} \tag{13}$$

It is important to point out that this design procedure is general in the sense that it can be used to any suitable applications. For a specific application, this design procedure must be suited to the requirements of those applications. In the case of buck converter, an important constraint is that the crossover frequency must be less than one-fourth of the switching frequency. This constraint is required to avoid the large signal instability [1]. The design of compensator follows the design of power stage because power stage parameters, such as filter inductance, capacitance, and ESR of capacitance, are needed. The next step is to convert the obtained values of poles and zeros to the component values of compensator. This is a straightforward process. In short, the conversions occur as follows:

$$C_3 = \frac{f_{z12}}{(\omega_i R_3 f_{\rho_{12}})} \tag{14}$$

$$C_2 = C_3 \left( \frac{f_{p12}}{f_{z12}} - 1 \right) \tag{15}$$

$$R_2 = \frac{1}{2\pi f_{z12} C_2} \tag{16}$$

$$R_1 = \frac{R_3}{\left(\frac{f_{p12}}{f_{z12}} - 1\right)} \tag{17}$$

$$C_1 = \frac{1}{2\pi f_{\pi/2} R_1} \tag{18}$$

$$R_{bias} = \frac{V_{ref}}{V_o - V_{ref}} R_3 \tag{19}$$

#### IV. PSPICE IMPLEMENTATION

The PSPICE simulator is provided with an extension called Analog Behavioral Modeling (ABM). With ABM the simulator can be used like a programming language and to solve general mathematical problems by translating them to an electrical circuit. ABM in PSPICE is able to evaluate expressions that are functions of circuit variables (voltages, currents, and simulation time) using the controlled current and voltage sources (G and E devices). ABM can also be used to solve system of linear and nonlinear algebraic equations as well as systems of complex,

transcendent and ordinary, differential equations in their implicit or explicit form. In each case, the equations are converted into electrical circuits and solved by PSPICE with a DC analysis for only algebraic equations or a transient analysis for systems of algebraic and differential equations. Editing the input file of PSPICE is relatively more comfortable than programming in MATLAB, C or other programming languages.

To implement the equations in PSPICE, all variables are coded into voltages. The relevant equations are represented by dependent sources that are function of the coded variables and constants. There are two parts of design equations to be programmed in PSPICE: power stage and control loop. The power stage design equations to be programmed are equations (2)-(4), while the control loop design equations are equations (7)-(19). All the equations are implemented in PSPICE by using the .PARAM statement. By using the .PARAM statement we can create parameters and assign algebraic mathematical expressions to it. To enable the related parameters available in schematic, ABM parts are used. The complete PSPICE listing of design equations is given in Appendix.

# V. DESIGN EXAMPLE

A design example is used to demonstrate the effectiveness of the proposed approach in designing DC-DC converters. The example is a buck converter operated in continuous conduction mode (CCM) with the switching frequency,  $f_s$  =100 kHz. The only known parameters are: input voltage  $V_g$  = 12V, output voltage,  $V_o$  = 5V, sawtooth peak voltage of PWM,  $V_p$  = 3V, reference voltage,  $V_{ref}$  = 2.5V. The value of  $R_{bias}$  is chosen arbitrarily as 10 k $\Omega$ . For the control loop design, the crossover frequency,  $f_{co}$ , is chosen as  $f_s/6$  and the phase margin is chosen as  $60^\circ$ . This is a typical specification to design the compensator of a buck converter.

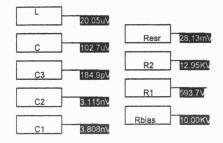

All the given parameters above serve as inputs to the programmed design equations. It outputs the following parameters: *L*, *C*, *R<sub>ESR</sub>*, *C1*, *C2*, *C3*, *R1*, *R2*, and *R3*. Since PSPICE simulator always performs bias point analysis before performing other analysis, these values can be passed to other circuit models in order to perform the other analysis such as transient and frequency response. By doing so, the design phase and the verification phase appear to be simultaneously performed by PSPICE. Obviously, this is one of the advantages to program the design equations in PSPICE.

In this design example, the design parameters were passed to the averaged circuit models to perform frequency response and transient analysis. The design parameters were also passed to the switching detailed model to perform transient analysis (cycle-by-cycle simulation). The result of design parameters obtained by bias point analysis of PSPICE is shown in Fig. 2. It can be seen from the result that all the obtained parameters were given in volt due to all the variables were already coded into voltages.

Figure 2. The result of design parameters using PSPICE bias point analysis

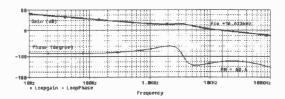

Using averaged circuit model, frequency response of loopgain based on the averaged circuit model was simulated by PSPICE AC analysis. The result is shown in Fig. 3. From the bode plot, we can see that the crossover phase is  $-119.6^{\circ}$ , indicating stable operation with PM of  $60.4^{\circ}$ . The crossover frequency is at 16.623 kHz. The differences between the desired values (PM =  $60.0^{\circ}$  and  $f_{co}$  = 16.667kHz) and the results of PSPICE are fairly small.

Figure 3. Bode plot of loop-gain (gain in dB and phase in degree)

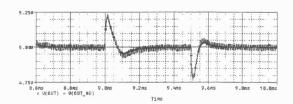

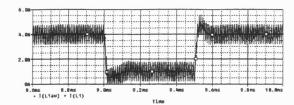

Transient analysis of the output voltage and the inductor current based on the averaged circuit and switching detailed models are shown in Fig. 4 and 5, respectively. Both the results of the averaged and switching detailed model are superimposed in the same graphs for comparison. It can be seen that, both the waveforms agree very well. To evaluate the performance of the system, load steps were performed. The load steps were programmed to step-down at 9.0 ms (from 4A to 1A) and to step-up at 9.5 ms (from 1A to 4A). It can be seen that the step responses of the inductor current and the output voltage reflect the behavior of a system with phase margin of about 60°, verifying the design.

Figure 4. Load step responses of the output voltage

In order to make the design equations easy to use, it was made as a subcircuit model and stored in PSPICE's library. In this manner, the design equations are treated as a library component.

Figure 5. Load step responses of the inductor current

#### VI. CONCLUSION

A complete set of SPICE-compatible design equations for design buck converter systems has been developed. Both power stage and controller design equations are programmed in PSPICE. Using this method, the design parameters can be easily obtained by means of PSPICE bias point analysis. The obtained design parameters can be consecutively passed to other circuit models to perform the other analysis such as transient and frequency response. The extension of this approach to other converters and control schemes like peak current mode (PCM), average current control (ACC) and power factor correction (PFC) is straightforward provided that there exist small-signal models and their design procedures.

# ACKNOWLEDGMENT

The authors would like to thank the Research Management Center (RMC), Universiti Teknologi Malaysia, for the financial support provided under Grant No. 71435 to carry out this research.

#### REFERENCES

- L. H. Dixon, "Closing the feedback loop," Unitrode Power Supply Design Seminar Handbook: SEM 700A, 1990.

- [2] W. Tang, F. C. Lee and R. B. Ridley, "Small-Signal Modeling of Average Current-Mode Control," IEEE Trans. Power Electronics, Vol. 8, no. 2, pp. 112-119, Apr. 1993.

- [3] Holland, "Modeling, Analysis and Compensation of the Current-Mode Converter," Proc. of the Powercon 11, pp. I-2-1-I-2-6,1984.

- [4] H. D. Venable, "The k-factor: A New mathematical Tool for Stability, Analysis, and Synthesis," Proceeding of Powercon 10, San Diego, CA, March 22-24, 1983.

- [5] L. H. Dixon, "Average Current Mode Control of Switching Power Supplies," Unitrode Application Note, 1999.

- [6] N. D.Muhamad and A. J. Shafie, "An approach to PSPICE-Aided Control Loop Design of DC-DC Converter System," Proc. of PECon, Bangi, Malaysia, Dec. 15-16, 2003.

- [7] D. Czarkowski and M. K. Kazimierczuk, "Static and Dynamic Circuit models of PWM buck-derived DC-DC Converters, "IEE Proc. Part G, Circuit Devices and Systems, Vol. 139, No. 6, pp. 669-679, Dec. 1992.

- [8] J. Sun, R. M. Bass, "Modeling and Practical design issues for Average Current Control," Proc. of APEC, Vol. 2, pp. 980-986, 1999.

- [9] S.A. Chickamenahalli, "Effect of target impedance and control loop design on VRM stability," *Proc. Of APEC*, Vol. 1, 2002.

- [10] A. I. Pressman, Switching Power Supply Design, McGrawHill, 1998.

- [11] N. Mohan, T. M. Undeland, W. P. Robins, Power Electronics: Converters, Applications and Design, John Wiley, 1995.

- [12] C. M. Liaw, T. H. Chen, W.L. Lin, "Dynamic modelling and control of a step up/down switching-mode rectifier," IEE Proc. - Electric Power Applications, Vol. 146 Issue: 3, pp. 317–324, May 1999.

#### APPENDIX

# PSPICE Listing for Power Stage and Control Loop Design Equations

## Power Stage and Control Loop Design Equations

PARAMETERS: PARAMETERS: pi = 3.14159265 PARAMETERS: | Tydown | 1-10. | L = (1.1\*Lmin) | Resr = {IF(0.9\*Rc>40m,40m,0.9\*Rc)} | C = (1.1\*Cmin) | R3 = 10k | Vp = 3 | Vref = 2.5V  $\label{eq:mag_Buck_LC} \begin{tabular}{ll} \hline Mag_Buck_LC = ($VgNp)/SQRT(((w/(Q^w)))^*(w/(Q^w)))+(1-(w^w)/(wo^wo)))^*(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))^*(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo)))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(wo^wo))+(1-(w^w)/(ww)/(ww)+(w^w)/(ww)+(w^w)/(ww)+(w^w)/(ww)+(ww)/(ww)+(ww)/(ww)+(ww)$ Q = {R/(wo\*L)} wo = {1/SQRT(L\*C)}  $f = \{fco\}$ fs = 100k fco = 16.666k PARAMETERS: PARAMETERS: PowerStage = {Mag\_Buck\_LC\*Mag\_Buck\_Zesr} PARAMETERS: Ph\_PowerStage = {Ph\_Buck\_Zesr+Ph\_Buck\_LC}  $\overline{wi = \{w/(Aco^*k)\}}$ wp12 = {w\*sqrt(k)} wz12 = {w/sqrt(k)} PARAMETERS: PARAMETERS: Mag\_Buck\_LC\_at\_fco = {(Vg/Vp)/SQRT(((wco/(Q\*wco))\*(wco/(Q\*wco)))+(1-(wco\*wco/(wo\*wo)))\*(1-(wco\*wco/(wo\*wo))))}

Mag\_Buck\_Zesr\_at\_fco = {SQRT((1+(wco\*wco)/(wzesr\*wzesr)))}

Mag\_Buck\_fco = {Mag\_Buck\_LC\_at\_fco\*Mag\_Buck\_Zesr\_at\_fco} Vg = 12 Vo = 5 R = 1.25 PARAMETERS: PARAMETERS: PARAMETERS: PARAMETERS:

Cmin = {max((1-D)/(2\*Rc\*fs),D/(2\*Rc\*fs))} Rc = {fs\*Lmin\*Vr/(Vo\*(1-D))} PM = 60

Vr = {PVC\*Vo/100} PVC = 1 Lmin = {5\*(Vg-Vo)\*D/((PIL/10)\*fs\*Vo/R)} D = {Vo/Vg}  $\begin{array}{ll} \text{riv} = \text{ou} & \text{Lmin} = \{5^*(Vg\text{-Vo})^*D/((PlL/10)^*fs^*Vo/R) \\ \text{Aco} = \{PowerStage\} & D = \{Vo/Vg\} \\ \text{Pc} = \{Ph\_PowerStage\} & PlL = 20 \\ \text{k} = \{(Tan(((Pboost/4)^*45)^*pi/180))^*(Tan(((Pboost/4)^*45)^*pi/180)))} \\ \text{Pboost} = \{PM\text{-90-Pco}\} \\ \end{array}$

PIL: Percentage of Inductor Current PVC: Percentage of Capacitor Voltage