# Group Key Management: Algorithms, Benchmarking, and Reconfigurable Architectures

Vom Fachbereich Informatik der Technischen Universität Darmstadt genehmigte

#### **DISSERTATION**

zur Erlangung des akademischen Grades eines Doktor-Ingenieurs (Dr.-Ing.)

von

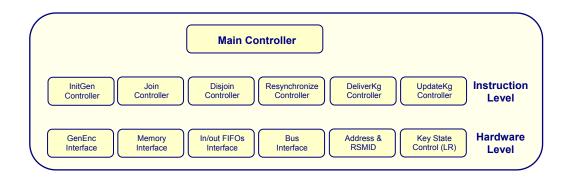

# Dipl.-Ing. Abdulhadi Shoufan

aus Homs-Syrien

Referenten der Arbeit: Prof. Dr.-Ing. Sorin A. Huss

Prof. Dr.-Ing. Klaus D. Müller-Glaser

Tag der Einreichung:06.02.2007Tag der mündlichen Prüfung:30.03.2007

To Mother & Father and to Madieha ZUSAMMENFASSUNG V

# Zusammenfassung

IP Multicast ist eine effiziente Lösung für Gruppenkommunikation über das Internet. Sowohl die Serverressourcen als auch die Netzbandbreite werden durch diese neue Technologie entlastet. Spezielle Probleme und Herausforderungen entstehen allerdings, wenn die Gruppenkommunikation Sicherheitsanforderungen erfüllen muss. Ein wichtiger Aspekt bezieht sich auf die gemeinsame Nutzung eines Kommunikationsschlüssels. Dieser Schlüssel muss nämlich jedes Mal aktualisiert und verteilt werden, wenn die Gruppenzusammensetzung sich ändert. Dieser Prozess, der als *Rekeying* bezeichnet wird, wirft ein *Skalierbarkeitsproblem* für große dynamische Gruppen auf: Das Rekeying basiert auf rechenaufwendigen kryptographischen Operationen und erfordert die Übertragung von Rekeyingnachrichten. Das Skalierbarkeitsproblem zeichnet sich daher durch ein Rechenoverhead auf der Serverseite und durch ein Kommunikationsoverhead im Übertragungsnetzwerk aus.

In der Literatur wurden zahlreiche Architekturen, Algorithmen und Protokolle publiziert, die dieses Skalierbarkeitsproblem adressieren. Lösungen zur Optimierung der Rekeyingperformanz konzentrieren sich auf die Minimierung der Anzahl der erforderlichen kryptographischen Operationen und somit der Länge der Rekeyingnachrichten. Eine akzeptierte Strategie zur Reduzierung der Rekeyingkosten verwendet eine Stapelverarbeitung von Rekeyinganfragen, die innerhalb eines festgelegten Rekeyingintervalls gesammelt werden. Eine Spezifizierung der maximalen Länge dieses Intervalls fehlt jedoch in der Literatur bisher. Zu lange Rekeyingintervalle verursachen längere Wartezeiten für neue Mitglieder und längere Zugriffszeiten für Verlassende. Folglich ist die Stapelverarbeitung von Rekeyinganfragen stets verbunden mit einem Verlust an Dienstgüte einerseits und an der Systemsicherheit andererseits. Aufgrund der Neuigkeit und der Komplexität dieses Forschungsgebiets vermissen die präsentierten Lösungen eine einheitliche Methode zur Abschätzung der Rekeyingperformanz. In den meisten Fällen wird dadurch eine Evaluierung von verschiedenen Rekeyingalgorithmen enorm erschwert.

Die vorliegende Dissertation erörtert die oben erwähnten drei Probleme des Gruppenrekeying. Erstens wird eine Methode präsentiert, die die Probleme der Dienstgüte und der Sicherheit im Stapelrekeying adressiert. Diese Methode wird als *Ereignisgesteuertes Stapelrekeying* bezeichnet. Zweitens wird ein *Rekeyingbenchmark* eingeführt, der einen einheitlichen zuverlässigen Weg zur Abschätzung der Rekeyingperformanz verschiedener Rekeyingalgorithmen darstellt. Drittens werden drei innovative Hardware-und HW/SW-Architekturen zur Optimierung der Rekeyingperformanz präsentiert. Im

Unterschied zu bisherigen Lösungen wird die Rekeyingperformanz durch diese Architekturen nicht nur auf der algorithmischen Rekeyingebene optimiert, sondern auf der kyptographischen Ebene und auf der Plattformebene. Die neuen Architekturen werden als der Real-Time Rekeying Processor, der Batch Rekeying Processor und der High-Flexibility Rekeying Processor bezeichnet.

Preface

# **Preface**

IP multicast is an efficient solution for group communication over the Internet, as both the sender resources and the network bandwidth are relieved with the aid of this emerging technology. However, this superiority suffers, when the group communication must fulfill some security requirements. An essential issue relates to sharing the communication key. Particularly, this key must be updated and securely distributed, every time the group membership changes. This process, which is denoted as *group rekeying*, raises a scalability problem in large dynamic groups: Rekeying is based on computationally extensive cryptographic operations and on the dissemination of rekeying messages. Thus, the scalability problem presents itself by a computation overhead on both the sender and the receiver sides, and by a communication overhead in the network.

Numerous architectures, algorithms, and protocols have been proposed in the literature to cope with this scalability problem. Related work on *optimizing rekeying performance* mostly concentrates on minimizing the number of required cryptographic operations and thus the length of the rekeying message. An accepted strategy to reduce rekeying costs utilizes batch processing of rekeying requests, which are summed up during a rekeying interval. However, a specification of the maximal length of this rekeying interval is not provided, so far. Too long rekeying intervals cause longer waiting times for new members and longer access times for removed ones. Consequently, a *problem of QoS and security* is associated with batch rekeying. Because of its novelty and complexity, the work on rekeying optimization lacks a unified way to estimate rekeying performance. In most cases, therefore, an *evaluation of different algorithms* is impossible.

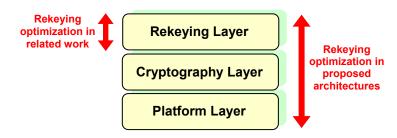

The presented dissertation addresses the above three problems of group rekeying. Firstly, an approach, denoted as *Even-Driven Batch Rekeying*, is proposed to tackle the QoS and security problems caused by long rekeying intervals in batch rekeying. Secondly, to enable a reliable evaluation of rekeying algorithms, a *Rekeying Benchmark* is introduced, which provides a unified way to estimate the performance of different rekeying algorithms on the system level. Thirdly, three novel hardware and hardware/software architectures are presented for optimizing the rekeying performance. In contrast to related work, these architectures, denoted as the *Real-Time Rekeying Processor*, the *Batch Rekeying Processor*, and the *High-Flexibility Rekeying Processor*, optimize rekeying not only on the rekeying algorithm level, but also on the cryptography and platform levels.

ACKNOWLEDGMENTS ix

# Acknowledgments

This work developed during my activity as scientific assistant in the Integrated Circuits and Systems Laboratory at the University of Technology Darmstadt. Though a doctorial thesis is related to its author, I can not forget the great support of other people, estimable people.

### A grateful word of thanks to

Prof. Dr. Sorin A. Huss, my advisor. Only with his directing, without to enforce, his advices, without to restrict, and with his energy, without to disturb, it was possible to accomplish this work in the best working atmosphere and in the right time.

Prof. Dr. Klaus D. Mueller-Glaser, my co-referee for taking the time and making the effort to read this work and comment it constructively.

All my colleagues for the nice time and the friendly cooperation, Maxim Anikeev, Tom Assmuth, Markus Ernst, Prih Hastono, Stephan Hermanns, Dan Honciuc, Elisabeth Hudson, Adeel Israr, Michael Jung, Andreas Kuehn, Joseph Laschgari, Ralf Laue, Steffen Klupsch, Stephan Klaus, Tim Sander, Maria Tiedemann, Juergen Weber, Song Yuan, and Kaiping Zeng.

All the students, who substantially supported the realizations presented in this thesis and other research work, Mujtaba Abrooy, Peter Bungert, Murtuza Cutleriwala, Zhaoming Dai, Torsten Hahn, Nico Hubert, Marcus Lindner, Dominik Litzinger, Felix Madlener, Joana Otetelisanu, Sven Rettig, Abdeloahid Tadoo, Bieanvenu Tatsi, and Tobias Teichner.

My teacher and role model Zaki Ramdoun.

My mother and my father for their love, generosity, patience, and stamina. Despite the modest means, they managed to bring four of five sons and the only daughter to complete study.

My wife Madieha for the wonderful years with her, for her advices and her comments regarding this work.

Syria, which produced me, and Germany, which refined me.

# Content

|   |       | menfassung                              |      |

|---|-------|-----------------------------------------|------|

|   |       | e                                       |      |

|   |       | vledgments                              |      |

| C |       | ıt                                      |      |

| 1 | Intro | duction                                 |      |

|   | 1.1   | Overview                                |      |

|   | 1.2   | IP Multicast                            |      |

|   | 1.2.1 |                                         |      |

|   | 1.2.2 |                                         |      |

|   |       | Information Security                    |      |

|   | 1.3.1 |                                         | 5    |

|   | 1.3.2 | - Jr - 6 - r J                          |      |

|   | 1.4   | Secure Multicast                        |      |

|   | 1.4.1 |                                         | 8    |

|   | 1.4.2 | C Group Rekeying                        |      |

|   | 1.5   | Work Objectives and Outline             |      |

| 2 | QoS   | and Access Control Aware Batch Rekeying | . 15 |

|   | 2.1   | Overview                                | . 15 |

|   | 2.2   | Batch Rekeying                          | . 15 |

|   | 2.3   | Problems of Batch Rekeying              | . 16 |

|   | 2.3.1 | Join Batch Delay                        | . 17 |

|   | 2.3.2 | 2 Disjoin Batch Delay                   | . 17 |

|   | 2.4   | Optimized Batch Rekeying                | . 18 |

|   | 2.4.1 | - F                                     | . 18 |

|   | 2.4.2 | r                                       |      |

|   | 2.4.3 | Event-driven Batch Rekeying             | . 19 |

|   | 2.5   | Case Studies                            | . 21 |

|   | 2.6   | Summary                                 |      |

| 3 | Reke  | eying Benchmark                         |      |

|   | 3.1   | Overview                                | . 25 |

|   | 3.2   | Rekeying Performance Evaluation Problem | . 25 |

|   | 3.3   | Rekeying Benchmark Design Concept       |      |

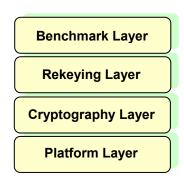

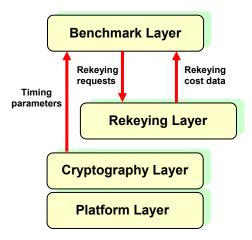

|   | 3.3.1 | Benchmark Abstraction Model             | . 28 |

|   | 3.3.2 | Benchmark Data Flow                     | . 30 |

|   |       |                                         |      |

|   | 3.4   | Rekeying Benchmark as a Simulation Environment | 31 |

|---|-------|------------------------------------------------|----|

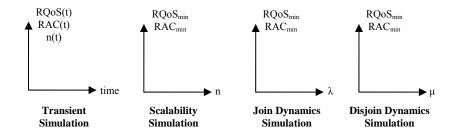

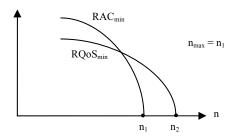

|   | 3.4.1 | Cost metrics and Evaluation Criteria           | 31 |

|   | 3.4.2 | Simulation Modes                               | 33 |

|   | 3.5   | Rekeying Benchmark Design                      | 36 |

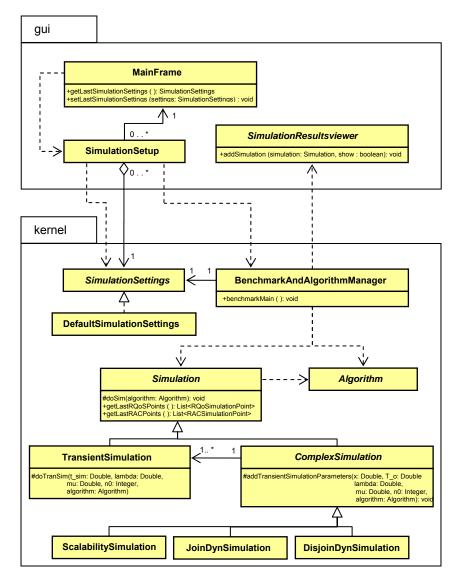

|   | 3.5.1 | General Architecture                           | 36 |

|   | 3.5.2 | Request Generator                              | 38 |

|   | 3.5.3 | •                                              |    |

|   | 3.5.4 |                                                |    |

|   | 3.6   | Implementation                                 | 50 |

|   |       | Case Study (LKH Tree Rebalancing)              |    |

| 4 |       | nfigurable Architectures                       |    |

|   |       | Overview                                       |    |

|   |       | Introduction                                   |    |

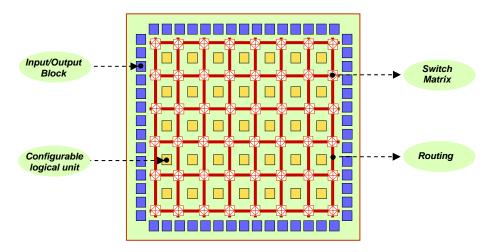

|   |       | Field Programmable Gate Arrays                 |    |

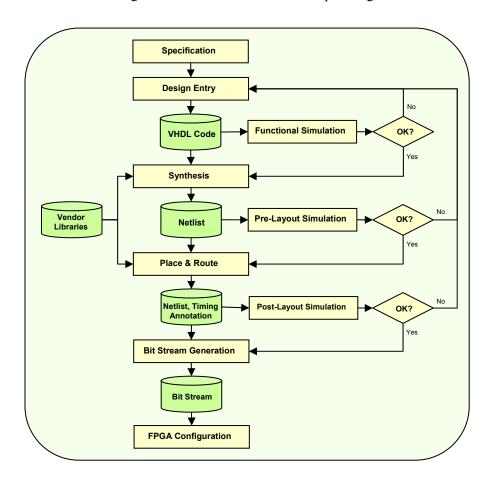

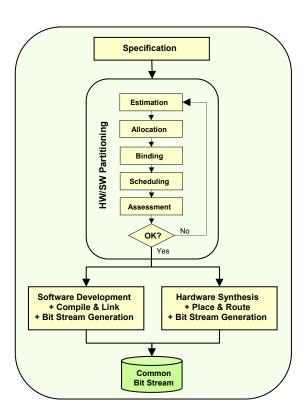

|   |       | FPGA Design Process                            |    |

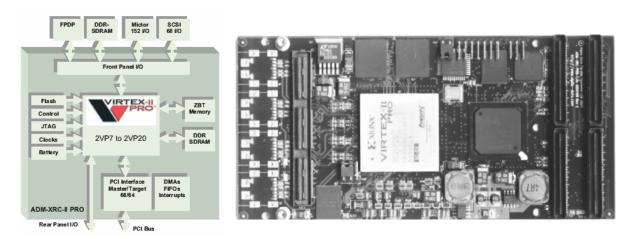

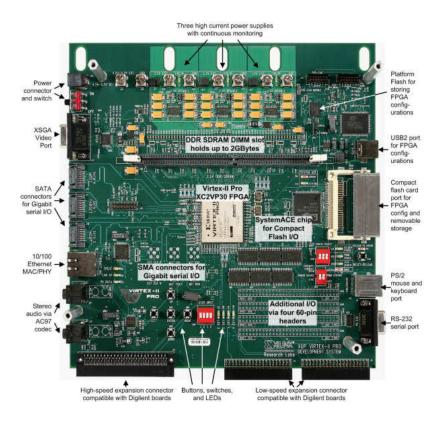

|   |       | Deployed Hardware Platforms                    |    |

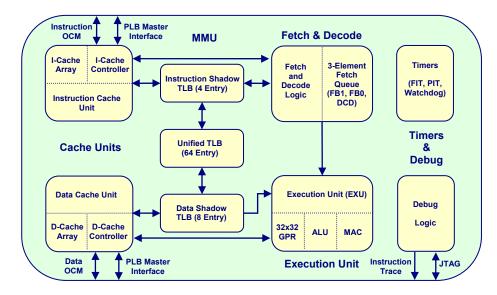

|   | 4.5.1 | • •                                            |    |

|   | 4.5.2 |                                                |    |

| 5 | New   | Architectures for Group Rekeying               |    |

|   |       | Overview                                       |    |

|   |       | Introduction                                   |    |

|   |       | Rekeying Security Requirements                 |    |

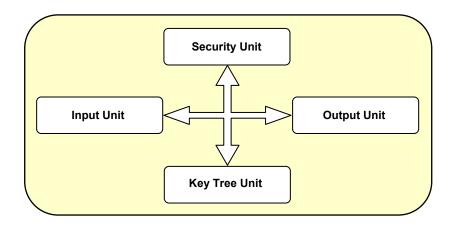

|   |       | General Architecture                           |    |

|   |       | Key Tree Management                            |    |

|   | 5.5.1 | •                                              |    |

|   | 5.5.2 |                                                |    |

|   | 5.5.3 | •                                              |    |

|   | 5.5.4 |                                                |    |

|   |       | Hardware Security Modules                      |    |

|   | 5.6.1 | Encryption Module                              |    |

|   | 5.6.2 | **                                             |    |

|   | 5.6.3 | Hash Module                                    |    |

|   | 5.6.4 | MAC Module                                     |    |

|   | 5.6.5 | Digital Signature Module                       |    |

|   |       | Input/Output Units                             |    |

|   |       |                                                | 83 |

|   | 5.7.2 | Rekeying Message Format                        |    |

| 6 |       | Time and Batch Rekeying Processors             |    |

| Ŭ |       | Overview                                       |    |

|   |       | Real-Time Rekeying Processor (RTRP)            |    |

|   | 6.2.1 | Architecture                                   |    |

|   | 6.2.2 | Instruction Set and Rekeying Algorithms        |    |

|   | 6.2.3 | Implementation and Results                     |    |

|   |       | Batch Rekeying Processor (BRP)                 |    |

|   | 6.3.1 | Architecture                                   |    |

|   | 6.3.2 | Instruction Set and Rekeying Algorithms        |    |

|   | 6.3.3 | Pipelined Batch Rekeying                       |    |

|   | 634   | Implementation and Results                     |    |

| 7  | High      | -Flexibility Rekeying Processor          | 103 |

|----|-----------|------------------------------------------|-----|

|    | 7.1       | Overview                                 |     |

|    | 7.2       | Introduction                             | 103 |

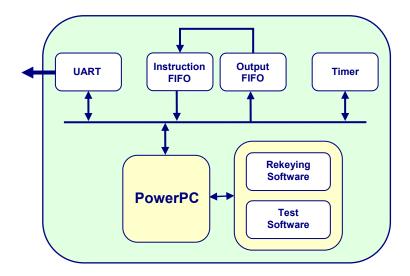

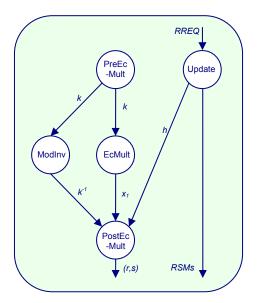

|    | 7.3       | HiFlexRP Architecture                    | 104 |

|    | 7.4       | Rekeying Algorithms                      | 106 |

|    | 7.4.1     | Tree Data Structure                      | 106 |

|    | 7.4.2     | Join Algorithm                           | 108 |

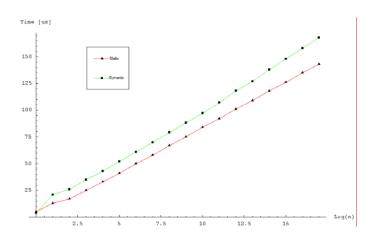

|    | 7.5       | Design Approach and Performance Features | 113 |

|    | 7.5.1     | HiFlexRP Test Environment                | 114 |

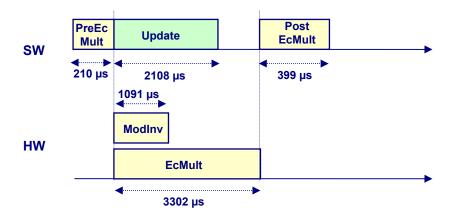

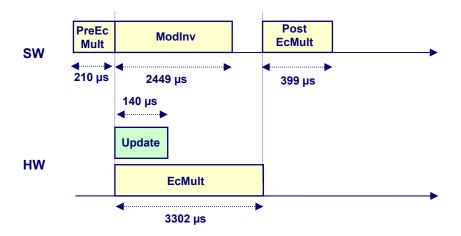

|    | 7.5.2     | Update Subtask Design Alternatives       | 115 |

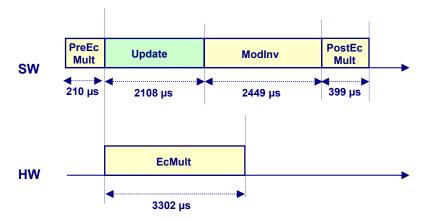

|    | 7.5.3     | Sign Subtask and HW/SW Partitioning      | 119 |

|    | 7.6       | HiFlexRP vs. Related Work                | 123 |

| 8  | Conc      | elusion                                  | 125 |

| Bi | bliograp  | hy                                       | 127 |

| Li | st of Pul | olications                               | 135 |

| Li | st of Su  | pervised Theses                          | 137 |

# 1 Introduction

#### 1.1 Overview

This chapter introduces to the scope of the presented dissertation, specifies its objectives, and outlines it. Section 1.2 illustrates some basics of IP multicast and its advantages. Section 1.3 briefly highlights the role of security in information systems and explains cryptographic methods as essential security means. Section 1.4 represents the problems resulting from applying security models of unicast communication to IP multicast. An essential issue relates to the group key management which is detailed as well in this section with an overview of related work. Section 1.5 lastly depicts the three main objectives of this work and outlines the methods and solutions to attain these objectives. The structure of the dissertation is provided in this concluding section, too.

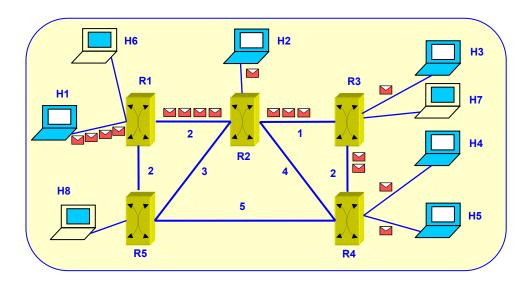

#### 1.2 IP Multicast

Various Internet applications rely on group communication in either one-to-many or in many-to-many mode. One way to support this communication relates to sending data packets from the sender to all receivers using the well-known unicast technique. However, this approach does not scale and results in overloading both the sender resources and the network. **Figure 1.1** represents an example for this communication mode, where the hosts H1 to H5 build a group and H1 is trying to deliver a data packet to other group members. As can be seen, the data packet is duplicated 17 times before it arrives the destination hosts. Note that the packets are transferred over the shortest path to destinations. This is achieved by the different network routers (R) which execute a routing algorithm based on the line cost values depicted in this figure. Some solutions hand over the task of data duplication from the sender host to a dedicated server, which is denoted as multipoint control unit (MCU) in the scope of video conferencing. By this means the sender resources are relieved but the network traffic does not ease as data packets are still transmitted in multiple copies.

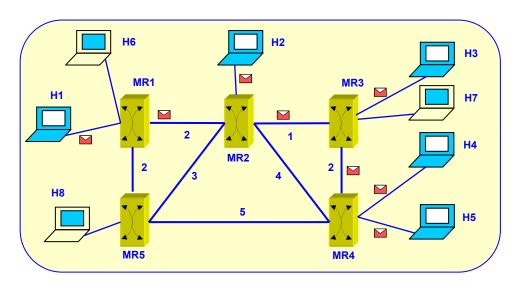

A scalable group communication demands the dissemination of just one copy of the data packet over the network. IP Multicast represents a technique that fulfills this requirement as depicted in **Figure 1.2**. Based on its special address class a multicast data packet is recognized by multicast routers (MR), which duplicate this packet as necessary. Multicast IP-addresses belong to class-D, which assigns 28 bits (from a total of 32 bits) to identify different groups. Thus, IP multicast can support up to 250 million different groups. When

1.2 IP MULTICAST 2

investigating this routing technology, two questions arise. Firstly, how do multicast routers learn the hosts belonging to some group? This question results from the fact that class-D addresses do not contain a field, which specifies the subnet to which a host belongs, as it is the case in other IP-address classes for unicast communication. Secondly, how does routing perform? These two questions are first answered in the next section briefly. Afterwards, some application scenarios of IP multicast are described and the associated difficulties in employing this communication technology are outlined.

Figure 1.1. Example for unicast-based group communication

#### 1.2.1 IP Multicast Protocols

For an efficient multicast routing each router must be kept informed about all the running multicast groups and about the belonging of other multicast routers to these groups. A multicast router is said to belong to some multicast group, if it has at least one host in its local network, which is a member of this group. This information is saved in form of a *multicast address table* (MAT). In the example shown in **Figure 1.2** the multicast routers MR1 to MR5 manage the MAT depicted in **Table 1.1**. In this example hosts H1 to H5 and H6 to H8 build two multicast groups, which are called A and B, respectively. The first entry in this table, for instance, indicates that the router MR1 has one or more hosts in its subnet, which are members in the multicast groups A and B. Remember that a multicast group is identified by its IP address. The establishment of the MAT is supported by two multicast protocols:

- 1. The *Internet group management protocol* (IGMP) which is executed between each multicast router and the hosts in its local network to check which of these hosts belong to which multicast group.

- 2. A routing protocol, e.g. the *distance vector multicast routing protocol* (DVMRP), which enables multicast routers to exchange data obtained from executing the IGMP

protocol, so that all routers have the up-to-date MAT. Note that a routing protocol is originally used to route useful data from a sender to all group members.

Besides the MAT, each multicast router manages a *routing table* (RT). In the DVMRP protocol, for instance, these tables contain information on the distance (D) to each other router and how to reach it. **Table 1.2** depicts the RTs for the example of **Figure 1.2**. The left-most table relates to MR1 and states, for instance, that the shortest path from MR1 to MR4 has a distance of 5 and that this router can be accessed through MR2.

Figure 1.2. Example for multicast-based group communication

Both the IGMP and the DVMRP belong to the IP layer of the Internet layer model and were first defined as RFC (request for comment) in the late eighties. Current specifications of these protocols can be found as Internet Drafts in [Ca97] and [Pu98], respectively.

| <b>Table 1.1.</b> MAT | for the | example | of <b>Figure 1.2</b> |

|-----------------------|---------|---------|----------------------|

|                       |         |         |                      |

| Multicast Router | Multicast address |

|------------------|-------------------|

| MR1              | A, B              |

| MR2              | Α                 |

| MR3              | A, B              |

| MR4              | Α                 |

| MR5              | В                 |

1.2 IP MULTICAST 4

| MR1 |    |   | N  | IR2 |   | N  | IR3 | R3 I |  |    | MR4 |   |  | MR5 |    |   |

|-----|----|---|----|-----|---|----|-----|------|--|----|-----|---|--|-----|----|---|

| MR  | MR | D | MR | MR  | D | MR | MR  | D    |  | MR | MR  | D |  | MR  | MR | D |

| 1   | 1  | 0 | 1  | 1   | 2 | 1  | 2   | 3    |  | 1  | 3   | 5 |  | 1   | 1  | 2 |

| 2   | 2  | 2 | 2  | 2   | 0 | 2  | 2   | 1    |  | 2  | 3   | 3 |  | 2   | 2  | 3 |

| 3   | 2  | 3 | 3  | 3   | 1 | 3  | 3   | 0    |  | 3  | 3   | 2 |  | 3   | 2  | 4 |

| 4   | 2  | 5 | 4  | 3   | 3 | 4  | 4   | 2    |  | 4  | 4   | 0 |  | 4   | 4  | 5 |

| 5   | 5  | 2 | 5  | 5   | 3 | 5  | 2   | 4    |  | 5  | 5   | 5 |  | 5   | 5  | 0 |

**Table 1.2.** Routing tables for the example of **Figure 1.2**

#### 1.2.2 IP Multicast Applications

The transport control protocol TCP of the transport layer supports only point-to-point services. Therefore, multicast applications must utilize the user datagram protocol UDP, which offers unreliable connectionless services on the transport layer. However, this does not restrict multicast to error-tolerant applications such as multimedia streaming. Reliable multicast applications can be supported, for example, by adding a special layer between the application and the transport layers, which emulates the TCP. Accordingly, multicast applications can be classified into four categories [Mi99]:

- 1. **Real-time multimedia applications,** e.g. video conferencing, internet radio, and multimedia events. These applications are error-tolerant but demand low timing jitter characteristics for correct synchronization.

- 2. **Real-time data applications,** such as the distribution of stock quotes and interactive gaming. The requirements of scalability and reliability for these applications differ depending on the particular data. Text news, for instance, must be delivered error-free to very large groups as a rule. Some latency in the transmission of these data, however, can be tolerated.

- 3. **Non real-time multimedia applications,** e.g. remote class rooms with high reliability but low or moderate scalability requirements.

- 4. **Non real-time data applications,** such as database replication and software distribution, with both high reliability and high scalability demands.

Despite its scalability and usability in a vast number of current and new Internet applications, IP multicast technology is not yet exploited to large extent. Several economic and technical reasons are responsible regarding both private and public networks. Some examples for the deployment barriers of IP multicast in private networks relate to the limited application software and administration tools supporting this technology. One essential obstacle in the usage of this communication technique over the public Internet is attributed to the fact that not all current IP routers are multicast-able.

For further reading on networking and IP multicast the following publications are recommended [Ha01], [Ta00], [Mi99], and [Go99].

#### 1.3 Information Security

#### 1.3.1 Threats, Requirements, and Solutions

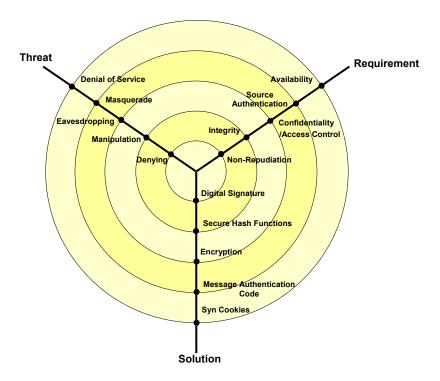

An information system is regarded as secure if it ensures the delivery of the right information to the right party at the right time. The meaning of the terms *right information*, *right party*, and *right time* in the context of security is illustrated as follows. To ensure the delivery of right information, the representing data must be able to be checked on their integrity and their source. *Data integrity* means that no manipulation has been performed on these data en route. *Data source authentication* guarantees that data stem from the source claiming or denying to be the sender. The protection against denying is known as *non-repudiation* property of a secure system. Supplying information to the right party implicates the hiding of this information against unauthorized parties which requires applying mechanisms for *data confidentiality*. Providing data with integrity, authentication, and confidentiality is only reasonable if these data are available at the right time. *Data availability* is regarded as security goal, since several attack schemes aim this property.

Figure 1.3. Visualization of security requirements, threats, and solutions

The decision on required security objectives for an information system and on the measures to attain these goals is a largely sophisticated task, which is defined as a *security policy* for that system. The specification of a security policy relies on an in-depth analysis of the criticality of the information to be exchanged, the data delivery system, and the threats it is exposed to. Receivers of Pay-TV data, for instance, do not need to verify that video

contents originate from the Pay-TV provider, as a rule. Thus, data source authentication is not a requirement in this case. In contrast, for a commercial site it is indispensable to verify the client identity before executing its order. Only by applying a non-repudiation strategy a possible denying can be disproved. Inspired by the graphical representation of Gajski's diagram [Ga92], the relation between security requirements, well-known threats, and possible countermeasures can be depicted schematically by means of a Y-Diagram as illustrated in **Figure 1.3**. The hierarchical representation reflects to large extent the dependency of the different security requirements. In this respect, data availability is an essential aspect, which all other requirements are based upon. The non-repudiation property, however, assumes data availability, authentication, and integrity. In some cases, furthermore, non-repudiation largely relies on data confidentiality.

#### 1.3.2 Cryptography

Regardless of solutions to the availability requirement, all other countermeasures on the solution axis of Figure 1.3 rely on cryptographic operations. Cryptography is defined in [Me96] as the study of mathematical techniques related to aspects of information security such as confidentiality, data integrity, entity authentication, and data origin authentication. The mathematical techniques are applied to data representing the information to be protected from eavesdropping, manipulation, etc. All cryptographic methods rely on using some information denoted as key. The way how to exchange and manage this key represents the most important criterion to classify cryptographic algorithms. According to this criterion two main categories are present: the symmetric-key and the public-key cryptography. In symmetric-key cryptography both communication parties use the same key, denoted as symmetric key, to apply cryptographic operations to encipher or decipher data. Cryptographic enciphering and deciphering are referred to as encryption and decryption, respectively. The Data Encryption Standard (DES) [Ni81] and the Advanced Encryption Standard (AES) [Ni01] are the most known examples for this cryptography class. Besides encryption and decryption for the purpose of confidentiality, symmetric-key cryptography may be employed to realize secure hash functions and message authentication code, which support data integrity and source authentication, respectively, see Figure 1.3. For the functionality of symmetric-key cryptography, however, a secret key must be agreed and delivered over a secure channel. This hard requirement is avoided by the public-key cryptography, which exploits two different keys for encryption and decryption. These keys are denoted as the *public* and the *private key*. For a communication party A to send an encrypted message to another party B, it uses the public-key of B. Getting the encrypted message, B can decrypt it with its private key. The idea of public-key cryptography was first published in [Di76]. RSA [Ri78], ElGamal [El85], and Elliptic Curve Cryptography (ECC) [Ko87, Mi86] represent the most known public-key cryptosystems. As the mathematically inverse function of encryption, decryption is based on a relation between the private and public keys. The security of public-key cryptography is based on the fact that this relation is so complex that an extraction of the private key from the public one is impossible during defensible time. This is realized by using complex mathematical problems to generate key pairs such as the factorization of large prime numbers, e.g. in the case of RSA, or the determination of the discrete logarithm, e.g. in the cases of ElGamal and ECC. The security of public-key cryptography does not only rely on the complex relation between the private and the public key, but also on complicating the encryption and decryption processes themselves. This fact negatively affects the performance of these algorithms and makes them unsuitable to encrypt large data under hard timing constraints. In practice, therefore, public-key cryptography is mainly used to process small amounts of data such as in the following two cases. First, public-key encryption can be used to agree on a symmetric key which can then be employed for secure communication based on symmetric-key encryption. The second application relates to the digitally signing of short data. In this case a sender uses its private key to sign a message and the receiver access the public key of the sender to verify that the message stems from this sender. Digital signing is a measure to ensure non-repudiation as depicted in **Figure 1.3**. Note that public-key cryptography depends on the availability of authentic public keys. The resources, policies, protocols, and procedures demanded to create, distribute, manage, and revoke public keys construct a framework denoted as *public-key infrastructure* (PKI). The task of distributing certified keys in PKI is assigned to an entity which is trusted by every one and referred to as *certification authority*. Consequently, *key management* represents an essential issue in both symmetric-key and public-key cryptography.

In the scope of this work several cryptographic algorithms are utilized. These include the Advance Encryption Standard (AES) as a symmetric-key encryption primitive, the secure Meyer hash function [Ma85], and the Message Authentication Code MAC [Is89]. Both the Meyer hash function and MAC are based on symmetric-key encryption. In addition, for generating secure keys, an algorithm specified in ANSI X9.17 is exploited, which also relies on symmetric-key cipher. For building digital signatures the Elliptic Curve Digital Signature Algorithm (ECDSA) [Ie00] is employed. All these algorithms are briefly described in Chapter 5 with focus on their hardware realization. For further reading on these topics it is referred to the related literature and to text books on security and cryptography, e.g. [Da01], [Ec06], [Me96], and [Sc96].

#### 1.4 Secure Multicast

Various multicast applications demand data delivery under security conditions such as confidentiality, integrity, and data source authentication. A collaborative group of company employees, for instance, may use Internet conferencing to exchange information and need to keep their communication secret. Another example from the multimedia streaming field relates to a multicast Pay-TV scenario, where the access should only be granted to those members, who already have paid the charge. Applying security strategies to multicast communication poses special problems, which are unfamiliar in the one-to-one communication mode. These special issues are attributed to the following properties:

- 1. Secure communication is based on sharing a secret, i.e. a key, between communicating parties. The more parties learn the secret, the higher the risk to disclose it.

- In general, multicast groups are large-scale and characterized by highly dynamic membership. To restrict access to authorized members, the group communication key must be changed after every change in the group membership. This increases the complexity of key management.

- 3. Based on the fact that symmetric key in one-to-one communication is shared by only two partners, data source authentication can be easily verified by encrypting these data

- with the shared symmetric key. Unfortunately, this so-called message authentication code (MAC) can not be employed in secure multicast, since the secret key is shared by a large number of members.

- 4. As mentioned previously, to communicate securely, a security policy must be defined and negotiated between communication parties. Such an agreement in multicast mode is much more sophisticated than in the unicast case, because a security policy must be found which satisfies the requirements of many parties, instead of just two.

#### 1.4.1 Secure Multicast Problem Areas

These and other difficulties in applying security issues to IP multicast have been recognized by research and industry institutions and resulted in establishing the research group *Secure Multicast Group* (SMuG) within the *Internet Research Task Force* (IRTF) in early 1998 [Sm98] and the working group *Multicast Security* (MSEC) within the *Internet Engineering Task Force* (IETF) in early 2000 [Ms00]. A main contribution of SMuG and MSEC relates to identifying the following three problem areas in secure multicast [Ha03]:

- 1. Secure multicast data handling: In this problem area secure data transmission including data confidentiality, integrity, and source authentication is treated. Investigating the adaptability of available security protocols to secure multicast presents an essential issue in this problem area. One example relates to the Multicast Encapsulating Secure Payload (MESP) as an extension to the known ESP protocol in IP security [Ca00]. Furthermore, in the scope of this area the concept of group authentication [Ca99] is introduced as a simple form of data source authentication. Some groups are trustful and only need to protect themselves against non-member parties. In this case, group authentication can be employed, which relies on simple symmetric-key cryptography. In contrast, if group members do not trust each other, an exact data source authentication must be used. This kind of authentication in multicast can not be performed on the base of symmetric-key cryptography as in the unicast case. Instead, solutions based on public-key cryptography such as digital signatures must be employed.

- 2. Management of keying material: This problem area concerns the generation and distribution of the group communication key. This process is performed both during registration in static groups and after every membership change in dynamic groups. The generation and distribution of a new communication key as an effect of joining new members or removing old ones in dynamic multicast groups is denoted as Group Rekeying. This process represents the focus of this dissertation and will be detailed in next section.

- 3. *Multicast security policies:* In secure multicast different members may have different capabilities and responsibilities. One task of the security policy is to define the roles of group members, e.g., as a sender, a receiver, or as a *group controller and key server* (GCKS). Besides, the security policy specifies, for instance, which encryption algorithm should be used for data confidentiality. As policy negotiation among large groups is in practice impossible, a mechanism for policy enforcement by the GCKS must be employed [Di00].

#### 1.4.2 Group Rekeying

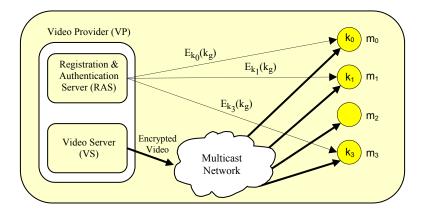

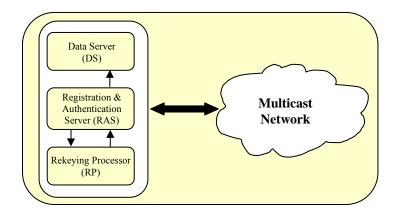

Consider the multicast Pay-TV system illustrated in Figure 1.4. A video server (VS) encrypts video packets with a group key  $k_g$  and sends them using IP-multicast. Members  $m_0$ ,  $m_1$ , and  $m_3$  aim to buy the service. For this purpose, they connect to a registration and authentication server (RAS), pay the charge, and get each an individual identity key  $k_0$ ,  $k_1$ , and  $k_3$ . In a following step the RAS encrypts the group key  $k_g$  with each of the identity keys and sends it to the corresponding member per unicast. The notation  $E_{k_d}(k_b)$  in **Figure 1.4** refers to the encryption of key  $k_b$  with key  $k_a$ . Each authorized member accordingly receives the encrypted  $k_g$ , decrypts it with its identity key and gets thereby the group key  $k_g$ . Members  $m_0$ ,  $m_1$ , and  $m_3$  in this scenario can now use  $k_g$  to decipher the encrypted video data and watch the movie. Member  $m_2$ , however, is excluded: he or she can download encrypted movies, but cannot enjoy them. Note that referring to  $m_2$  as a group member relates to the multicast group, not to the secure multicast group. As mentioned before, joining a multicast group is loose and is performed between a host and the multicast router in the corresponding network based on the Internet Group Management Protocol (IGMP). The video provider in this scenario does not know who is currently a group member, therefore, it uses encryption to control access. The way how the registration works and the identity keys are distributed is not in the focus of this work. It is assumed that the task of generation and distribution of identity keys is covered by the RAS.

Figure 1.4. Pay-TV: Potential scenario for secure multicast

#### 1.4.2.1 Scalability Problem

If  $m_2$  decides to buy the service later on, then this member registers at the RAS and gets its own identity key  $k_2$ . To keep *backward access control*, i.e., to prevent  $m_2$  from decrypting old videos, the RAS generates a new group key  $k_g^{new}$ , encrypts it with the current group key  $k_g$ , and multicasts it. By this means  $k_g^{new}$  becomes available to all current members of the group. In addition, the RAS encrypts  $k_g^{new}$  with  $k_2$  and sends it to  $m_2$  per unicast. Consequently, joining a new member in this scheme causes two encryptions on the server side, which is fairly acceptable. In contrast, the process of disjoining a member is highly inefficient. Assume for example that  $m_1$  has to leave the group, because his or her

subscription period ended. To keep *forward access control*, i.e., to prevent  $m_1$  from decrypting future video material, the RAS again has to generate a new group key, but this must NOT be encrypted with the current group key like in the join case. Instead, the RAS encrypts the new group key with each of the identity keys of the remaining members, i.e. with  $k_0$ ,  $k_2$ , and  $k_3$ . Thereafter every remaining member gets the  $k_g^{new}$  encrypted with its identity key. In other words, disjoining a member from a group having n participants costs a total of n-l encryptions on the server side.

Assuming that there are as much join as disjoin requests, then the average cost of a join/disjoin operation is nearly equal to n/2. Obviously, this scheme is not scalable for large groups. In the sequel this rekeying scheme is denoted as *simple rekeying*.

#### 1.4.2.2 Related Work on Group Rekeying

Several solutions have been proposed in literature to cope with the scalability problem in multicast group rekeying. In the Iolus scheme [Mi97] the group is divided into several subgroups. Each subgroup is controlled by a trusted third-party proxy, whereas these proxies are controlled by the group owner. The rekeying within a subgroup occurs as in the simple scheme, which means that Iolus approach becomes unscalable for large subgroups, apart from the drawback of the need of trusted third-party agents. Similar decentralized rekeying schemes are presented in [Do00] and [Bi00]. MARKS [Br99] is a mechanism for efficient key distribution. In this mechanism the group controller knows each member's disjoin time and performs rekeying at fixed time instances, which restricts system dynamics. The Logical Key Hierarchy scheme (LKH) proposed in [Ha99] and [Wo00] allows an efficient rekeying for large groups without a-priori knowledge of group joins or leaves. Many improvements for LKH were proposed to enhance performance. Originally, LKH performs rekeying in real-time mode, i.e. rekeying is executed immediately for each join or disjoin request. One performance improvement relies on processing rekeying requests in batch. In this mode several requests are summed up during a rekeying interval and then processed simultaneously, see, e.g., [Li01], [Ji02], and [Ma04]. Other improvements to LKH deal with tree rebalancing to keep a logarithmic relationship between rekeying costs and group size, see, e.g., [Mo99], [Ra01], [Go04]. Because of its relevance for this work, the next section is dedicated to illustrating the LKH rekeying approach. Another rekeying scheme relies on One-way Function Trees (OFT). This scheme reduces the communication overhead for disjoin rekeying at the expense of additional computations on both the server and the member side [Ba00], [Sh03]. Recently, the interest in group key management exceeded the scope of typical IP multicast. Thus, several solutions for group key management are proposed for Ad-Hoc networks [Se04], [Li06], mobile multicast [Ro06], satellite multicast [Ho04], and wireless cellular networks [Um06].

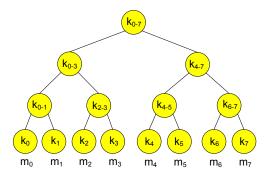

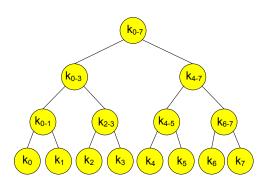

#### 1.4.2.3 Logical Key Hierarchy

The basic idea behind the LKH is to divide the group into hierarchical subgroups and to provide the members of each subgroup with a shared key, which is called the *help-key*. Consider the example illustrated in **Figure 1.5** for an eight-member group. In this model members  $m_0$  and  $m_1$  build a subgroup with the help-key  $k_{0-1}$ , members  $m_0$ ,  $m_1$ ,  $m_2$ , and  $m_3$  build a larger subgroup, whose help-key is  $k_{0-3}$ . All members compose the largest subgroup

with the help-key  $k_{0-7}$ . This key represents the group key which is used to encrypt useful data. Consequently, a member now holds several instead of just two keys. These keys are the identity key  $k_d$ , which is known only to this member and to the server, the group key  $k_g$  known to all group members, and some help-keys  $k_{x-y}$  corresponding to the subgroups, which the member belongs to. Member  $m_6$ , for example, has  $k_d = k_6$ ,  $k_g = k_{0-7}$  and two help-keys, which are  $k_{6-7}$  and  $k_{4-7}$ .

**Figure 1.5.** LKH example

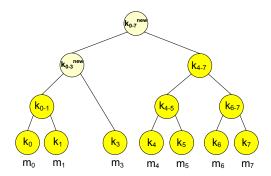

#### Disjoin Rekeying

Assume that the member  $m_2$  wants to leave the group. How many encryptions have to be computed by the server to rekey the group?

Except for the identity key all the keys held by  $m_2$  (i.e.  $k_{2-3}$ ,  $k_{0-3}$  and  $k_{0-7}$ ) have to be changed. After removing  $m_2$ , however, the help-key  $k_{2-3}$  can be destroyed, as this key is only known by one member, i.e.  $m_3$ . Therefore, only two keys,  $k_{0-3}$  and  $k_{0-7}$  are generated, encrypted, and sent to the remaining members needing these keys. **Figure 1.6** represents the key tree after this processing:

Figure 1.6. LKH example after disjoining m<sub>2</sub>

Using the notation  $E_{k_a}(k_b)$  to refer to a *rekeying submessage* representing the encryption of the key  $k_b$  with the key  $k_a$ , the server has to generate the following rekeying submessages in order to disjoin  $m_2$ :

$$E_{k_{3}}(k_{0-3}^{new}), E_{k_{0-1}}(k_{0-3}^{new}), E_{k_{0-3}^{new}}(k_{0-7}^{new}), E_{k_{4-7}^{new}}(k_{0-7}^{new})$$

A *Rekeying Message* is composed of all rekeying submessages and other related information, e.g., the *rekeying submessage identification* illustrated later on in this work.

The server has to compute just 4 encryptions to rekey the group. In contrast, in the simple scheme a total of 7 encryptions would be necessary. The gain of LKH becomes more obvious in the case of large group sizes. **Table 1.3** details this comparison.

#### Join Rekeying

Assume now that another member will be joined at the tree position of  $m_2$ . The new member will be called  $m_2$ , too. How many encryptions have to be performed by the server to rekey the group?

All keys from the join point of  $m_2$  to the root ( $k_g$ ) have to be updated and encrypted. The following rekeying submessages are constructed:

$$E_{k_{3}}(k_{2-3}^{new})$$

,  $E_{k_{2}}(k_{2-3}^{new})$ ,  $E_{k_{0-1}}(k_{0-3}^{new})$ ,  $E_{k_{2-3}}^{new}(k_{0-3}^{new})$ ,  $E_{k_{0-3}}^{new}(k_{0-7}^{new})$ ,  $E_{k_{4-7}}(k_{0-7}^{new})$

In contrast to the simple scheme, where just two encryptions would be needed for join rekeying, the LKH requires more encryptions. Nevertheless, considering both join and disjoin processes, the LKH is clearly superior to the simple scheme, as visible from **Table 1.3**. While the average encryption costs increase linearly with *n* in the simple scheme, LKH unveils a logarithmic dependence.

|               | # Encryptions |                           |  |  |  |  |

|---------------|---------------|---------------------------|--|--|--|--|

|               | Simple scheme | LKH                       |  |  |  |  |

| Join          | 2             | 2*log <sub>2</sub> n      |  |  |  |  |

| Disjoin       | n-1           | 2*(log <sub>2</sub> n -1) |  |  |  |  |

| Average value | O(n)          | $O(log_2n)$               |  |  |  |  |

Table 1.3. LKH vs. simple rekeying scheme

# 1.5 Work Objectives and Outline

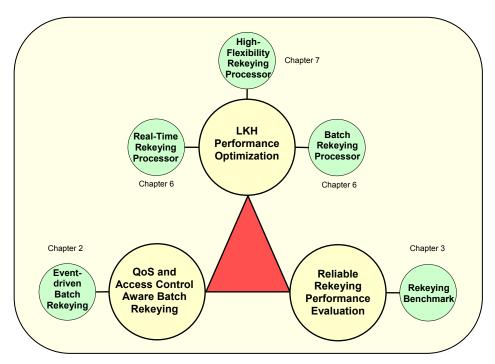

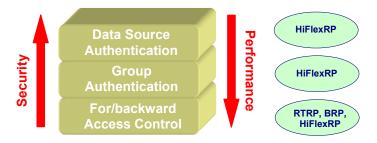

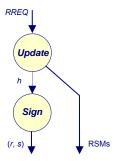

This dissertation makes three main contributions to multicast group rekeying. Thus, solutions, algorithms, and architectures presented in this work can mainly be assigned to the second problem area in secure multicast, see Section 1.4.1. As rekeying results in multicasting rekeying messages, which must be authenticated to prevent manipulation, this work deals also with corresponding authentication issues which belong to the first problem area. **Figure 1.7** illustrates schematically the three objectives followed in this work as big bubbles surrounded by related solutions. This figure can be used as a reference in this dissertation.

QoS and Access Control Aware Batch Rekeying: As mentioned previously, batch rekeying aims at optimizing the rekeying performance by processing several requests at the same time. By this means some key generations and encryptions are saved. Refer to the discussed disjoin and join requests in the example of last section and to Figure 1.5 and **Figure 1.6**. Note that the separate handling of these requests required the generation of 5 new keys and the execution of 10 encryptions, in total. In contrast, if these two requests are processed simultaneously, then only 3 generations and 6 encryptions will be needed. This batch rekeying mode, however, demands that former requests have to wait on later ones. Consequently, new members must wait longer to be granted access, and members who must be removed keep access for longer time periods. Related work on batch rekeying assumes a fixed rekeying interval or defines a lower bound for this parameter. In this work an upper bound is introduced, which assures that the quality of service for joining members and the access control against leaving ones always remains within system specific limits. Besides the necessary metrics for this solution, an algorithm, denoted as *Event-driven Batch Rekeying*, is presented which considers this issue. Two simulation case studies illustrate the significance of the proposed method. Chapter 2 is dedicated to this work objective.

Figure 1.7. Work objectives and solution structure

2. **Reliable Rekeying Performance Evaluation:** The reader of related work on group rekeying misses up to now a way to compare proposed solutions to each other. This comparison is impeded by a wide spectrum of non-unified performance metrics and by largely different ways to estimate these metrics in literature. For a reliable rekeying performance evaluation this work presents a novel *Rekeying Benchmark* as a unified way for estimating unified metrics expressing rekeying performance. The reliable evaluation origins from defining new metrics to estimate performance, which are system-specific and independent of both rekeying algorithms and the underlying cryptographic operations and execution platforms. The rekeying benchmark is the subject of Chapter 3.

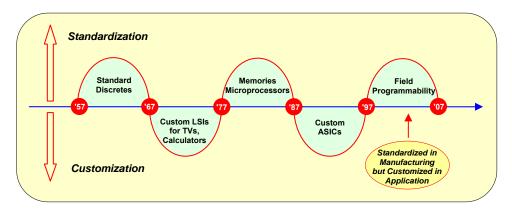

3. **LKH Performance Optimization:** All previous work on optimizing the performance of rekeying algorithms concentrates on reducing the number of time-consuming operations, which are needed to perform rekeying such as the number of key generations or the number of encryptions. In this work novel architectures are proposed, which optimize rekeying performance on a lower level. By means of hardware acceleration, not only the amount of cryptographic operations is reduced, but also the execution time of these operations. In the course of this work two hardwareonly processors and one hardware/software processor were designed and implemented on reconfigurable platforms. These are the Real-Time Rekeying Processor (RTRP), the Batch Rekeying Processor (BRP), and the High Flexibility Rekeying Processor (HiFlexRP). Each of these architectures may be used as a coprocessor in the server environment of a multicast group owner, e.g. as a coprocessor for the registration and authentication server to accelerate rekeying in the Pay-TV scenario presented in Figure 1.4. Because of several similarities between the rekeying processors and to avoid repeating similar facts Chapter 4 highlights the employed implementation platforms and Chapter 5 describes the common features of these architectures. Chapter 6 then details both the RTRP and the BRP. Chapter 7 is devoted to the HiFlexRP.

#### Remarks and notation:

This work treats the key management problem in secure multicast with an emphasis on the server side. As for the network, only the dynamic group behavior is investigated which is reflected by member join and leave rates. Neither communication overhead nor protocol issues are considered. The dissertation can be read either in the order of its chapters or in a different way taking the following points into account. Chapter 3 is completely independent. Chapter 4 represents an introduction to reconfigurable architectures and some commercial devices and tools. Therefore, this chapter may be skipped by experts in this field. Chapter 6 and Chapter 7 depend strongly on Chapter 5, but are themselves independent of each other. Furthermore, Chapter 6 is slightly based on some points presented in Chapter 2.

As a quick reference, **Table 1.4** summarizes some important terms, which were presented in this chapter and will be used frequently in next chapters.

| Term                        | Meaning                                                                                           |

|-----------------------------|---------------------------------------------------------------------------------------------------|

| Identity key k <sub>d</sub> | A key which is known to the server and one member $m_d$                                           |

| Group key k <sub>g</sub>    | A key which is known to the server and to all group members. $k_g$ is used to encrypt useful data |

| Help-key k <sub>x-y</sub>   | A key shared between the server and some group members. $k_g$ is regarded as a special help-key   |

| Rekeying Submessage (RSM)   | An encrypted key $k_b$ with a key $k_a$ : $E_{k_a}(k_b)$                                          |

| Rekeying Message (RM)       | The set of all RSMs and some auxiliary data                                                       |

Table 1.4. Notation

# 2 QoS and Access Control Aware Batch Rekeying

#### 2.1 Overview

This chapter represents a solution to the batch rekeying problem resulting from long rekeying intervals. Section 2.2 describes the batch rekeying and compares it with the real time rekeying based on the LKH algorithm. The problems of batch rekeying are then presented and specified by new metrics in Section 2.3. Section 2.4 uses these metrics to provide different methods for optimizing batch rekeying. Section 2.5 represents two case studies and Section 2.6 concludes the chapter with some design hints for batch rekeying solutions.

# 2.2 Batch Rekeying

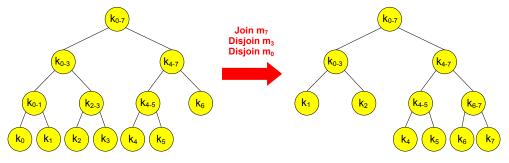

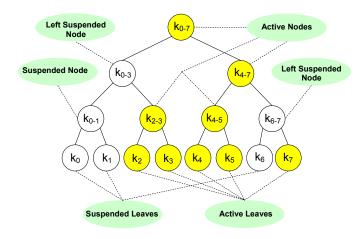

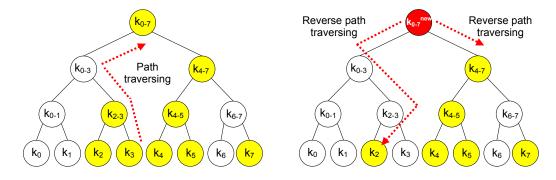

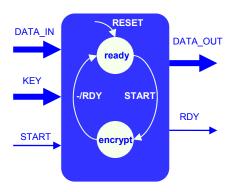

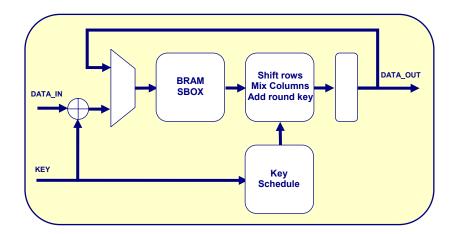

Group rekeying based on the algorithm of logical key hierarchy LKH presented in Section 1.4 features a real time characteristic. According to this algorithm each rekeying request is granted separately. However, a performance improvement can be achieved, if several requests are processed simultaneously. This processing mode is denoted as batch rekeying [Li01]. Different rekeying requests demand an update of several keys. Some of these keys, however, are likely to be processed several times if these requests are treated separately. The performance gain in batch rekeying relies on avoiding this multiple processing by reducing the number of updates of some key to one, maximally. To illustrate this point consider the left key tree in **Figure 2.1** and assume that the rekeying server receives three rekeying requests in the following order: *join m\_7, disjoin m\_3*, and *disjoin m\_0*. The right key tree in **Figure 2.1** represents the state after performing rekeying for these three requests.

Figure 2.1. Batch rekeying example

**Table 2.1** summarizes how often each of the help-keys is processed in both real-time and batch rekeying. Processing a key in this context means an update of this key and two following encryptions of it with the left and the right son keys. From this table it is obvious that processing rekeying requests in batch is more efficient than real-time rekeying.

|                    | k <sub>0-1</sub> | k <sub>2-3</sub> | k <sub>4-5</sub> | k <sub>6-7</sub> | k <sub>0-3</sub> | k <sub>4-7</sub> | k <sub>0-7</sub> |

|--------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| Real-time rekeying | 0                | 0                | 0                | 1                | 2                | 1                | 3                |

| Batch rekeying     | 0                | 0                | 0                | 1                | 1                | 1                | 1                |

Table 2.1. Batch vs. real-time rekeying for the previous example

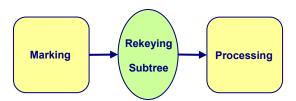

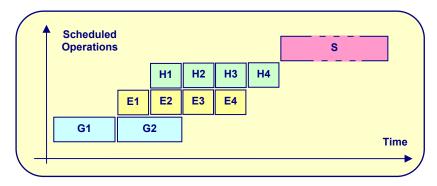

Batch rekeying proceeds in two phases which are repeated frequently. **Figure 2.2** depicts this point:

- 1. *Marking:* In this phase rekeying requests are collected and the help-keys, which need to be processed, are marked. The marked keys build a so-called *rekeying subtree*.

- 2. *Processing:* In this phase all keys in the rekeying subtree are regenerated and encrypted by the corresponding keys to build the rekeying message.

Figure 2.2. Batch rekeying

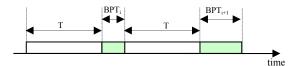

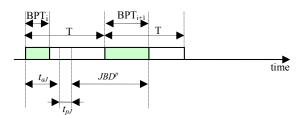

The marking is performed within regular time slots called *rekeying intervals* T. The processing takes differently long according to the built subtree. **Figure 2.3** depicts this situation, where  $BPT_i$  denotes the *batch processing time* of the *i-th* batch.

Figure 2.3. Timing in batch rekeying

# 2.3 Problems of Batch Rekeying

The analysis given in the previous section on batch rekeying performance is optimistic because it does not consider the waiting times of requests before they are served. The longer the rekeying interval the higher the probability for some requests to wait longer. Too long rekeying intervals in batch rekeying have two drawbacks with regard to *Quality of*

Service and Access Control. A new member, on the one hand, gets the group key in batch rekeying later than in real-time rekeying which means that only a worse QoS can be offered by batch rekeying. On the other hand, a leaving member remains to have a valid group key in batch mode for a longer time period than in immediate rekeying which corresponds to degradation in the access control. To quantify these items two new metrics are introduced: these are the Join Batch Delay (JBD) and the Disjoin Batch Delay (DBD).

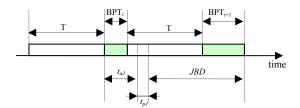

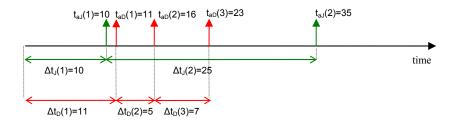

#### 2.3.1 Join Batch Delay

#### Definition 2.1:

Join Batch Delay is defined as the additional waiting time for a joining member to get the group key in batch rekeying compared to the real-time case, see **Figure 2.4.** Within a rekeying interval T a join request appears delayed by  $t_{aJ}$  from the end point of last interval. An immediate processing of this request, i.e., without batching, would take  $t_{pJ}$ . However, through batch processing the corresponding member will be joined at the end of the processing of the (i+1)-th batch. Accordingly, JBD can be estimated using the following formula.

$$JBD = T + BPT_i + BPT_{i+1} - (t_{aJ} + t_{pJ})$$

(2.1)

Figure 2.4. JBD in batch rekeying

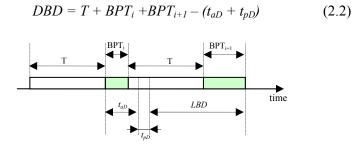

#### 2.3.2 Disjoin Batch Delay

#### Definition 2.2:

Disjoin Batch Delay is defined as the additional time needed to deactivate the help-keys and the group key of a leaving member in batch rekeying compared to the real-time case, see **Figure 2.5.** Similarly to JBD, DBD can be estimated as follows.

Figure 2.5. DBD in batch rekeying

#### *Note 2.1:*

Because of the analogies in the behavior of JBD and DBD, the analysis in next sections is sometimes limited to JBD to avoid repetition.

## 2.4 Optimized Batch Rekeying

As a rule, the processing time of a join request in real-time rekeying  $t_{pJ}$  is short compared to the other terms of equation (2.1) and can therefore be neglected. In addition, considering all joining members in one rekeying interval, the worst-case JBD must be investigated. This case occurs for the earliest join request in the interval, in other words for the join request with the minimal appearance time  $t_{aJ}^{min}$ . The JBD equation, accordingly, can be rewritten as follows.

$$JBD_{worst} = T + BPT_i + BPT_{i+1} - t_{aJ}^{min}$$

(2.3)

In general, optimizing the QoS for joining members is based on minimizing  $JBD_{worst}$  which can be achieved by means of elimination or minimization of the contributing terms in (2.3). These terms are:

T: Rekeying interval

BPT<sub>i</sub>: Batch processing time of the current batch

$BPT_{i+1}$ : Batch processing time of the next batch

#### 2.4.1 Optimized Cryptographic Algorithms and Platforms

The batch processing time BPT in (2.3) is mainly affected by four parameters:

- 1. G: Number of new keys needed for processing the corresponding subtree.

- 2. E: Number of encryptions needed for processing the corresponding subtree.

- 3.  $C_g$ : Cost of the generation of one key in time units (generation cost factor).

- 4.  $C_e$ : Cost of one encryption in time units (encryption cost factor).

Thus, BPT can be estimated as follows.

$$BPT = C_e \cdot E + C_g \cdot G \tag{2.4}$$

The encryption/generation cost factors  $C_e$  and  $C_g$  depend, on the one hand, on the used algorithms for encryption and key generation. On the other hand, they are affected by the performance of the underlying platform. The more efficient the encryption/generation algorithms and the more high-performance the executing platform is, the smaller BPT and therefore the smaller JBD will be. The number of encryptions and generations, E and G, however, is much more complex to estimate because of its dependency on the current state of the key tree and on the following indeterministic factors:

- 1. The number of join/disjoin requests  $N_J/N_D$  in the corresponding rekeying interval, which is a function of the temporal request distribution and of the rekeying interval.

- 2. The logical (spatial) distribution of disjoin requests in the tree. (In contrast, join requests have no indeterministic contribution, because the server decides on the join points in the tree).

In general, both *E* and *G* increase with higher request rates, with higher dispersion of disjoin requests and with higher group sizes. To keep the number of encryptions/generations small, an appropriate rekeying algorithm must be chosen, e.g., LKH [Wo00] or One-way Function Trees [Sh03], etc.

Optimizing the QoS and access control in batch rekeying by means of *BPT* minimizing can be classified as hard QoS/AC management, because it demands essential improvements of algorithms and/or platforms which is expensive and can not be performed in real time, as a rule.

#### 2.4.2 Pipelined Batch Rekeying

In addition to performance enhancements, parallelizing the marking and processing phases of batch rekeying results in a smaller JBD and consequently a higher QoS. During the processing of the i-th batch the (i+1)-th subtree can be generated as depicted in **Figure 2.6**. The suffix p in  $JBD^p$  stays for pipelining. See **Figure 2.4** for a comparison.

Figure 2.6. JBD in pipelined batch rekeying

From this figure it is obvious, that the contribution of  $BPT_i$  to JBD is eliminated.

$$JBD^{p}_{worst} = T + BPT_{i+1} - t_{aJ}^{min}$$

(2.5)

Similarly to *BPT* minimizing, pipelining can be seen as hard QoS/AC management. This strategy, however, optimizes QoS/AC independent of the underlying algorithms for rekeying, encryption and key generation, and without relation to the network situation, which is mirrored by the request rate.

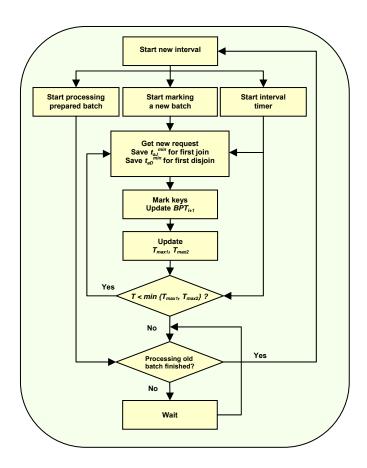

#### 2.4.3 Event-driven Batch Rekeying

Related work on batch rekeying assumes either a constant rekeying interval, e.g. [Li01] and [Zh01], or defines a lower bound on this interval to limit communication overhead, e.g. [Ya01] and [Ji02]. For the purpose of QoS/AC improvement an upper bound on *T* has to be introduced as follows.

$$T < min \{T_{max1}, T_{max2}\}$$

(2.6)

$T_{max1}$  and  $T_{max2}$  correspond to the maximal allowable join and disjoin batch delays in the system specification  $JBD_{max}$  and  $DBD_{max}$ , respectively. Using (2.5)  $T_{max1}$  can be estimated as follows. The pipelining suffix p is neglected, for clarity.

$$T_{max1} = JBD_{max} - BPT_{i+1} + t_{aJ}^{min}$$

(2.7)

Similarly, for  $T_{max2}$  the following can be written.

$$T_{max2} = DBD_{max} - BPT_{i+1} + t_{aD}^{min}$$

(2.8)

Secure multicast applications differ according to their sensitivity to the QoS and access control associated with batch processing. While Pay-TV, for example, emphasizes high QoS values and accepts as a rule some loss of access control, other applications, e.g., in military fields, do not tolerate any sacrifice of these parameters. Furthermore, the demands on QoS and access control can vary from time to time for the same application depending on some scenario-specific parameters. A Pay-TV provider, for example, can tolerate longer values of *DBD* to guarantee the required *JBD* at times of high join rates, e.g., shortly before starting the streaming of a sport event.

Figure 2.7. Pipelined event-driven batch rekeying

The application of (2.6) results in an *event-driven batch rekeying* which is activated by the events of exceeding  $T_{max1}$  and  $T_{max2}$ . These events cause the concluding of the current rekeying interval and the starting of a new one.

**Figure 2.7** illustrates the new batch rekeying algorithm which supports both pipelining and event-driven operation modes to optimize QoS and access control. Note that, because of pipelining, a new interval can only be started if the processing of the old batch is already finished which is true in most cases. As depicted in **Figure 2.7**, event driven rekeying relies on estimating the batch processing time  $BPT_{i+1}$  during marking. This task assumes knowing the encryption and the generation cost factors  $C_e$  and  $C_g$  according to (2.4).

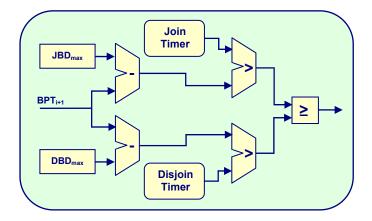

The Batch Rekeying Processor presented in Chapter 6 realizes an event-driven batch rekeying [Sh05]. In this hardware implementation the factors  $C_e$  and  $C_g$  are well defined and a real-time functionality guarantees an accurate estimation of  $BPT_{i+1}$  because of the common time base for all hardware modules. The module Batch Delay Monitor of this processor is integrated to a preprocessing unit which performs the marking to prepare the rekeying subtree.

In contrast to the other optimization strategies, event-driven rekeying provides a real-time control of QoS and access control in each rekeying interval and can, therefore, be classified as soft QoS/AC management which keeps QoS/AC within desirable values during the system operation.

#### 2.5 Case Studies

Though the JBD behaviour given in (2.5) appears to be simple to evaluate, a comprehensive analysis of this quantity is almost impossible. This is particularly because of the highly complex dependencies of the batch processing time. To illustrate this point, this characteristic is represented as a set of functional relationships, where  $N_J$  and  $N_D$  refer to the number of join and disjoin requests summed up in a rekeying interval, respectively.

```

JBD<sup>p</sup><sub>worst</sub> = f<sub>1</sub> (T, BPT<sub>i+1</sub>, t<sub>aJ</sub><sup>min</sup>)

BPT<sub>i+1</sub> = f<sub>2</sub> (C<sub>e</sub>, E, C<sub>g</sub>, G)

C<sub>e</sub>, C<sub>g</sub> = f<sub>3</sub> (encryption/generation algorithms, platform)

E, G = f<sub>4</sub> (N<sub>J</sub>, N<sub>D</sub>, tree state, spatial request distribution in the tree)

N<sub>J</sub>, N<sub>D</sub> = f<sub>5</sub> (T, temporal request distribution)

```

Note that the rekeying interval T affects  $JBD^p_{worst}$  not only directly according to  $f_I$ , but also indirectly corresponding to  $f_5$  depending on the current distribution function of join/disjoin requests.

Almost all the related work on batch rekeying only consider the relation  $f_4$  for E based on borderline cases. A few papers [Ya01, Zh03] investigate the relation  $f_5$  assuming an exponential request distribution. Based on these approaches, a form for the function  $f_1$  is derived, which can be evaluated by means of simulation. For this purpose, borderline conditions are introduced for the different relations  $f_1$ ,  $f_2$ ,  $f_4$ , and  $f_5$  to ease the analysis. The

2.5 CASE STUDIES 22

steps outlined in this derivation can be used as a general guideline for other cases and conditions.

1.  $t_{aJ}^{min} = 0$ , which means that the first join request appears at the beginning of a rekeying interval. Accordingly,  $JBD^{p}_{worst}$  can be written as follows.

$$JBD^{p}_{worst} = T + BPT_{i+1} \tag{2.9}$$

2. Binary trees: In this case a help-key needing to be updated is generated once and encrypted twice, thus,

$$E = 2 \cdot G \tag{2.10}$$

3. Based on the key generator specified in [An00], the generation of one key costs two encryptions, i.e.,

$$C_g = 2 \cdot C_e \tag{2.11}$$

Setting (2.10) and (2.11) in (2.4):

$$BPT_{i+1} = 2.C_e.E$$

(2.12)

4. Exponential distribution of the inter-arrival times of disjoin requests [Al96]. According to [Ya01, Zh01], the number of disjoin requests in a rekeying interval T is given by the following formula, where n denotes the group size.  $\mu$  is the disjoin request rate.

$$N_D = n(1 - e^{-\mu T}) (2.13)$$

5. Balanced trees and an equal number of join and disjoin requests in the rekeying interval,  $N_J = N_D$ . The number of encryptions needed to process this batch can be calculated according to [Li01] as follows, where h represents the tree depth,  $h = log_2 n$ .

$$E = 2\sum_{i=0}^{h-1} 2^{i} \left(1 - \frac{\binom{n - n/2^{i}}{N_{D}}}{\binom{n}{N_{D}}}\right)$$

(2.14)

Setting (2.13) in (2.14), (2.14) in (2.12), and (2.12) in (2.9):

$$JBD_{worst}^{p} = T + 4C_{e} \sum_{i=0}^{h-1} 2^{i} \left(1 - \frac{\binom{n - n/2^{i}}{n(1 - e^{-\mu T})}}{\binom{n}{n(1 - e^{-\mu T})}}\right)$$

(2.15)

The resulting *JBD* is a function of the rekeying interval, the request rate, the encryption cost factor and the group size:

$$JBD^{p}_{worst} = f_{l}(T, \mu, C_{e}, n)$$

The following two case study simulations illustrate the hard and soft management of QoS introduced in the previous sections.

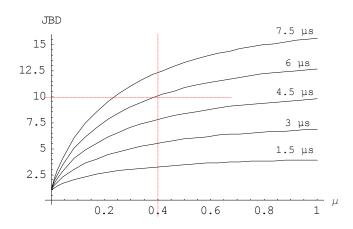

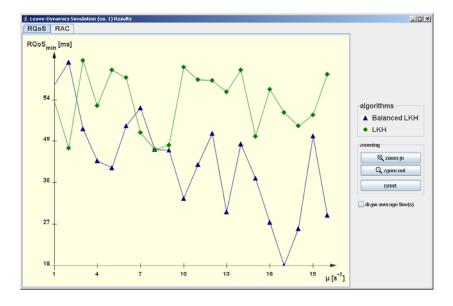

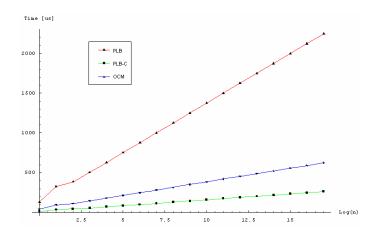

#### Case study 1

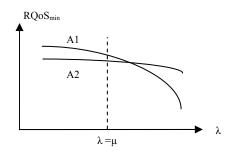

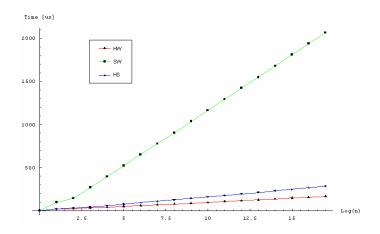

If the rekeying interval has a pre-specified value, e.g., for communication overhead reasons, then JBD can only be controlled by the encryption cost factor  $C_e$  for some group size n. **Figure 2.8** shows JBD as a function of the request rate  $\mu$  with  $C_e$  as a parameter and with:

**Figure 2.8.**  $JBD^{p}_{worst} = f(\mu, C_e)$ ; T, n = const.

The diagram of **Figure 2.8** can be viewed as a representation of the design space which can be used to decide on the minimal performance of the encryption algorithm and/or the minimal performance of the underlying platform. If the maximal acceptable join batch delay equals 10 sec, for example, and the maximal request rate in the multicast group is  $\mu = 0.4 \text{ sec}^{-1}$ , then  $C_e$  must be chosen equal to  $6.10^{-6} \text{ sec}$  as a maximum. The sought value of  $C_e$  can then be obtained by means of selecting an appropriate encryption algorithm, or by using a sufficiently powerful runtime platform, or both.

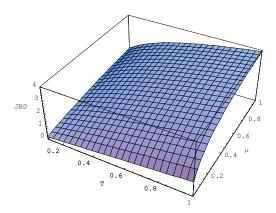

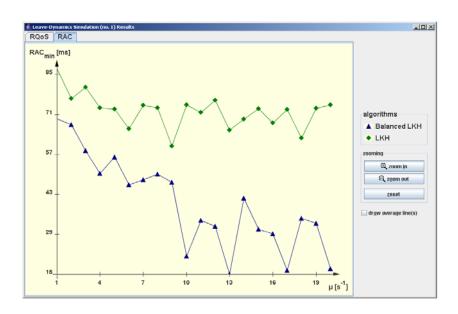

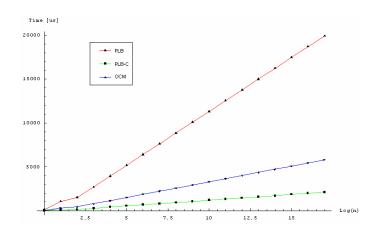

#### Case study 2

For a given encryption algorithm and a given runtime platform the JBD can be optimized softly by the rekeying interval according to the request rate. **Figure 2.9** shows the simulation results for JBD as a function of T and  $\mu$  with:

$$n = 524.288$$

$C_e = 1.5.10^{-6} \text{ sec}$

By exploiting this representation it can be decided on the rekeying interval appropriate to some value of the request rate in order to satisfy the QoS specification. The algorithm presented in Section 2.4.3 provides without loss of generality an automatic selection of the rekeying interval according to both the network situation and the tree state in real-time.

2.6 SUMMARY 24

**Figure 2.9.**  $JBD^{p}_{worst} = f(\mu, T)$ ;  $C_{e}$ , n = const.

# 2.6 Summary

In this chapter the problems of quality of service and access control associated with batch rekeying were investigated. The analysis has resulted in several improvement possibilities of the rekeying system which can be summarized in form of the following hints:

- 1. Arrange for a high-performance execution platform.

- 2. Provide efficient algorithms for encryption and key generation.

- 3. Provide efficient key management algorithms.

- 4. Exploit a pipelined batch rekeying algorithm.

- 5. Use event-driven batch rekeying with a variable rekeying interval.

Case studies have demonstrated the two generic methods of QoS management for batch rekeying: (1) hard, and (2) soft QoS management. Event-driven batch rekeying assumes given values for system-specific parameters  $JBD_{max}$  and  $DBD_{max}$ .

# 3 Rekeying Benchmark

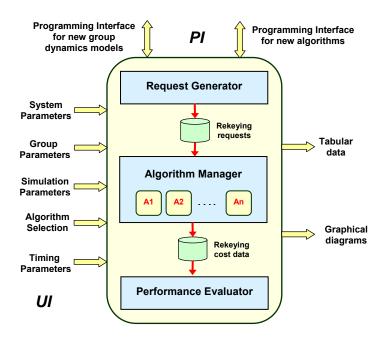

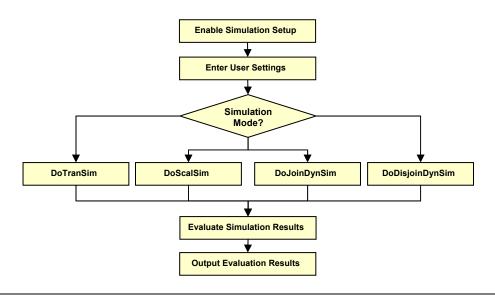

#### 3.1 Overview

This chapter presents a novel approach to performance evaluation of rekeying algorithms. First, Section 3.2 illustrates the problem of rekeying performance evaluation. Section 3.3 introduces the design concept of a rekeying benchmark as a solution to this problem. New performance metrics and relating simulation modes are then discussed in Section 3.4. The design of the rekeying benchmark and its components is detailed in Section 3.5. Section 3.6 depicts some implementation issues of the benchmark. Lastly, Section 3.7 illustrates the application of the benchmark by means of a simulation case study.

## 3.2 Rekeying Performance Evaluation Problem

A typical problem in scientific work relates to the analysis and evaluation of own results and comparing them with those of related work. This problem, on the one hand, can be attributed to the increasing number of scientific institutions and the vast publication possibilities such as journals, conferences and workshops. This trend hinders a comprehensive overview of the state-of-the-art situation in some scientific field. On the other hand, some research areas – because of their novelty, complexity, or both – lack a unified way to draw these comparisons. This situation, for instance, does not apply to the work on performance optimization of the new encryption algorithm AES. Since its release in 2001 by NIST [Ni01], an enormous amount of work is published. However, the recognized way to describe the performance of a block cipher in terms of throughput and latency allows for a reliable comparison between these solutions. On the contrary, such unified metrics are still missing for estimating the performance of rekeying algorithms, which is caused by both the novelty of this problem area and its complexity.

This complexity, however, did not only result in largely different metrics to express rekeying performance, but also in diverse ways of estimating these metrics. In this respect, the reader of proposed work on multicast group rekeying is not only confronted with different performance quantities, but also with various estimation methods such as analytical modeling, simulation based approaches, and real-time measurement using provisional prototypes. Each one of these techniques has specific constraints and drawbacks, which can be outlined in the following points:

- 1. *Analytical approaches* are always based on simplified models and relate to special cases such as full balanced trees. As a rule, rekeying performance can only be expressed by abstract numbers of some primitive operations, e.g. the number of encryptions, for borderline cases, e.g. a worst-case analysis or a best-case analysis.

- 2. **Simulation based approaches** are mostly used to prove a presented analytical investigation without model enhancement and without including sophisticated effects such as group dynamics.

- 3. *Measurement approaches* deliver results, which are strongly dependent of the deployed cryptographic primitives, their implementation, and of the platform they run on.

Furthermore, the performance of group rekeying is influenced by a couple of factors reflecting the group state and dynamics, on the one hand, and by some algorithm specific parameters such as the tree degree in LKH, on the other. Accordingly, two questions arise for performance estimation: which factors must be taken into consideration, and how should they be included, as variables or as parameters? Again, the largely different answers to these questions in related work make a large contribution to the performance evaluation problem. In summary, the difficulty of evaluating different rekeying algorithms is attributed to the following three points:

- 1. Non-unified performance estimation methods.

- 2. Non-unified consideration of the input quantities affecting the performance.

- 3. Non-unified definition of output metrics representing the performance.

**Table 3.1** delivers a representative view of this situation in related work. Note that an input quantity can be considered either as a variable or as a parameter. This differentiation is needed when the corresponding performance metric is a function of several variables. For some estimation, a variable, which is kept constant, is called a parameter.

The diverse ways of looking at rekeying performance do not only obstruct an objective assessment of the corresponding algorithms, but also give an explanation of some inconsistencies in the conclusions drawn by some related work. The following two examples illustrate this point:

## Example 3.1: Tree Degree

Though many publications on tree-based rekeying do not address the effect of tree degree, some work investigates its value, which results in optimized rekeying costs. While [Wo00] states a value of 4 as an optimal tree degree, [Go03] proves that trees with variable degree between 2 und 3 are more efficient.

#### Example 3.2: Tree Rebalancing

A lot of related work on LKH has commented that the logarithmic relation of rekeying costs to group size may be easily violated if the tree gets out of balance as an effect of multiple disjoin operations. In extreme cases rekeying costs can even grow linearly to the group size which makes a rebalancing of the tree indispensable.

Table 3.1. Dissimilarity in rekeying performance estimation in related work

| Wast     | Performance estimation | Performance estimation mode                                                                      | Input Quantities                                      |                                                          | Performance                                                          |  |  |

|----------|------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------|--|--|

| Work     |                        |                                                                                                  | Parameter                                             | metric                                                   |                                                                      |  |  |

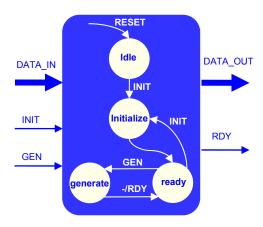

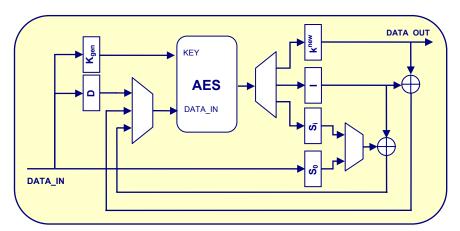

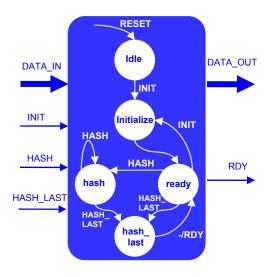

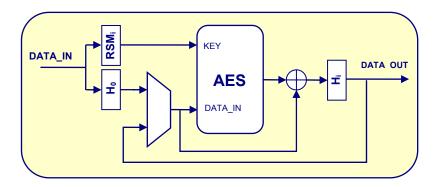

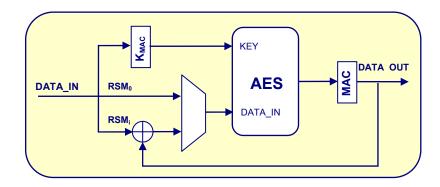

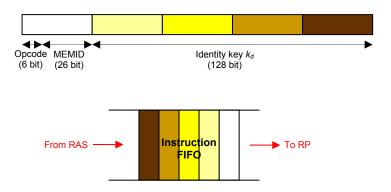

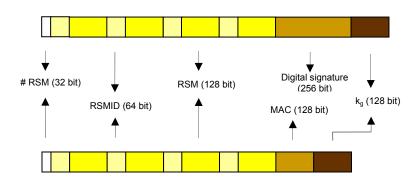

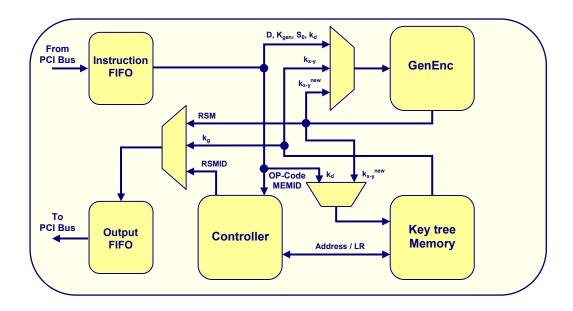

|          | Analytical             | Average costs Group size                                                                         |                                                       | ıp size                                                  | # Encryptions                                                        |  |  |