### **DIPLOMARBEIT**

Titel der Diplomarbeit

# A Product Mix and a Material Flow Problem Concerning the Semiconductor Manufacturing Industry

Verfasserin

Vera Hager

gemeinsam mit

Karin Spannraft

angestrebter akademischer Grad

Magistra/Magister der Sozial- und Wirtschaftswissenschaften (Mag. rer. soc. oec.)

Wien, im Dezember 2009

Betreuer/Betreuerin:

Studienkennzahl It. Studienblatt: Studienrichtung It. Studienblatt:

157

Internationale Betriebswirtschaft

o. Univ.-Prof. Dipl.-Ing. Dr. Richard F. Hartl

# Ehrenwörtliche Erklärung

Wir versichern hiermit, dass wir die vorliegende Arbeit mit dem Thema

#### A Product Mix and a Material Flow Problem Concerning the Semiconductor Manufacturing Industry

selbstständig verfasst und alle uns zuteil gewordenen Hilfen sowie das benutze Schrifttum am Ende der Arbeit angegeben haben. Es wurden keine unerlaubten Hilfen eingesetzt und die vorliegende Arbeit wurde bisher in keiner Form als Prüfungsarbeit vorgelegt.

Wien, im Dezember 2009

#### Acknowledgement

We would like to dedicate this thesis to our parents for supporting and financing our studies.

Furthermore, we take this opportunity to thank all those who have supported us in preparing and finishing our work. Without the help of all those people, we would have never been able to complete it.

In particular, we wish to thank Dr. Martin Romauch for his active support in the preparation of the thesis. We are grateful for his helpful suggestions and patience.

We would also like to thank all those who have helped us in preparing our assignment. We are grateful for the help of o. Univ.-Prof. Dipl.-Ing. Dr. Richard F. Hartl, Sophie Parragh PhD and Mag. Dipl.-Ing. Dr. Verena Schmid, who supported us with useful information and helped us to overcome any kind of problem. Additionally, we want to thank Mag. Eva Ferrigato for proofreading our work.

# **Table of Contents**

| <u>LIST</u>  | OF FIGURES                                                   | VII       |

|--------------|--------------------------------------------------------------|-----------|

|              |                                                              |           |

| <u>LIST</u>  | OF ABBREVIATIONS                                             | VIII      |

|              |                                                              |           |

| INTR         | ODUCTION AND PROBLEM DESCRIPTION (VERA HAGER/KARIN           |           |

|              | _                                                            | 4         |

| SPAI         | NNRAFT)                                                      | 1         |

|              |                                                              |           |

| <u>1.</u>    | INFINEON – THE COMPANY (VERA HAGER)                          | 3         |

|              |                                                              |           |

| 1.1          | Infineon Technologies AG                                     | 3         |

| 1.2          | Infineon Technologies Austria AG                             | 7         |

| 1.3          | INFINEON TECHNOLOGIES AG AND THE ECONOMIC & FINANCIAL CRISES | 9         |

| •            | LUCTORY AND DEVEL ORMENT (KARIN ORANNIRAET                   | 40        |

| <u>2.</u>    | HISTORY AND DEVELOPMENT (KARIN SPANNRAFT                     | 12        |

|              |                                                              |           |

| 2.1          | HISTORY                                                      | 12        |

| 2.2.<br>2.3. | MOORE'S LAW TECHNOLOGICAL DEVELOPMENT AND COSTS              | 13<br>14  |

| 2.3.         | TECHNOLOGICAL DEVELOPMENT AND COSTS                          | 14        |

| <u>3.</u>    | CLEANROOM (KARIN SPANNRAFT)                                  | 15        |

|              |                                                              |           |

| 3.1.         | TWO AIR FLOW PRINCIPLES IN CLEANROOMS:                       | 16        |

| 3.2.         |                                                              | 16        |

|              |                                                              |           |

| <u>4.</u>    | BASIC MATERIALS IN SEMICONDUCTOR MANUFACTURING (K            | ARIN      |

| SPA          | NNRAFT)                                                      | 18        |

|              |                                                              |           |

| 4.1.         | BASIC ELEMENTS USED                                          | 18        |

| 4.1.1        | . SILICON                                                    | 18        |

|              | . Aluminum                                                   | 18        |

| _            | S. GOLD                                                      | 19        |

|              | SILVER                                                       | 19        |

| 4.1.5        | . Copper                                                     | 19        |

| <u>5.</u>    | SCHEDULING PROCEDURES IN SEMICONDUCTOR                       |           |

|              | UFACTURING (KARIN SPANNRAFT)                                 | 20        |

| 1117KIN      | or no round (maint of Addition 1)                            |           |

| <b>5</b> 1   | FLOW SHOP                                                    | 20        |

|              | . PERMUTATION FLOW SHOP                                      | 20        |

|              | JOB SHOP                                                     | <b>20</b> |

|              | RE-ENTRANT FLOW                                              | 21        |

| <u>6.</u>    | STRUCTURE OF A WAFER FAB (KARIN SPANNRAFT)                                           | 22           |

|--------------|--------------------------------------------------------------------------------------|--------------|

|              |                                                                                      |              |

| <u>7.</u>    | THE MANUFACTURING PROCESS – OVERVIEW (VERA HAGER)                                    | 24           |

|              |                                                                                      |              |

| 7.4          | DROCESSING STEDS IN DETAIL (VERA HACER)                                              | 27           |

| <u>7.1</u>   | PROCESSING STEPS IN DETAIL (VERA HAGER)                                              | 27           |

|              |                                                                                      |              |

|              | OXIDATION                                                                            | 27           |

|              | PHOTOLITHOGRAPHY                                                                     | 29<br>30     |

| 7.1.3 E      |                                                                                      | 32           |

|              | N-TYPE DOPING                                                                        | 32           |

|              | P-TYPE DOPING                                                                        | 33           |

| 7.1.5 ld     | ON IMPLANTATION AND ANNEALING                                                        | 33           |

| 7.1.6        | CLEANING TREATMENTS AND TESTING                                                      | 34           |

| •            | POTENTIALLY COOLIDDING (OCUES (VED A LIACED)                                         | 0.5          |

| <u>8.</u>    | POTENTIALLY OCCURRING ISSUES (VERA HAGER)                                            | <u>35</u>    |

| •            |                                                                                      |              |

| <u>9.</u>    | DETERMINISTIC AND STOCHASTIC MODEL FORMULATION (KAR                                  |              |

| <u>SPANI</u> | NRAFT)                                                                               | 37           |

|              |                                                                                      |              |

| 9.1          | DETERMINISTIC BASIC MODEL                                                            | 37           |

| _            | TOCHASTIC BASIC MODEL                                                                | 39           |

| 9.2.1        | METHODS FOR CONSIDERING UNCERTAINTY                                                  | 40           |

| <u>10.</u>   | STATEMENT OF TASK (VERA HAGER)                                                       | 42           |

| 10.          | STATEMENT OF TASK (VERA HAGER)                                                       | 72           |

| 44           | DRODUOT MIX OUDDROD! EM (KADIN ODANNDAET)                                            | 40           |

| <u>11.</u>   | PRODUCT MIX SUBPROBLEM (KARIN SPANNRAFT)                                             | <u>43</u>    |

|              |                                                                                      |              |

| 11.1. N      | ATHEMATICAL FORMULATION                                                              | 47           |

| 12.          | MATERIAL FLOW SUBPROBLEM (VERA HAGER)                                                | 50           |

| 14.          | MATERIAL FEOW COST ROBLEM (VERA HACER)                                               | <u> </u>     |

| 40.4         | Course Course Course Course Volume - Reviews Breeze Volume                           | <b>5</b> 4   |

|              | GENERAL CHARACTERIZATION OF THE VEHICLE ROUTING PROBLEM OPEN VEHICLE ROUTING PROBLEM | <b>54</b> 57 |

|              | ADJUSTMENTS AND SIMILARITIES OF THE STANDARD VRP AND THE OPEN VI                     |              |

| 12.1.2       | TO THE MATERIAL FLOW SUBPROBLEM                                                      | 60           |

| 12.2         | MATHEMATICAL FORMULATION                                                             | 63           |

| 12.3         | ABBREVIATED MATHEMATICAL FORMULATION                                                 | 68           |

| 12.4         | AUTOMATED MATERIAL HANDLING SYSTEM (AMHS)                                            | 70           |

| 40           | ADDDO AGUEO TO GOLVINO DDODI EMO IN GENEDAL (VEDA                                    |              |

| <u>13.</u>   | APPROACHES TO SOLVING PROBLEMS IN GENERAL (VERA                                      |              |

| <u>HAGE</u>  | R/KARIN SPANNRAFT)                                                                   | <u>76</u>    |

|              |                                                                                      |              |

|              | EXACT METHODS                                                                        | <b>77</b>    |

|              | BRANCH AND BOUND                                                                     | 77<br>70     |

| 13.1.2       | BRANCH AND CUT                                                                       | 78           |

| 13.              | 2 HEURISTICS – APPROXIMATION PROCEDURE                                    | 78                        |

|------------------|---------------------------------------------------------------------------|---------------------------|

| 13.2             | 2.1 Constructive Heuristics                                               | 79                        |

| _                | 2.2 IMPROVEMENT HEURISTICS                                                | 81                        |

| 13.              |                                                                           | 82                        |

|                  | 3.1 ANT COLONY OPTIMIZATION                                               | 83                        |

|                  | 3.2 TABU SEARCH                                                           | 84                        |

|                  | 3.3 VARIABLE NEIGHBORHOOD SEARCH                                          | 85                        |

| _                | 3.4. SIMULATED ANNEALING                                                  | 86                        |

| 13.              | 3.5. GRASP: GREEDY RANDOMIZED ADAPTIVE SEARCH PROCEDURES                  | 88                        |

| <u>14.</u>       | IMPLEMENTATION (VERA HAGER)                                               | 91                        |

| <u>15.</u>       | COMPUTATIONAL RESULTS OF THE PRODUCT MIX ISSUE                            | (KARIN                    |

| SP               | ANNRAFT)                                                                  | 92                        |

| <u>16.</u><br>HA | COMPUTATIONAL RESULTS OF THE MATERIAL FLOW ISSI                           | <u>UE (VERA</u><br>- 95 - |

| <u>co</u>        | NCLUSION (VERA HAGER/KARIN SPANNRAFT)                                     | - 98 -                    |

|                  |                                                                           |                           |

| BIE              | BLIOGRAPHY                                                                | - 99 -                    |

| ΑP               | PENDIX A – MODELS                                                         | - 106 -                   |

|                  |                                                                           |                           |

| 1.               | PRODUCT MIX WITHOUT INTEGER VARIABLES                                     | - 106 -                   |

| 1.1              | PRODUCT MIX WITH INTEGER VARIABLES                                        | - 108 -                   |

| 2.               | MATERIAL FLOW MODEL                                                       | - 110 -                   |

| 2.1              | ABBREVIATED MATERIAL FLOW MODEL                                           | - 116 -                   |

| <u>AP</u>        | PENDIX B – DATA SETS                                                      | - 122 -                   |

|                  |                                                                           |                           |

|                  | ODUCT MIX ISSUE                                                           | - 122 -                   |

| MA.              | TERIAL FLOW ISSUE                                                         | - 124 -                   |

| <u>AP</u>        | PENDIX C – COMPUTATIONAL RESULTS IN DETAIL                                | - 127 -                   |

| 4                | Dropuot Miy Morei                                                         | 407                       |

|                  | PRODUCT MIX MODEL  MATERIAL FLOW MODEL - XPRESS RESULTS                   | - 127 -<br>- 128 -        |

|                  | MATERIAL FLOW MODEL - APRESS RESULTS  . ABBREVIATED MATERIAL FLOW PROBLEM | - 128 -<br>- 131 -        |

|                  | MATERIAL FLOW MODEL - C++ RESULTS                                         | - 131 -<br>- 133 -        |

| J.               | MATERIAL I LOW MODEL - OTT RESULTS                                        | - 133 -                   |

| <u>AB</u>        | STRACT (VERA HAGER/KARIN SPANNRAFT)                                       | - 139 -                   |

| 7119             | SAMMENFASSUNG (VERA HAGER/KARIN SPANNRAFT)                                | - 140 -                   |

| <u> _ U</u>      | SAMMEN ASSUNG (VENA HAGEN/NANIN SPAMMNAFI)                                | - 140 -                   |

| CURRICULUM VITAE: VERA HAGER      | - 141 · |  |

|-----------------------------------|---------|--|

|                                   |         |  |

| CURRICULUM VITAE: KARIN SPANNRAFT | - 142 - |  |

# List of figures

| FIGURE 1: NUMBER OF EMPLOYEES PER COUNTRY[14]                   | 6      |

|-----------------------------------------------------------------|--------|

| FIGURE 2: SURVEY OF REVENUE PER SEGMENT[15]                     | 9      |

| FIGURE 3: MOORE'S LAW[43]                                       | 13     |

| FIGURE 4: AIRFLOW PATTERN[11]                                   | 16     |

| FIGURE 5: NASA'S GLENN RESEARCH CENTRE CLEANROOM[62]            | 22     |

| FIGURE 6: GENERIC SURVEY OF SEMICONDUCTOR MANUFACTURING PROCES  | S[27]  |

|                                                                 | 25     |

| FIGURE 7: FABRICATION OF A SINGLE LAYER[35]                     | 26     |

| FIGURE 8: DEMONSTRATION OF A FURNACE FOR OXIDATION[54]          | 28     |

| FIGURE 9: GROWTH BEHAVIOR OF OXIDE ON SILICON[54]               | 29     |

| FIGURE 10: TRANSMISSION OF THE PATTERN ON THE OXIDE LAYER[54]   | 30     |

| FIGURE 11: ISOTROPIC AND ANISOTROPIC ETCHING[48]                | 31     |

| FIGURE 12: N-DOPING[22]                                         | 32     |

| FIGURE 13: P-DOPING[22]                                         | 33     |

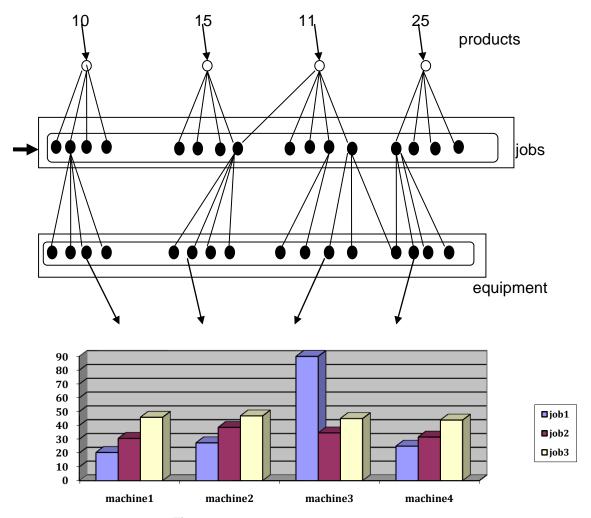

| FIGURE 14: PRODUCT MIX ISSUE - OUTLINE                          | 46     |

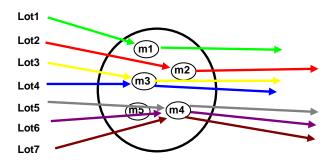

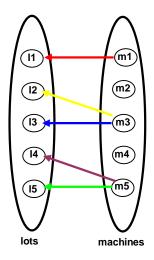

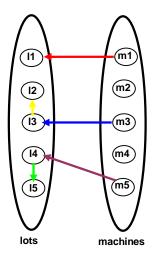

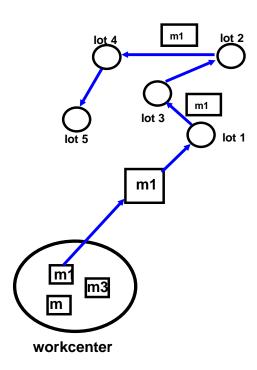

| FIGURE 15: LOT SCHEDULING WITHIN THE WAFER FAB                  | 51     |

| FIGURE 16: WORK CENTRE IN DETAIL WITH ARRIVING LOTS             | 52     |

| FIGURE 17: LOT PROCESSING ON MACHINE WITHOUT SEQUENCE           | 53     |

| FIGURE 18: LOT PROCESSING ON MACHINE                            | 53     |

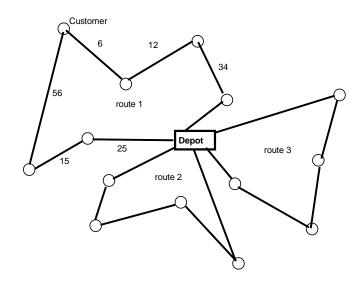

| FIGURE 19: GENERAL VEHICLE ROUTING PROBLEM                      | 55     |

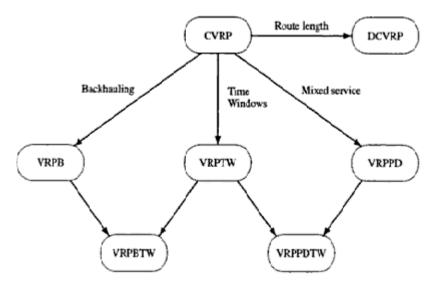

| FIGURE 20: SURVEY OF BASIC VRP'S [64]                           | 57     |

| FIGURE 21: MATERIAL FLOW ISSUE                                  | 62     |

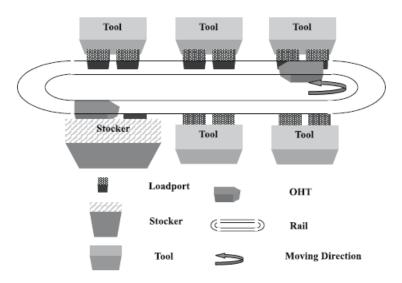

| FIGURE 22: INTRA-BAY MATERIAL HANDLING [41]                     | 71     |

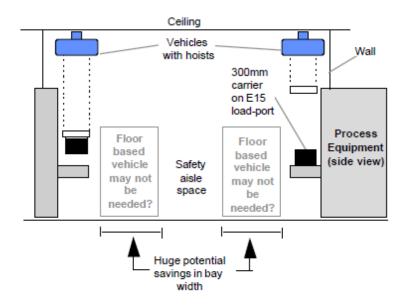

| FIGURE 23: VEHICLE TYPE COMPARISON[55]                          | 74     |

| FIGURE 24: OVER HOIST INTRA-BAY MATERIAL HANDLING [55]          | 75     |

| FIGURE 25: OUTLINE OF PRIORITY RULES [68]                       | 81     |

| FIGURE 26: VNS ALGORITHM[42]                                    | 86     |

| FIGURE 27: PSEUDOCODE GRASP METAHEURISTIC [29]                  | 89     |

| FIGURE 28: A PSEUDOCODE OF A LOCAL SEARCH WITH THE CONSTRUCTIVE |        |

| SOLUTION (SOLUTION) [29]                                        | 89     |

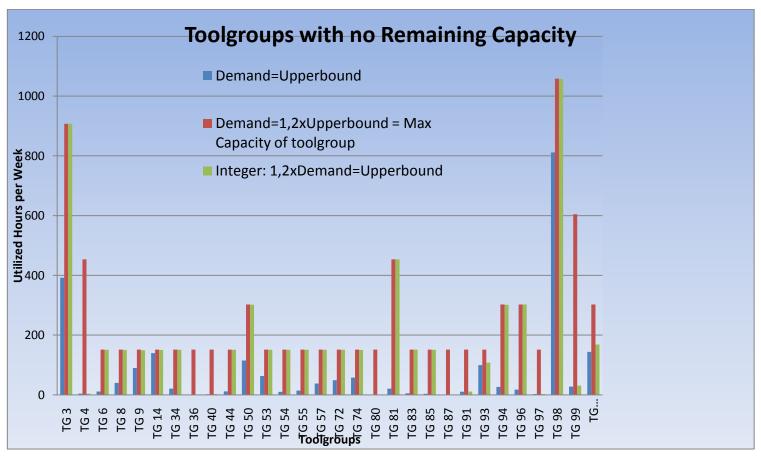

| FIGURE 29: TOOLGROUPS WITH NO REMAINING CAPACITY IN SCENARIO 2  | 93 -   |

| FIGURE 30: UTILIZATION IN PERCENT                               | 94 -   |

| FIGURE 31: COMPUTATION TIME OF EXACT AND ABBREVIATED MODEL      | 95 -   |

| FIGURE 32: COMPARISON OF TOTAL MAKESPANS                        | 96 -   |

| FIGURE 33: QUALITY OF RESULTS                                   | 96 -   |

| FIGURE 34: COMPARISON OF COMPUTATION TIME                       | - 97 - |

#### List of abbreviations

ABS anti-lock braking system

AG Aktiengesellschaft / stock corporation

AGV Automatic guided vehicles

AMHS Automated material handling system

CEO Chief executive officer

CMOS Complementary metal-oxide-semiconductor

CPE Customer premises equipment

LPT Longest processing time

CR Critical ratio

CVRP Capacitated Vehicle Routing Problem

DRAM Dynamic random access memory

EBIT Earnings before interest and taxes

EDD Earliest due date

EDGE Enhanced Data rates for GSM Evolution

ESD Earliest start date

ESP Electronic Stability Programme

FA Factory automation

FIFO First in First out

GPRS General packet radio service

GRASP Greedy Randomized Adaptive Search Procedures

GSM Global system for mobile communication

H<sub>2</sub> Hydrogen

H<sub>2</sub>O<sub>2</sub> Hydrogen peroxide

HV Highest value

IC Integrated circuit

ITRS International Technology Roadmap for Semiconductors

mm Micrometer

MOSFET metal-oxide-semiconductor field-effect transistor

NASA National Aeronautics and Space Administration

O<sub>2</sub> Oxide

OVRP Open Vehicle Routing Problem

PC Personal computer

R&D Research & Development

RF Radio frequency

RGV Rail guided vehicles

Rm Random

SA Simulated Annealing

S<sub>i</sub> Silicon

S<sub>i</sub>O<sub>2</sub> Silicon oxide

SPT Shortest processing time

SrPT Shortest remaining processing time

TPM Trusted platform module

TSP Traveling Salesman Problem

VNS Variable neighborhood search

VRP Vehicle Routing Problem

VRPB Vehicle Routing Problem with Backhauls

VRPPD Vehicle Routing Problem with Pick up and Delivery

#### Introduction and Problem Description

The overall purpose of an enterprise consists of achieving the highest possible gain without extensive investments and disbursements. Exactly current economic instances enhance the pressure on companies to undertake extensive savings in order to ensure their continuity and to overcome challenges concerning their daily business. In most instances the workforce is the first position which is subject to abridgements. To prevent these retrenchments, the underlying work attempts to accomplish savings in their current expenditures and their utilized time units in order to pervade production orders while optimizing the overall production process.

The subjacent thesis is composed in collaboration with Infineon Technologies Austria AG which is a well acquainted business in the Austrian semiconductor manufacturing industry. As the whole production process in this branch is subject to a tremendous level of complexity, the work abstracts two different problems which are associated to Infineon Technologies Austria AG. More precisely the thesis deals with a product mix problem and a material flow problem

The product mix problem mainly emphasizes on maximizing the company's profit by taking capacity and demand restrictions into account. An important characteristic of this model insists on the decomposition of products to jobs and their further assignment to different tool groups.

However, the material flow problem aims at acquiring the optimal allocation of lots to machines while curtailing the overall time units for incoming production orders. The main property of the subjacent issue is the affinity to the well established open Vehicle Routing Problem, which targets to minimize its costs or time units while servicing customers by means of several vehicles. Furthermore, the material flow problem reveals the quick achievement of complexity limits in the implementation and thus attempts to ameliorate its boundaries of intricacy and lot assignment through heuristics and priority rules.

The work is organized as follows: In the first part, the organization of the company and as well the high-complex production process with its enormous requirements of high cleanness standards are outlined. The subsequent chapters deal with the presentation of the two underlying production issues, its mathematical formulation and capabilities for their optimization.

The second division of the work puts emphasis on the implementation of the theoretical models by means of two software packages namely XPRESS and C++. To evaluate the proposed models, generated results of the exact and heuristic approaches are assessed with respect to their computational times and deviations of optimality. Concluding remarks are quoted at the end of the thesis.

#### 1. Infineon – The Company

#### 1.1 Infineon Technologies AG

In 1990 Infineon Technologies AG was incorporated due to the fact that the semiconductor production was outsourced from the holding company, Siemens AG. The head office of the newly founded company is located in Neubiberg near Munich, Germany. Today Infineon Technologies obtains a global performance operating through its subsidiaries spread over all five continents, totaling in 58 countries, whereat the majority of their operations and investments is concentrated on Central Europe, Asia and North America[15] In the year 2006, Infineon Technologies realized a further step in its strategic by carving out its memory products division to a new company named Qimonda. Initially Qimonda resides as an entirely owned subsidiary of Infineon Technologies[56] Since the beginning of the calendar year 2007 Qimonda suffers great decreases in turnover through furthermore declining prices of its products. Due to this fact Infineon Technologies strives to divest its remaining 77, 5 % shareholding of Qimonda in the fiscal year 2008[15] Besides Qimonda, Infineon Technologies AG holds a 100 % share of the company Comneon Solutions, which is a leading provider of software for mobile communications[13]

In order to remain an innovative, foresighted and ambitious company, Infineon Technologies emphasizes its business on three values, which are significantly for the present economic status:

- Efficiency in Energy

- Communications

- Security

In addition to the semiconductor fabrication for automotive and industrial electronics Infineon Technologies provides chip cards as well as security

and communication devices. The outline below gives an impression of the comprehensive diversity of their existing product lines[15]

#### Automotive

components of the automotive infotainment (dashboard, navigation, multimedia), body and convenience elements (lightening, seat control), safety and vehicle devices (ABS / ESP, airbag)

#### **Industry and Multimarket**

renewable energy (solar, wind), automation, medical technology, power supplies (notebooks, servers), computer peripherals

Due to their creation of substantial know how and competence over the last 40 years in the sector of automotive, industry and Multimarket, Infineon Technologies holds a leading position in its global target markets[16]

#### Chip card and Security

payment, identification, SIM cards, pay-TV, computer and network security platforms, TPM<sup>1</sup>

Within in the market of Chip cards Infineon Technologies obtains the prime position with a market share of 27%.

#### Wireless Solutions and Communications

mobile phone platforms, mobile software, Radio Frequency (RF) technology, TV and satellite receiver, navigation, broadband CPE<sup>2</sup>, wireless infrastructure and telephones, home network

In the field of RF technologies for mobile phones and in the wireline access market Infineon Technologies occupies the first place with a market share of 22 %.

The products of Infineon Technologies stand for unique quality, state-of-the-art technology and enormous persistency. Due to their profound knowledge and experiences over years in the semiconductor manufacturing, their steady improvement of existing products, their rapid adjustments as a result of quick changes in consumers' demands and their

<sup>&</sup>lt;sup>1</sup> Trusted Platform Module: a specified chip for enhancing computer security

<sup>&</sup>lt;sup>2</sup> Customer Premises Equipment: Devices which are interfaced with telephone or data network (e.g. fax machines, modes or telephones)

focus on environmental changes and requirements, Infineon Technologies obtains the leading position in the market[15]

The following utterances stated below should emphasize the leading position of Infineon Technologies AG.

"Semiconductors for power electronics are the key to efficient energy management. Infineon is the global market leader in power electronics." [24]

"As the leader in this market and in power technologies, we can enable the industry to minimize power losses and maximize energy savings along the entire power cycle: generation, transmission and consumption." [24]

"It is expected that 80 percent of all electrical energy will be controlled and regulated by power electronics by 2010." [24]

Infineon Technologies AG recognized one of the first companies to develop modern technologies due to the awareness of finite energy resources and global warming. Several promising statements of Peter Bauer, CEO of Infineon Technologies AG, are given below out of the interview about energy efficiency used as competitive advantage.

"Our products make a fundamental contribution to energy efficiency. They operate in a phenomenally wide variety of everyday gadgets, such as PCs, notebooks, washing machines, cookers, lamps, air conditioning systems and so on, without the public at large being aware of the fact." [36]

"[...] our chips are to be found in many industrial drives and consumer products [...]. Using our products, these drives can be controlled so as to reduce the energy requirement by 30 to 40 percent." [36]

"It pursues several goals. Firstly, to raise awareness of energy efficiency both internally and externally; secondly, to strengthen our market position and to address existing and new customers; thirdly, to initiate government projects all over the world or get ourselves involved in existing projects devoted to energy efficiency."[36]

"We advise and throw light on existing possibilities for energy-efficient applications and on potential future developments. We know what is technically still feasible, [...]. Infineon teams worldwide are working on raising the awareness of energy efficiency issues among politicians and organizations."[36]

"The market opportunities for our entire product portfolio are better than ever before. The energy-efficient product market will provide sustained growth. We started to position ourselves for this sphere in good time." [36]

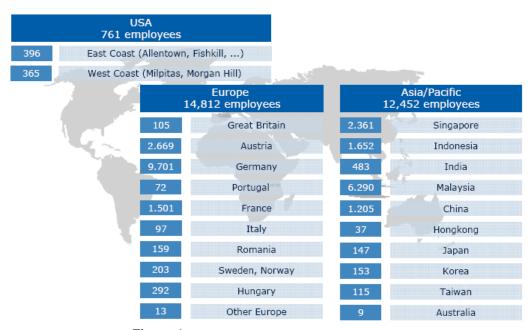

Infineon Technologies AG employs 28.025 workers (status 12/2008 without Qimonda) around the world (status 09/2007 29.598 employees) and generated in the business year 2008 annual sales of 4.321 billion Euros (status fiscal year 2005 6.8 billion Euros). There leading position in the market arise form their profound understanding for technology (6.270 workers operate in the R&D sector) resulting in over 21.600 patents[14]

Figure 1: Number of employees per country[14]

#### 1.2 Infineon Technologies Austria AG

In Austria the Infineon Technologies AG is represented through five subsidiaries, whereat the headquarter is located in Villach. Additional associated companies are established in Vienna, Linz, Graz and Klagenfurt. To obtain an overview of the track record of Infineon Technologies Austria AG over the last years the following chronological outline should help[15]

1970: Incorporation of the production entity of diodes in Villach

1979: Incorporation of the development entity in Villach

Production of the 4 inches (100 mm<sup>3</sup>) wafers initiated

1984: Wafer production of 5 inches (127 mm) started

1987: Expansion of the research and development department in Villach

1997: Villach receives the status of being a hub of competence for power electronics

Begin of the 6 inches (150 mm) wafer production

1998: Formation of the subsidiary in Graz

1999: Incorporation of the development centre in Linz

2000: Initial public offering of Infineon Technologies AGSoftware Development centre COMNEON was incorporatedStart of the 8 inches (200 mm) wafer production

2001: Another incorporation of a development centre in Vienna until 2003

2003: Villach obtains the status and functions of an headquarter

2004: Formation of another subsidiary in Klagenfurt

2005: Foundation of the development centre in Bucharest

Start of construction of a front-end factory<sup>4</sup> in Kulim, Malaysia

Opening of a new research and development building in Villach

2006: Opening of the development centre in Bucharest

Disclosure of the front-end factory in Kulim, Malaysia

Expansion of the development centre in Graz

Integration of an expert support service centre in Klagenfurt

2008: Opening of the new building for research and innovation in Villach

<sup>4</sup> Implies all production processes to fabricate a wafer.

\_

<sup>&</sup>lt;sup>3</sup> Micrometer, a human hair obtains a diameter of approximately 70 mm [14]

In total, about 2.900 employees are operating in the established locations through Austria (until the end of the fiscal year 08/09 the workforce will be reduced to 2.600 workers due to the planned reduction of jobs) and approximately 1.000 workers of the entity are performing actions in the Research and Development (R&D) sector[14]

In the preceding financial year Infineon Technologies Austria AG generated 1, 2 billions of Euros by means of a production volume of 20 billions of chips. Due to their high requirement to innovate state-of-the-art technologies through Europe or at best through the world, it is not surprising that about one third of the Austrian employees are operating in the R&D segment and about 228 millions of Euros, this relates to 19% of the total revenues, are invested in the development of innovative approaches. Hence, Infineon Technologies Austria AG is one of the companies through Austria which undertakes that much vast capital expenditure in this department.

Solely Villach stands out for operating in the R&D as well as in the production segment. They focus their attention in the production segment towards the fabrication of automotive and industrial electronics. This sector will be operated with a production capacity of 97%. A variety of about 1,300 products will be fabricated in Austria. In the R&D department they put emphasis on power electronics for automotive and industrial devices as well as Integrated Circuits (ICs) for telecommunication[15]

All the remaining subsidiaries Graz, Linz and Klagenfurt are concentrating on their core competence in the R&D sector. In the fiscal year 2008 Infineon Technologies AG applied for about 200 new patents and at least one high potential from Austrians subsidiaries took part on this innovative technology. [14] However, Vienna is charged with the distribution of Austria and southeast European countries[15]

# 1.3 Infineon Technologies AG and the economic & financial crises

In the fiscal year 2008 the global economy slowed down substantially in comparison to the previous one. The economic recession was deepened through the crises in the financial markets and steadily increasing resource prices. Although there was high financial pressure, Infineon Technologies AG was able to increment their overall revenues about 6% compared to the previous year from 4,074 billion € in 2007 to 4,321 billion € in 2008. The Communication Solution sector denoted the greatest improvement in revenues due to their wireless communication applications.

|                                      | For the years ended September 30, |                     |                               |      |  |

|--------------------------------------|-----------------------------------|---------------------|-------------------------------|------|--|

|                                      | 2007 2008                         |                     |                               |      |  |

|                                      | (                                 | € in millions, exce | millions, except percentages) |      |  |

| Automotive, Industrial & Multimarket | 3,017                             | 74%                 | 2,963                         | 69%  |  |

| Communication Solutions              | 1,051                             | 26                  | 1,360                         | 31   |  |

| Other Operating Segments             | 219                               | 5                   | 100                           | 2    |  |

| Corporate and Eliminations           | (213)                             | (5)                 | (102)                         | (2)  |  |

| Total                                | 4,074                             | 100%                | 4,321                         | 100% |  |

Figure 2: Survey of revenue per segment[15]

Despite this positive improvement in the revenue performance, Infineon Technologies AG reorganized its cost structure in order to respond to the steady increasing risks in the market environment, the negative exchange rate and spread. Therefore, the cost reduction program "IFX10+" was invented in the third quarter of the fiscal year 2008. The reduction program contains the rejection of unprofitable product lines and the efficient utilization of the R&D sector. It also involves the retrenchment of manufacturing costs, a better coordination of the value chain, an optimization in the production processes but also a partly reduction in the workforce. Due to this program, Infineon Technologies AG realized restructuring charges in the amount of 188 million €[15]

The improvement in the overall revenues for the fiscal year 2008 is composed through the increase in the segment of Communication Solutions but also through an augmented sale of patents. However, increased negative affects of the foreign currency of 2% diminished the

overall performance of Infineon Technologies AG. Despite a positive result in the overall revenues, Infineon Technologies AG generates a negative performance of Earnings before interest and taxes (EBIT) resulting mainly through the restructuring charges of 188 million €.

However, which development experienced Infineon Technologies AG in the beginning of the current fiscal year? The revenues declined in the second quarter of the year about 10% that are 83 million € less compared with the previous quarter and a 29% per cent reduction of revenues according a quantity of 302 million € year-over-year. Through their cost reduction program "IFX10+" it was possible to generate about 60 million Euros savings, mainly acquired through reductions in the operating costs. Unfortunately also at the division workforce must diminish its quantity of employees. At the end of March solely 26.400 workers were employed compared to September where 29.100 workers operated at Infineon Technologies AG. Further measures like short time and uncompensated vacations should assist in terms of cost reduction.

For the upcoming quarter a forecasted improvement of 10% will be expected for Infineon Technologies AG in nearly all segments but a greater augmentation will be predicted in the segment of Wireless Solutions. Further, Infineon conducted an enormous reduction in inventory due to a couple of indications of demand stabilization, accordingly the level of inventory and production needs to be adjusted to the current customer deliveries and demands. Along with the benefits of increased sales and further reductions in costs, Infineon Technologies AG predicts a meaningful augmentation in the segment result[15]

In the face of the results of the past six months<sup>5</sup> and the forecasts of the forthcoming quarter, a reduction of the revenues of nearly 20% is expected for the fiscal year 2009.

CEO Peter Bauer valuates the current economic situation in conjunction with the actual positioning of Infineon Technologies AG as follows:

<sup>&</sup>lt;sup>5</sup> Fiscal year October – September, Calendar year January - December

"In this challenging environment, we further need to have a tight grip on expenses. Strategically, Infineon is positioned well. We address the growth markets, which will gain even more in importance in the future with our three core topics energy efficiency, communications, and security. The recent customer endorsements from Bosch and Toyota in automotive power products and from Nokia in single-chip platforms for GSM/GPRS and EDGE illustrate the competitiveness of our product offering and our customers' faith in our operations."[15]

The announcement of the third quarterly report clarifies the upward tendency of Infineon Technologies AG in the current fiscal year. The expected recovery of Infineon's revenues by 10 percent was achieved and could even be excelled by 3 percent. Compared to the previous quarter a significant improvement in its performance was accomplished, mainly driven through its intense production portfolio resulting in greater revenues, significant cost savings by the means of the cost retrenchment program IFX 10+ and through higher production utilization owing to an augmentation of demand. Hence, a positive performance in nearly all segments could be achieved.

The outlook for the remaining quarter is as well promising. Owing to the rise in demand, the production utilization will be accordingly adjusted. Together with a predicted continuing rise in revenues and a furthermore strict cost control, Infineon Technologies AG can assume further improvements in its segment result[15]

#### 2. History and Development

#### 2.1 History

The beginning of semiconductor manufacturing is dated back to 1948. This year AT&T Bell Lab built the first bipolar transistor. The inventors are called Walter Brattain, William Shockley and John Bardeen.[60] About ten years later the junction transistor technology (Planar) was invented. By then it was already possible to produce MOSFETs (metal oxide semiconductor field effect transistors) and transistors that contain integrated circuits, the so-called ICs. The mass production of devices started in the early 1960s because at that time it was possible to prepare silicon in its purest state. Further details concerning wafer fabrication and the basic raw materials are explained in the following chapters[35]

Some advantages of MOSFETs compared to bipolar transistors are:

- A MOSFET only uses 1/10 of the space of a bipolar transistor when their size of structure is even. Therefore, integrated circuits can be developed.

- The design of a device and the electrical features can stay the same even though the dimension of the component is proportionally diminished. The possibility to foresee the characteristics of the devices leads to the construction of roadmaps. The cost reduction by diminishing was enabled by the scalability.

- Low-level consumption circuits using CMOS-technology can be well adapted for ICs[60]

In 1971 the first microprocessor was launched, the mask of it was still handwork. Today's structures of processors cannot be tracked by human beings. Engineers only deal with structural considerations concerning the architecture and the procedures producing the chips. In 2003 more than 100 millions of transistors per head existed and one expected the number to increase up to one billion in 2007[59]

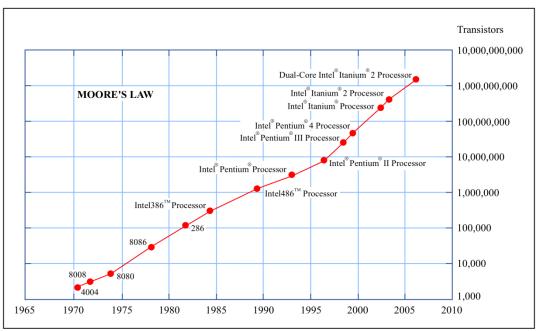

#### 2.2. Moore's Law

The incredible fast growing of microprocessors is explained by Moore's Law. In 1965 Gordon Moore, who was one of the founders of INTEL, discovered the coherence of the capacity of microchips doubling every 18 months, while the production costs were cut into half. Between 1975 and 2001 the duplication really took place in the period of two years[35]

Image by MIT OpenCourseWare.

Figure 3: Moore's Law[43]

This law is not a physical law in the precise meaning; it is an observation which can be extrapolated to a real roadmap. Moore's law has mainly an economic relevance, which means: if the producers adhere by this law, they are able to maximize their profit because of knowing the exact market potential. Another advantage of Moore's finding is that planning becomes much easier for anybody in this business.

Since 1992 the so-called ITRS, the International Technology Roadmap for Semiconductors, exists. This Roadmap takes into account all the necessary technical characteristics for MOSFETs, which are necessary for the adherence of Moore's Law.

The cost reduction can be obtained by different methods. Diminishing represents one method where the size of the structures is minimized and more chips per wafer are produced. Another approach is to enlarge the wafers. The second procedure leads to high investments because new technical devices have to be installed.

Another important point concerning Moore's Law illustrates the Yield. This depicts the function of microchip sizes (the bigger the chip the more a defect is probable), structure sizes (smaller sizes are more susceptible) and shift number (every new shift causes new defect-possibilities).

#### 2.3. Technological Development and Costs

The new technologies induce a cost reduction on one side, but also additional costs on the other side. New technologies require new equipment and new equipment is connected to high investments in semiconductor manufacturing. Expensive devices are needed for producing the constantly smaller structures of transistors. When a new semiconductor manufactory opens, approximately 75% of all costs are spent for new equipment. Therefore, the usage of the devices should be as efficient as possible in order to reduce costs for new investments[35]

An extraordinary expensive investment in this industry is the cleanroom, which will be explained in the next chapter.

#### 3. Cleanroom

The most important point of cleanrooms is the fact that the level of environmental pollutants should be as low as possible. These pollutants consist of dust, airborne microbes, aerosol particles and chemical vapors.

"More accurately, a cleanroom has a controlled level of contamination that is specified by the number of particles per cubic meter at a specified particle size. To give perspective, the ambient air outside in a typical urban environment might contain as many as 35,000,000 particles per cubic meter, 0.5 µm and larger in diameter, corresponding to an ISO 9 cleanroom."[11]

#### Class limits (maximum allowed particles):

|        | FED     |               |        |       |            |      |

|--------|---------|---------------|--------|-------|------------|------|

|        | STD     |               |        |       |            | 5.0μ |

| ISO    | 209     | 0.1 μm        | 0.2 μm | 0.3μm | 0.5μm      | m    |

| Class3 | 1       | 1,000/35      |        |       | 35/1       |      |

| Class4 | 10      | 10,000/345    | 75     | 30    | 352/10     | 0    |

| Class5 | 100     | 100,000/3,450 | 750    | 300   | 3,520/100  | 0    |

| Class6 | 1,000   | 1,000,000/    | N/A    | N/A   | 35,200/    | 7    |

|        |         | 34,500        |        |       | 1,000      |      |

| Class7 | 10,000  | 345,000       | N/A    | N/A   | 352,000/   | 70   |

|        |         |               |        |       | 10,000     |      |

| Class8 | 100,000 | 3,450,000     | N/A    | N/A   | 3,520,000/ | 700  |

|        |         |               |        |       | 100,000    |      |

ISO 14644-1 (per cubic meter)

Fed Std. 209 E USA (per cubic foot)

ISO standard requires results to be shown in cubic meters (1 cubic meter = 35.314 cubic feet)[12]

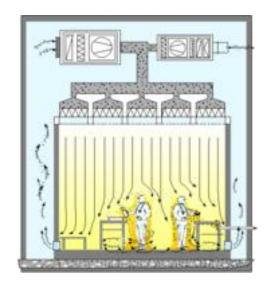

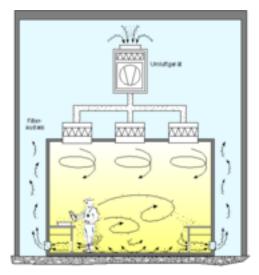

#### 3.1. Two air flow principles in cleanrooms:

Figure 4: Airflow pattern for "Turbulent Cleanroom"

Figure 4- 1: "Laminar Flow Cleanroom"[11]

The disparity of these two cleanrooms lies in the structure, the airflow behavior and the overall specifications. In turbulent cleanrooms the air is changed 85 times per hour whereas in laminar flow cleanrooms this happens 420 times per hour. In laminar flow cleanrooms the range of overpressure, humidity and temperature is lower and so higher classes (standards) are achieved. It is clear that humidity as well as temperature, have to be kept constant all the time. Only very little deviations are allowed, otherwise higher failure rates would occur.

#### 3.2. Cleanrooms in Semiconductor Manufacturing

All devices that are built on a chip are microscopically small. The components can be compared with tiny freeways where electricity either flows or does not flow. That is the reason why they are called semiconductors. Through these networks a microchip has the ability to accomplish the required functions and controls.

The small size of devices is the reason that some requirements have to be respected while working on wafers. The most important request is an artificial environment called cleanroom. Even the smallest pollution can cause a very hard damage of the device. For keeping the air as clean as

possible in these surroundings, it is sent through filtration plants. Both, the fresh and the circulating air are filtered to keep the contamination of the wafer as small as possible. One of the biggest problems in such cleanrooms is the worker. Each human being carries many particles. The first suggestion for avoiding the contamination by workers would be to automate the whole process, which is not possible because of the high complexity. Therefore, every employee must wear a so-called cleanroom-overall, a facemask and gloves.

The number of particles which are allowed in a production facility differs and the above-mentioned classifications are used as a guideline.

There exist two different types of contamination: chemical (fingerprints, sweat, and fat) and mechanical contamination (dust of machines, space components)[30]

After a short explanation of cleanrooms in semiconductor manufacturing the next chapter casts an eye at the basic materials used during the production process.

#### 4. Basic Materials in Semiconductor Manufacturing

To produce an engine control out of a grain of sand is a very complex subject. Before starting the production the basic material, called monocrystalline silicon, is needed. This required chemical element does not exist in nature; but many chemical bonds with silicon are detected. The most common form is SiO<sub>2</sub> which is the basic for pure silicon[30]

#### 4.1. Basic Elements used

#### 4.1.1. Silicon

As mentioned before silicon Si is the most common basic building block of integrated circuits in semiconductor manufacturing. This element either conducts or insulates electricity; therefore silicon is a semiconductor at room temperature. For building p-n junctions on silicon dopant elements are needed. After adding these, electrical components and ICs can be built from these junctions.

"Silicon is obtained by heating silicon dioxide (SiO<sub>2</sub>), or silica, with a reducing agent in a furnace. Silicon dioxide is the main component of ordinary sand." [45]

#### 4.1.2. Aluminum

Aluminum is used very often in semiconductor manufacturing. Metal lines are the conductors between the different components. It shows a good adherence to silicon, applied as a thin film. Wire bonding integrated circuits in ceramic packages is another usage of aluminum in semiconductor manufacturing.

#### 4.1.3. Gold

"A good conductor of heat and electricity, it is also the most malleable and ductile of all metals."

The main use of gold in semiconductor manufacturing is in the assembly, packaging process and wire bonding. Most commonly gold is used as wires for the connection of the IC to the leads of the package. The benefit of gold is that wires are resistant to wire breaking during the encapsulation process.

#### 4.1.4. Silver

It is also a very good conductor of heat and electricity. Silver is used like gold in the assembly and packaging processes. It prevents plastic packages from chemical degradation.

#### 4.1.5. Copper

Copper is a good conductor of heat, less efficient than silver but better than gold. It is used in assembly. Most of the lead frames for plastic packages are made out of copper. In semiconductor devices copper is applied as metal lines[45]

The following chapter deals with different procedures in semiconductor manufacturing, namely job shop, flow shop and the reentrant flow.

# Scheduling Procedures in Semiconductor Manufacturing

In semiconductor manufacturing many different approaches are used to create a machine plan for the next periods. Three of the scheduling procedures will be explained, first theoretically and in a special case in one of the following chapters.

Scheduling deals with the chronology allocating of jobs to machines and vice versa with respect to different goals and restrictions. At every time, one machine can only work on a single job and each job can be processed by a single machine[51]

#### 5.1. Flow Shop

Only once each job has to be processed precisely on each machine and the machine order is fixed. Every job has to be processed in the same order.

#### 5.1.1. Permutation Flow Shop

A permutation flow shop includes another important rule. A restriction on overtaking must be considered. The job order on the machines remains the same for all jobs. A convenient permutation of the jobs must be determined.

#### 5.2. Job Shop

Each job of such a problem has a given order. The machine orders of different jobs vary from each other but they are fixed in advance. Most of the time, each job must be processed exactly once on each machine[52] In semiconductor manufacturing job shops are more likely to be found because different products have different machine orders.

#### 5.3. Re-entrant Flow

Another difficult point in semiconductor manufacturing relate to the fact that wafers have to be processed more than once on each machine.

"Most manufacturing systems do not have the same work piece revisiting the same equipment except for rework. In semiconductor manufacturing, recirculation is the essence of the system. Semiconductor devices are layered structures in which each layer is produced in essentially same manner, with some variations to deal with differing materials introduced, or accuracy required."

Some of the lots will return to the same machine in a cyclic manner which causes unusual outcomes on one hand and provides an opportunity for production control on the other hand. The degree and impact of the reentrant flow in semiconductor manufacturing is much higher than in any other industry[26]

The following chapter shows the general structure of a so-called wafer fab.

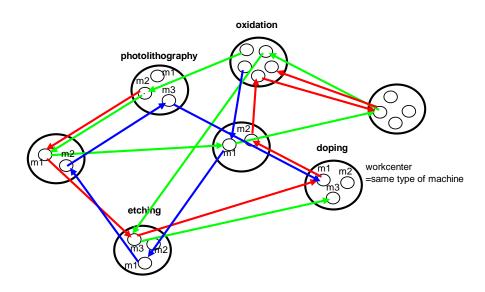

#### 6. Structure of a Wafer Fab

In so-called semiconductor fabs wafers are produced. On each semiconductor wafer there are either logic chips (integrated circuits) or memory chips (DRAMs) located. For the production the difference is very important, because the variety of products affects the logistical requirements.

Because of the hundreds of different work plans, mass production cannot yet be realized in semiconductor manufacturing. It is very important to place as many types of equipment as possible in a small room in wafer fabs to obtain the work environment. Therefore, shop fabrication is the leading layout for wafer fabs. That means that the equipment is the influencing variable for the fab layout. Machines are pooled together in modules, with regard to the processes they are implementing. This production flow is also called farm-layout. In semiconductor manufacturing machines, that are grouped together, because they are exactly the same, are called work centers[35]

Figure 5: NASA's Glenn research centre cleanroom[62]

Since the workflow does not play any role in layout planning, lots might travel long distances when changing the equipment. As mentioned before, wafers are produced using the so-called re-entrant flow and so the way of transportation might be very long and this may cause a big loss of time.

Operators play a significant role in semiconductor manufacturing. The automation in the logic chip field stands on a low level. It is not possible to install equipment that accomplishes to produce all the different product variations. Therefore, the operator has to transport the lots, load in and unload the machinery, correct disruptions, adjust parameters and load in new process programs. In order to know when an operator has to perform which step of the production plan, a so-called lot traveler is added to each lot. On this protocol, each step is recorded and all parameters are listed. As the semiconductor manufacturing takes place in a paperless fab, communication between the operators is not that necessary. Paperless fab means that all the information about a lot has already been sent to the machines and is available in the computer system. Even the route of transportation is fixed. One reason for inefficient performance can be the fact that the process of manufacturing is preset. If anything unforeseen happens, it is very difficult to react and stay on schedule[30]

In order to recognize the complexity and diversity of the entire semiconductor manufacturing process in a wafer fab, the coming section should provide a deeper insight.

#### 7. The Manufacturing Process – Overview

For the production of semiconductors, the raw materials need to undergo many hundreds of different process steps operated through machines with state-to-art technologies which are presupposing a high level of accuracy. The manufacturing process is furthermore characterized through the necessity of returning to the same machines for a number of times at different stages of their fabrication[2] Due to this complexity and the throughput of nearly thousands of production centers, the underlying progress is considered as one of the most difficult manufacturing processes in today's life[5]

In general, there is a coarse separation of the whole production progress: the front-end and the back-end part. The first fraction called front-end is responsible for the complete transformation of the raw material to the semiconductor substrate until the wafer probe where the selection of detective wafers occurs. Especially the wafer fabrication is the most complex and therefore also most cost-intensive part of the whole manufacturing process. Whereat the back-end production consists of assembling the completed semiconductors and additionally executes a final testing[27][35]

Since the manufacturing process of semiconductors is subjected to great complexity a successive production would make it rather impossible to generate a maximum throughput of finished microchips. Hence, depending on the diameter of a silicon wafer nearly thousands of identical circuit patterns or microchips, established of 25 different layers can be arranged on only one single semiconductor substrate[27]

Within a semiconductor plant, also known as a fab, the transportation of wafers is organized in lots. About 25 wafers (sometimes can also have a size of 50 wafers) are merged to one lot and several lots are integrated in one box while they are transported and traversing the route of production. For several production steps like processes in furnaces, the transportation and the processing can be abstracted in greater units like so called

batches. This supports the intra-plant logistic chain but also abbreviates the total throughput flow. As aforementioned, wafers are composed of 25 several layers with distinctive layer structures. This variety of layers is responsible for the fabrication of a circuit, which is the essential part of a finished semiconductor. Thus to the differences of the raw materials (silicon, gallium, gallium arsenide) layers may exhibit distinctions in their electrical conductivity and hence in their quality. Due to the production of the different layer surfaces a plurality of machines that possesses high modern technologies is essential. During the entire manufacturing process, a number of different products is fabricated and thus every product requires a certain production plan that dedicates a distinct route through the fab. According to the diversity of the product mix, it needs to be taken into account that set-uptimes and costs are occurring. The sequence of the production steps diversifies from product to product[35] The figure stated below should give a generic survey of the entire semiconductor manufacturing process.

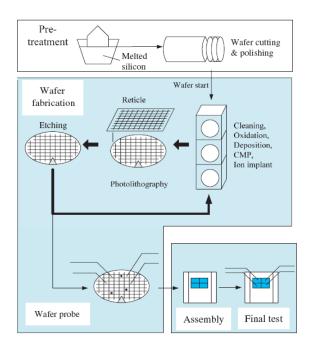

Figure 6: generic survey of semiconductor manufacturing process[27]

The whole production process consists of the following major procedures:

- Oxidation

- Photo Lithography

- Etching

- Doping/Ion implantation

- Anneal (heat treatment)[2]

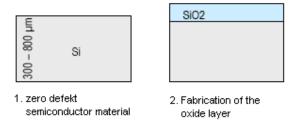

In order to initiate the entire production process, raw silicon wafers are fabricated from silicon ingots. The ingot is first shaped and afterwards trenched into very thin wafers[45] In the first processing step, an oxide layer will be placed upon the raw silicon wafers surface through the exposure in a furnace. This first layer operates like a certain pattern thus forces the further treatment of the underlying material. Furthermore, a photosensitive film (photo-resist layer) will be deposited on the oxide layer and subsequent this layer is exposed with ultraviolet light through a resolution patterned mask. For these parts on the layer, which were exposed to the ultraviolet light, are now undergoing a transformation and these areas can be processed with a chemical solvent, a so called developer. After this procedure there exist only the unexposed parts of the photo resist. An etching process enables the translation of the generated pattern to the oxide surface beneath. Further processing steps like doping enable to diversify the remaining oxide layer in its structure and characteristics. Through the displacement of the pattern the application of the first layer is completed[35]

Figure 7: Fabrication of a single layer[35]

Figure 7- 1: Fabrication of a single layer[35]

# 7.1 Processing steps in detail

The previous chapter displayed the complexity of the entire manufacturing process in general as well as the application of solely one layer on a silicon raw wafer. As aforementioned, the fabrication of merely one layer is necessitating a number of distinct procedures. However, for the production of a complete integrated circuit a diversity of special layers is required. Thus the following section should give a deeper insight in the procedures a raw wafer traverses during its transformation to a semiconductor integrated circuit.

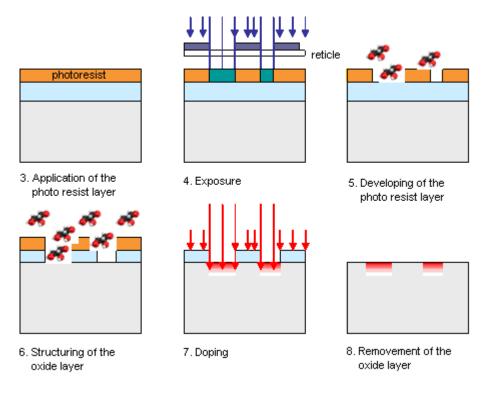

#### 7.1.1 Oxidation

As mentioned above, a multitude of diverse layers is fundamental to generate an integrated circuit. The great number of different layers is the essential part for the further generation of distinct structures and patterns on a wafer through the photolithography. The different fabricated layers obtain certain functions, for instance for isolation, ion implant, planarization, diffusion, as an alignable mark or for protection.

Prior cleaning the raw wafer and thus the removal of eventual contamination needs to be achieved. In order to gain a disposition for the raw wafer, a procedure called oxidation is performed. This chemical reaction occurs through the compound of the raw material silicon Si and the exposure to oxide O<sub>2</sub>. This generated silicon dioxide SiO<sub>2</sub> enables a very fine and evenly application of layers and is used furthermore to cover the wafer with the initial layer. Through this layer, the wafer substrate obtains certain resilience and can only be processed with hydrofluoric acid. Further substances like water or other acids cannot corrode the wafer's surface.

In course of this thermal oxidation the silicon raw wafer is transferred into a furnace which is heated with approximately 1000 °C. Subsequent gaseous oxide is admitted and owing to the reaction of the silicon raw wafer and the gaseous oxide silicon dioxide is generated upon the surface[54]

Figure 8: Demonstration of a furnace for oxidation[54]

The thermal oxidation differentiates between

- Dry oxidation

- Humid oxidation

- Wet oxidation

- H<sub>2</sub>O<sub>2</sub> burning

Dry oxidation only takes place in a pure oxide atmosphere, whereas wet oxidation also disposes water in the element of water vapor. Dry oxidation is basically characterized through a rather steady growing oxide but with a great tightness. However, wet oxidation displays high growth of oxide already at low rate of temperature but with minor quality. H<sub>2</sub>O<sub>2</sub> burning

utilizes besides pure oxide also pure hydrogen. Equal to the wet oxidation,  $H_2O_2$  burning characterizes through its rapid growth of oxide layers with hardly any contamination. At a rather low level of temperature as well as fine and thick layers are fabricated.

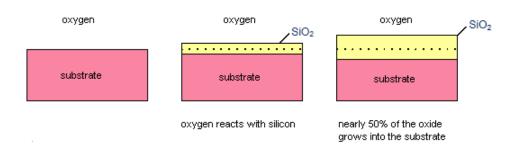

Initially oxide reacts with the silicon surface of the wafer and thus constitutes a silicon dioxide layer. In order to obtain a reaction of the oxide with the silicon, diffusion occurs. The oxide grows with approximately 50% into the silicon dioxide wafer substrate[54]

Figure 9: growth behavior of oxide on silicon[54]

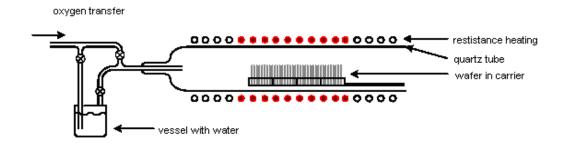

# 7.1.2 Photolithography

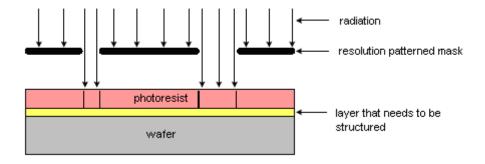

The photolithography is seen as the operation that necessitates the greatest accuracy and is also subjected to an enormous complexity. Due to the photolithography, the wafer obtains its certain structure and pattern. Based on the prior generated oxide layer, a radiation-sensitive liquid is deposited onto the wafer, a so-called photoresist. Subsequently a very high resolution patterned mask is utilized in order to fabricate a certain pattern to the deposited photoresist. Furthermore, this wafer deposited now with the oxide layer and the photoresist, is exposed to ultraviolet light. Through a chemical solvent the exposed parts are developed. The remaining unexposed as well as the exposed fragments is forming now the fundamental pattern of the circuit achieved through the extern reticle. Due to the etching operation, the reticle is translated to the underlying silicon dioxide layer[53]

Figure 10: Transmission of the pattern on the oxide layer[54]

Owing to the requirement of a plurality of distinct layers also a magnitude of diverse reticles is necessary in order to obtain certain structures on the integrated circuit. As a guideline for the enormous amount of various masks it can be said that about 400 different types of integrated circuits require approximately 40.000 different reticles. Due to the fact that an integrated circuit contains of a magnitude of diverse layers, the photolithography as well as the oxidation operation need to be traversed approximately 30 times during the entire manufacturing process[35]

Owing to this essential fact, it is crucial that this operation is not starving a failure. Otherwise the total fabrication will be down and this will cause an enormous financial loss to the company.

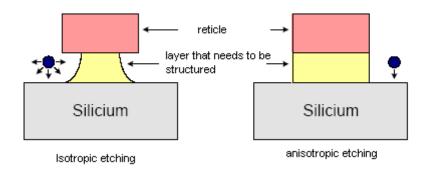

# 7.1.3 Etching

Etching is essential either for the removal of an entire layer or for the transmission of a structured photoresist layer to the beneath surface through the operation of photolithography. The etching operation is differentiated in wet-chemical and dry etching. Furthermore, there is a distinction between isotropic and anisotropic etching procedures. An isotropic operation is mainly characterized through its freedom of etching. It may occur as well as horizontal or vertical but also can diversify the layer in its size, whereas an anisotropic procedure is restricted to a solely upright direction. Therefore, undercuts are unfeasible and etching the underlying surface occurs along the previous pattern[48]

Figure 11: isotropic and anisotropic etching[48]

A further crucial factor in etching is the selectivity. Selectivity in this context is stated as the proportion by the removal of the layer that need to be structured and therefore etched and the removal of other layers. If the selectivity is quoted as 2:1 that implies that the oxide layer is etched twice as fast as the underlying layer. In order to spare the subjacent layer from further etching, the layer, which needs to be diversified, exhibits a great selectivity[48]

As aforementioned, there is the distinction among wet-chemical and dry etching. Wet-chemical etching is characterized through the conversion of the fixed layer into a liquid by the use of chemical solvents. This approach obtains a high selectivity thus to the fact that the chemical solvent can be deposited very precise onto the removable layer. For many solvents the selectivity accounts the proportion of 100:1. In this approach the abrasive occurs mainly isotropic while especially for extremely fine layers an anisotropic etching is recommendable. The method of dry etching is advantageous for exactly such situations. Besides a sufficient selectivity, this approach also exhibits the option of isotropic and anisotropic operations[65]

In order to fabricate integrated circuits it is furthermore essential to satisfy the conductivity requirements. The method of doping enables to enhance the conductivity of a semiconductor[30]

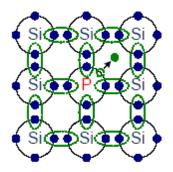

## 7.1.4 Doping

Doping is known as the implementation of external atoms into a chip in order to enhance its electrical properties. Through this insertion, it is possible to manipulate certain parts of the wafers conductivity. The selected impurities are introduced into the monocrystalline grid and through this procedure; the chips conductivity can be enhanced by a factor of 10<sup>6</sup>. It will be distinguished among the n-doping and the p-doping. The amount of external electrons is essential for the type of doping. The two main elements in order to perform doping are Boron and Phosphor. Boron consists of 3 valence electrons and is therefore responsible for the p-type doping, whereas Phosphor inhabits 5 electrons and thus accountable for the n-type doping[22]

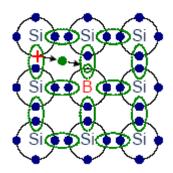

## 7.1.4.1 n-type Doping

As the silicon wafer possesses solely 4 valence electrons, the fifth electron provides as a charge carrier and can move freely in the lattice. This remaining valence electron needs significant less energy in order to be moved into the conduction band compared to the other electrons that are accountable for the intrinsic conductivity. The doping element Phosphor receives a positive charge through the emission of negative charge carriers and is permanent integrated into the grid, only the electrons are roaming freely. Doping is denoted as n-type doping owing to the generation of conductivity through negative free moving electrons. They also are named the majority charge carriers because of their surplus of free electrons[22]

Figure 12: n-doping[22]

## 7.1.4.2 p-type doping

Exactly the counterpart occurs at the p-type doping. There are no valence electrons that can roam freely, contrariwise the doping element Boron consists solely of 3 valence electrons and therefore leaves a gap in the valence band of the lattice. Due to this now generated gap, the electrons can roam in the valence band. But the movement of the gaps occurs in the reverse direction to the electron flow. The doping element Boron is charged negatively through the insertion of an electron. As seen before, the doping element is bounded into the lattice and only the positive charge is roaming. This doping is named p-type doping due to the generation of conductivity through positively charged gaps. On the contrary to the n-type doping, freely moving gaps are now available in a greater amount and thus are called the majority charge carriers. The denomination of n-type or p-type doping conforms to the majority charge carriers[22]

Figure 13: p-doping[22]

## 7.1.5 Ion implantation and annealing

The most important method as to doping is the ion implantation. This process implies the direct bombardment of the underlying wafer with high energy ions. Due to the advantage of high precision for depositing dopant atoms onto the wafer substrate, ion implantation replaced the thermal diffusion. Ion implantation as a method of doping is accountable for the diversion of the type and level of conductivity of semiconductor materials. During the process of ion implantation, atoms of impurity are vaporized and accelerated onto the silicon substrate. The atoms are now inserting the crystal lattice and are forfeiting their energy due to collidings with the

existing silicon atoms until the impurity atoms are located at some place in the crystal lattice. Through heat treatment, the lattice dysfunctions, resulting through the collidings of atoms, are mended and rebuilt. The collidings of atoms and thus the generated disturbances are accountable for the alteration of the electronic characteristics of the silicon wafer. Through the procedure of annealing, the lattice defects are repaired. This process, however, is also essential for the positioning of dopant atoms in order to guarantee the electrical activity[45]

## 7.1.6 Cleaning treatments and testing

The entire manufacturing process necessitates a high level of accuracy and purity. Already very small amounts of particle or other forms of contamination can destroy the whole wafer production. In order to maintain purity of the wafers during the throughput of the production chain, several cleaning procedures are integrated so as to retain a high qualitative final product. Before the completed circuits are assembled and delivered, the finished semiconductors traverse a number of testing instances owing to separate defective semiconductors and inspect once more the qualitative requirements[30]

All displayed procedures are traversed a number of times during the entire production process. As it is one of the most complex processes in today's life, it requires a high level of coordination and also awareness of potentially appearing issues in order to generate a trouble free production chain.

# 8. Potentially occurring issues

The semiconductor process itself is subjected to tremendous complexity but a few crucial factors need to be recognized as well in order to generate an optimal production and capacity plan for a semiconductor fab.

Initially, it is important to become aware of the fact that the semiconductor manufacturing underlies quickly altering technical and social requirements. Semiconductor fabs need to cope with the demands of their costumers towards high qualitative, always innovative products but also to enhance their delivery times. As customers are mainly demanding more and more customized products, causing a great diversity of the product mix, this also implies an enormous challenge to plan a feasible production flow in a wafer fab. Additionally, technologies obsolesce rapidly and in order to keep up with the fast changes it is essential to develop continuously state-to-the art technologies[53] Nowadays, technologies and machines are facing more and more shortened life cycles, as an innovative technology might be out of date within a few months.

Furthermore, the wafer fab faces also the issue of the capital-intensive equipment and its lead-time. In order to detect breakdowns or disruptions of machines early enough, a good working shop floor control system needs to be implemented in every fab. Otherwise the entire production might be subjected to a shutdown and that implies an enormous financial loss due to the fact that the new tools underlie a lead-time of several months ahead. If an existing fab wants to expand its capacity, this process will take about nine months, whereas arranging a cleanroom would take nearly a year. For instance, a new fab is worth at least a billion and its incorporation time is about one year. Due to this vast capital amounts inside a semiconductor shop floor, the fab planners need to decide whether to expand the capacity based on the fact that forecasted demands are rather imprecisely or to keep machines with older technology in the production flow[27]

Another important factor in association with the semiconductor fabrication is the fact that the demand underlies a stochastic behavior. So the

requested quantity for the coming periods cannot be predicted exactly and therefore fab planners are subjected to volatile demand behavior and need to make decisions to whether expand their capacity through the utilization of old machines or through an order of innovative machines which necessitating several month to be delivered[27]

As production plans are subjected to the volatility of demand and capacity but as well as disruptions or starvations of machines, the underlying production and capacity planning needs to be adjusted more often in order not to suffer a breakdown of the entire production flow. Therefore, a rolling production planning seems to be an improved method to overcome eventual breakdowns and changes in demands. A rolling production plan implies that after a certain interval of time the already occurred planning for the further months will be recalculated and updated due to the current challenges in the shop floor.

All these possible issues refer to the parameter called uncertainty which is contemplated in a stochastic model. Therefore, the following section of this work is dealing with the specification of a deterministic, whereat all factors are conversant and a stochastic model. Furthermore, the work attempts to display a generic deterministic mathematical formulation for our manufacturing issue and give adjustments for a stochastic model.

## Deterministic and Stochastic Model Formulation

Due to the general description of the highly complex semiconductor manufacturing process, the objective is now to optimize the sequence of the processing steps by the means of two distinct subproblems: on the one hand the challenge of the material flow and on the other hand the product mix issue. Foremost, the thesis pays attention towards the generic formulation of deterministic and stochastic models. Further amplifications respectively the two subproblems will emphasize on the formulations of solely deterministic models.

The generic description of the deterministic model will be the first to be shown. Further, the stochastic model description is explained.

#### 9.1 Deterministic Basic Model

In general, a multi-period deterministic model describes a problem in which all of the different parameters are known in advance. For each period the profit, demand, supply, capacity, processing times, set-up times, wafers and the number of equal machines is given. In this case no uncertainty exists and therefore this kind of model is called deterministic.

Another characteristic of this model shows the fact that in different periods the amount of each parameter is different. That emphasizes the circumstance that the basic model can be defined as a dynamic deterministic multi-period model.

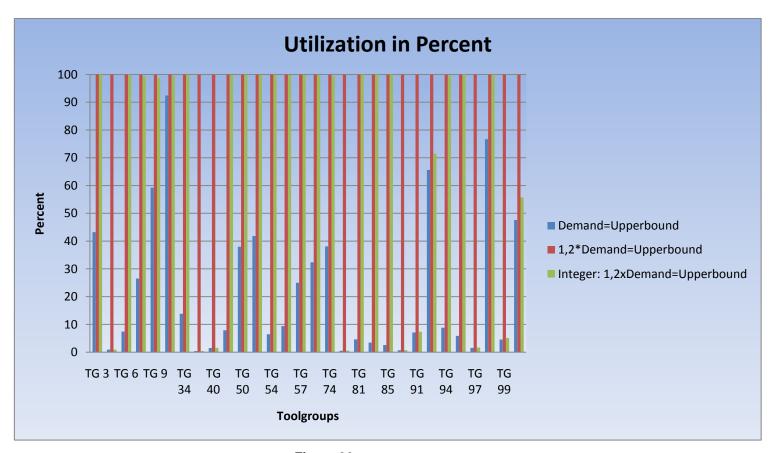

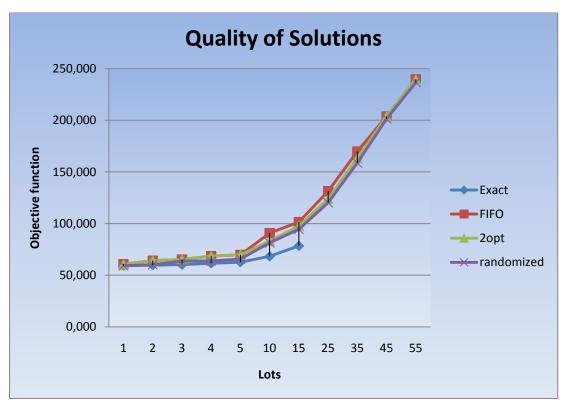

#### In other words: