# Power Constrained Test Scheduling in System-On-Chip Design

Liang Gao, B. Eng.

Submitted in fulfillment of the requirement for the degree of the M.Eng in Electronic Engineering

Supervisor: Dr. Xiaojun Wang

School of Electronic Engineering

Dublin City University

September 2004

# Approval

| Name:              | Liang Gao                                                     |

|--------------------|---------------------------------------------------------------|

| Degree:            | M. Eng.                                                       |

| Title of thesis:   | Power Constrained Test Scheduling in System-On<br>Chip Design |

| Examine Committee: | to be appointed, Dublin City University Chair                 |

|                    | Prof. Steve Grainger, Staffordshire                           |

|                    | University, External Examiner                                 |

|                    | Dr. Xiaojun Wang, Lecturer, Dublin City                       |

|                    | University, Internal Supervisor                               |

|                    | Dr. Sean Marlow, Senior Lecturer, Dublin City                 |

|                    | University, Internal Examiner                                 |

|                    |                                                               |

| Date Approved:     |                                                               |

## Declaration

I hereby certify that this material, which I now submit for assessment on the program of study leading to the award of M.Eng. is entirely my own work and has not been taken from the work of others save and to the extent that such work has been cited and acknowledged within the text of my work.

Signed: Liang Gao (Candidate)

ID No.: 50161539

Date: September 22, 2004

To my wife Yan

## Acknowledgements

My best acknowledgments go to

Dr. Xiaojun Wang for supervising my work and for valuable guidelines, and hints with much freedom, for many interesting discussions, patient correction, sharp criticism but also encouragement.

Valentin Muresan, Gabriel-Miro Muntean, Duro Todinca, Rosemary Kingston, Yongle Liu, and Gerald Considine for their friendly assistance on numerous occasions.

All the colleagues in RINCE, DCU for providing a very friendly atmosphere to work with.

Finally I would appreciate God, who let me come to know that patience will finally bear fruit.

### **Abstract**

With the development of VLSI technologies, especially with the coming of deep sub-micron semiconductor process technologies, power dissipation becomes a critical factor that cannot be ignored either in normal operation or in test mode of digital systems. Test scheduling has to take into consideration of both test concurrency and power dissipation constraints. For satisfying high fault coverage goals with minimum test application time under certain power dissipation constraints, the testing of all components on the system should be performed in parallel as much as possible.

The main objective of this thesis is to address the test-scheduling problem faced by SOC designers at system level. Through the analysis of several existing scheduling approaches, we enlarge the basis that current approaches based on to minimize test application time and propose an efficient and integrated technique for the test scheduling of SOCs under power-constraint. The proposed merging approach is based on a tree growing technique and can be used to overlay the block-test sessions in order to reduce further test application time. A number of experiments, based on academic benchmarks and industrial designs, have been carried out to demonstrate the usefulness and efficiency of the proposed approaches.

# List of Acronyms

| ALU Arithmetical Logic Unit                    |

|------------------------------------------------|

| APD Average Power Dissipation                  |

| ASIC Application Specific Integrated Circuit   |

| AT Automatic Test                              |

| ATE Automatic Test Equipment                   |

| ATPG Automatic Test Pattern Generation         |

| BILBO Built-In Logic-Block Observer            |

| BISTBuilt-In Self-Test                         |

| BSBoundary Scan                                |

| BSR Boundary Scan Ring                         |

| BT Block Test                                  |

| BTS Block Test Scheduling                      |

| BUT Block Under Test                           |

| CBILBOConcurrent Built-In Logic-Block Observer |

| CBSOC Core-Based System-on-Chip                |

| CMOS Complementary Metal-Oxide Semiconductor   |

| CPUCentral Processing Unit                     |

| CPUT Central Processing Unit Time              |

| CTD Compressed Test Data                       |

| CTLCore Test Language                          |

| CTS Concurrent Test Set                        |

| СТТ  | Core Testing Techniques            |

|------|------------------------------------|

| CUT  | Circuit Under Test                 |

| DFT  | Design for Testability             |

| DRAM | Dynamic Random Access Memory       |

| DS   | Digital System                     |

| DV   | Digital Verification               |

| DSP  | Digital Signal Processor           |

| ECT  | Extended Compatibility Tree        |

| EMC  | Extended Main Clique               |

| ЕТВ  | Expandable Tree Branch             |

| FPGA | Field Programmable Gate Array      |

| GA   | Genetic Algorithm                  |

| HLLS | High Level Low-Power Synthesis     |

| HLS  | High-Level Synthesis               |

| HLTS | High-Level Test Synthesis          |

| IC   | Integrated Circuits                |

| IP   | Intellectual Properties            |

| ILP  | Integer Linear Programming         |

| I/O  | Input/Output                       |

| JTAG | Joint Test Action Group            |

| LFSR | Linear Feedback Shift Register     |

| LSI  | Large Scale Integration            |

| MA   | Merging Approach                   |

| MCM  | .Multi-chip Module                 |

| MILP | Mixed Integer Linear Programming   |

| MISR | .Multiple Input Signature Register |

| MPCS | .Maximum Power Compatible Set      |

| MT   | Macro Test                         |

| . Non-deterministic Polynomial          |

|-----------------------------------------|

| . Power Compatible List                 |

| . Power Compatible Set                  |

| . Power Dissipation                     |

| Power-Constrained Block-Test Scheduling |

| Reduced Instruction Set Computer        |

| .Root Mean Square                       |

| . Register Transfer                     |

| . Register Transfer Level               |

| . Simulated Annealing                   |

| .System on Chip                         |

| .Test Application Time                  |

| .Test Compatibility Graph               |

| Testable Design Methodology             |

| Test Incompatibility Graph              |

| Test Length                             |

| Test Parallelism                        |

| . Test Pattern Generation               |

| Tabu Search                             |

| Traveling Sales Person                  |

| . Test Time Reduction                   |

| . Total Test Time                       |

| Very Large Scale Integration            |

|                                         |

# List of Tables

| Table 1.1 Level of abstraction in information              |    |

|------------------------------------------------------------|----|

| processing by a digital system                             | 3  |

| Table 5.1 Experimental results on Muresan's Design One     | 69 |

| Table 5.2 Experimental results on Design by Kime           | 71 |

| Table 5.3 A comparison of different test                   |    |

| schedule approaches on ASIC Z                              | 73 |

| Table 5.4 Experimental results on System L                 | 75 |

| Table 5.5 Experimental results on ASIC Z Design Two        | 78 |

| Table 5.6 Experimental results on Two Muresan's Design Two | 80 |

# List of Figures

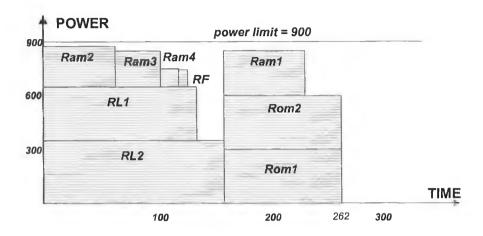

| Figure 1.1 | An Example of SOC2                                     |

|------------|--------------------------------------------------------|

| Figure 1.2 | A typical High-Level Synthesis (HLS) System 6          |

|            |                                                        |

| Figure 3.1 | First Example of Node Under Test                       |

| Figure 3.2 | A General Hierarchical Test Structure23                |

| Figure 3.3 | Power Dissipation as a Function of Time35              |

| Figure 3.4 | Merging Step Example38                                 |

| Figure 3.5 | Test Scheduling Chart and ECT Example40                |

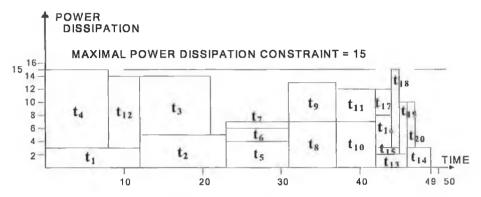

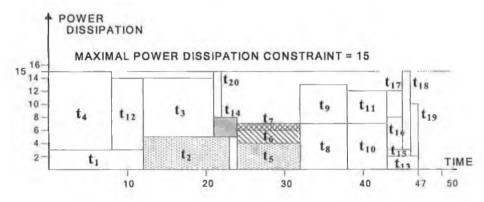

| Figure 3.6 | An Example of PTS Chart of 20 Tests                    |

| ,          | with Power Dissipation Constraint (PTC)41              |

|            |                                                        |

| Figure 4.1 | An Example of Acceptable Overlap of                    |

|            | Tests by Merging Approach44                            |

| Figure 4.2 | The Comparison of the Merging Approach with            |

|            | Tree Growing Technique (Extended Compatibility Tree)45 |

| Figure 4.3 | EMC Test Length and the First Level Gap Length46       |

| Figure 4.4 | Equivalent Test Schedule in Merging Approach46         |

| Figure 4.5 | Power-Test Scheduling Result by ECT Approach55         |

| Figure 4.6 | Test Compatibility List of 10 Tests56                  |

| Figure 4.7 | Tree Growing Steps Example58                           |

| Figure 4.8 Merging Result Followed by EMC                     |

|---------------------------------------------------------------|

| Approach to 10 Tests60                                        |

| Figure 4.9 Merging Steps of the Example62                     |

|                                                               |

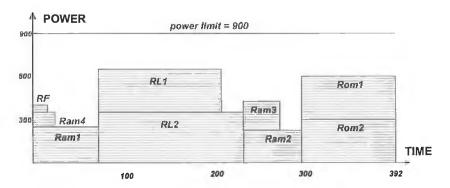

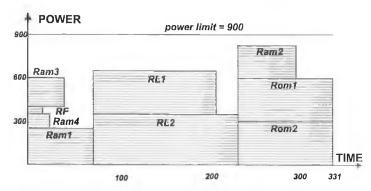

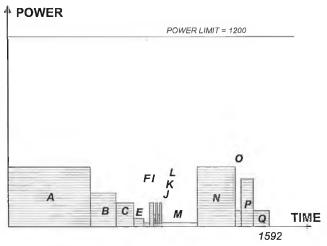

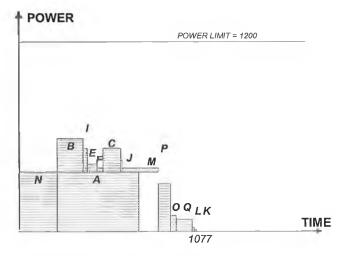

| Figure 5.1 Test Schedule Produced by                          |

| Muresan's Approach on Design One67                            |

| Figure 5.2 Test Schedule Produced by Erik's Simulated         |

| Annealing Implementation on Muresan's Design One67            |

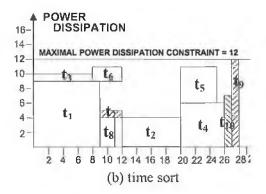

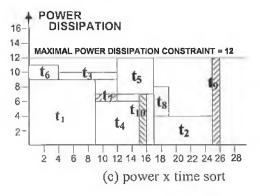

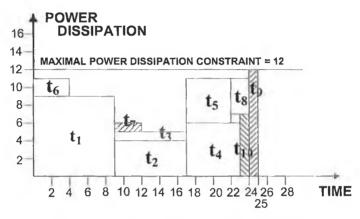

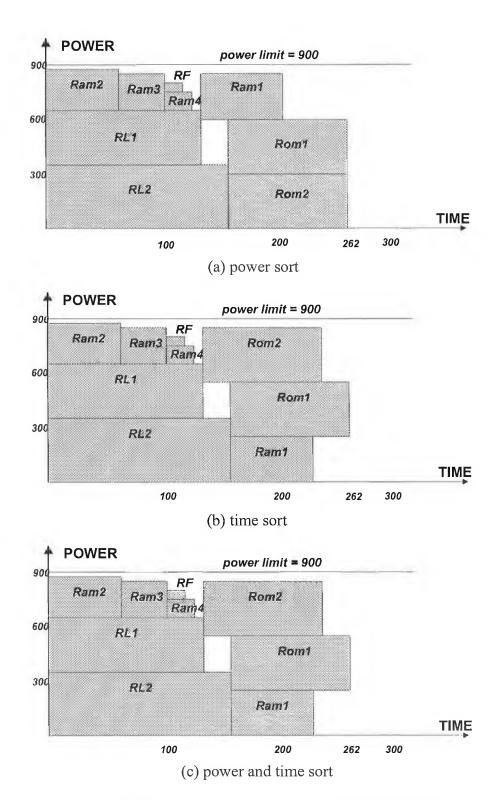

| Figure 5.3 Test Schedule using Erik's Approach with Initial   |

| Sorting based on (a) Power, (b) Time and                      |

| (c) Power x Time on Muresan's Design One68                    |

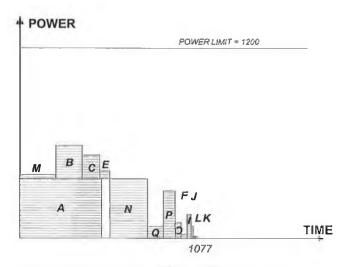

| Figure 5.4 Test Schedule using Merging Approach on            |

| Muresan's Design One69                                        |

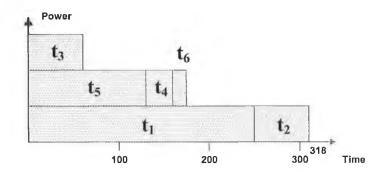

| Figure 5.5 Test Schedule using Merging Approach on Design     |

| Kime (no power dissipation constraint)70                      |

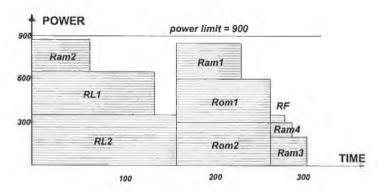

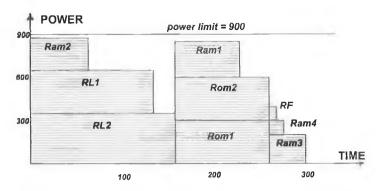

| Figure 5.6 Test Schedules Generated using Zorian's Approach71 |

| Figure 5.7 Test Schedules Generated using Chou's Approach     |

| Figure 5.8 Test Schedules Generated using Erik's Approach     |

| Figure 5.9 Test Schedules Achieved using Merging Approach     |

| Figure 5.10 Designer's Test Schedule on System L74            |

| Figure 5.11 Test Schedules Achieved using Erik's Heuristic    |

| with Sorting Based on Power on System L74                     |

| Figure 5.12 Test Schedules Achieved using Our                 |

| Heuristic on System L75                                       |

| Figure 5.13 Test Schedules Achieved using Erik's Heuristic    |

| on ASIC Z Design Two using Initial Sorting Based on           |

| Based on (a) Power, (b) Time and (c) Power x time             |

| Figure 5.14 Test Schedules Achieved using Merging Approach |                                          |   |

|------------------------------------------------------------|------------------------------------------|---|

|                                                            | on ASIC Z Design Two7                    | 8 |

| Figure 5.15                                                | Test Schedule Produced by Muresan et al. |   |

|                                                            | on Muresan's Design Two7                 | 9 |

| Figure 5.16                                                | Test Schedule using Merging Approach     |   |

|                                                            | on Muresan's Design Two7                 | 9 |

# Contents

| $\mathbf{A}_{\parallel}$ | pproval     |                                        | II  |

|--------------------------|-------------|----------------------------------------|-----|

| D                        | eclaration. |                                        | III |

| A                        | cknowledg   | gments                                 | V   |

| A                        | bstract     |                                        | VI  |

| Li                       | st of Acr   | onyms                                  | VII |

| Li                       | ist of Tab  | les                                    | X   |

| Li                       | ist of Figu | res                                    | XI  |

| C                        | ontents     |                                        | XIV |

|                          |             |                                        |     |

| 1                        | Introdu     | ction                                  | 1   |

|                          | 1.1 Thes    | is Scope                               | 1   |

|                          | 1.1.1       | What is SOC                            | 1   |

|                          | 1.1.2       | Digital System Testing                 | 3   |

|                          | 1.1.3       | Testable Design                        | 4   |

|                          | 1.1.4       | Low-Power Design for Test              | 5   |

|                          | 1.1.5       | High-Level Synthesis                   | 5   |

|                          | 1.1.6       | Test Parallelism and Power Constraints | 7   |

|                          | 1.1.7       | Power-Constrained Test Scheduling      | 7   |

|                          | 1.2 Thes    | is Overview                            | 8   |

|                          |             |                                        |     |

| 2                        | Rackar      | cound                                  | 9   |

|   | 2.1 Intro | duction                                       | 9  |

|---|-----------|-----------------------------------------------|----|

|   | 2.2 Desig | gn for Testability (DFT)                      | 9  |

|   | 2.3 High- | -Level Test Synthesis                         | 11 |

|   | 2.4 High  | -Level Low-Power Synthesis                    | 13 |

|   | 2.5 Test  | Parallelism and Test Time Reduction           | 15 |

|   | 2.6 Test  | Scheduling Heuristics                         | 16 |

|   | 2.6.1     | Simulated Annealing.                          | 16 |

|   | 2.6.2     | Tabu Search                                   | 17 |

|   |           |                                               |    |

| 3 | Power-C   | Constrained Test Scheduling Problem           | 19 |

|   | 3.1 Syste | m Testing                                     | 21 |

|   | 3.1.1     | Core Testing                                  | 22 |

|   | 3.1.2     | Core Testing Scheduling                       | 24 |

|   | 3.2 Power | er-Conscious Test Parallelism                 | 26 |

|   | 3.2.1     | Power Minimization During Test Application    | 27 |

|   | 3.2.2     | Power-Constraint Test Scheduling              | 31 |

|   | 3.3 PTS   | Problem Modeling                              | 34 |

|   | 3.3.1     | System Modeling                               | 34 |

|   | 3.3.2     | High-Level Power Dissipation Estimation       | 34 |

|   | 3.3.3     | PTS Problem Formulation                       | 37 |

|   | 3.3.4     | The Tree Growing Technique                    | 37 |

|   | 3.3.5     | Power-Test Scheduling Chart                   | 40 |

|   |           |                                               |    |

| 4 | Merging   | g Approach Based On Tree Growing Technique    | 42 |

|   | 4.1 Intro | duction                                       | 42 |

|   | 4.2 Exist | ing Test Scheduling Techniques                | 42 |

|   | 4.3 Merg  | ging Approach Based On Tree Growing Technique | 44 |

|   | 4.3.1     | Operating Procedures                          | 45 |

| 4.3.2 Algorithm Pseudocode48              |

|-------------------------------------------|

| 4.3.3 Algorithm Complexity54              |

| 4.3.4 Test Scheduling Example54           |

| 4.4 Conclusions65                         |

|                                           |

| 5 Experimental Results66                  |

| 5.1 Experiments on Muresan's Design One   |

| 5.2 Experiments on Design by Kime70       |

| 5.3 Experiments on ASIC Z Design One71    |

| 5.4 Experiments on System L74             |

| 5.5 Experiments on ASIC Z Design Two76    |

| 5.6 Experiments on Muresan's Design Two79 |

|                                           |

| 6 Conclusions and Future Work81           |

| 6.1 Thesis Summary81                      |

| 6.2 Contributions83                       |

| 6.3 Future Work83                         |

|                                           |

| Bibliography84                            |

| Appendix A: Benchmark ExamplesA           |

| A.1 Muresan's Design One                  |

| A.2 Design by KimeB                       |

| A.3 ASIC Z Design OneC                    |

| A.4 System LD                             |

| A5 ASIC Z Design TwoE                     |

| A6 Muresan's Design TwoF                  |

| Appendix B: Publication                   |

# Chapter 1 Introduction

### 1.1 Thesis Scope

#### 1.1.1 What is SOC

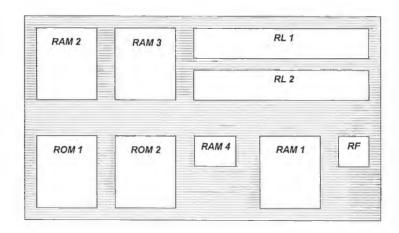

The rapid development of semi-conductor technology, especially the deep sub-micron process technology, has lead to the implementation of system-on chip (SOC). Manufacturers are integrating increasing numbers of components on one chip. Usually, as a complete system, a SOC includes multiple types of circuitry, such as several Application Specific Integrated Circuits (ASIC), memories, microprocessor, and intellectual property (IP) blocks. Typically, SOCs are designed using embedded reusable cores. An example of SOC is shown in Figure 1.1.

Embedded reusable cores make it easier to import technology to a new digital system and differentiate the corresponding product by leveraging intellectual property advantages. Furthermore, the use of embedded cores shortens the time-to-market for new digital systems through design reuse.

#### 1.1.2 Digital System Testing

Testing of a system is a process in which the Digital System (DS) is run and its resulting response is analyzed to ascertain whether it behaved correctly. The complexity of a circuit relates to the level of abstraction. The level of abstraction relating to information processing on a digital system, can be briefly characterized as that shown in Table 1.1

| Control                       | Data            | Level of abstraction  |

|-------------------------------|-----------------|-----------------------|

| Logic value                   |                 | Logic level           |

| (or sequence of logic values) |                 |                       |

| Logic value                   | Words           | Register level        |

| Ins                           | Words           | Instruction set level |

| Programs                      | Data structures | Processor level       |

| Messages                      |                 | System level          |

**Table 1.1:** Level of abstraction in information processing on a digital system.

A complex circuit is usually regarded as a System because it becomes unmanageable or meaningless for us to consider circuit operations only in terms of processing logic values. A system usually comprises two sections-Data and Control.

Testing involves the activity, which aims at ascertaining design errors and physical faults. Sometimes, the testing of design errors is called Design Verification. Several examples of design errors are, incomplete or inconsistent specifications, incorrect mapping between different levels of design, and conflicts of design rules. Physical faults comprise fabrication errors,

fabrication defects and physical failures [Abr94]. A number of examples of physical faults are:

- Wrong components

- Incorrect wiring

- Shorts caused by improper soldering

#### 1.1.3 Testable Design

With the increasing complexity of digital systems, testing becomes more and more important. Test Processing affects the viability of the current semiconductor industry significantly. The cost of testing a digital system has become a major component in the cost of designing, manufacturing and maintaining. The cost of testing reflects many factors such as testing time, Automatic Test Equipment (ATE), etc.

Digital System design must take testability into consideration in addition to its functionality. In the other words, Digital System design must be testable. This is a fundamental concern to the successful implementation of a digital system design.

Examples that embody testable design criterion are the consideration of inserting test points, Built In Self Test circuitry (BIST), and scan chains. Another one is partitioning of large combinational circuits.

#### 1.1.4 Low-Power Design for Test

The principle of lower power seems to be the permanent objective of digital system design. Currently, it is the miniaturization of some communication and information processing products such as mobile phone

and portable computing products that prioritize the relevant research of low power design methodologies. The target of this research is to enhance the lifetime of mobile phone batteries. However, from a test point of view, low power techniques are more significant.

Digital systems designed with Design For Testability (DFT) considerations can operate in Normal Mode and Test Mode. As is commonly known, digital system devices running in Test Mode can consume more power than when running in Normal Mode [Zor93], it can cause excessive heat, and could destroy the device.

#### 1.1.5 High-Level Synthesis

Synthesis is usually defined as the translation of a behavioral representation of a design into a structural one [Ele98]. The whole synthesis process comprises several consecutive steps performed at different abstraction levels. Various basic implementation primitives are used and different synthesis methods are employed in the different steps. Usually Synthesis relates to system level, high level, logic level and physical design. In this thesis, the Synthesis refers to high-level synthesis only.

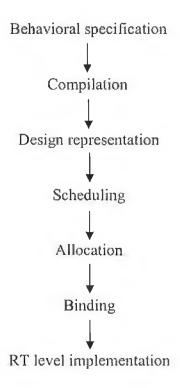

High-Level Synthesis (HLS) accepts a behavioral specification of a digital system and a set of objectives as inputs, an RT-level implementation is produced by HLS. A general high-level synthesis system comprises of five main steps: Compilation, High-level transformations, Scheduling, Allocation, and Binding. A typical HLS system is shown in Figure 1.2.

Figure 1.2: A typical High-Level Synthesis (HLS) System.

While the first objective of High-Level Test synthesis is to improve the testability of a design, other constraints, such as performance and area, are also satisfied.

#### 1.1.6 Test Parallelism and Power Constraints

Partitioning has been used widely. Partitioning is significantly important to reduce the number of actual combinational circuits for testing. The notion of Block-Tests (BT) has been brought into Digital System testing. The next problem is to determine the compatibility among the blocks. To reduce test application time, tests of blocks must be performed concurrently as far as possible. However, power constraints have to be considered to avoid chip

overheating and possible damage. Power constraints must be observed during test scheduling. Test Scheduling will be focused on in greater depth in this thesis.

#### 1.1.7 Power-Constrained Test Scheduling

In general, Operation Scheduling deals with the assignment of each operation to a time slot corresponding to a clock cycle or time interval.

Obviously, the main task for Test Scheduling is to minimize the Test Application Time (TAT), by ordering tests in an efficient schedule. Test Scheduling affects the concurrency of testing, therefore determines the parallelism of testing. The maximum number of simultaneous tests should be scheduled under power-dissipation constraint so as to benefit the minimization of TAT.

It is well known that TAT and power dissipation are two increasingly important issues. TAT affects the cost directly.

Since the problem of test scheduling is viewed as NP-Complete problem, the application of Heuristics is essential in Test Scheduling, which is the focus of this thesis.

#### 1.2 Thesis Overview

The overview of the thesis is briefly introduced here. The background of the topics dealt with in this thesis is included in the Second Chapter.

A Power-Constrained Block-Test Scheduling (PTS) problem will be formulated and modeled in the Third Chapter. Here the Test Scheduling issue will be discussed in detail. Relevant definitions and explanations of the terms used in this thesis will be described in this chapter.

A proposed novel Test Scheduling approach, named Merging Approach (MA) based on a tree growing technique, will be introduced in detail in Fourth Chapter, including the algorithm, the complexity analysis and an example of Test Scheduling using the proposed algorithm.

The experimental results will be presented in Chapter Five, including the comparison of experimental results of different Test Scheduling approaches.

The analysis of the advantages and disadvantages of the proposed approach in this thesis will be given in Chapter Six.

# Chapter 2 Background

#### 2.1 Introduction

In this chapter, a brief introduction to Block Test Scheduling (BTS) will be given. The following sections will cover the use of Design For Testability (DFT), High-Level Test Synthesis (HLTS), High-Level Low-Power Synthesis (HLLP), Test Parallelism (TP) and Test Time Reduction (TTR). The last section will cover several Heuristics approaches.

## 2.2 Design for Testability (DFT)

With the increasing complexity of digital systems, traditional methods of electronic device testing are becoming insufficient. The problem of testing digital systems has become more of a challenge.

Undoubtedly, economic considerations are at the heart of all testing problems [Wil94]. Testing application time cannot be too long; otherwise the relevant cost will increase rapidly, which is unacceptable. Because of this, Automatic Testing (AT) is an essential procedure for digital system

verification. This verification idea involves the use of Automatic Test Equipment (ATE).

In our context "Testing" means Digital System Testing (DST). Digital Systems are tested by applying a sequence of signals to their inputs and observing their outputs. If the input and output ports are directly accessible by the Test Equipment, they are called **primary inputs/outputs**. Otherwise, if they are directly inaccessible, they are called **component inputs/outputs**. According to output signals, identification is made to judge that the circuit is correct or not. The practical testing procedure depends on the method used. For example, it is unnecessary to get the observation of output ports for I<sub>ddq</sub> testing; instead the power supply current is monitored. Built-In Self-Test (BIST) method can be used to compress the outputs and provide only the test outcome in the form of a signature. However, an input pattern, generated based on a given fault model, is required by all methods. (Here, only the stuck-at fault model [Abr90] is considered which captures also many other faults.)

Obviously, the key problem of testing is the derivation of an adequate test set for a particular circuit. This process is known as Test Pattern Generation (TPG). TPG is automated using a computer and is called Automatic TPG (ATPG).

An exhaustive test is not practical for any non-trivial combination circuit, because of the exponential complexity.

Functional testing for blocks containing recognizable functions [Wil94] is used for testing a sequential circuit. A functional test strategy is also employed when testing Medium-Scale Integration (MSI) and Large-Scale Integration (LSI) devices especially where Microprocessors (MP) are concerned.

The testing of digital system is quite complex. To reduce the number of test vectors, partitioning of a digital system is essential, and the treatment of test points is rather flexible.

## 2.3 High-Level Test Synthesis

As mentioned above the basic aim of High-level Test Synthesis (HLTS) is to improve the testability of a design, while other constraints such as performance and area are satisfied.

HLTS is usually carried out by DFT specific transformations together with traditional High Level Synthesis methods. Testability measures are associated with Test Synthesis as one factor of the cost function to guide the synthesis process. HLTS tries to find a good trade-off between Design Testability, performance, area and Power dissipation. Heuristic algorithms are usually employed to estimate the testability measures, when the final implementation at the gate level is not yet known.

So far, a number of different approaches have been proposed in both the behavioural and structural domains at algorithm or RT levels.

A survey on HLTS is given in [Wag96]. Strategies and challenges of the System-on-Chip test are given in [Agr94, Cho94, Var97, Zor98a, Mar99b]. Information about Structural test-point insertion can be found in [Bat85, Dey94, Gu96, Var98].

Test-Register Minimization (TRM) is another technique derived from either HLS techniques or RTL Transformations [Avr91, Pap91, Avr93, Har93] The main challenges in relation to System-on-Chip Test are:

- (1) Core Internal Test Challenges

- (2) Core Test Access Challenges

#### (3) System-chip Test and Diagnosis Challenges.

In relation to Core Level Test, it can be said that a core is typically the hardware description of current standard ICs, e.g., DRAM core, RISC processor, or DSP. A given core is tested as part of the overall System-chip by the System Integrator and not tested individually as in standard ICs. Usually the cores, especially hard cores, are dealt with as a black box, because the system integrator in most cases (except for soft cores) has very limited knowledge of the structural content of the adopted core. So this necessitates that the core provider develops the core test, i.e., the corresponding test pattern and the DFT structures, and delivers the test with the core [Zor98a].

In the traditional approaches, hard cores tests are predetermined for the overall chip test method and the desired fault coverage. So it's the designer that incorporates hard cores test requirements during test development. With a System chip, on the other hand, a core provider is not necessarily familiar with the target application information of components and their quality requirements. Thus, the provided quality level might or might not be adequate. If the fault coverage is too low, the quality level of the system chip is put at risk, and if it is too high, the test cost might become unacceptable.

Core-based System-on-Chip (CBSOC) designs bring us a number of test challenges. Several reusable intellectual property (IP) cores are integrated to form a wide range of functionality on a single die. As IP cores become more complex, the volume of test data for a SOC is growing rapidly. To test these systems effectively, each core must be adequately exercised with a set of precompiled test patterns provided by the core vendor.

Unfortunately, the input-output (I/O) channel's capacity, speed and accuracy, as well as data memory of Automatic Test Equipment (ATE), are

limited. So to apply the enormous volume of test data to the SOC is becoming increasingly difficult.

Reducing test-data volume will not only reduce ATE memory requirements, but also reduce testing time. The testing time depends on the test-data volume, the time required to transfer the data to the cores, the rate at which the test data is transferred (measured by the cores test-data bandwidth and ATE channel capacity), and the maximum scan chain length. Shortening and reorganizing the scan chain can also reduce the total test time. So, test-data compression and decompression techniques offer a promising solution to reduce the enormous test-data volume for SOC's.

A novel approach that uses an embedded processor to aid in deterministic testing of the other components of an SOC is presented in [Jas02]. By this approach, a program containing Compressed Test Data (CTD) can be loaded into the processor on-chip memory by the tester. The proposed approach supports external testing of embedded cores using deterministic test vectors.

A kind of new test-data compression method and decompression architecture is presented in [Cha01b]. Other test-data compression techniques are presented in [Ish98, Jas02].

## 2.4 High-level Low-Power Synthesis

There are three major sources of power consumption in CMOS circuits-Switching, Short-circuit and Leakage. Usually, if proper design techniques are used, short-circuits and leakage can be made negligible. Thus, switching is the main factor responsible for power consumption. Switching determines the effect of charging and discharging of node capacitance in the circuit and it's given by the following formula [Ped96]:

$$P_{switch} = \frac{1}{2} C_l V_{dd}^2 E_{sw} f_{clk}$$

Where  $C_l$  is the total physical capacitance at the output of the node,  $V_{dd}$  is the supply voltage,  $E_{sw}$  is the average number of output transistors per clock cycle (also called switching activities), and  $f_{clk}$  is the clock-frequency.

According to the above formula, if a lower power consumption design is required, a reduction in supply voltage  $V_{dd}$  might be desirable due to its quadratic relation to power. However, the reduction of  $V_{dd}$  has a negative impact on the design speed. It is well known that the reduction of  $V_{dd}$  increases the delay of the components and thus reduces the throughput of the design, which is a very undesirable effect. Many high-level low-power synthesis techniques have been presented in the literature, a survey on these techniques is given in [Ped96].

High-level power consumption estimation [Meh94, Cha95a] plays an important role in high-level lower-power synthesis. A general approach that uses a parameterized module library together with other heuristics or analytical methods to get the power consumption estimation for a complete design can be found in [Kum95, Mar95].

Power Optimization technique is also used in high-level low-power synthesis. The main goal of a High-Level Power Optimization system is to produce a RT level design, which has minimum power consumption, while achieves the required throughput.

#### 2.5 Test Parallelism and Test Time Reduction

The approaches that reduce the test application time by restructuring the test sequence can be classified into two classes: the Static approaches and the

Dynamic approaches. The main feature of Static Test Sequence restructuring approaches is that they do not increase the complexity of test generation. The test generators are assembled in order so that the overall application time is reduced [Dim 91, Fen91].

Dynamic test sequence restructuring tries to reduce the number of test vectors by carefully assigning the unspecified input signal values to binary constants [Lee92, Pra92].

For a Built-In Self-Test (BIST) circuits, the first test sub session lasts until the sub-circuit with the smallest test length has been tested. The minimized execution techniques, which order the registers included in single scan chain, are proposed in [Gup91, Nar92]. In [Nar93, Nar95], a configuration approach for single scan chain in order to minimize the shift time in applying test patterns on a device is proposed.

For reducing the overall test application time, multiplexers are employed to bypass registers that are not frequently accessed in the process. In [Lai93] a technique that reduces test application time for general scan design circuits, is proposed. The test application time can be reduced to a given scan path by exploiting and eliminating unnecessary scan operations.

In [Lar01c], the authors deal with Scan-chain Sub-division, which is used as a technique to reduce test application time for SOC.

Many attempts have been made to share hardware elements when dealing with optimization of test scheduling. Unfortunately, there is a conflict in the reduction of area overhead and testing time.

A minimal set cover technique [Kim88] is proposed for Built-In Logic-Block Observation (BILBO) minimization. A technique of area optimization, while considering test scheduling using a graph coloring approach, is presented in [Kim82]. In [Cha01], the authors formulated the same problem as an Integer Linear Programming (ILP) as well as a graph search problem with a

heuristic cost function. A High-level Power Optimization survey is contained in [Mac97].

### 2.6 Test Scheduling Heuristics

Several Heuristics for Test Scheduling will be introduced next. They are Simulated Annealing and Tabu Search respectively.

#### 2.6.1 Simulated Annealing

Simulated annealing is a combinatorial optimization procedure corresponds to the annealing process in physics, where a material is heated up to its melting point and then the temperature slowly lowered to find its minimal energy state.

Its algorithm is similar to the Random Descend Method in that the neighborhood is sampled at random. By allowing uphill moves in a controllable mode, SA provides hill-climbing mechanism to avoid getting stuck in a local optimum.

The Simulated Annealing algorithm is proposed in [Kir83]. After an initial solution is first created, a minor modification of it creates a neighboring solution and the cost of the new solution is evaluated. If the new solution is better than the previous, the new solution is kept. A worse case solution can be accepted at a certain probability, which it controlled by the temperature parameter.

The temperature is decreased gradually during the optimization process and this reduction in temperature leads to the probability of accepting worsening solution decreases. When the temperature value is approximately zeroed, the optimization terminates. The advantage of the Simulated Annealing algorithm is that it is relatively easy to implement. Among its disadvantages are long computational time and it requires complicated tuning of the relevant annealing parameters [Gaj92]. Regulations and guidelines for parameter selection do not exist, with the rules often depending on the experimental results.

#### 2.6.2 Tabu Search

Tabu Search (TS) [Hal96] is a search approach, which employs an artificial intelligence inspired technique. It can avoid trapping the actual solution at local optima, as a result of this intelligence being kept in memory [Glo86].

As in the case of Simulated Annealing, TS is a high level heuristic procedure used to guide other methods towards an optimal solution.

TS is based on the assumption that an intelligent search should be based on more systematic forms of guidance rather than random selection. It also exploits flexible memory to control the search process. The main mechanism for exploiting flexible memory is to classify a subset of the neighborhood moves as forbidden moves (called Tabu). A short-term memory with a predefined length is used to remember the number of recent moves, which comprises both downhill and uphill moves. These moves are allowed to repeat and are selected intelligently (the best admissible moves are selected).

TS is very useful when the feasibility condition is very strong and the randomly generated neighborhood solutions are usually unfeasible ones. This is partly due to the fact that TS emphasizes complete neighborhood evaluation to identify moves of high quality, while SA samples the neighborhood solutions randomly.

The main drawback of TS is that no theory has yet been formulated to support TS and its convergence behavior. Another obvious difference between TS and SA is that TS uses both short-term and long-term memory intelligently, while SA uses no memory.

# Chapter 3 Power-Constrained Test Scheduling

The Digital System / SOC test problems cannot be dealt with at low levels. Test Application Time (TAT), being one of these problems, has to be considered more carefully. Cost considerations affect many designers in their product inventions.

Besides the cost consideration of TAT, the heat dissipated during test application of digital systems also affects the design of test methodologies. It is reported in [Zor93] that one of the major considerations in test scheduling is the fact that heat dissipated during test application is significantly higher than that during a digital system's normal operation. While trying to increase test parallelism in order to reduce test application time, the confining condition of power dissipation constraint (which relates to the overlap of block-tests.) should, of course, also be satisfied.

The so-called Unequal-Length Block-Test Scheduling [Cra88] refers to the scheduling tests for blocks of logic, which has unequal test lengths. It is viewed as part of a system-level block-test approach to be applied on a modular or view of a test hierarchy. The modular elements of this hierarchy include blocks at the following levels: subsystem, back-planes, boards, MCMs, IC dies, macro blocks and RTL blocks. The test hierarchy accepts

RTL blocks as the lowest level blocks, and it is assumed that a test-step level scheduling has been carried out on RTL blocks.

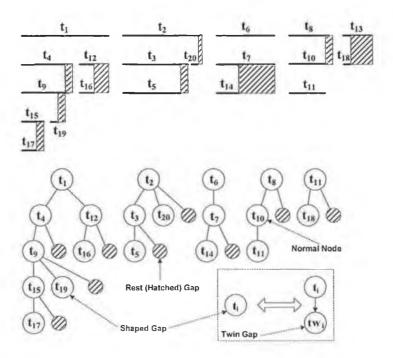

Usually, any node in the hierarchy has different sub-nodes. After the test scheduling optimization has been performed on the node, a few parameters of each test node  $t_i$  are determined. These features are given in Figure 3.1, test application time  $T_i$ , or Test Length (TL), power dissipation  $P_i$  and test resource set RES.SET<sub>i</sub>.

Figure 3.1: First Example of Node under Test.

To a certain node, its sub-nodes are considered for the optimization of parameters, such as test length, power dissipation. This optimization is performed so as to get an optimal or near optimal sequencing or overlaying

(scheduling) of them quickly, while the power dissipation constraints are satisfied. A technique named Merging Approach based on the tree growing technique is proposed here to generate the block-test schedule profile at the node level. It is used to minimize the overall TAT, and to analyze and optimize the characteristics of power dissipation during test.

The first section of this chapter describes the current systems testing issues and the approaches currently employed. The emphasis here is on Core Testing Techniques and Core Related Scheduling approaches.

The second section outlines a brief survey of Power Test Parallelism techniques.

In the last section, system-testing under power constraints is described. Efficient algorithms that can be applied to this power-test model are proposed in the next chapter.

## 3.1 System Testing

With the steep increase of Digital System design dimensions the tendency is to shift to SOC technology (it has been changing for the classical synthesis methodology at high-level). Because of the cost consideration, design reuse is emphasized widely [And97]. Nowadays, more and more reusable cores are provided to the customers by IP vendors. A core is typically the hardware description of current standard ICs, e.g., Digital Signal Processor (DSP), Reduced Instruction Set Computer (RISC) processor, Dynamic Random Access Memory (DRAM). Such cores may be available in synthesizable RTL (soft) form, gate-level net-list form, or layout-level "hard macro" form [Zor97]. So, a lot of research effort today is concentrated on core synthesis and its testing.

From a digital system-testing viewpoint a core should initially be well characterized. The core internal test (prepared by a core vendor or creator) needs to fit for adequate description, portable and ready for plug and play. This allows for interoperability in the relevant SOC test. An internal test should be described in a standard format, so that compatibility is ensured. The IEEE P1500 [Zor97] proposes such a standard. The SOC test requires adequate test scheduling. The scheduling is required to satisfy a number of system level requirements, such as overall test time, power dissipation, and area overhead. It is necessary to run intra-core, inter-core tests and test scheduling in a certain order so as to avoid impacting the test contents of individual cores or modules.

In the last few years' interest in MCMs has grown rapidly, due to advances in miniaturization techniques. This has contributed to higher performance and reliability in the field of commercial to military electronic products. The production test and field test of large MCM designs will be seriously affected by TAT and Test Mode power dissipation problems unless they have been optimised in testing. The complexity and dimensions of such digital systems (like MCMs) balance the optimisation of TAT with power dissipation constraints.

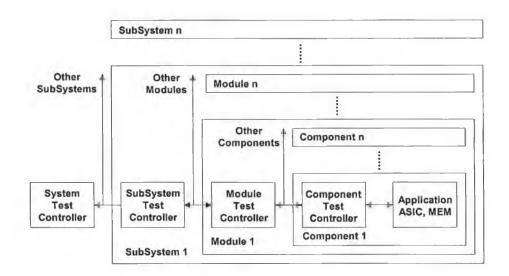

# 3.1.1 Core Testing

A general hierarchical test structure is described in Figure 3.2 [Zor97]. Since more and more VLSI chips adopt multiple cores from different vendors, the testing issue and the power dissipation problem become increasingly serious. All core users must face the following two key issues: one is the interconnection of cores within a chip, another is the ability to perform an effective test on the final device.

Test concurrency of core-based system testing is affected by the core supplier's application interface.

Figure 3.2: A General Hierarchical Test Structure.

A core should, therefore be characterized well from a test perspective, fault coverage and power consumption in test mode or normal mode. Adequate test scheduling is required for the SOC composite test. Test scheduling is performed to satisfy a number of system level requirements, such as Total Test Time (TTT), Power Dissipation (PD), area overhead, etc. Furthermore, test scheduling is also necessary to run intra-core and inter-core tests in a certain order so as to avoid impacting the testing contents of other individual cores or modules.

Many general approaches concerning core testing are introduced in [And97]. Firstly, to finalize core functional tests that run in the complete chip, parallel multiplexed access mechanism from chip pins is provided. The degree of test concurrency drops when there are more I/Os than chip pins or when routing is complex. Secondly, by encapsulating cores in a JTAG (Joint Test

Action Group) scheme, such as Boundary Scan Ring (BSR), to run core tests in parallel is isolated with little need for external support. Thirdly, by using BIST or scan techniques to test each core, internal control and observation are provided.

If there is no method to ensure that multiple cores are tested in parallel, system test time may be unacceptably long. Fortunately, being a test method, one of the features of BIST is autonomy and self-sufficiency. So, BIST is considered ideal for a modular-based system [Zor97].

There are BIST strategies, such as the one referred to in [Zor90], which tries to solve the core test scheme problem, by using a divide and conquer approach to enhance the overall control and observation. There are still pending problems, however, when using this strategy, in isolating and accessing the boundaries of the modules. There are also problems in automating the process of assembling the set of inter-module and intra module set of tests in the overall chip [Ben97].

A Macro Test is an approach used for testing embedded modules as standalone units. This approach is very suited for core-based testing and from this point of view it is very suitable for hierarchical and divide and conquer approaches.

# 3.1.2 Core Test Scheduling

Scheduling can be used to reduce the overall Test Vector Set (TVS) substantially in the various core tests, but the test quality of IC design is not improved. An example of this is a core-based design, with a given set of cores, and given corresponding test protocols and sets of test patterns.

Through test protocol scheduling, the various expanded test protocols can be scheduled, and the total TVS of the system can be minimized [Mar99a]. At

test protocol level, the test scheduling offers a good trade-off between test vectors set reduction and the computational effort to achieve this.

A method is introduced in [Sug98] that selects a test-set for each core from a set of tests provided by the core vendor. Meanwhile, the problem of scheduling their tests in order to minimize the testing time is addressed also. Each test set comprises a subset of patterns for BIST and a subset of patterns for external testing. It is the core vendor that provides multiple test sets for each core, including varying pattern proportions for BIST and external testing for the test sets. The core test-scheduling problem can be formulated as a combinatorial optimization problem and solved using heuristics. Two restrictive assumptions are made in the method. The first one is that every core has its own BIST logic. In other words, the BIST components of the test set for any two cores can be assigned identical starting times. The second assumption is that external testing can be carried out for only one core at a time (i.e. there is only one test access bus at the system level).

An optimal solution approach for the test-scheduling problem for corebased systems is proposed in [Cha01a]. This approach is based on a mixed-integer linear programming model. The drawback is that, when the number of cores in large test-scheduled systems grows, this approach features non-polynomial time. A heuristic-scheduling algorithm, named Shortest-Task-First (STF), is proposed instead to handle such systems. Given a set of test-tasks, a set of test resources and the test access architecture, the test scheduling solution refers to the problem of determining start time for the tasks, so that the total test application time is minimized. Other approaches [Zor98b] deal with the core test problem at system level by focusing the design of efficient test access architectures.

In [Lar00a, b], a greedy heuristic is proposed for core test scheduling under power constraints. The relevant work is developed in [Lar01a, b]. It

considers test scheduling and design of test bus infrastructure at the same time. With this approach, test time, test bus length and width are minimized while power consumption constraints and test resources are considered. There are two steps for this approach. In the first step, a heuristic is used repetitively to select a feasible solution at a low computational cost. The second step optimizes the feasible solution by a simulated annealing approach.

# 3.2 Power-Conscious Test Parallelism

Power consumption limitation is a critical issue in computing devices, particularly in portable and mobile platforms such as laptop computers and cell phones. Power dissipation during test has not yet been thoroughly researched with much more research to be done. Power consumption during test is important since excessive heat dissipation can damage the circuit under test. Since power consumption in Application Test Mode (ATM) is significantly higher than that during normal operation, special attention must be taken to ensure that the power rating of the SOC is not exceeded during test [Zor93].

A number of techniques to control power consumption in test mode have been presented in the literature. These include the following:

Test-Scheduling Algorithm under power constraint [Abr90], low-power Built-In Self-Test (BIST) [Agr93a, Agr95], and techniques for minimizing power during Scan Testing [Agr93b, Agr94, Ait99]. Power consumption is especially important for SOC's, because test-scheduling techniques for system integration attempt to reduce the test time by applying scan BIST vectors to several cores simultaneously [Ali94, AMS]. Therefore, it is extremely important to control power consumption while testing the IP cores in a SOC.

There are a few Structural Domain approaches that tackle the power dissipation problem during test application at logic level. These include Test Vector Reordering (TVR), Test Vector Inhibiting (TVI), switching activity conscious ATPG and Scan Latch Reordering (SLR). Unfortunately, the above approaches are inefficient at high levels. An efficient solution that partitions the system under test at system-level is proposed in [Zor93], which includes appropriate test planning and scheduling to solve the test-scheduling problem under high-level power constraints. A feasible solution is proposed in the next chapter in this thesis.

The power dissipation problem during test application is described in this section. Then the main techniques, which have been applied to solving the problem, are surveyed. Finally, previous work on Power-Constrained Test Scheduling techniques, the main topic of this thesis, will be focused on.

### 3.2.1 Power Minimization During Test Application

Performance, cost, and testability are the main parameters targeted during the Synthesis and Optimization phase of integrated circuits. The following research outlined solutions for minimizing power dissipation during normal (functional) operation mode. High-level power minimization techniques in [Abr90, Agr93a, Agr95] yield trade-off throughput, area and power dissipation during scheduling, allocation and binding. At logic level, two successful power management techniques, based on pre-computation [Agr93b, Agr94] and graded evaluation [Ait99], have been presented. However, to consider only power dissipation during the normal operation mode is not enough. It is essential to scrutinize it during test operation mode as well.

In [Zor93, Ali94], it is proposed that power dissipated during test application is significantly higher than power dissipated during normal

functional operation, which can lead to loss of yield and decrease the reliability of circuits under test. The reasons for high power dissipation during test application are as follows:

- 1). The correlation between consecutive test vectors generated by an automatic test pattern generator (ATPG) is very low, since a test is generated for a given target fault without any consideration of the previous test vector in the test sequence.

- 2). The use of design for testability (DFT) scan techniques destroy the correlation, which typically exists between successive states of the sequential circuit by allowing the application of any desired value to the state latches.

During the VLSI design flow, minimizing power dissipation increases the reliability and the lifetime of circuits [Cha95b, Rey00, Wed96]. It is reported [Ped96] that the Deterministic Dominant Factor of power dissipation is dynamic power dissipation caused by switching activities [Cha95b, Rey00]. The additional power dissipation in test mode is caused by significantly higher switching activity during testing than in functional operation. Techniques developed in the above references have successfully reduced the circuit power dissipation during functional operation.

Testing of low power circuits has recently become an area of concern for the following reasons:

Firstly, it is reported [Zor93] that there is significantly higher switching activity during Test Mode than during normal operation and, hence higher power dissipation in test mode. This can decrease the reliability of the circuit in Test Mode due to excessive temperature and current density. Circuit designed using power minimization techniques may not tolerate this.

Secondly, high switching activity during Test Application can leads to manufacturing yield loss, which can be explained as follows: High switching activity during test application causes a high rate of current flowing in power and ground lines leading to excessive power and ground noise. And this noise can change the logic state of circuit lines leading to incorrect operation of circuit gates causing some good dies to fail the test [Wag98]. Hence, it has become an important issue to address the problems associated with testing low power VLSI circuits.

Spurious transitions (i.e. glitches) during functional operation do not have any useful function and cause useless power dissipation. So power can be saved during test application and during normal operation, by eliminating spurious transitions [Cha95b, Ped96, Rey00]. Many (new) techniques have been presented in the literature.

- 1. Memory optimization techniques

- 2. Hardware-Software partitioning

- 3. Instruction-level power optimization

- 4. Control-Date-Flow transformations

- 5. Variable-Voltage techniques

- 6. Dynamic power management

- 7. Interface power minimization

- 8. Approximate signal processing

Many techniques have been proposed to overcome the problem of high power dissipation during test application. Usually, the ordering of both scan flip-flops and the test patterns influences power and energy. Most of the techniques relate to BIST methodologies at logic level. They can be classified into those that apply to Test-per-Scan BIST schemes and those that apply to Test-per-Clock BIST schemes. In Test-per-Scan BIST systems, a test pattern is applied to the Circuit-Under-Test (CUT) via a scan chain every m+1 clock cycles, where m is the number of flip-flops in the scan chain. The response is

captured into the scan chain and scanned out during the next m clock cycles; meanwhile the next test vector can be scanned in simultaneously. A modification of the scan cell design is proposed in [Her98]. By this method, the Circuit-Under-Test inputs remain unchanged during operation, and a significant energy saving can be realized by means of this novel design for scan path elements. A low transition random pattern generation technique is proposed in [Wan99]. Using this technique, signal activities in the scan chain can be reduced. Using a K-input Gate and T Latch a high correlation between neighboring bits in the scan chain can be generated. Consequently, the number of transitions, and thus the average power dissipation is significantly reduced.

A post ATPG phase technique is proposed in [Cha94a, b, c], to reduce power dissipation for full-scan and for pure combination [Dab94] circuits. In [Dab98], the authors summarize the above techniques and use a transition graph for low power consumption in scan circuits and combination circuits. Firstly, in the full-scan case, a fixed scan-latch ordering is assumed and then, using a greedy heuristic, a test-vector ordering is computed so as to minimize the power dissipation during test application. Secondly, two heuristics are used to minimize power dissipation. Scan-Latch Ordering uses the Random Ordering Heuristic and Test-Vector Ordering uses Simulated Annealing. Finally, by the methods of circuit disabling, switching activity is inhibited in the embedded combination circuits, meanwhile the test values are scanned-in and scanned-out.

In test-per-clock BIST systems, the outputs of a test pattern generator are connected directly to the inputs of the CUT. A new test pattern is applied at each clock cycle and the response is loaded into the response analyzer. By generating test vectors from TPGs that cause fewer transitions at circuit inputs, switching activity in the CUT can be reduced. In the same vane, a BIST strategy based on two different speed LFSRs is proposed in [Wan97b]. Its

objective is to decrease the overall internal activity of the circuit by means of connecting inputs with elevated transition density to the slow LFSR. This approach can reduce the average power consumption without any loss of fault coverage.

A technique named as Reseeding Scheme in conjunction with a Vector Inhibiting Technique, is proposed in [Gir99a] for the purpose of minimizing the energy dissipation during test. This is an effort at tackling the increased activity during test operation of hard-to-test circuits that contain pseudorandom resistant faults. An improvement of this technique is proposed in [Man99], where the filtering action is extended to all the non-detecting vectors of the pseudo-random test sequence. However, a circuit cannot be prevented from excessive peak power consumption by these techniques.

In [Moh02], an approach for reducing power consumption in the checkers used for Concurrent Error Detection (CED) is proposed. Spatial correlation between the outputs of the circuit that drives the primary inputs of the checkers is analyzed to order them such that switching activity (and hence power consumption) in the checker is minimized. The reduction in power consumption comes at no additional impact to area or performance and does not require any alteration to the design flow. The only cost involved is the computing time in the input ordering for the checker that minimizes the power consumption.

# 3.2.2 Power-Constraint Test Scheduling

Most of the Block-Test Scheduling techniques proposed so far, are only addressed at logic-level in order to schedule for test time minimization by using parallelism, or to schedule for area overhead optimization by sharing test resource in data path blocks [Cra88]. These techniques are certainly valid for

logic-level, or at most, RT level blocks. Unfortunately, their function is limited. They cannot schedule BIST of parallel blocks for a complex VLSI device.

In [Zor93], the BIST scheduling approach has taken power dissipation into account during block-test scheduling for the first time. This approach not only performs global optimization, but also considers other factors such as block type, adjacency of blocks (device floor plan). The latter are unknown at high-level, however. In complex VLSI circuit design, the block test set is large and varies in test length. So it is impractical to expect that this approach can provide any polynomial complexity algorithm. This approach is useful only for defining and analyzing the problem.

Even if there is no resource conflict on a pair of tests, it still does not necessarily mean the two tests can be performed concurrently. This is because the combined power consumption must be ensured carefully not to exceed the maximum power limit. One example is memories. Usually they are organized into blocks of a fixed size. In normal operation mode, just one block is activated per memory access at the same time; other blocks are in the power-down mode so as to minimize the power consumption. For memory system in test mode, it is desirable to concurrently activate as many blocks as possible so as to minimize test time provided that the power consumption limit of the system is not exceeded.

Testing of MCMs is another example. For testing MCMs, an attractive approach is to use BIST block executing in parallel. In normal operation mode, the blocks are not activated simultaneously. So the inactivated blocks do not contribute significantly to total power dissipation. However, in test operation mode, a concurrent execution of BIST in many blocks will bring significantly higher power dissipation, and it might exceed the maximum power dissipation limit. In consideration of the reliability of a digital system

under test, execution of self-test blocks must be scheduled carefully following a certain principle so that the maximum power dissipation limit is not exceeded at any time during testing.

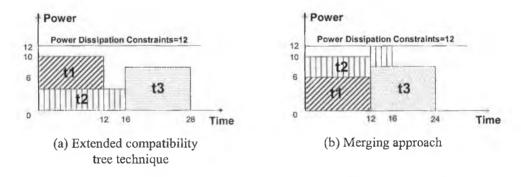

The problem of minimizing power dissipation during test applications is addressed at a higher level in [Cho94, Cho97]. In [Cho97], where the problem of scheduling equal length tests with power constraints is formulated. The objective is to find a test schedule with power-constraint, which covers every test in at least one test session, so that the total test application time is minimized. The solution is divided into two steps: identifying the solution space, and then, searching the solution space for an optimum solution. For solution space identification, the following definitions are given. The first one is Power Compatible Set (PCS), which is a set of tests that can be performed concurrently. The second one is Maximum PCS (MPCS), which is a subset of PCS, in which no compatible tests can be added without exceeding the maximum power consumption limit.

Macro Test (MT), is an approach being used to test embedded modules as stand-alone units, and is very suited for core-based testing. From this point of view it is very suitable for hierarchical and divide and conquer approaches. Macro Test is based on the following concept [Mar97]. A test can be divided into a test protocol and test patterns, where the test protocol gives the regulation on how to apply the test patterns to the inputs and how to observe the outputs of the macro under consideration. Through test protocol expansion, a translation of macro-level test to IC-level test is performed. Macro Test and test protocol expansion are designed to support multiple levels of hierarchy in a design. Once the various core tests are expanded to chip level, they can be applied in a simple sequential order, or be scheduled by the test protocol scheduler [Mar99a]. Test Protocol Scheduler attempts to perform the various cores tests in parallel as much as possible so that the Test Application Time

(TAT) can be reduced. However, the possibility of power dissipation increases while reducing the TAT is not taken into account yet. Macro Test (MT) supports every kind of test accesses, including parallel direct access, serial scan and BIST.

# 3.3 PTS Problem Modeling

The modeling of PTS problem will be discussed in detail in this section. It comprises of five subsections: System Modeling, High-Level Power Dissipation Estimation, PTS Problem Formulation, The Tree Growing Technique and Power-Test Scheduling Chart.

### 3.3.1 System Modeling

The problem of Power-Constrained Block-Test Scheduling (PTS) was first theoretically analyzed in [Cho97] at IC level. Generally, it can be viewed as a compatible test-clustering problem, which is a known NP-Complete problem. A merging approach based on the tree growing technique is proposed in this thesis to tackle the PTS problem. The approach has a polynomial complexity, and this is very important for the system level test scheduling efficiency. The proposed approach deals with the so-called Unequal-Length block test schedule problem, i.e., the tests for blocks of logic are of unequal length. In this approach, the order of the tests within a block test set is not considered.

### 3.3.2 High-Level Power Dissipation Estimation

When we talk about power in relation to the current topic we usually mean the instantaneous power.

Instantaneous power can be represented as p(t), which is the power dissipation value at any time instant t:  $p(t) = i(t) \times v(t)$ , where i(t) and v(t) are the instantaneous current and voltage in the circuit respectively. In general, the voltage is a constant and equals to the power supply, i.e.,  $v(t) = V_{dd}$ .

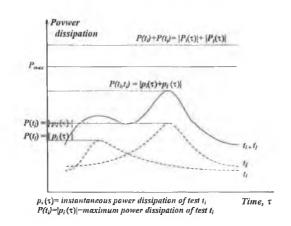

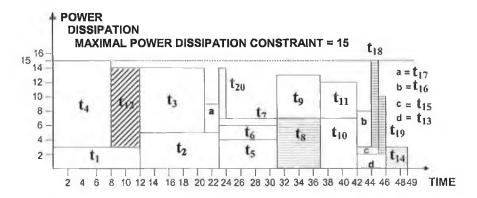

Provided  $p_i(t)$  is the instantaneous power dissipation of test  $t_i$  and  $p_j(t)$  is the instantaneous power dissipation of test  $t_j$ , then the total power dissipation of a test session (i.e., two overlapped tests) is approximately the sum of the instantaneous power of test  $t_i$  and test  $t_j$ . This relation as depicted in [Cho97] is shown in Figure 3.3. Normally it is unacceptable for the instantaneous power to exceed a maximum power dissipation limit  $P_{max}$ , because the IC might be destroyed if this occurs. Unfortunately, the instantaneous power of test vectors are difficult to obtain, as different test schedules will result in diverse instantaneous power dissipation profiles for the same test.

**Figure 3.3:** Power Dissipation as a Function of Time.

In order to simplify the analysis, a fixed power value  $P_i$  is assigned to all test vectors in test  $t_i$  so that at any time instant the power dissipation is no higher than  $P_i$ .

To evaluate the power properties of BIST architecture several parameters are important; most of which are detailed in [Ger99]. The consumed power is directly determined by the switching activity and affects the battery lifetime or junction temperature during test. The maximum power corresponds to the maximum power consumption rate during test time. If the maximum power limit is exceeded, the IC may be destroyed. The Time-average power (Average power) is the total consumed power divided by the test time. This parameter affects reliability caused by constant high-power consumption.

The approach for power analysis as described above, is suitable for work with the proposed algorithms in this thesis. Accurate high-level power evaluation is impossible, so power estimation is the only viable solution. A constant additive model is employed for power estimation. For the purpose of simplification, only a constant Power Dissipation ( $P_i$ ) value is associated with each block-test. As to the total power dissipation at a given test schedule time, it is only the  $P_i$  summing relation of the running block-tests.

Usually there are three ways to estimate the Power Dissipation,  $P_i$  of a block-test at a high level:

- Maximum  $P_i$ ,

- Average  $P_i$  and

- RMS  $P_i$ .

Firstly,  $P_i$  can be defined as the Maximum power dissipation (Peak Power) over all test vectors in test  $t_i$ . It is the upper bound power dissipation in test  $t_i$ , and its definition is pessimistic. In this case, two tests  $t_i$  and test  $t_j$ , where peak power occurs at different time intervals, are not allowed be scheduled in the same test session.

Secondly,  $P_i$  can be defined as the Average power dissipation over all test vectors in a block-test  $t_i$ . In the analysis of power dissipation, its definition might be optimistic when many test vectors are applied simultaneously, as the

average value cannot describe the instantaneous power dissipation of each test vector. Therefore, at some time intervals, it is possible that the power dissipation limit of the IC might be exceeded.

Thirdly, RMS power dissipation is needed to tackle the problem when instantaneous power dissipation includes short power spikes and a more accurate estimation is sought.

### 3.3.3 PTS Problem Formulation

The circuit activity should be maximized so that the circuit can be tested thoroughly in the shortest possible time. However, in a test environment, the difference between the various power estimation values for each test is very small [Cho97]. In this thesis the lowest level block considered is at the RTL (Register Transfer Level) in the test hierarchy, and it is assumed that a test-step level scheduling has already been applied at this level. Additionally, by using the approach proposed here for optimizing the blocks in the test hierarchy from the lowest level (RTL) to the top level (System Level), the difference between the power values could be further reduced. The reason is that, after applying the PTS algorithm at each level, the circuit activity or power consumption is maximized and balanced.

So  $P_i$  can be viewed as the maximum Power Dissipation over all tests vectors in test  $t_i$  [Cho97]. In further analysis,  $P_i$  is assumed to be the maximum Power Dissipation of test  $t_i$ .

# 3.3.4 The Tree Growing Technique

A tree growing technique was first proposed in [Jon89] and further developed in [Mur00a, b].

It is used to exploit the potential of test parallelism by merging and constructing the Concurrent Test Set (CTS). This is achieved by means of a Binary Tree Structure (not necessarily complete), called Compatibility Tree, which is based on the compatibility relation between tests.

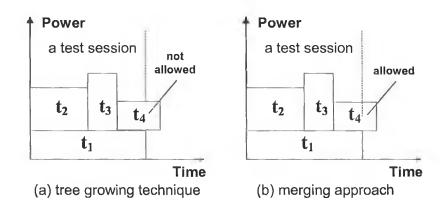

A drawback in the original technique [Jon89] is that the compatibility trees are binary trees. This limits the number of children test-nodes that could be

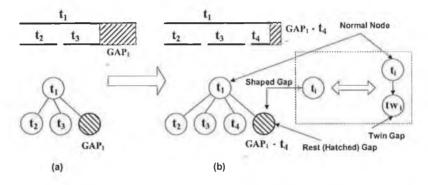

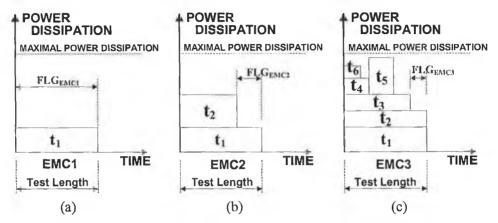

Figure 3.4: Merging Step Example.

overlapped to the parent test node to only two. The number of children test nodes in practice can be larger than two, as in the example depicted in Figure 3.4. [Mur00c]. An Extended Compatibility Tree (ECT), given by means of a generalized tree, is proposed in [Mur01] to break this limitation.

The compatibility relationship comprises three components.

- (1) The power dissipation accumulated on each tree branch should not exceed the power dissipation constraint  $P_{max}$ .

- (2) The test lengths of the nodes in a tree branch should be non-increasing from root to leaf. In other words, the boundary of test sessions cannot be broken when growing the tree.

- (3) Tests have to be compatible from the resource usage point of view.

In the merging step example in Figure 3.4, the partial test schedule chart is given at the top, while the partially grown compatibility tree is at the bottom. Let's assume as follows:

- (1) Tests  $t_2$ ,  $t_3$  and  $t_4$  are compatible with test  $t_1$ , while they are not compatible with each other;

- (2)  $T_1$ ,  $T_2$ ,  $T_3$  and  $T_4$  are the test lengths of test  $t_1$ ,  $t_2$ ,  $t_3$  and  $t_4$  respectively;

- (3)  $T_2 + T_3 < T_1$

- (4)  $T_4 < T_1 (T_2 + T_3)$ .

As can be seen in Figure 3.4(a), there is a gap GAP<sub>1</sub> given by the following test length difference:  $GAP_1 = T_1$ -  $(T_2 + T_3)$  after tests  $t_1$ ,  $t_2$  and  $t_3$  have been scheduled. So a merging step can be achieved, because  $T_4 < GAP_1$ , by inserting test  $t_4$  in the partial test schedule and its associated ECT as in Figure 3.4(b).

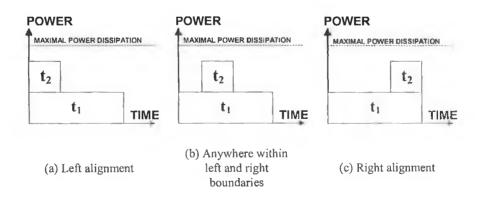

The process of constructing CTS's is implemented by growing the ECT from the roots to their leaf nodes. The root nodes are regarded as test sessions, whereas the expanded tree branches are regarded as their test sub-sessions. When a new test has to be merged to the CTS, the algorithm should avail of all possible branches in the ECT. In order to keep track of the available tree branches and to avoid the complexity of the generalized tree travel problem, a list of potentially Expandable Tree Branches (ETB) is maintained. This list is kept by means of special nodes that are inserted as leaf nodes in each ETB of the expanded compatibility tree. These leaf nodes are called *gaps* and are depicted as hatched or shaded nodes in Figure 3.5.

There are two types of *gaps*. The first set of *gaps* (hatched), called "remnants *gaps*" are those left behind each merging step, as in the cases of  $GAP_1$  and  $GAP_1 - t_4$  in the above example. They are similar to the incomplete branches of the binary tree from [Jon89].

The second set of gaps (shaded), are auxiliary gaps created as the superposition of the leaf nodes and their twins as in the equivalence given at the right in Figure 3.5. They are generated in order to keep track of "non-saturated" tree branches, which are also potential ETBs. "Non-saturated" tree branch means any ETB with accumulated power dissipation still under the given power dissipation limit. The root nodes (test sessions) are considered by default "shaded" gaps before being expanded.

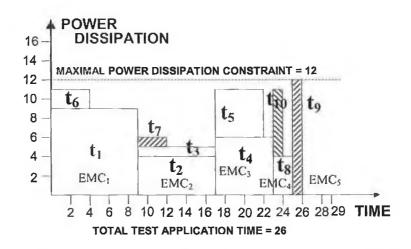

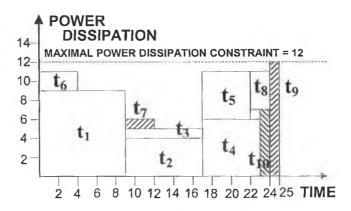

### 3.3.5 Power-Test Scheduling Chart

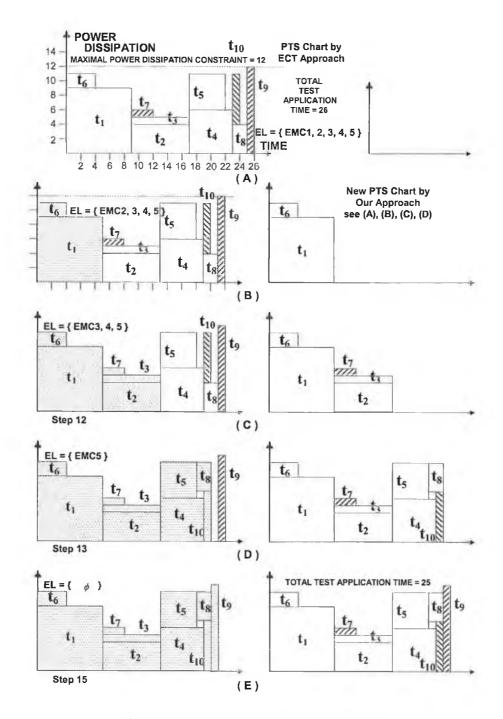

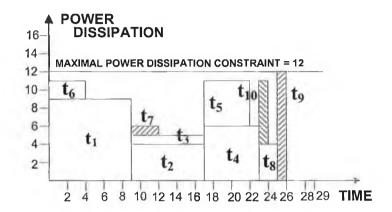

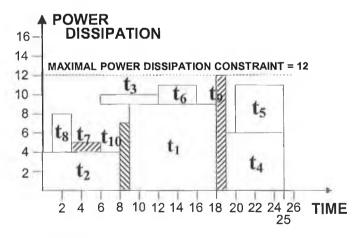

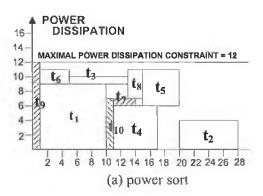

A Test Schedule generated by the so-called List Scheduling-Based PTS Algorithm (PTS-LS) is given in Figure 3.5 [Mur00b]. It can be easily translated into a PTS chart as in Figure 3.6, which gives a clear view of the power dissipation distribution over the test application time.

Figure 3.5: Test Scheduling Chart and ECT Example.

Figure 3.6: An Example of PTS Chart of 20 Tests with Power Dissipation Constraint.

# Chapter 4 Merging Approach Based on the Tree Growing Technique

# 4.1 Introduction

The goal of this chapter is to seek an approach with better efficiency and lower computational cost, e.g., less computational time. The comparison of existing test scheduling approaches is given in Section 4.2. In Section 4.3, our approach, the merging approach based on tree growing technique, is described in detail, including the description of the operating procedures, algorithm pseudocode, the analysis of the algorithm complexity and a test schedule example. In Section 4.4, the conclusion about this chapter will be given.

# 4.2 Existing Test Scheduling Techniques