# University of Southern Queensland Faculty of Engineering and Surveying

# Modelling Load Balancing Type Static Var Compensator Control System Response

A dissertation submitted by

Kim Maree Dawson

in fulfilment of the requirements of

## Course ENG4111/ENG4112 Project

towards the degree of

Bachelor of Engineering (Electrical and Electronic)

Submitted: October 2005

## **Abstract**

As power system interconnection becomes more prevalent, there has been an increase in use of thyristor controlled shunt connected compensation devices for dynamic power system compensation and power transmission capacity increase. A Static Var Compensator (SVC) functions as a variable reactance capable of operating in both the inductive and capacitive region as required on a cycle by cycle basis to provide compensation at the point of connection to the power system.

Voltage regulation is the operational objective of most SVCs. Therefore, transient response of SVC control systems impacts overall power system performance and inappropriate settings may lead to voltage instability. SVCs are also commonly used to convert single phase load into balanced three phase load, thereby reducing negative phase sequence voltages and currents within the power transmission system. As most load balancing SVCs are consistently operated to their capacity, removal from service to apply and test control system setting changes impacts system regulation and stability. Therefore, model development of a load balancing type SVC control system to predict response to setting changes may provide an alternative to lengthy outages of SVC plant.

This paper examines the theoretical basis of thyristor controlled shunt compensation, establishing conditions for voltage support and unbalanced load compensation. Load balancing type SVC control system model development and validation is documented.

#### University of Southern Queensland

#### Faculty of Engineering and Surveying

## ENG4111 & ENG4112 Research Project

#### **Limitations of Use**

The Council of the University of Southern Queensland, its Faculty of Engineering and Surveying, and the staff of the University of Southern Queensland, do not accept any responsibility for the truth, accuracy or completeness of material contained within or associated with this dissertation.

Persons using all or any part of this material do so at their own risk, and not at the risk of the Council of the University of Southern Queensland, its Faculty of Engineering and Surveying or the staff of the University of Southern Queensland.

This dissertation reports an educational exercise and has no purpose or validity beyond this exercise. The sole purpose of the course pair entitled "Research Project" is to contribute to the overall education within the student's chosen degree program. This document, the associated hardware, software, drawings, and other material set out in the associated appendices should not be used for any other purpose: if they are so used, it is entirely at the risk of the user.

#### Prof G Baker

Dean

Faculty of Engineering and Surveying

# Certification

I certify that the ideas, designs and experimental work, results, analyses and conclusions set out in this dissertation are entirely my own effort, except where otherwise indicated and acknowledged.

I further certify that the work is original and has not been previously submitted for assessment in any other course or institution, except where specifically stated.

**Kim Maree Dawson**

**Student Number: 0019423038**

Signature

Date

# **Acknowledgements**

I would like to acknowledge and thank the following people for their support, guidance and assistance:

Mr Ron Sharma – Faculty of Engineering and Surveying, University of Southern Queensland.

Mr Phil Harvey – Technical Services Rockhampton, Ergon Energy Corporation.

Mr Paul Windle – Grid Planning Business Unit, Powerlink Queensland

Mr Randal Jones – Asset Monitoring Team, Powerlink Queensland

Mr Alwyn Janke - Technology and Standards Engineering, Powerlink Queensland

Mr Ross Johnson - Communications and Control Systems, Powerlink Queensland

Mr Dave Millan – Secondary Systems Rockhampton, Ergon Energy Corporation

Mr Glen Kieseker – Powerlink Queensland Field Test Section

And finally, I would like to thank my family and friends for their understanding and support.

K. DAWSON

University of Southern Queensland October 2005

# **Table of Contents**

| Abs  | stract    |         |                                   | ı    |

|------|-----------|---------|-----------------------------------|------|

| Disc | claimer   |         |                                   | ii   |

| Cert | tificatio | on      |                                   | ii   |

| Ack  | nowled    | dgemer  | nts                               | ii   |

| List | of Figu   | ures    |                                   | xi   |

| List | of Tab    | les     |                                   | XV   |

| Glo  | ssary     |         |                                   | xv   |

| Non  | nenclat   | ture    |                                   | xvii |

| 1.   | Intro     | oductio | n                                 | 1    |

| ••   | 1.1       | Backg   |                                   | 1    |

|      | 1.2       | _       | ct Objectives                     | 3    |

|      | 1.2       | •       | ntroduction to Theory             | 4    |

|      |           | 1.2.1   | ·                                 | 4    |

|      |           | 1.2.2   | Power Quality                     | 7    |

|      |           | 1.2.3   | Power System Compensation         | 15   |

| 2.   | Pow       | er Syst | tem Compensation                  | 19   |

|      | 2.1       | Dynan   | nic Power System Compensation     | 19   |

|      |           | 2.1.1   | Thyristor Controller Reactor      | 20   |

|      |           | 2.1.2   | Thyristor Switched Capacitor      | 23   |

|      |           | 2.1.3   | Combined Dynamic Characteristics  | 24   |

|      | 2.2       |         | Var Compensation                  | 26   |

|      | 2.3       |         | Balancing Static Var Compensation | 29   |

|      |           | 2.3.1   | Load Balancing Requirements       | 29   |

|      |           | 2.3.2   | Load Balancing SVC Substations    | 32   |

|      |           | 2.3.3   | Blackwater Static Var Compensator | 34   |

| 3. | SVC  | Contro   | ol Systems                         | 35 |

|----|------|----------|------------------------------------|----|

|    | 3.1  | Nome     | nclature                           | 35 |

|    | 3.2  | SVCC     | Control System Function            | 36 |

|    | 3.3  | SVCC     | Control System Structure           | 37 |

|    |      | 3.3.1    | Automatic Voltage Regulator        | 38 |

|    |      | 3.3.2    | Slope                              | 39 |

|    |      | 3.3.3    | Data Acquisition                   | 40 |

|    |      | 3.3.4    | Modes of Operation                 | 41 |

|    | 3.4  | Load E   | Balancing Type SVC Control Systems | 42 |

|    |      | 3.4.1    | Open Loop Load Balancing           | 43 |

|    |      | 3.4.2    | Closed Loop Voltage Regulation     | 46 |

|    |      | 3.4.3    | Priority Control                   | 50 |

|    |      | 3.4.4    | Control Signal Generation          | 51 |

| 4. | Metl | nodolog  | gy                                 | 52 |

|    | 4.1  | Prelim   | ninary Tasks                       | 52 |

|    |      | 4.1.1    | Industry Requirements              | 52 |

|    |      | 4.1.2    | Technical Research                 | 53 |

|    |      | 4.1.3    | Validation Site                    | 54 |

|    | 4.2  | Model    | Development                        | 55 |

|    | 4.3  | Model    | Validation                         | 56 |

|    | 4.4  | Experi   | imental Methodology                | 58 |

|    | 4.5  | Test E   | quipment                           | 60 |

|    |      | 4.5.1    | Chart Recorder                     | 60 |

|    |      | 4.5.2    | Power System Simulator             | 61 |

|    | 4.6  | Requir   | red Skills                         | 63 |

|    | 4.7  | Repor    | ting                               | 64 |

| 5. | Con  | trol Sys | stem Model Development             | 65 |

|    | 5.1  | Introdu  | ·                                  | 65 |

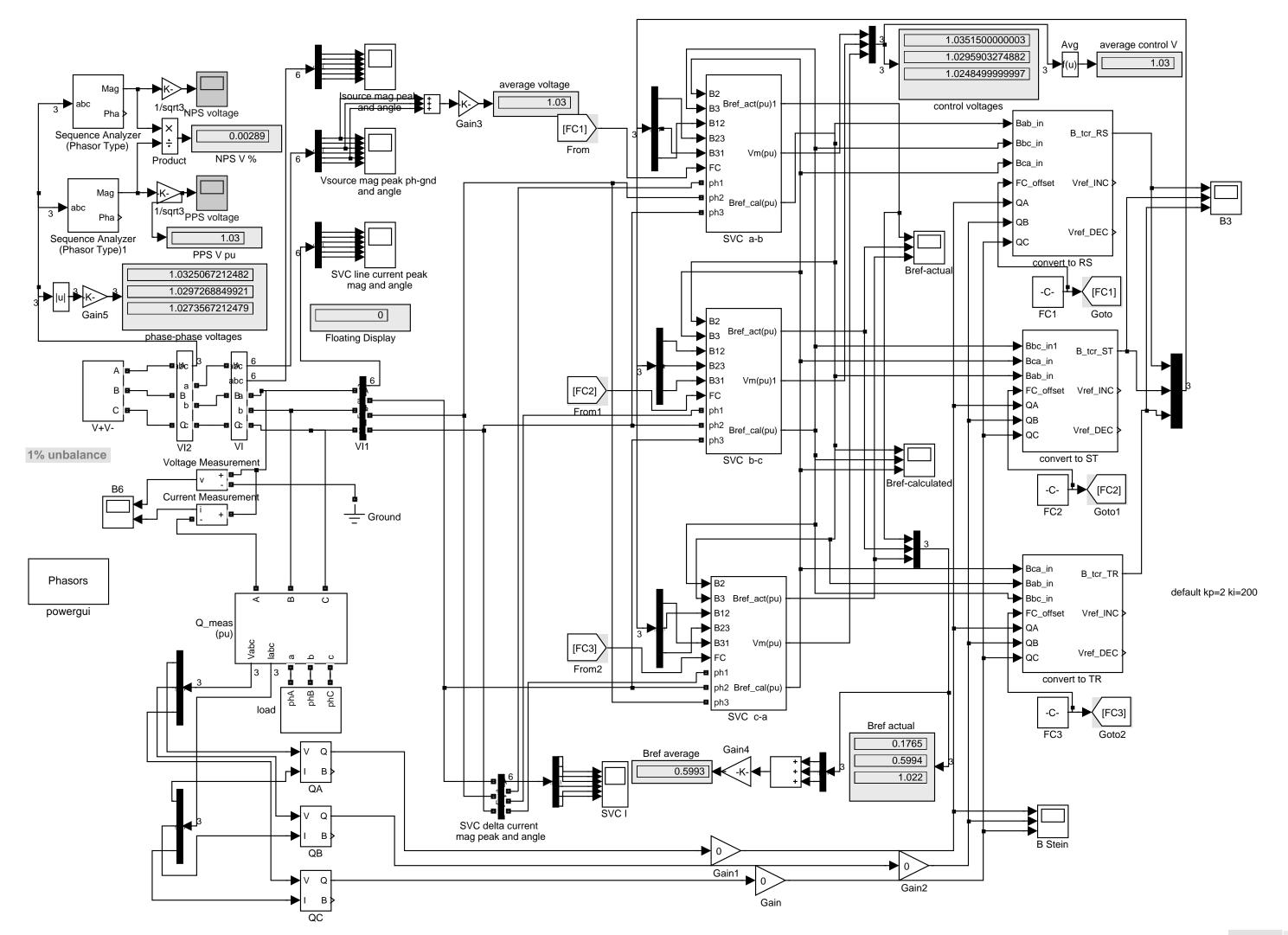

|    | 5.2  |          | ric control system model           | 52 |

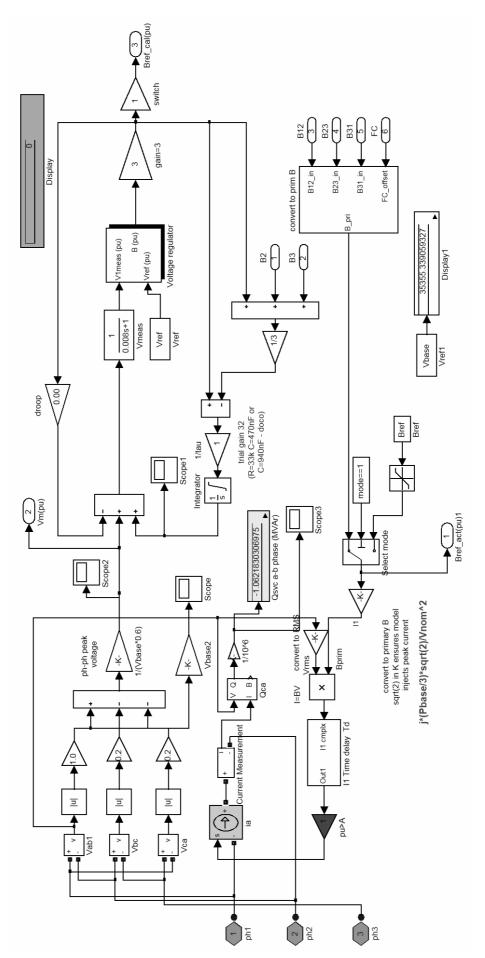

|    |      | 5.2.1    | Voltage Regulation                 | 67 |

|    |      | 5.2.2    | PI Controller                      | 68 |

|    |      | 5.2.3    | Control signal generation          | 69 |

|    |      | 5.2.4    | System load                        | 70 |

|    |      |          |                                    |    |

|      | 5.3    | Blackv    | vater SVC control system model     | 71  |

|------|--------|-----------|------------------------------------|-----|

|      |        | 5.3.1     | System Load                        | 71  |

|      |        | 5.3.2     | Voltage reference                  | 72  |

|      |        | 5.3.3     | SVC slope                          | 72  |

|      |        | 5.3.4     | Fixed capacitor offset             | 73  |

|      |        | 5.3.5     | Voltage Response                   | 78  |

|      |        | 5.3.5     | PI Controller                      | 83  |

|      | 5.4    | Theore    | etical Results                     | 54  |

|      |        | 5.4.1     | Voltage Response                   | 85  |

|      |        | 5.3.2     | Unbalanced Load Response           | 87  |

| 6.   | Ехр    | eriment   | tal Results                        | 89  |

|      | 6.1    | Measu     | urement of Control System Response | 89  |

|      | 6.2    | Wavef     | forms                              | 93  |

|      | 6.3    | Wavef     | form Processing                    | 95  |

|      |        | 6.3.1     | Data Acquisition                   | 95  |

|      |        | 6.3.2     | MATLAB                             | 95  |

| 7.   | Mod    | el Valid  | dation                             | 96  |

|      | 7.1    | Introdu   | uction                             | 96  |

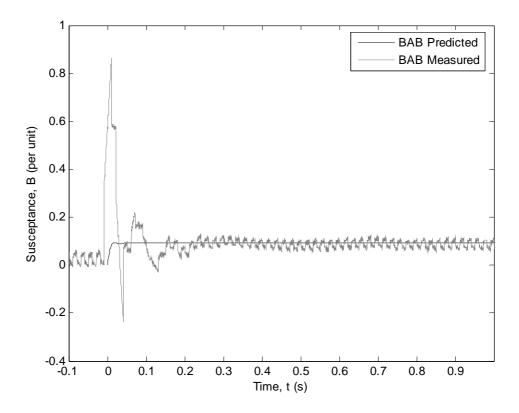

|      | 7.2    | Initial ( | Comparison                         | 97  |

|      | 7.3    | Valida    | tion of Voltage Regulation model   | 99  |

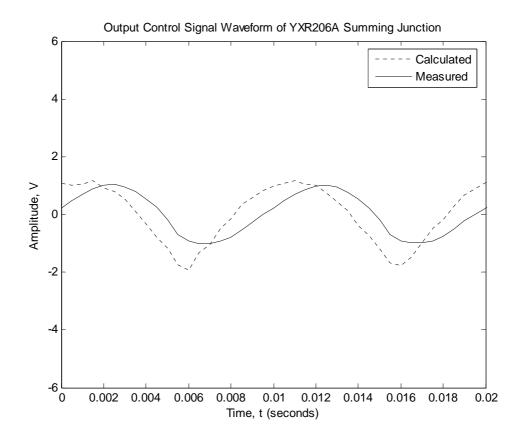

|      |        | 7.3.1     | Signal summation                   | 99  |

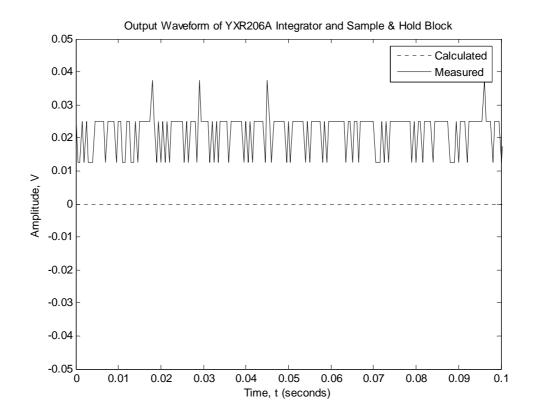

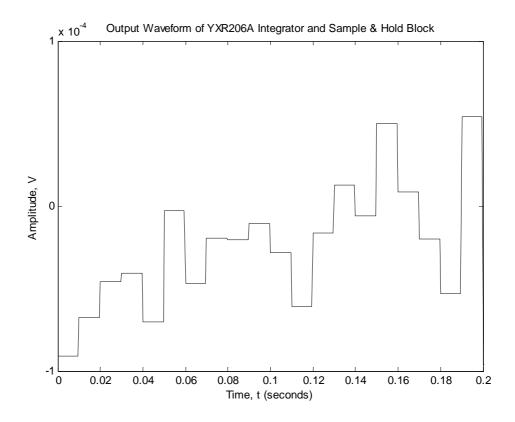

|      |        | 7.3.2     | Integration and Sampling           | 101 |

|      |        | 7.3.3     | Conclusion                         | 102 |

|      | 7.4    | Theore    | etical Model Adjustment            | 103 |

|      | 7.5    | Valida    | tion of Results                    | 104 |

| 0    | Can    | clusion   |                                    | 106 |

| 8.   |        |           |                                    | 106 |

|      | 8.1    |           | vement of project objectives       | 106 |

|      | 8.2    | -         | et outcomes                        | 108 |

|      | 8.3    | Furthe    | r Work                             | 109 |

| Refe | erence | S         |                                    | 111 |

| Appendix A - Project Specification                                         | 114 |

|----------------------------------------------------------------------------|-----|

| Appendix B - Voltage Excursion Waveforms                                   | 116 |

| Appendix C - Manufacturer's Abridged Schematics                            | 119 |

| Appendix D - Generic Control System Model                                  | 131 |

| Appendix E - Blackwater SVC Control System Settings                        | 134 |

| Appendix F - Model Theoretical Response Waveforms                          | 136 |

| Appendix G - Measured Control System Response Waveforms                    | 145 |

| Appendix H - MATLAB Code for Algorithm Validation                          | 157 |

| Appendix I - Blackwater SVC Control System Model                           | 174 |

| Appendix J - Comparison of Predicted and Measured Control System Responses | 177 |

| Appendix K - Voltage Regulation Relevant Standards and Codes               | 183 |

# **List of Figures**

|      |                                                                     | Page |

|------|---------------------------------------------------------------------|------|

| 1.1  | Blackwater 132kV Bus Voltage (Jones, R 2005)                        | 1    |

| 1.2  | Electrical Power Supply System Interconnection (ESAA 2002, p. 5)    | 4    |

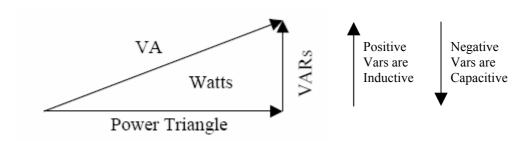

| 1.3  | Relationship between Active, Apparent and Reactive Power (ABB 1999a | n) 6 |

| 1.4  | Short Duration Voltage Disturbances (ESAA 2002, p. 44)              | 8    |

| 1.5  | Sustained System Overvoltage limits (NEC, p. 50)                    | 9    |

| 1.6  | Power Factor and Corrected Power Factor                             | 12   |

| 1.7  | Voltage Notching (ESAA 2002, p. 50)                                 | 13   |

| 1.8  | Power System Harmonics (ESAA 2002, p. 48)                           | 13   |

| 1.9  | Power Triangle                                                      | 15   |

| 1.10 | Power System equivalent circuit                                     | 16   |

| 1.11 | Power System compensation equivalent circuit                        | 16   |

| 1.12 | Power Transfer                                                      | 17   |

| 1.13 | Power Transmission Capability                                       | 18   |

| 2.1  | TSC and TCR line diagram (ABB 1999a0                                | 19   |

| 2.2  | Thyristor Controlled Reactor Current Waveform (ABB 1999a)           | 20   |

| 2.3  | TCR Characteristic (ABB 1999b)                                      | 21   |

| 2.4  | TCR fundamental current and Harmonic Magnitude (ABB 1999a)          | 22   |

| 2.5  | V/I performance of TSC (ABB 1999b)                                  | 23   |

| 2.6  | V/I performance of TCR with/without Filter (ABB 1999a)              | 24   |

| 2.7  | Combined TCR/TSC Characteristic (ABB 1999b)                         | 25   |

| 2.8  | Single line drawing of Typical SVCs (Janke 2002, p. 6)              | 27   |

| 2.9  | Load Balancing SVC location (ABB 1998)                              | 30   |

| 2.10 | Positive and Negative Sequence Voltage Balancing (ABB 1998)         | 31   |

| 2.11 | Typical Traction Substation Arrangement (Janke 2002, p. 13)         | 32   |

| 2.12 | Phasor Representation of Balancing Single Phase Loading             | 33   |

| 2.13 | Blackwater SVC Single Line Diagram (Powerlink 2005)                 | 34   |

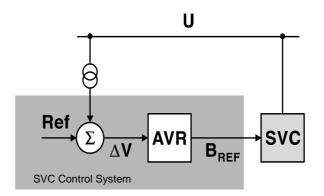

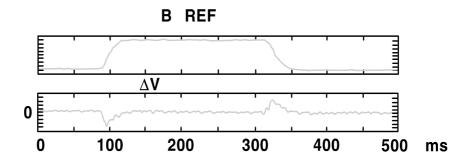

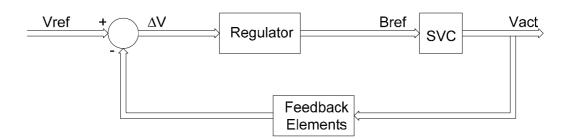

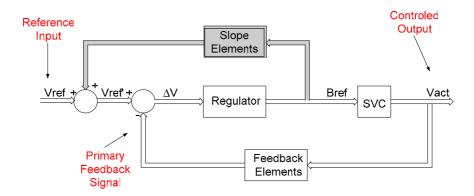

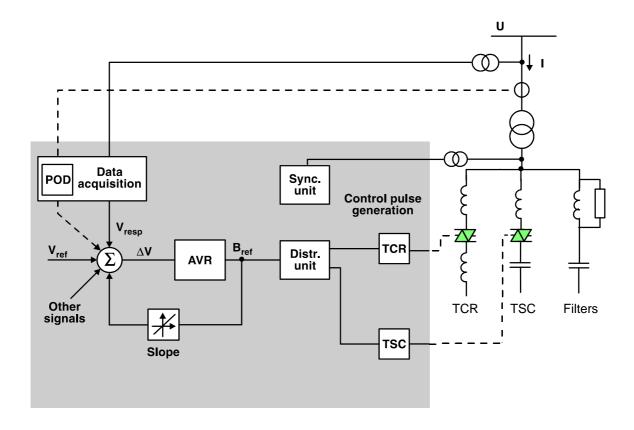

| 3.1  | SVC Control System Overview (ABB 1999b)                             | 36   |

| 3.2  | Basic SVC Control System Composition (ABB 1999b)                    | 37   |

| 3.3  | Basic Closed Loop SVC Control (ABB 1999b)                           | 38   |

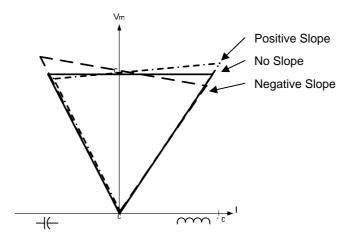

| 3.4  | Slope Correction (ABB 1999b)                                        | 39   |

| 3.5  | Closed Loop SVC Control with Slope Correction (ABB 1999a)           | 39   |

|      |                                                                              | Page |

|------|------------------------------------------------------------------------------|------|

| 3.6  | I/O signals associated with typical SVC control system (ABB 1999a)           | 40   |

| 3.7  | Load Balancing SVC Control System                                            | 42   |

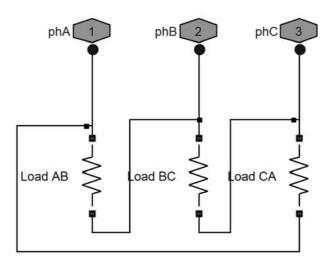

| 3.8  | Single Phase Loading (ABB 1998)                                              | 43   |

| 3.9  | Symmetrizing of Single Phase Loads (Janke 2002, p. 45)                       | 44   |

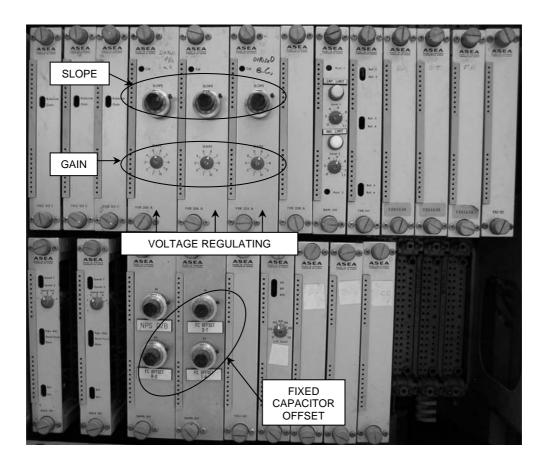

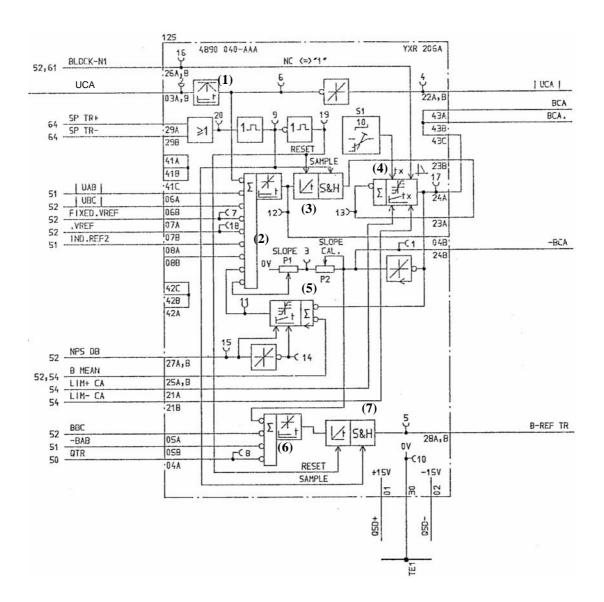

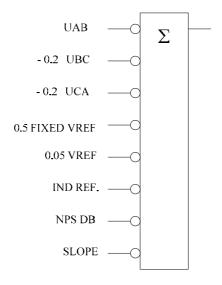

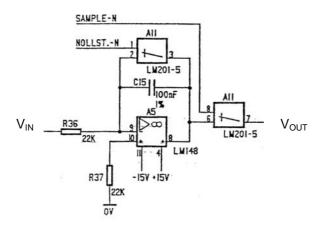

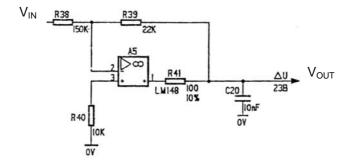

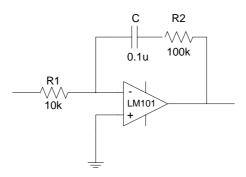

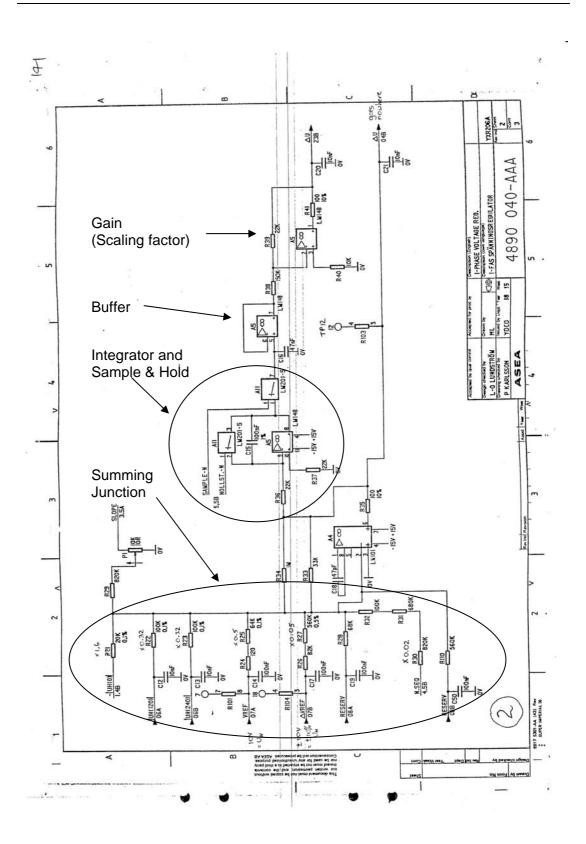

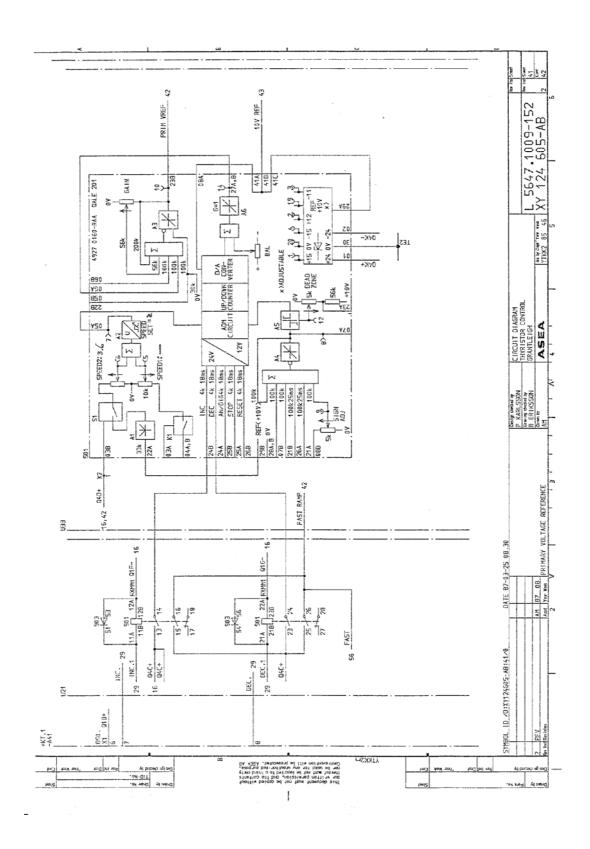

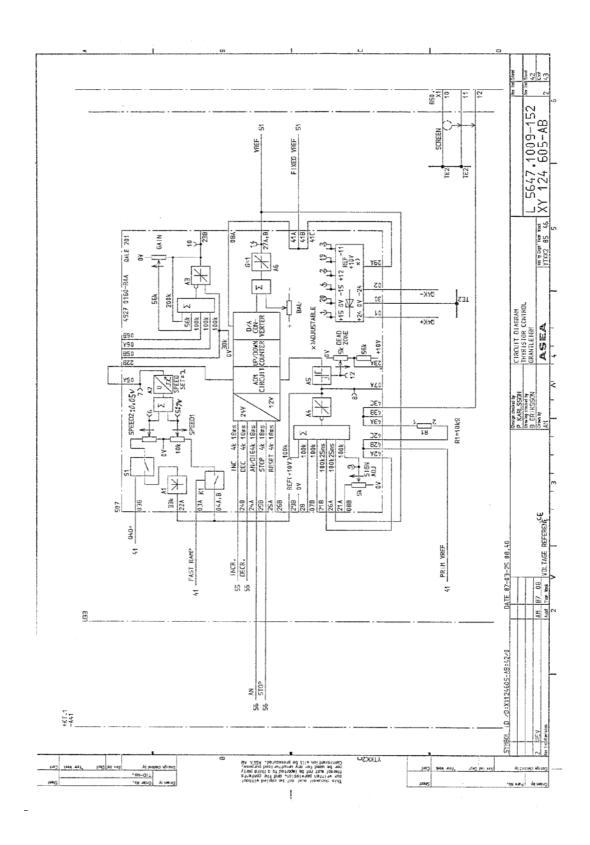

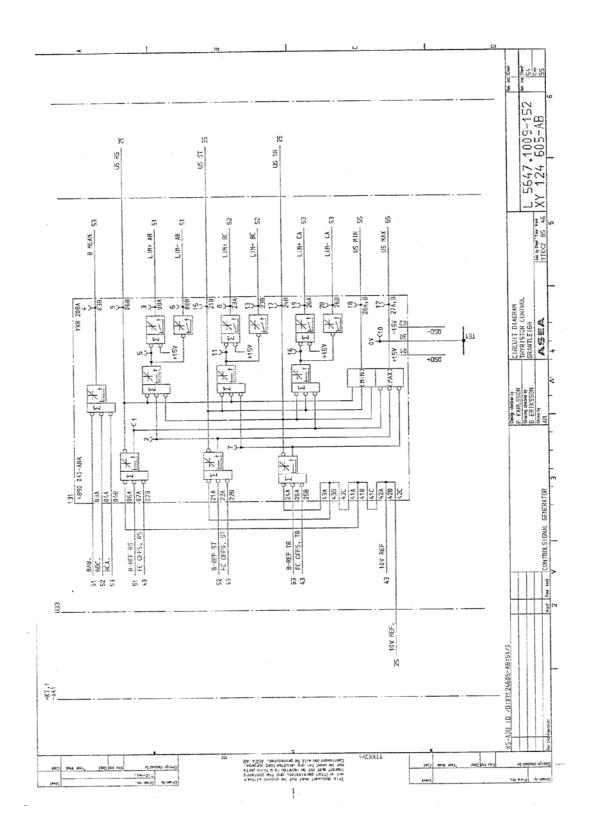

| 3.10 | C – A Ø Closed Loop Voltage Regulation Card Abridged Schematic               | 53   |

|      | (ASEA 1986, p. 15).                                                          |      |

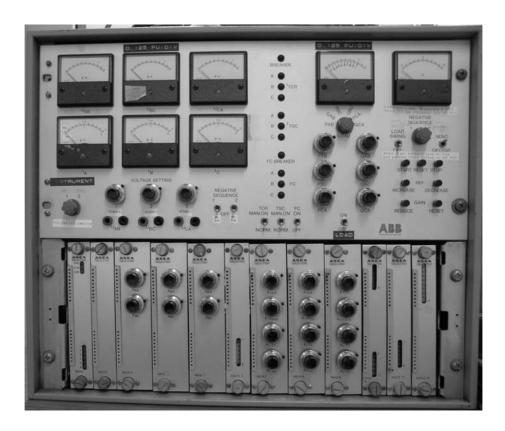

| 4.1  | ABB Power System Simulator                                                   | 61   |

| 5.1  | 132 kV Bus Voltage at Nebo and Blackwater Substations, 22 May 2004           | 65   |

| 5.2  | Generic Control System Model Voltage Regulation Block A-B Phase              | 67   |

| 5.3  | Generic Control System Model PI Controller Block A-B Phase                   | 68   |

| 5.4  | Generic Model Interface and Steinmetz Block A-B Phase                        | 69   |

| 5.5  | Control System Model Three Phase Load                                        | 70   |

| 5.6  | Fixed Capacitor Offset                                                       | 73   |

| 5.7  | Blackwater SVC Component Values                                              | 74   |

| 5.8  | Single Phase of SVC Tuned Filter                                             | 75   |

| 5.9  | Calculation of Fixed Capacitor Offset Value                                  | 77   |

| 5.10 | A-B Phase Voltage Regulation Card YXR 206A Summing Junction                  | 78   |

| 5.11 | Voltage Regulation Card YXR 206A Integrator, Sample and Hold Circuit         | 80   |

| 5.12 | Voltage Regulation Card YXR 206A Gain Circuit                                | 82   |

| 5.13 | Voltage Regulator PI Controller                                              | 83   |

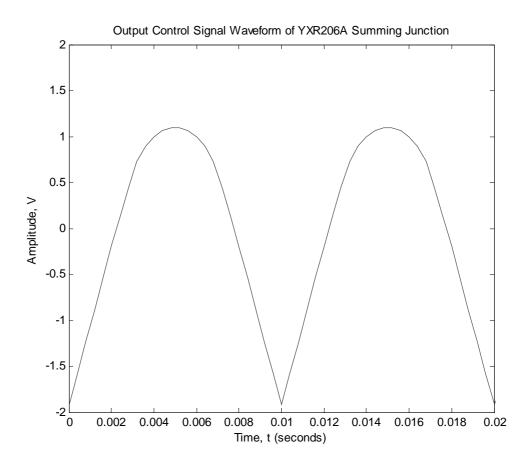

| 5.14 | One Cycle Simulation of YXR 206A Test Point TP12                             | 85   |

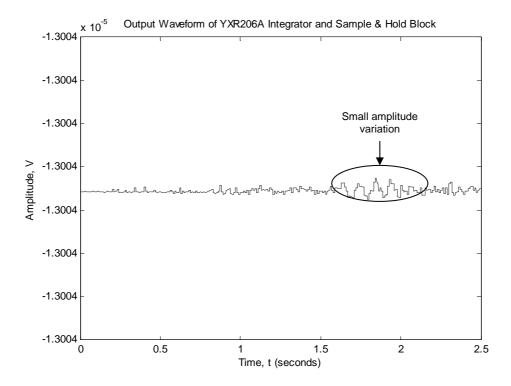

| 5.15 | One Cycle Simulation of YXR 206A Test Point TP13                             | 86   |

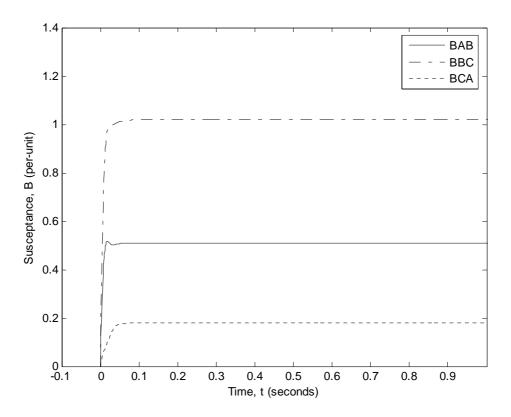

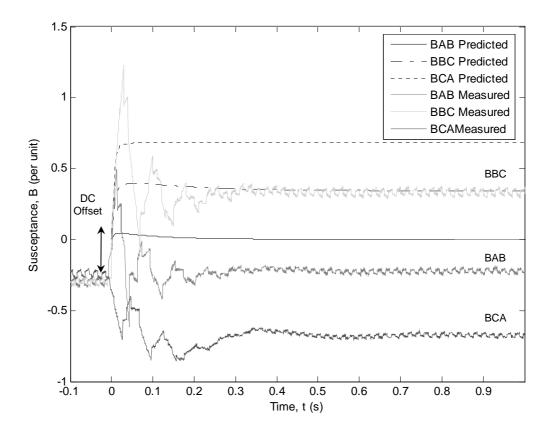

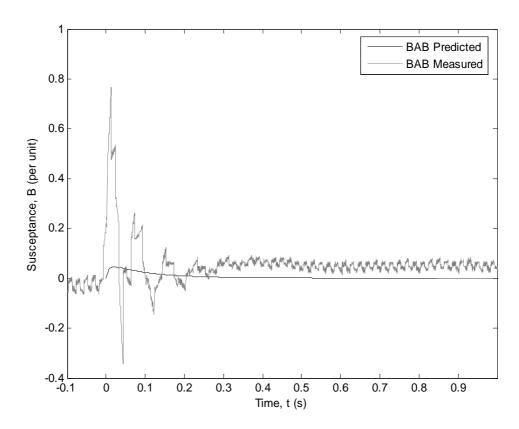

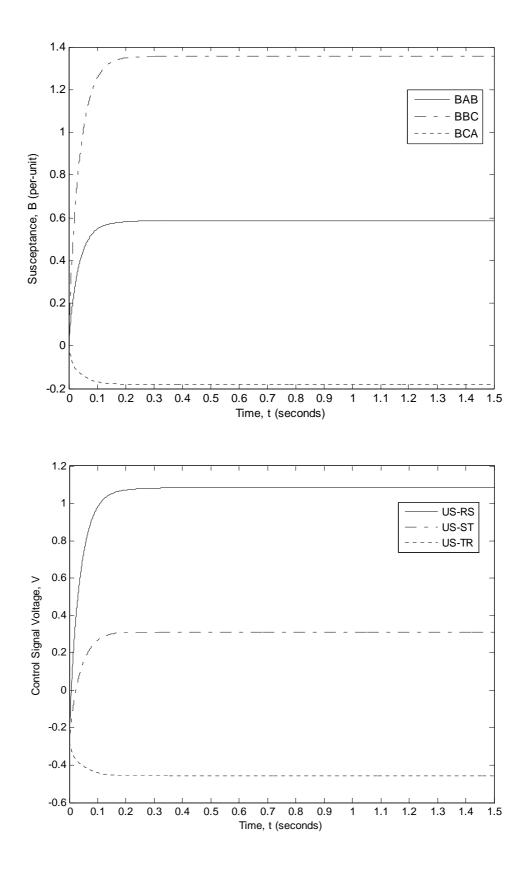

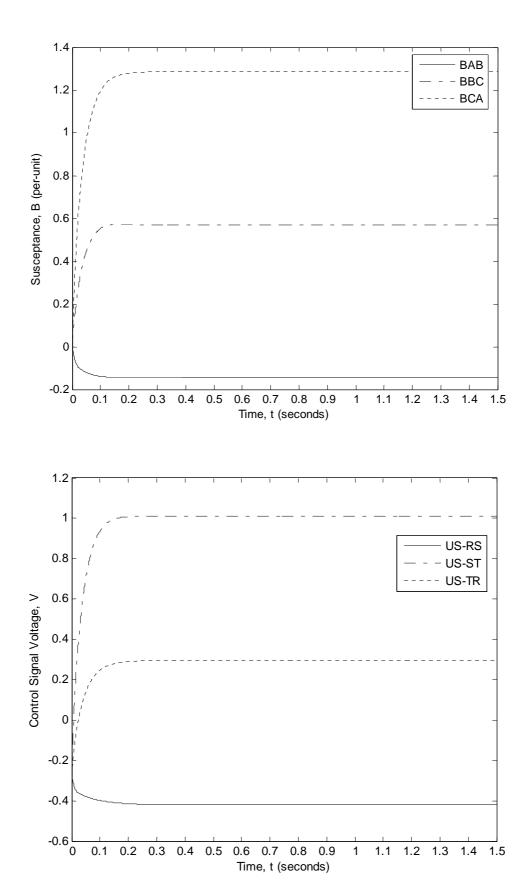

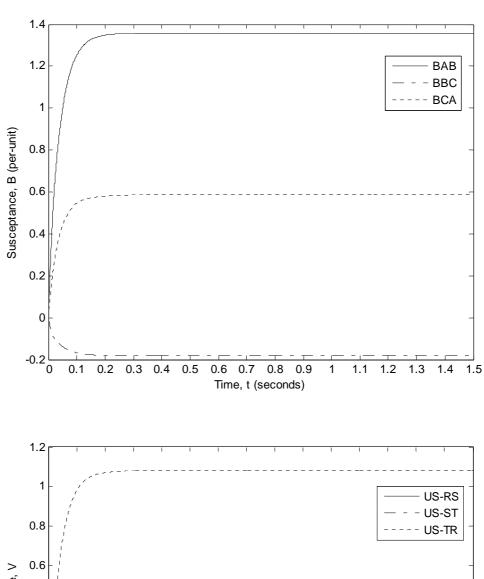

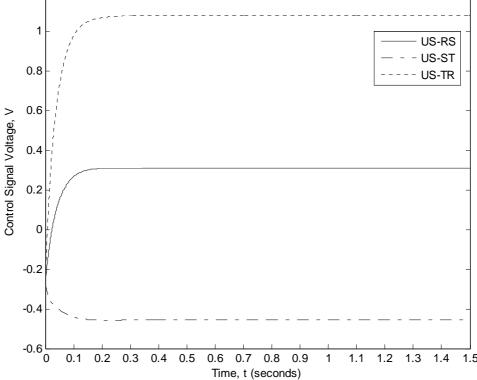

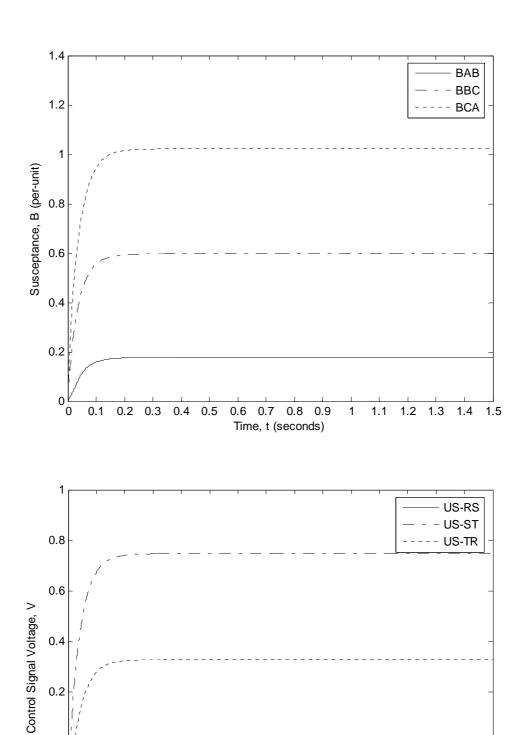

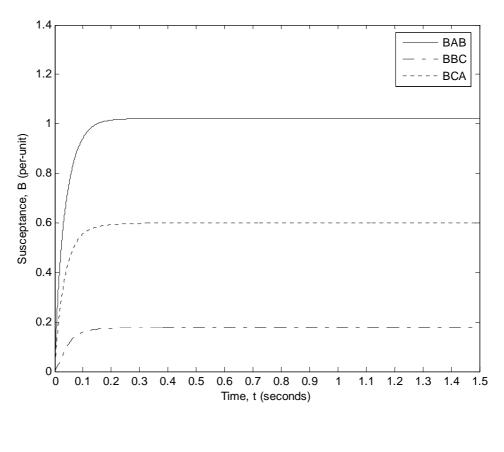

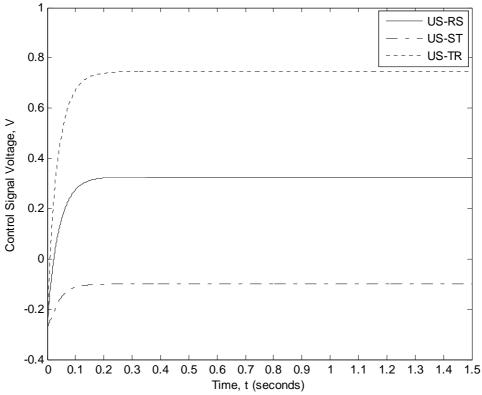

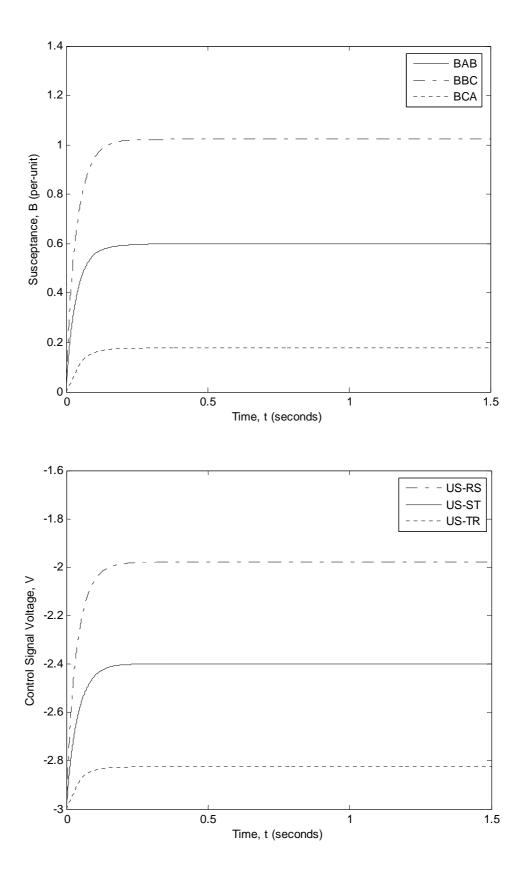

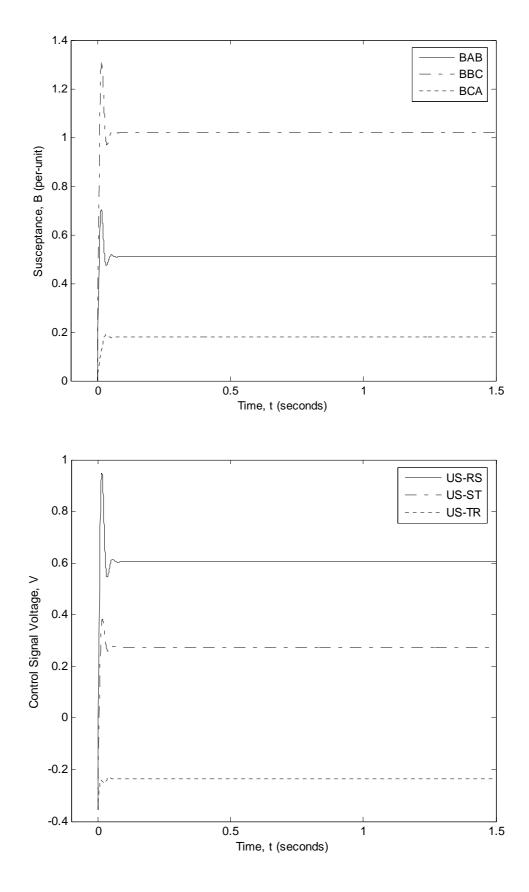

| 5.16 | Voltage Regulator Calculated Susceptance Response to Step Unbalanced Loading | 87   |

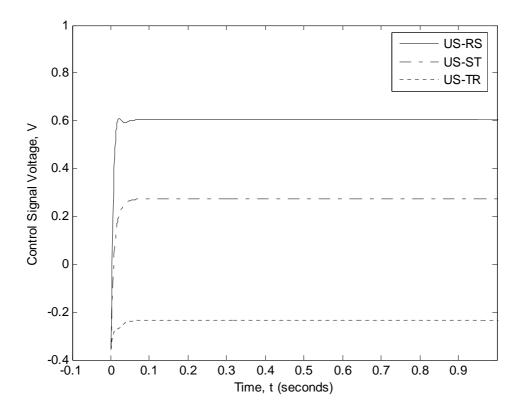

| 5.17 | Control Signal Voltage US Response to Step Unbalanced Loading                | 88   |

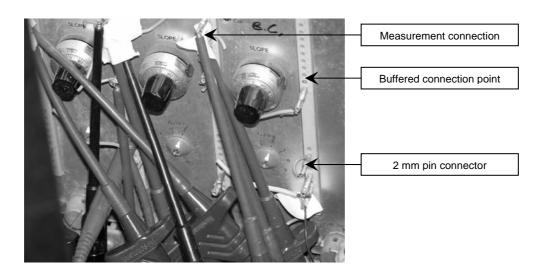

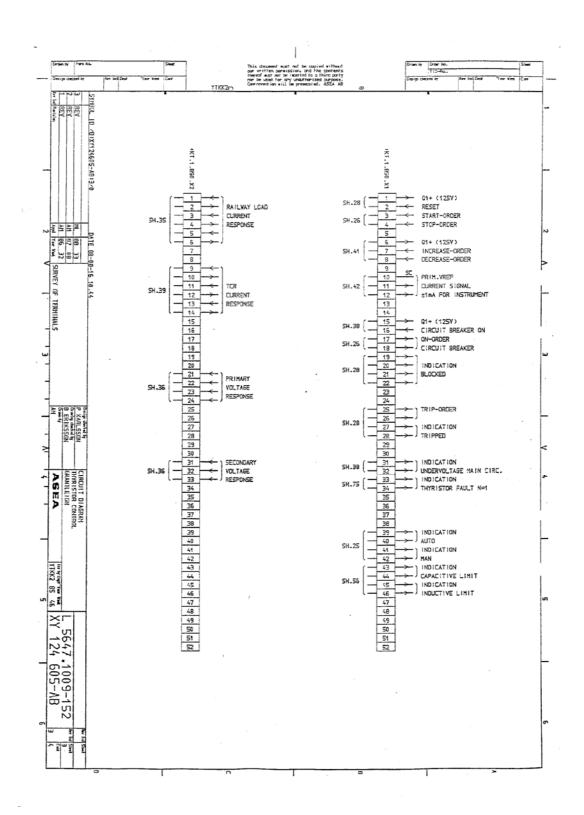

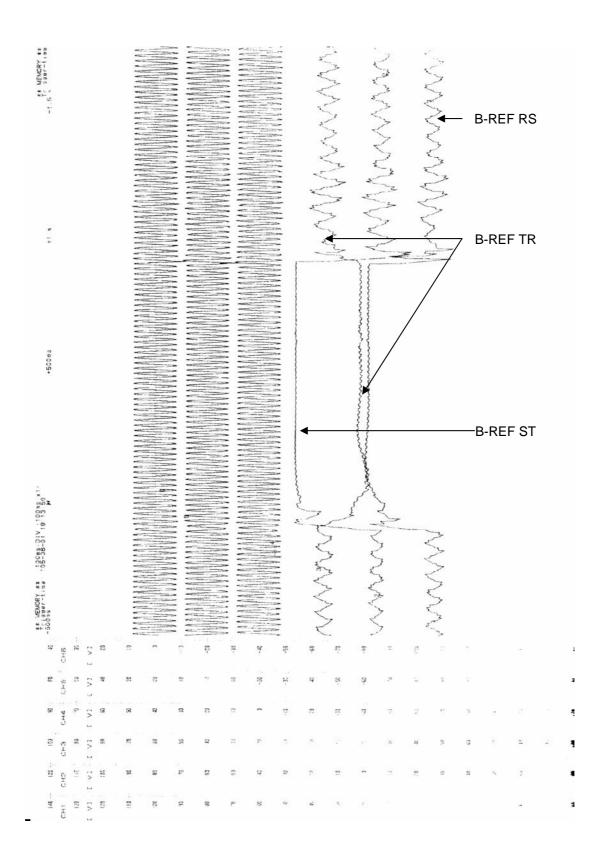

| 6.1  | Connection of Measurement Leads to Voltage Regulation Card YXR 206A          | 89   |

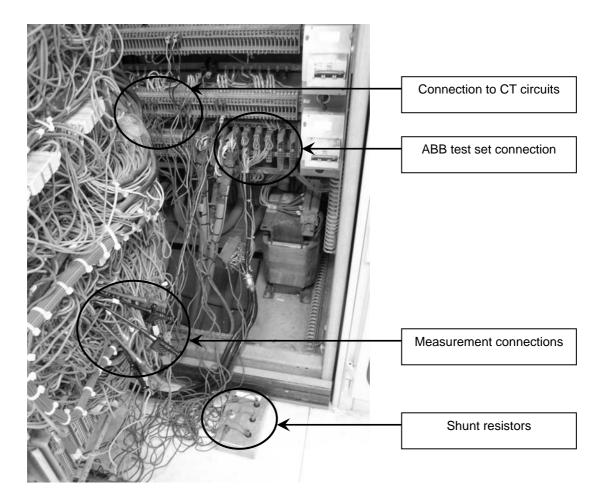

| 6.2  | Connection of ABB Test Set to SVC Control System                             | 90   |

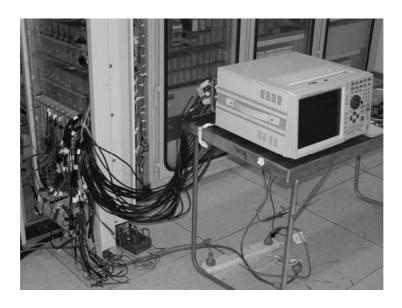

| 6.3  | Connection of Hioki Chart Recorder to the SVC Control System                 | 91   |

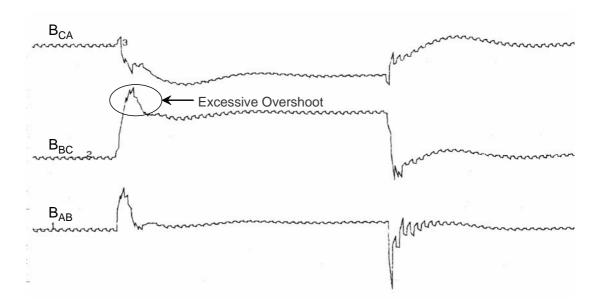

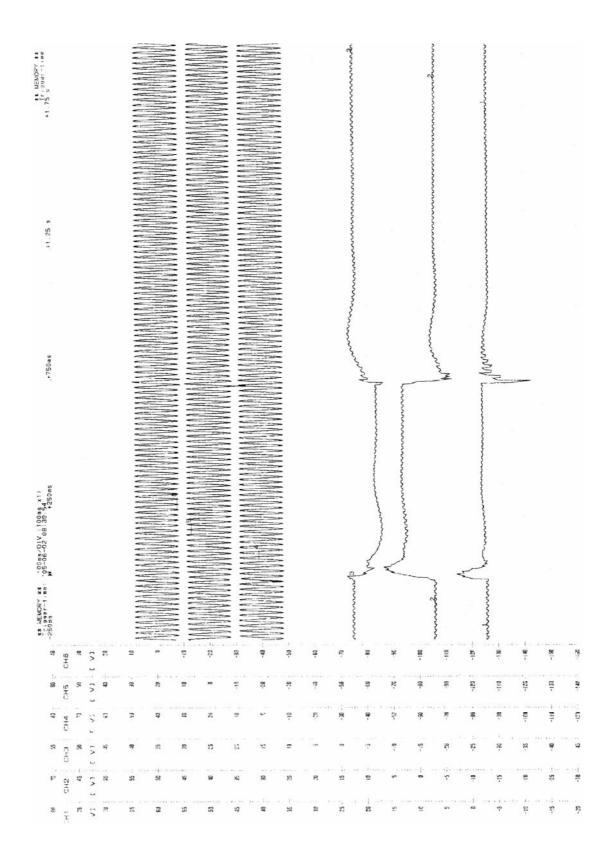

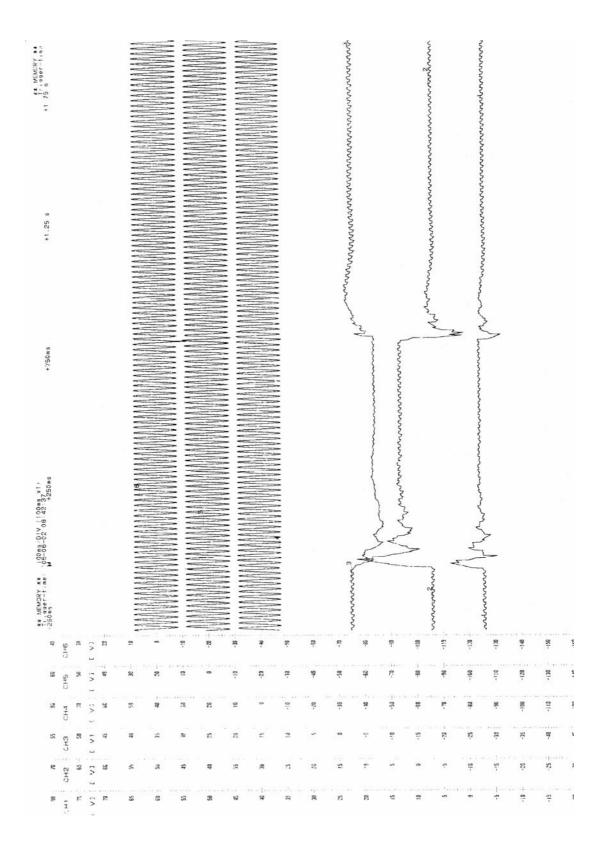

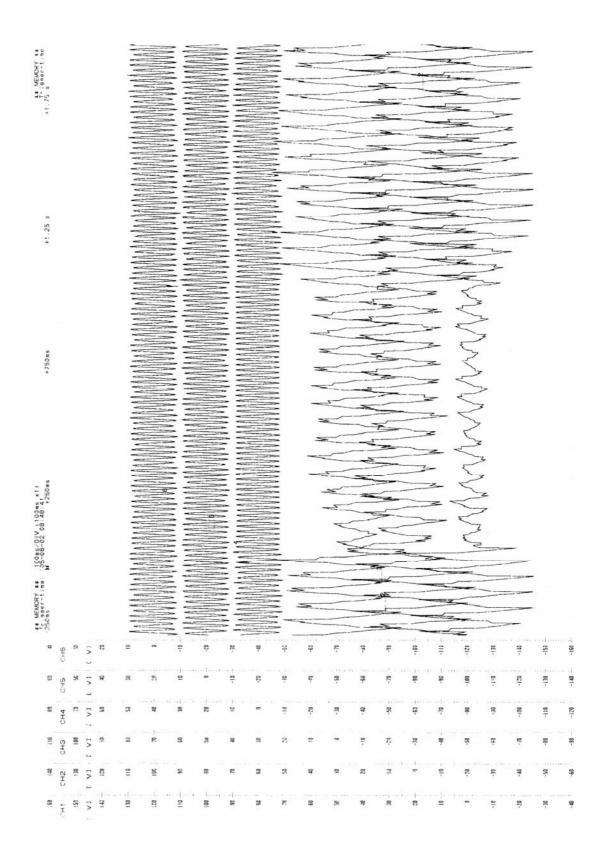

| 6.4  | SVC Control System Measured Susceptance Response to Load Imbalance           | 93   |

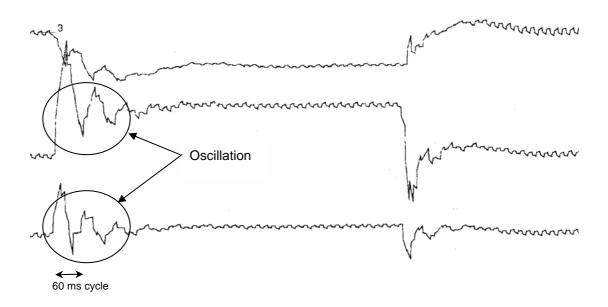

| 6.5  | SVC Control System Load Imbalance Response Oscillation                       | 94   |

(Kp = 1.0, Ki = 100)

|             |                                                                                          | Page |

|-------------|------------------------------------------------------------------------------------------|------|

| F.5         | Model Response to Step Unbalanced Load Applied to C-A $\varnothing$ (Kp = 1.0, Ki = 100) | 141  |

| F.6         | Model Response to Step Unbalanced Load Applied to A-B $\varnothing$ (Kp = 1.0, Ki = 100) | 142  |

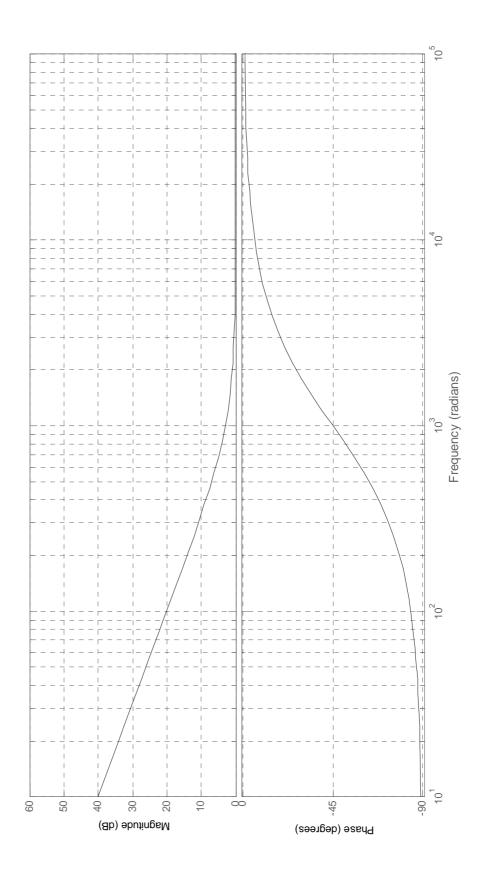

| F.7         | PI Controller Transfer Function Bode Plot                                                | 143  |

| F.8         | Model Response to Step Unbalanced Load Applied to A-B $\varnothing$ (Kp = 10, Ki = 1000) | 144  |

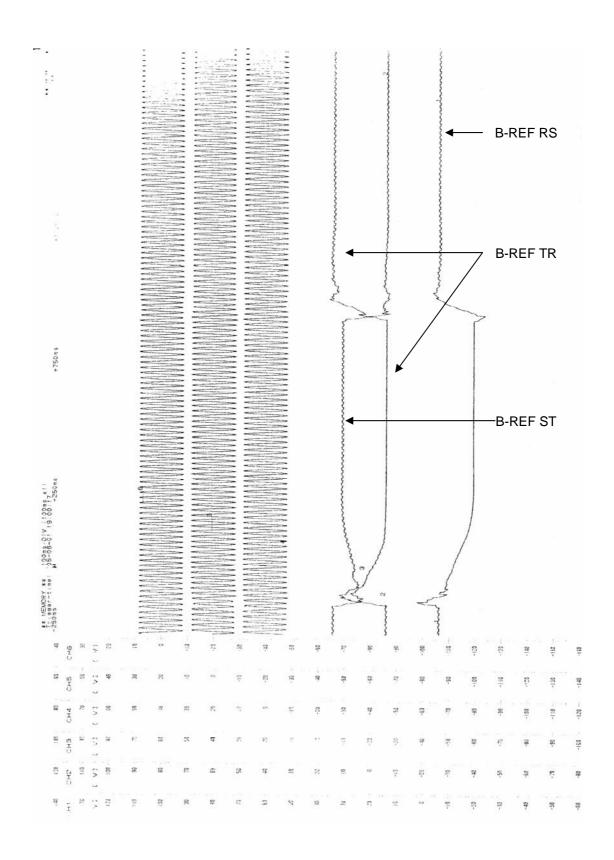

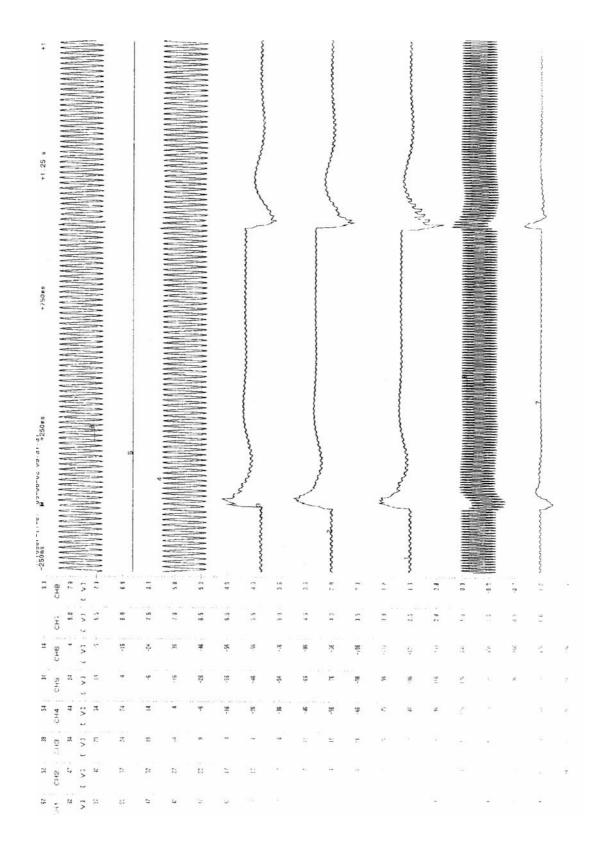

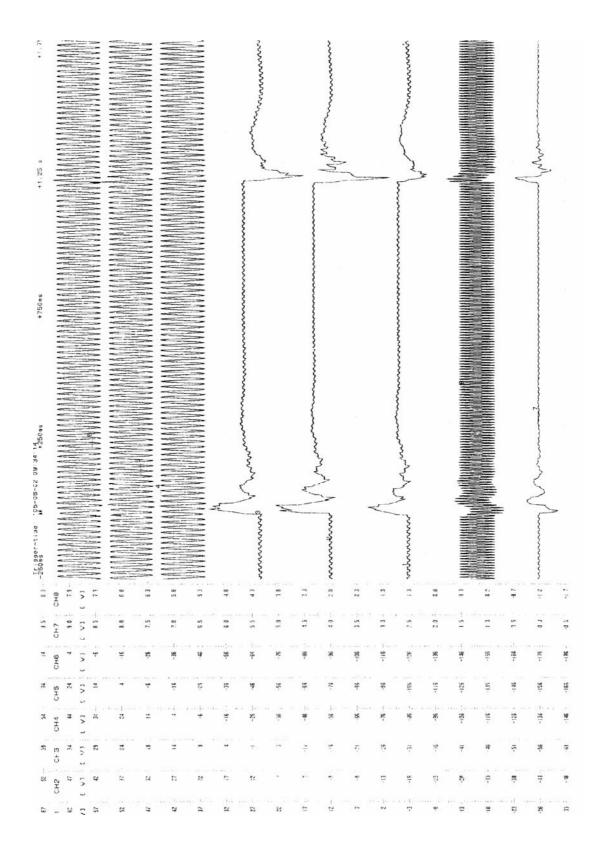

| G.1         | Control system calculated susceptance response to load imbalance,                        | 146  |

|             | Gain = 5.                                                                                |      |

| G.2         | Control system calculated susceptance response to load imbalance,                        | 147  |

|             | Gain = 6.                                                                                |      |

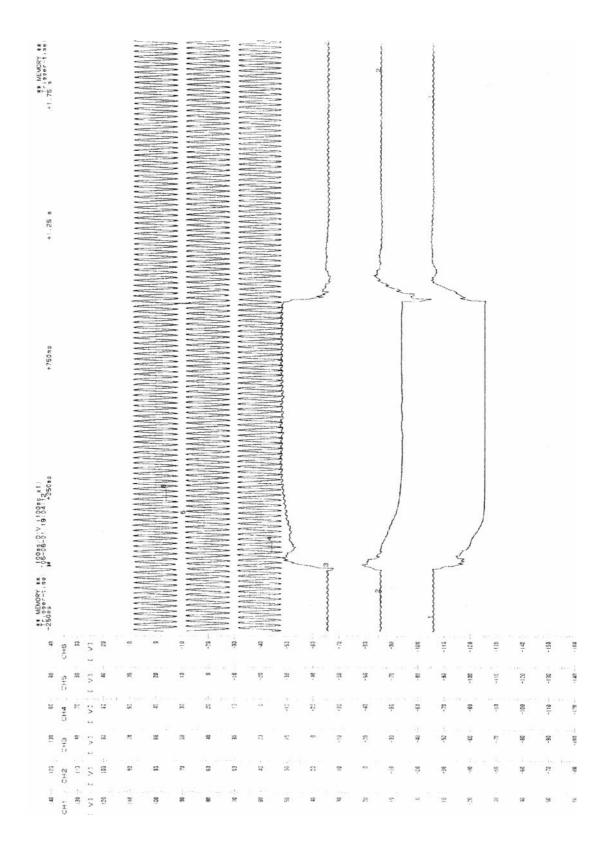

| G.3         | Control system calculated susceptance response to load imbalance,                        | 148  |

|             | Gain = 7.                                                                                |      |

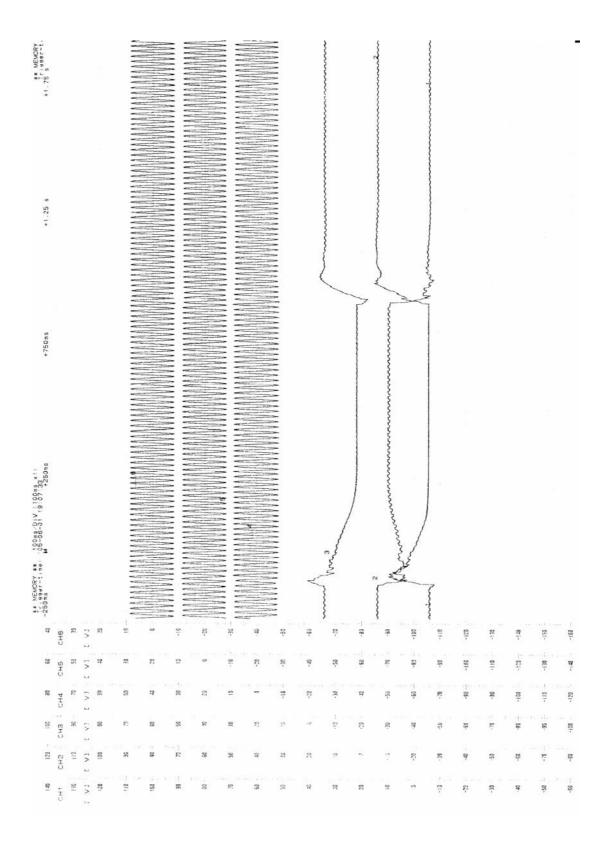

| G.4         | Calculated susceptance response to 0.5 pu step input A-B $\varnothing$ , Gain = 6.       | 149  |

| G.5         | Calculated susceptance response to 0.5 pu step input B-C $\varnothing$ , Gain = 6.       | 150  |

| G.6         | Calculated susceptance response to 0.5 pu step input C-A $\varnothing$ , Gain = 6.       | 151  |

| G.7         | Calculated susceptance response to unbalanced load input, $Gain = 5$ .                   | 152  |

| G.8         | Calculated susceptance response to unbalanced load input, Gain = 6.                      | 153  |

| <b>G</b> .9 | Calculated susceptance response to unbalanced load input, $Gain = 7$ .                   | 154  |

| G.10        | Steinmetz calculated susceptance response to unbalanced load input.                      | 155  |

| G.11        | SVC start sequence.                                                                      | 156  |

|             |                                                                                          |      |

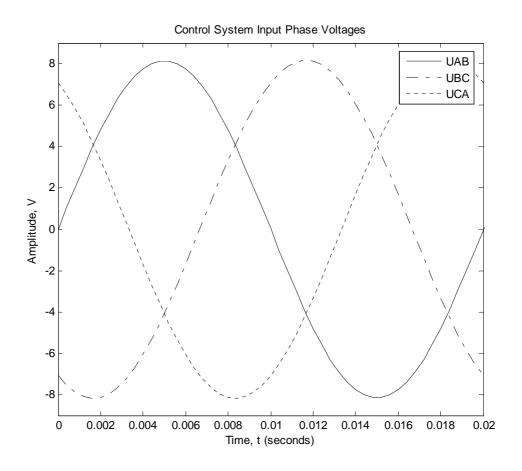

| H.1         | One Cycle Simulation of Ideal Voltage Input                                              | 158  |

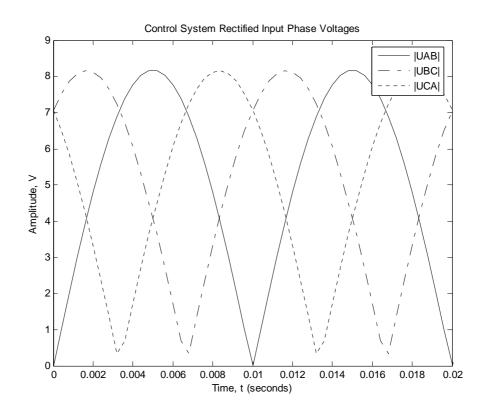

| H.2         | One Cycle Simulation of Ideal Rectified Voltage Input                                    | 159  |

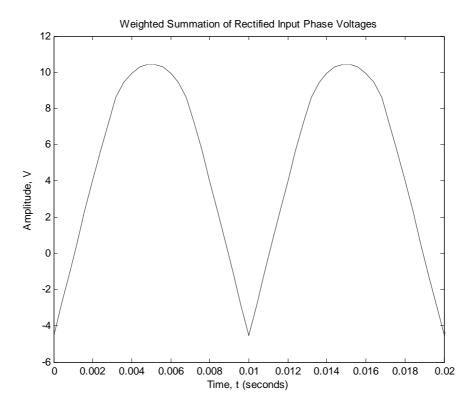

| Н.3         | One Cycle Simulation of Ideal Summated Voltage Input                                     | 159  |

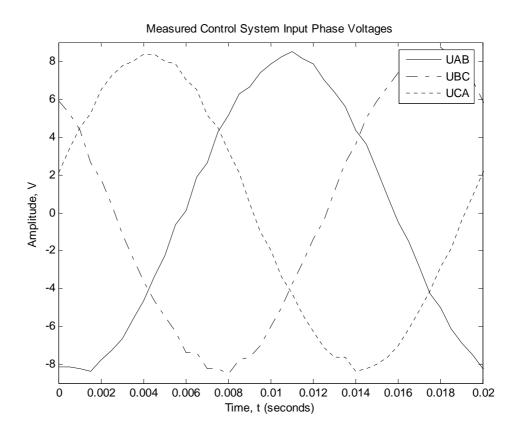

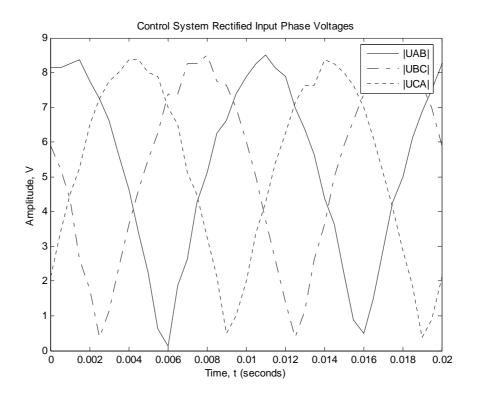

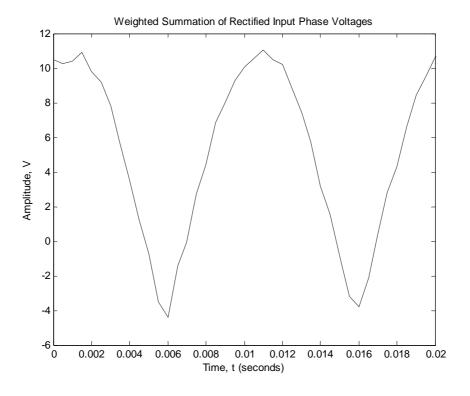

| H.4         | One Cycle of Measured Voltage Input to Control System                                    | 160  |

| H.5         | One Cycle of Calculated Rectification of Measured Voltage                                | 161  |

| H.6         | One Cycle of Calculated Summated Rectified Voltage                                       | 161  |

|     |                                                                  | Page |

|-----|------------------------------------------------------------------|------|

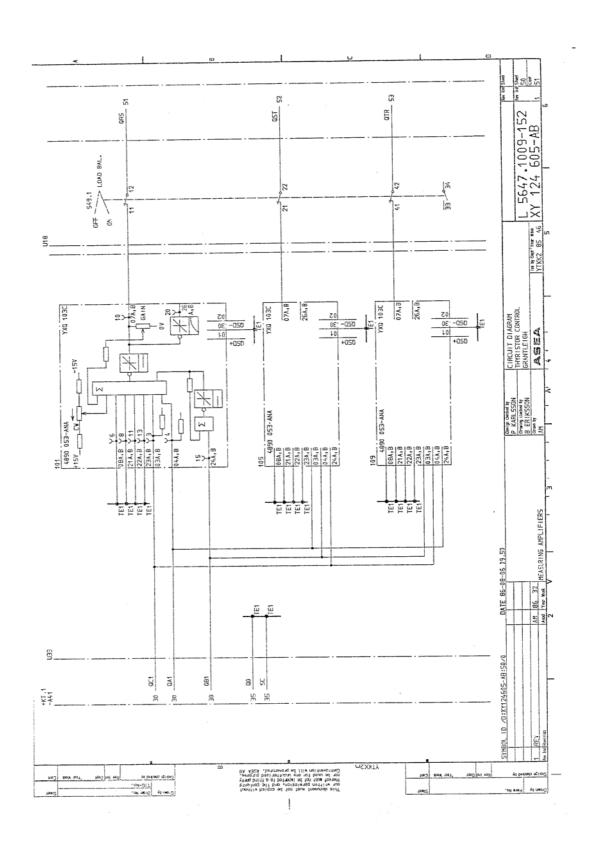

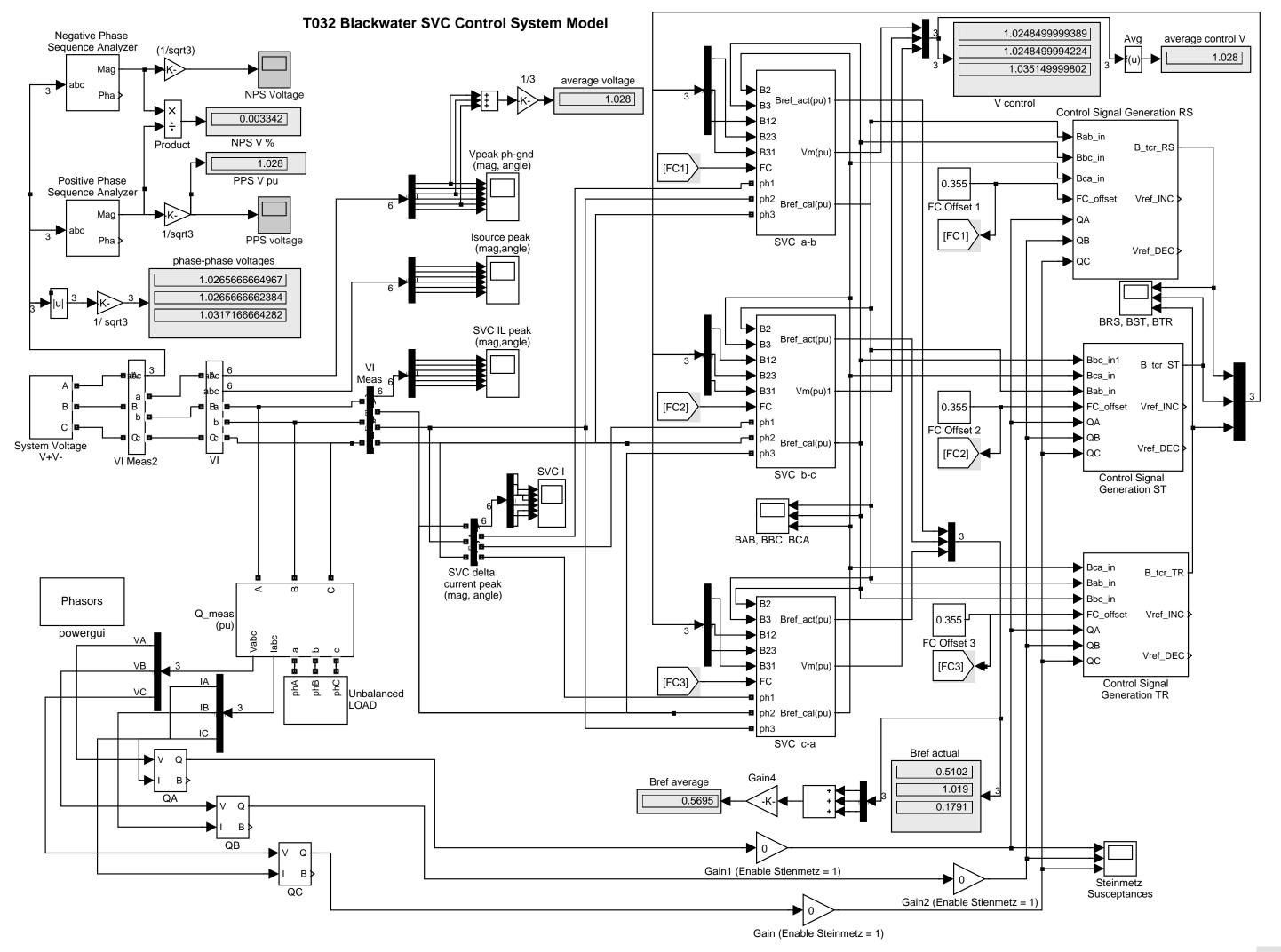

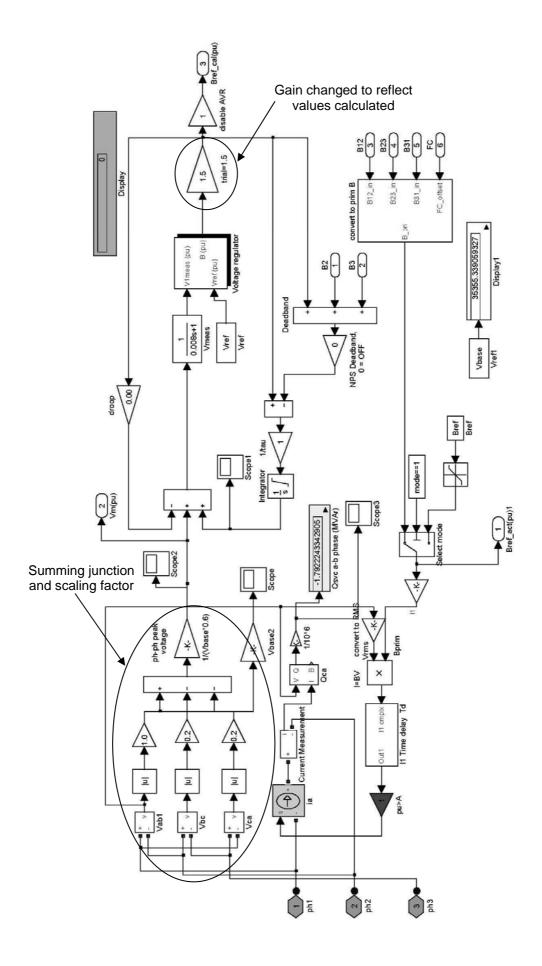

| I.1 | Blackwater SVC Control System Model                              | 175  |

| I.2 | Blackwater SVC Control System Model Voltage Regulation Block     | 176  |

|     |                                                                  |      |

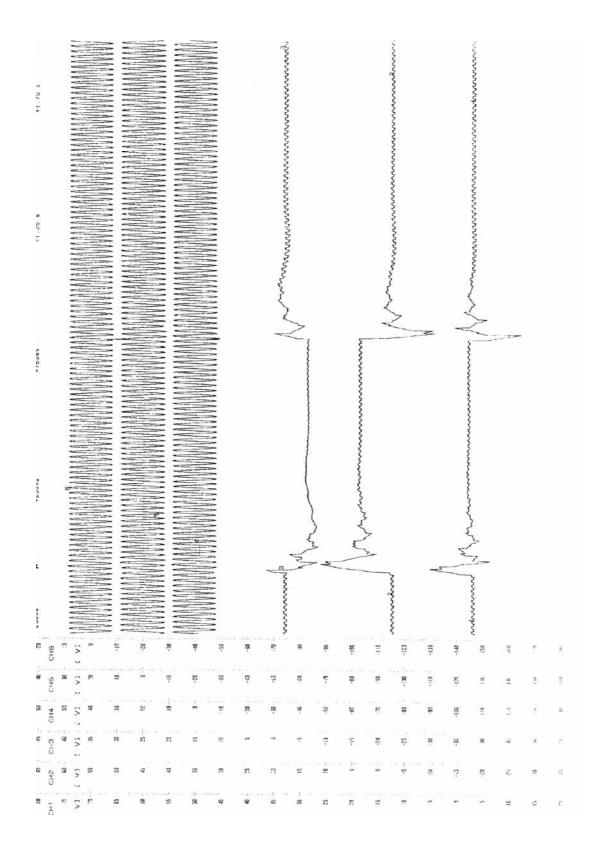

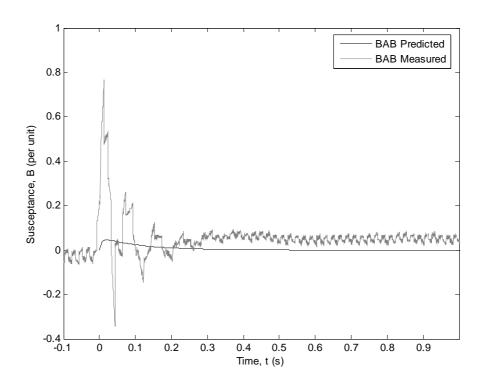

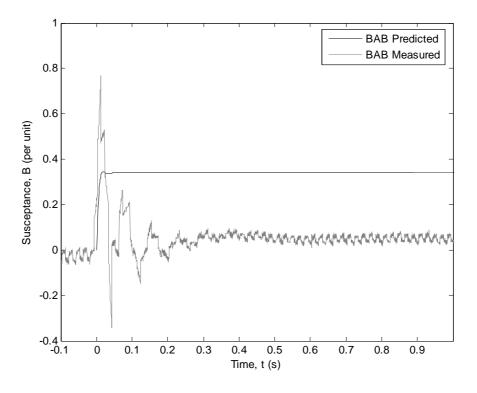

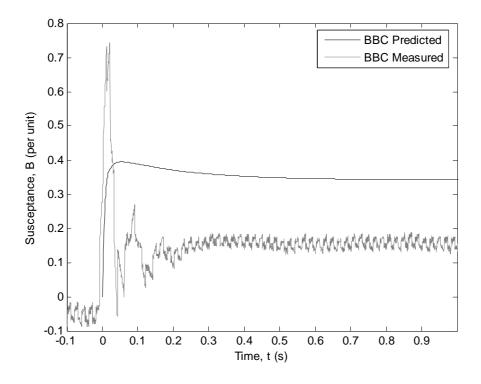

| J.1 | Comparison of A-B Phase Voltage Regulator Predicted and Measured | 178  |

|     | Response to A-B Phase Load Imbalance                             |      |

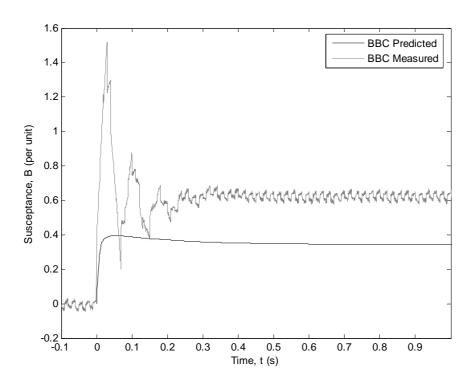

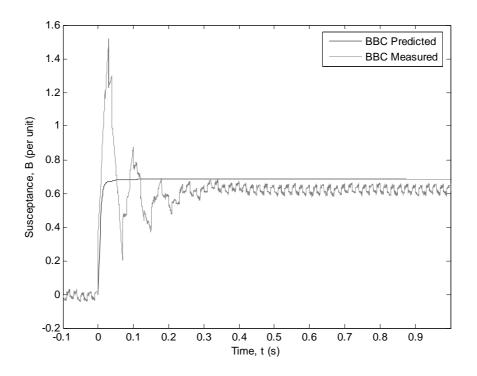

| J.2 | Comparison of B-C Phase Voltage Regulator Predicted and Measured | 178  |

|     | Response to A-B Phase Load Imbalance                             |      |

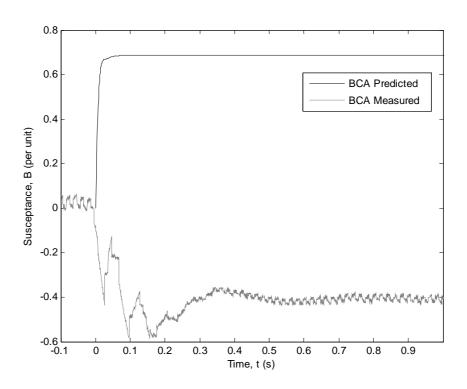

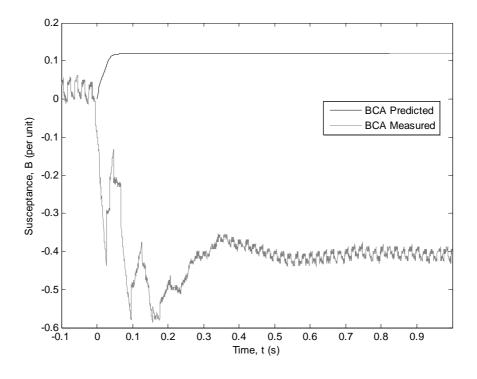

| J.3 | Comparison of C-A Phase Voltage Regulator Predicted and Measured | 179  |

|     | Response to A-B Phase Load Imbalance                             |      |

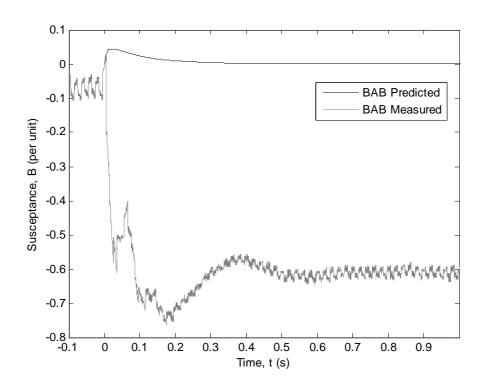

| J.4 | Comparison of A-B Phase Voltage Regulator Predicted and Measured | 179  |

|     | Response to B-C Phase Load Imbalance                             |      |

| J.5 | Comparison of B-C Phase Voltage Regulator Predicted and Measured | 180  |

|     | Response to B-C Phase Load Imbalance                             |      |

| J.6 | Comparison of C-A Phase Voltage Regulator Predicted and Measured | 180  |

|     | Response to B-C Phase Load Imbalance                             |      |

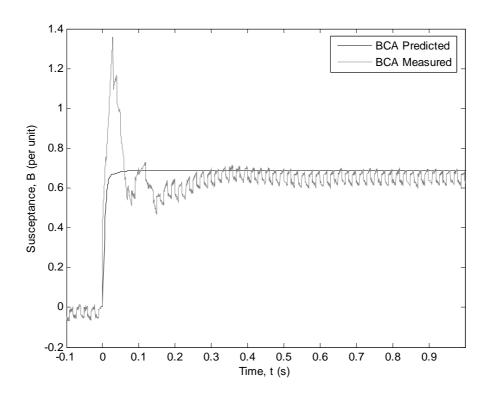

| J.7 | Comparison of A-B Phase Voltage Regulator Predicted and Measured | 181  |

|     | Response to C-A Phase Load Imbalance                             |      |

| J.8 | Comparison of B-C Phase Voltage Regulator Predicted and Measured | 181  |

|     | Response to C-A Phase Load Imbalance                             |      |

| J.9 | Comparison of C-A Phase Voltage Regulator Predicted and Measured | 182  |

|     | Response to C-A Phase Load Imbalance                             |      |

# **List of Tables**

| 1.1 | Frequency Excursions and Restoration times (ESAA 2005, p. 46)               | 10  |

|-----|-----------------------------------------------------------------------------|-----|

| 1.2 | Power Quality Categories and Causes (Ghosh & Ledwich 2002. p. 5)            | 14  |

| 2.1 | Load Balancing SVC Range and Ratings (Janke 2002, p. 41)                    | 33  |

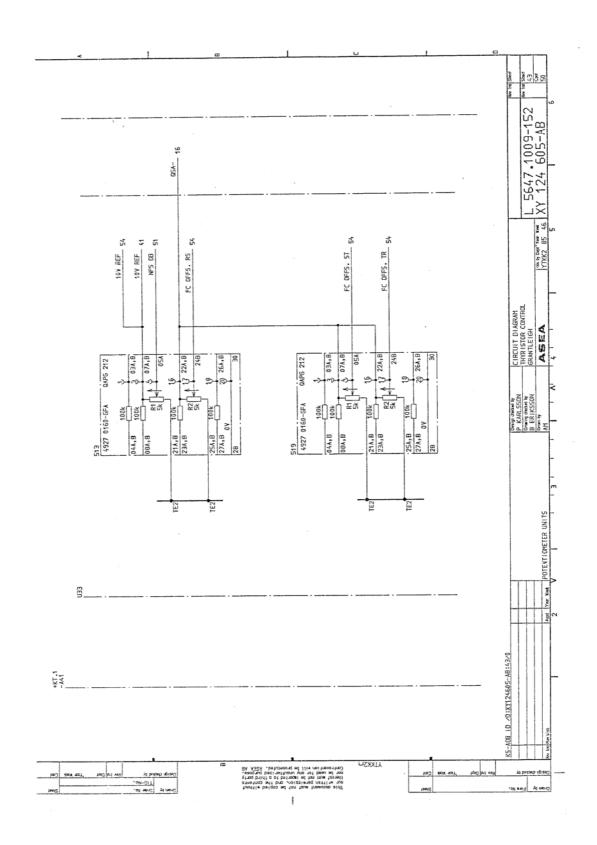

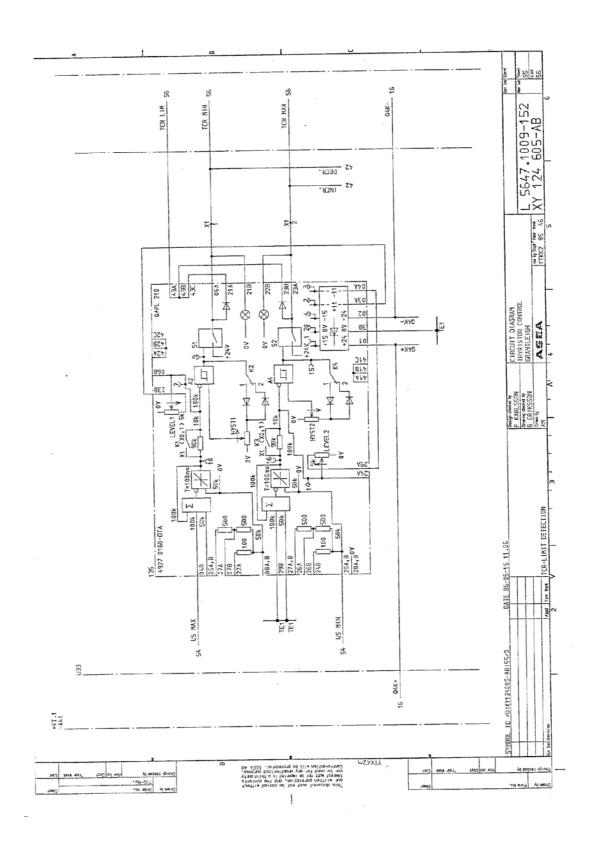

| 3.1 | Identification of ASEA SVC Control System Abridged Schematic Symbols        | 35  |

| 4.1 | Power System Simulator Settings for cards QECS 7, 8, 9 (ASEA 1986, p. E.25) | 62  |

| C.1 | Identification of ASEA Abridged Schematic Non-Standard Symbols              | 120 |

| C.3 | Experimental Test Measurement Points                                        | 130 |

## **Glossary**

AC Alternating current, a sinusoidal waveform of constant

frequency.

Ampere (A) The SI unit of current, defined the amount of current

produced by an electromotive force of 1 V across a

resistance of 1  $\Omega$ .

Bus High capacity conductor used at substations for transfer and

distribution of current. It is usually a hollow copper or

aluminium pipe.

Coulomb The SI unit of charge (Q), defined as the flow of 1 A for one

second.

Current Transformer A transformer with short circuited secondaries used to

proportionally reproduce primary current at a level suitable

for input to protection, control and measurement circuits.

Filter A passive compensation device comprising a combination of

resistance, inductance and capacitance to suppress a specific

power system attribute such as harmonics.

NEC National Electricity Code.

NEMMCO National Electricity Market Management Company.

NPS Negative phase sequence.

NSC Network Switching Centre – the network operational branch

of Powerlink Queensland responsible for authorising and managing access to plant connected to the extra-high voltage

transmission system.

Per unit A method of expressing a quantity as a fraction of a

nominated reference value such as a system voltage,

allowing easy quantity comparison. Abbreviated as 'pu'.

Reactance A measure of component resistance to alternating current as

a function of frequency.

Reactor A passive power compensation device comprised of inductor

coils.

Susceptance A measure defining the ease of transmission of alternating

current through a circuit, with zero indicating an open circuit and infinity indicating a short circuit or no impediment to transmission of AC. Susceptance is the inverse of reactance.

SVC Static Var Compensator.

TCR Thyristor Controlled Reactor.

Thyristor a power electronic device of high voltage rating that acts as a

switch to allow the flow of current through a circuit when a

firing pulse, or 'on' signal, is received.

Traction Load Single phase high voltage load produced by electric trains.

Transmission delay The actual delay between the generation and arrival of an

analog or digital signal.

TSC Thyristor Switched Capacitor.

Var Volt-Ampere reactive, a measure of power consumed by

devices that have reactance.

Voltage Transformer A transformer used to proportionally reduce system voltage

to a measurable level, suitable for input to control or

protection circuits.

Watt A measure of power consumed by devices that have

resistance.

# **Nomenclature**

The following symbols and representations are used throughout the document:

Table 1: Commonly used symbols and representations.

| Symbol                                | Interpretation                     | Units |

|---------------------------------------|------------------------------------|-------|

| V                                     | Voltage, SI unit is the Volt.      | V     |

| I                                     | Current, SI unit is the Ampere.    | A     |

| U                                     | Voltage (Asea and ABB convention)  | V     |

| R                                     | Resistance, SI unit is the Ohm.    | Ω     |

| С                                     | Capacitance, SI unit is the Farad. | F     |

| L                                     | Inductance, SI unit is the Henry.  | Н     |

| X Reactance, SI unit is the Ohm.      |                                    | Ω     |

| B Susceptance, SI unit is the Siemen. |                                    | S     |

| Ø Phase                               |                                    |       |

| —── Resistor                          |                                    |       |

| Inductor                              |                                    |       |

| _ Capacitor                           |                                    |       |

| Thyristor                             |                                    |       |

The following naming conventions are used throughout the document:

- A, B, C: Identify primary 50 Hz power system phase voltages and currents, where all phases are nominally separated by 120 electrical degrees.

- R, S, T: Identify phase voltages and currents referred to the secondary side of an SVC, corresponding to A, B and C phase respectively of the primary system. These quantities are phase shifted according to the vector group of the transformer.

- B<sub>AB</sub>: Indicates a susceptance delta connected between A and B phases of the power system. A subscript of BC indicates connection between B and C phases, and subscript CA connection between C and A phases. Likewise, RS represents connection between A and B phases referred to the secondary side of the SVC transformer.

- TP1: Identifies test point 1 on an ASEA abridged schematic. TP2 indicates test point 2 and so on.

# 1. Introduction

## 1.1 Background

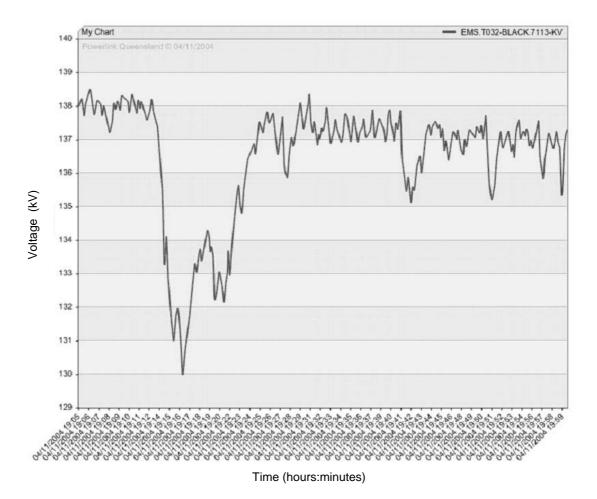

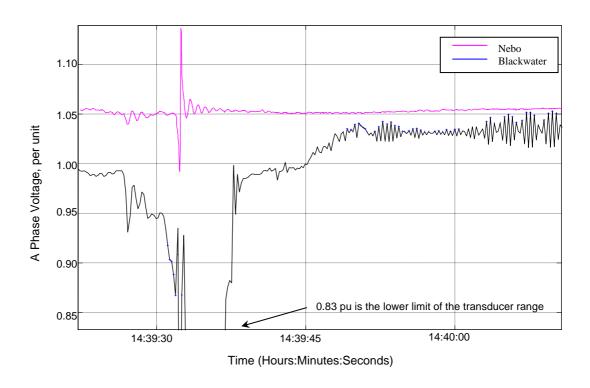

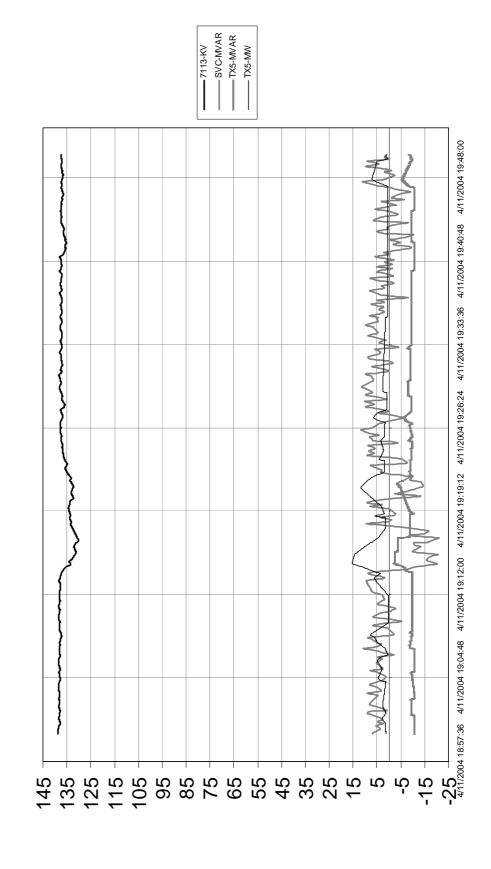

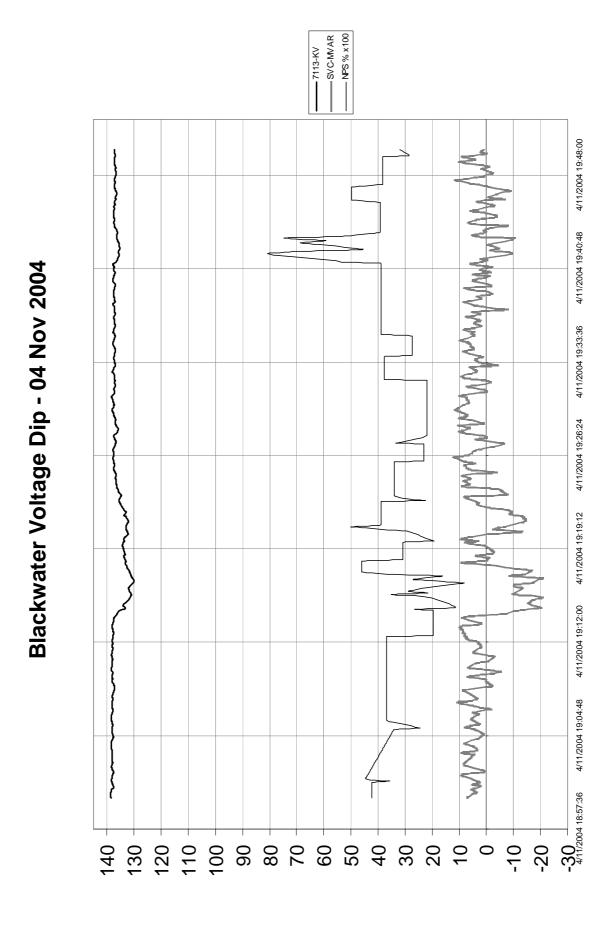

On the fourth of November 2004, a prolonged voltage dip was experienced at Blackwater 132kV Substation located in Central Queensland. The voltage fluctuation corresponded to a decrease of 6% of nominal voltage (132kV) for approximately 9 minutes as indicated in Figure 1.1. Events of this type affecting Power Quality are of concern as failure to comply with regulatory limits for voltage magnitude, balance and frequency results in penalties by regulatory authorities such as the National Electricity Market Management Company (NEMMCO) and possible litigation by industrial customers adversely affected by such failures.

Figure 1.1: Blackwater 132kV Bus Voltage (Jones, R 2005, pers. comm., 22 March)

Blackwater substation voltage levels are regulated by a device called a Static Var Compensator (SVC). Immediately prior to the voltage dip the SVC was providing transmission system voltage support, operating in capacitive mode. As shown by the voltage and load graph Figure B.1 (Appendix B), the SVC transformer T5 exhibited an increase in real and reactive power (Vars) during the voltage dip, while the SVC operating region shifted from capacitive mode to inductive mode, as negative Vars correspond to inductive SVC operation. Concurrently with the voltage dip, Negative Phase Sequence (NPS) voltage levels displayed no clear trend as shown by Figure B.2 (Appendix B), indicating no appreciable variation in unbalanced loading.

In the months previous to this event, the Static Var Compensator (SVC) voltage support and load balancing system at Blackwater substation was observed to intermittently malfunction, either failing to support voltage or causing voltage dips for short durations. At the time of these events no obvious explanation was found as the loading magnitude and type was deemed insufficient to cause such an event.

Theoretical analysis performed by Powerlink Queensland utilising available power system models failed to identify probable cause for this voltage instability. However results indicated that the SVC is not providing compensation as designed, particularly the susceptance presented by the SVC to the power system appears to intermittently deviate from optimal values resulting in voltage fluctuations (Jones, R 2005, pers. comm. 22 March).

A requirement to investigate and rectify the cause of this apparent control system malfunction was identified. Investigation of SVC control system malfunction requires some method of theoretical modelling of the control algorithms to identify deviations of control system response from design. As the SVC in question is a specialized load balancing compensator, modelling packages for this purpose are not commercially available and a specific modelling method must be developed for detailed analysis.

One such specific model does exist, developed by Mr. Paul Windle of Powerlink Queensland, although developed for academic purposes and for an alternate SVC rating. Therefore, it is proposed that the existing model be adapted for this purpose and site, and the results obtained compared with experimental results obtained from the actual SVC control to verify the validity of the model output. As the SVC to be investigated has a primary purpose of load balancing, control system response to voltage imbalance shall specifically be modelled.

#### 1.2 Project Objectives

It is proposed that the project fulfil the following objectives:

- 1. To evaluate the regulatory and operational requirements for voltage regulation and load balancing of power systems;

- 2. Analyse causes and impact of voltage imbalance and resultant Negative Phase Sequence voltages on high voltage plant and power system operation;

- Research information on Static Var Compensation control system operation and its overall effect on power systems;

- Critically evaluate mechanisms by which Static Var Compensation systems achieve voltage regulation, load balancing and minimisation of Negative Phase Sequence voltages;

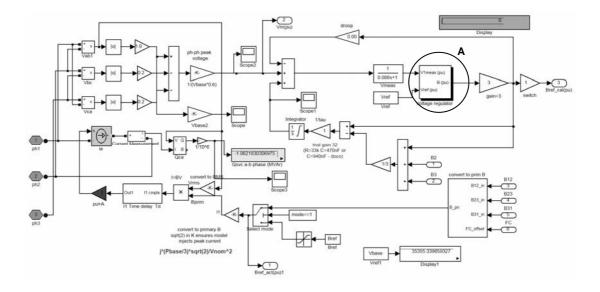

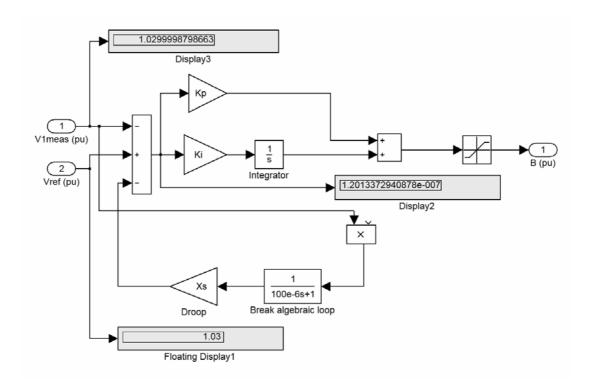

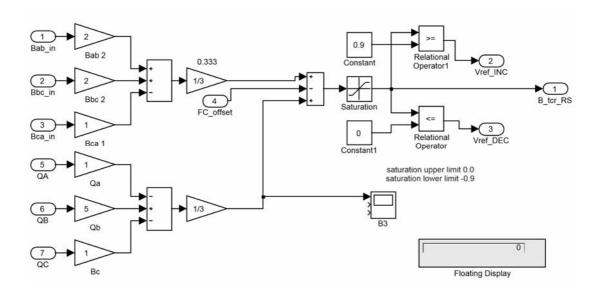

- 5. Develop or adapt a model to simulate the action of a load balancing type SVC system in MATLAB (Simulink) based on information obtained from manufacturer's documentation and component measurements;

- 6. Simulate model response to voltage imbalance utilising step load imbalance to simulate worst case conditions;

- 7. Measure actual SVC control system signals and record response to power system voltage or load imbalances;

- 8. Determine if the developed model is acceptable by comparison of predicted responses with measured values and thus validate or otherwise the assumptions made;

- 9. Write a report documenting the development, adaptation and validation of the control system model;

#### And as time permits:

10. Determine if any power system conditions exist where the dynamic response of the Static Var Compensator may cause instability.

#### 1.3 Brief Introduction to Theory

#### 1.3.1 Impact of Power System Interconnection

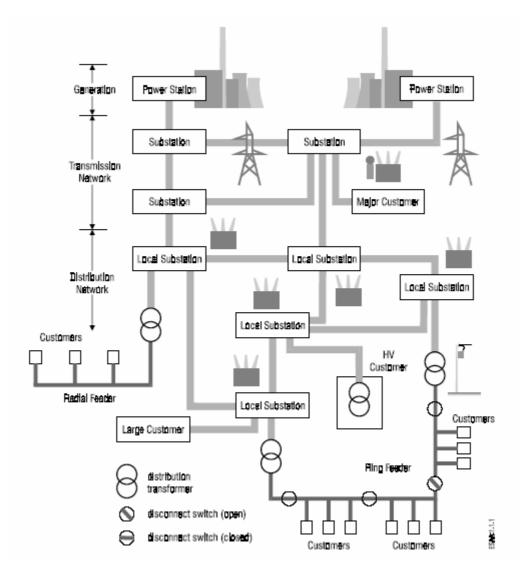

Power supply systems comprise three broad categories – generation, transmission and distribution. Electricity is generated at power stations from various natural resources such as coal, natural gas, hydro and wind, in large quantities where economies of scale can be achieved (ESAA p6). These generating stations are proximate to the fuel resource, often a considerable distance from major load centres. Therefore, large quantities of electricity are transported at high voltages via the transmission network to strategically located bulk supply substations, and from there to smaller substations where the supply is further reduced for distribution as illustrated in Figure 1.2. Power generation from other states may also be linked via interconnectors, linking the transmission systems (ESAA p8).

Figure 1.2: Electrical Power Supply System Interconnection (ESAA 2002, p. 5)

Modern power supply systems have evolved from separated utilities to large interconnected systems, with many generating stations and load centres being interconnected through power transmission lines. Traditionally power generation supplied local load via smaller systems operated at lower voltage levels. With the high degree of system interconnection, there is increased power exchange over larger distances at higher system voltage levels (Ghosh & Ledwich 2002, p. 4). Interconnection allows participating parties to share benefits such as power generation optimization, utilization of differences in load profiles, competition and pooling of reserve capacity (ESAA 2002, p. 8).

Operation and expansion of power systems impacts society and several factors must be considered. Technical and economic factors concern the improvement of existing equipment and design of new equipment which could offer economies. Social and demographic factors deal with the tendency of the power industry to influence social and political processes, including siting of industrial enterprises and distribution of working population (Ghosh & Ledwich 2002, p. 4). Environmental factors are concerned with the effects of the power industry upon the environment.

These concerns have resulted in the emergence of distributed generation, the current trend of interconnected smaller sized generating units such as Kogan Creek gas fired power station as opposed to the traditional coal fired large capacity stations such as Tarong and Stanwell. This trend is emerging as a consequence of increased Greenhouse gas issue significance, leading to consideration of alternate energy sources such as solar, wind and wave that operate with smaller sized generation units. These smaller units are also less complex, less expensive and more rapidly constructed, allowing more rapid adaptation to the requirements of expanding industries (Ghosh & Ledwich 2002, p. 4). Therefore, interconnection of power systems yields technical, economical and environmental benefits, as excess capacity generated by hydro resources from one region may augment load supplied by fossil-fuelled generation in another.

For interconnections to operate as intended, transmission systems must have adequate capacity or load rating to transmit the quantity of power intended. If the existing transmission system does not have adequate ratings for the predicted power transfer, additional lines may be constructed in parallel with existing transmission lines, or the transmission system may be upgraded to a higher operating voltage (Ghosh & Ledwich 2002, p. 5). This is not always possible due to environmental, economic and time factors, and public opinion.

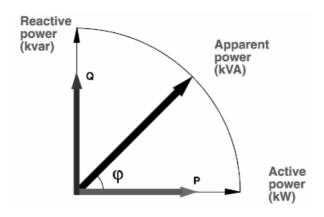

In an electrical power system, Vars (Volt-Amperes reactive or reactive power) are generated by lightly loaded lines and cables, and absorbed by transformers and heavily loaded lines. This reactive power decreases the useable power delivered to a load as shown in Figure 1.3. Power transfer limitations may be experienced due to reactive power imbalances, often limiting the transfer capacity of parallel transmission lines. Uncontrolled flow of Vars in transmission networks can lead to system stability and overvoltage problems while the rapidly varying Var demand of certain types of industrial load such as mining loads can produce unacceptable voltage fluctuations (Ghosh & Ledwich 2002, p. 7).

Figure 1.3: Relationship between Active, Apparent and Reactive Power (ABB 1999a).

These problems have greater impact on reliable and secure power supply in modern power supply systems due to globalisation, privatisation and energy transfer requirements (Ghosh & Ledwich 2002, p. 6). It is therefore essential to balance the supply and demand of active and reactive power in an electrical power system. If this balance is lost, system frequency and voltage excursions may occur with a worst case result of power system collapse.

#### 1.3.2 Power Quality

Power supply systems are intended to deliver near sinusoidal voltage of rated magnitude at the stipulated 50Hz frequency fundamental. The power supply to a customer should also be reliable, that is, uninterrupted. However, the actual energy received differs from these ideal specifications dependent on factors such as climatic conditions, system load and generational changes and the occurrence of contingencies. The degree to which the actual power received conforms to specifications and standards is referred to as power quality.

Deterioration of the supply quality affects customer power demand and may result in reduced machinery efficiency, electronics service life and manufacturing quality. Customers connected on a feeder also supplying a large motor may experience severe dips in voltage when motor load is switched on. This may adversely impact sensitive loads such as hospitals, financial institutions, airports and industrial processes (ESAA 2002, p.2). Supply voltage disturbances to industrial customers may cause significant financial losses as short duration voltage dips or interruptions are often sufficient to drop out motor drive contactors and thus interrupt manufacturing processes. This may require restarting of processes or destroy entire product batches such as in semiconductor manufacture. With the current trend toward litigation this can prove very costly to the supply authority if held accountable.

Customer awareness of power quality issues has increased in recent years, with rise in power quality impact attributed to modern technology such as computers, power electronics and controls sensitive to variations and disturbances in the electricity supply previously unnoticed. As transmission services are provided under contract, restrictions on allowable voltage and current distortion, deviation and fluctuations are imposed by regulatory authorities such as the NEMMCO.

Distribution systems are where power quality issues are commonly identified. However, transmission systems also impact on the quality of power as modern transmission systems have a low resistance to reactance ratio, resulting in low system damping. Therefore, system disturbances may oscillate for a considerable time before decaying (Ghosh & Ledwich 2002, p. 6).

Transmission of power over longer distances is at higher voltages to reduce line losses, although some losses will be experienced due to corona and line energising current. These transmission lines are usually metallic structures, open to the environment and thus exposed to hazards such as storms and lightning strikes which may cause voltage spikes.

Throughout the generation, transmission and distribution networks there are factors influencing reliability and quality of power supply. Deterioration in Power Quality may be attributed to:

- Natural Causes: faults or lightning strikes on transmission lines or distribution feeders, falling of trees or branches on distribution feeders during storm conditions or equipment failure, or;

- Man-made causes: load, capacitor or feeder switching, transformer energisation, power electronic loads such as uninterruptible power supply (UPS), variable speed drives and converters, are furnaces and induction heating systems.

Factors which affect supply quality include voltage regulation, supply frequency, voltage transients, imbalance, DC current injection, power factor, harmonic distortion and flicker.

Voltage Regulation is the maintenance of voltage within an acceptable range at the point of delivery to the customer. Regulatory authorities can impose sanctions on utilities for providing customers with out-of-range voltages (ESAA 2002, p. 42). Sustained overvoltage may cause equipment failure and insulation stress and sustained undervoltage can cause motors to stall. Voltage variations may be of short or long duration.

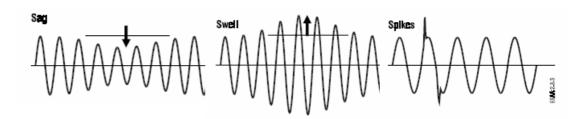

Any variation in the supply voltage for duration not exceeding one minute is called a short duration voltage variation (ESAA 2002, p. 43). These variations are further classified as voltage sags, voltage swells and spikes shown in Figure 1.4.

Voltage sag is a short duration decrease in supply lasting between 5 cycles to a minute, typically caused by system faults or energisation of heavy loads. Voltage may fall between a few percent below lower nominal limit to as much as 100%, although the duration is not long enough to be classed as an interruption. Most voltage sags do not exceed a 20% drop from nominal and usually persist for half a second or less (ESAA 2002, p. 43).

Figure 1.4: Short Duration Voltage Disturbances (ESAA 2002, p. 44)

Voltage swells are defined as increase of fundamental frequency voltage for a short duration lasting from milliseconds to a second, and spikes are very high magnitude voltage impulses lasting microseconds (Ghosh & Ledwich 2002, p. 8). Swells do not occur as commonly as sags, but might occur due to temporary voltage rise of an unfaulted phase during system earth faults.

Long duration voltage variations are any variation in the supply voltage for duration exceeding one minute and have greater impact on customers than short duration variations. These variations are further classified as overvoltages, undervoltages and sustained interruptions (ESAA 2002, p. 43).

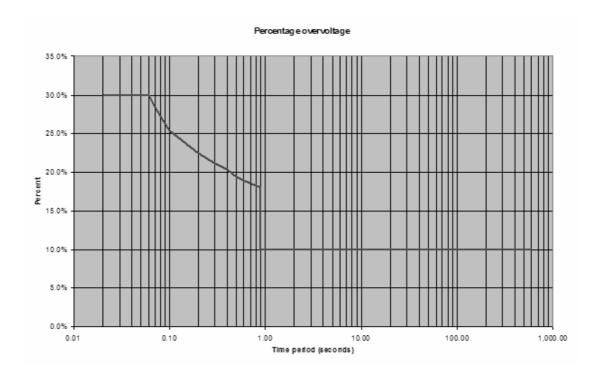

An overvoltage or undervoltage is a 10% or more increase or decrease in RMS voltage for a long duration. Switching off large loads or capacitor bank energisation may result in system overvoltage if voltage regulation is poor. The limits defined by the National Electricity Code (NEC) as to the percentage and duration of overvoltage events are displayed in Figure 1.5.

Figure 1.5: Sustained System Overvoltage Limits (NEC 2002, p. 50)

An undervoltage is the result of an event opposite in nature such as reactor energisation and a sustained undervoltage is referred to as a brownout. When supply voltage is zero for period of time in excess of 1 minute it is referred to as a sustained interruption (ESAA 2002, p. 43).

Supply frequency is the power quality aspect most easily altered and the factor most likely to have widespread impact. Frequency is the rate at which voltage alternates, generally maintained to within  $\pm 0.2\%$  of the nominal 50 Hz. Control of frequency is a function of the generation process, determined by the speed at which the generators spin and in turn, determining motor rotational speed. Large load increases act to slow generators, decreasing frequency (ESAA 2002, p. 45). Any significant decrease in system loading allows generators to increase speed, resulting in increased system frequency.

These load changes can occur anywhere on the transmission or distribution system and rapid load changes will cause system frequency disturbances. However major events such as system contingencies or very large load loss may alter system frequency by a significant amount, referred to as an excursion. This may cause alternate speed variations of system generators, and thus of system frequency, as the generators create power oscillations known as 'power swings' (ESAA 2002, p. 45). If these oscillations are not quickly damped, synchronism and thus stability may be lost. Sustained operation outside tolerable frequency limits may result in reduced life span of generator turbine blades (Sen 1997, p. 117). If frequency falls below a certain threshold, underfrequency protection relays may trip to protect turbine blades. Certain time limits are defined and enforced by NEMMCO for restoration of system frequency to acceptable values as indicated in Table 1.1.

Table 1.1: Frequency Excursions and Restoration times (ESAA 2002, p. 46)

| Event          | Range            | Frequency (Hz) | Restoration Time             |  |

|----------------|------------------|----------------|------------------------------|--|

|                | Normal           | 49.90 – 50.10  |                              |  |

| Large Load     | Normal Excursion | 49.75 – 50.25  | To Normal within 5 minutes   |  |

| Change         | Normal Execusion | 47.73 – 30.23  | 10 Normal within 5 minutes   |  |

| Loss of single | Frequency        | 49.50 - 50.50  | To Normal within 5 minutes   |  |

| generator unit | Tolerance        | 47.30 – 30.30  | 10 Normal within 5 minutes   |  |

| Single         | Frequency        |                | To Frequency Tolerance       |  |

| contingency    | Contingency      | 49.00 – 51.00  | within 1 minute, then Normal |  |

| contingency    | Contingency      |                | within 5 minutes             |  |

| Multiple       | Multiple         |                | To Frequency Tolerance       |  |

| •              | 1                | 47.00 - 52.00  | within 1 minute, then Normal |  |

| contingencies  | Contingency      |                | within 10 minutes            |  |

Voltage transients are waveform components that disappear during transition from one steady-state operating condition to another (ESAA 2002, p. 43). These may be classified as impulsive or oscillatory transients. An impulsive transient is a fast rise and decay time non-power frequency change in voltage or current, mainly caused by lightning strikes (Ghosh & Ledwich 2002, p. 13). Oscillatory transients have one or more sinusoidal components multiplied by a decaying term and caused by capacitor or transformer energisation, ferroresonance and converter switching.

Voltage imbalance is a condition in which the three phases of supply are not equal in magnitude and 120 ° separation between phases is not maintained. This supply imbalance can cause temperature rise, deterioration of insulation, de-rating of motors and large motor thermal trips (ESAA 2002, p. 46). For high voltage networks, this voltage imbalance is limited to 3% variation between highest and lowest phase magnitudes (Standards Australia 1991b, p. 5).

The primary cause of voltage unbalance is single phase loads in three phase circuits, with severe imbalance resulting during single phasing conditions (Ghosh & Ledwich 2002, p. 14). Unbalanced loading in three phase systems produces unequal currents generating Negative Phase Sequence (NPS) voltages. The magnitude of NPS voltage allowable is limited by electrical utilities due to the increased heating caused in three phase motors and generators. Australian Standard AS1359 (1997) specifies that 3-phase induction machines should be designed for continuous voltage unbalance levels of 1.0%. For induction motors, the positive phase sequence voltage components create positive torque that does useful work. The negative phase sequence voltage creates a flux rotating opposite to the rotor at almost twice the supply frequency, creating negative torque, increased current flow and consequential heating.

NPS voltage is defined in terms of the fundamental phase to neutral voltage phasors  $V_a$ ,  $V_b$  and  $V_c$  as:

$$V_{NPS} = \frac{\left(V_a + a^2 V_b + a \cdot V_c\right)}{\sqrt{3}}$$

where;  $a = e^{j120^{\circ}}$  (1.1)

(Standards Australia 1997, p. 4).

In balanced systems this phasor summation forms a closed triangle, giving  $V_{NPS}$ =0.

Direct Current (DC) injection is a situation that may cause saturation and heating of transformers and motors, and generation of excessive harmonic currents (ESAA 2002, p. 42). There are two main implications of DC current in an electricity supply system. DC current may bias the sinusoidal flux of a transformer core, positively offsetting transformer flux waveforms with the positive half cycle becoming heavily saturated while the negative half cycle remains within linear range. The increased flux peak value may result in transformer magnetic core saturation and heating due to excessive magnetising current and core losses (Ghosh & Ledwich 2002, p. 16). The other implication is that the DC current return path usually involves flowing through earth. This may involve DC current passing through subterranean metallic structures and the consequential acceleration of corrosion, possibly resulting in unsafe operating conditions if the earthing system is damaged.

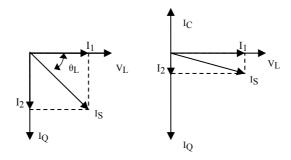

Poor power factor causes unnecessary power loss. Consider a feeder supplying an inductive load, with current denoted by  $I_s$  and load voltage by  $V_L$ . If the load power factor  $\cos \theta_L$  is lagging, the system phasor diagram may be represented as below in Figure 1.6.

Figure 1.6: Power factor and corrected power factor

Load current  $I_s$  is resolved into a real part  $I_1 = |I_s| \cos \theta_L$ , and a reactive part  $I_2 = |I_s| \sin \theta_L$ . Actual work done depends on real power and thus the reactive power is wasted. If the load power factor is small, then the reactive current component is large, resulting in significant voltage drop. Optimally, feeders should be operated near unity power factor (ESAA 2002, p. 47).

Power factor correction is achieved by connecting capacitance in parallel with the load, drawing current  $I_c$  in phase opposition to  $I_Q$ . The resultant current drawn by capacitor load combination is  $I_s$  indicated in the second diagram of Figure 1.6. The real component of current remains constant but the reactive component of current has reduced considerably. The magnitude of feeder current and the associated power factor angle have both decreased.

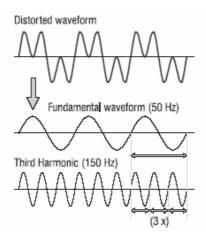

Harmonic Distortions are caused by the injection of currents having frequency components which are multiples of the fundamental frequency, resulting from equipment drawing non-sinusoidal current from the supply. Power electronic loads such as uninterruptible power supplies (UPS), converters and adjustable speed drives usually cause harmonics in power systems, in addition to draglines, arc furnaces and fluorescent lighting. A measure of harmonic content is the total harmonic distortion (THD). For quality power it is recommended that THD be less than 3% (Standards Australia 1991a, p. 3).

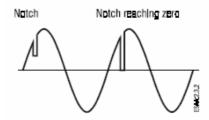

Notching is a periodic voltage distortion due to the operation of power electronic converters where current commutates from one phase to another due to finite supply inductance (Ghosh & Ledwich 2002, p. 18). During this period there is a momentary short circuit between the two phases that distorts voltages as shown in Figure 1.7. The maximum voltage during notches depends on the system impedance. The frequency components associated with notches are usually very high.

Figure 1.7: Voltage Notching (ESAA 2002, p. 50)

Analysis of harmonic distortions indicate that they are composed of a number of pure sine waves of various magnitudes and frequencies that are integer multiples (harmonics) of the fundamental frequency (50 Hz) as indicated in Figure 1.8.

Figure 1.8: Power System harmonics (ESAA 2002, p. 48)

Flicker is rapid voltage fluctuations causing unacceptable variations in lighting levels, often very annoying to the human eye. Flicker is mainly caused by rapid current magnitude variations of loads such as arc furnaces when initial arc strike produces large inrush currents, causing a dip in the supply voltage (Ghosh & Ledwich 2002, p. 19).

Table 1.2: Power Quality Categories and Causes (Ghosh & Ledwich 2002, p. 5)

| Category            |               | Characterisation                     | Typical Causes                                |  |

|---------------------|---------------|--------------------------------------|-----------------------------------------------|--|

|                     | Impulsive     | Peak magnitude, rise                 | Lightning strike, transformer energisation.   |  |

| Transients          | Impuisive     | time and duration                    | Capacitor switching                           |  |

| Transients          | Oscillatory   | Peak magnitude, frequency components | Line, capacitor or load switching             |  |

| Short               | Sag           | Magnitude, duration                  | Ferroresonant transformers, single            |  |

| duration            | Sag           | wagiittude, duration                 | line-to-ground faults                         |  |

| voltage             | Swell         | Magnitude, duration                  | Ferroresonant transformers, single            |  |

| variation           | Swell         | wagiittude, duration                 | line-to-ground faults                         |  |

| variation           | Interruption  | Duration                             | Temporary (self clearing) faults              |  |

| Long                | Undervoltage  | Magnitude, duration                  | Switching on loads, capacitor de-energisation |  |

| duration            | Overvoltage   | Magnitude, duration                  | Switching off loads, capacitor energisation   |  |

| voltage             | Sustained     | Duration                             | Faults                                        |  |

| variation           | Interruptions | Duration                             |                                               |  |

| Valtaga             | h.alan.aa     | Symmetrical                          | Single phase loads, single phasing            |  |

| voltage             | imbalance     | components                           | conditions                                    |  |

|                     | Harmonics     | THD, harmonic                        | Adjustable speed drives and other non-        |  |

|                     | riaimonics    | spectrum                             | linear loads                                  |  |

| Waveform distortion | Notching      | THD, Harmonic spectrum               | Power electronic converters                   |  |

|                     | Dc Offset     | Volta amna                           | Geo-magnetic disturbance, half wave           |  |

|                     | De Offset     | Volts, amps                          | rectification                                 |  |

|                     | L             | Frequency of                         |                                               |  |

| Voltag              | e flicker     | occurrence,                          | Arc furnace, arc lamps                        |  |

|                     |               | modulating frequency                 |                                               |  |

|                     |               | 1                                    | I.                                            |  |

As power quality problems have existed for a long time, conventional mitigation methods for these problems also are well developed. Passive filters based on inductors and capacitors are used in many transmission and distribution applications. Some of these filters are tuned to bypass specific harmonic frequencies, however the use of passive elements at high power levels result in bulky devices that are further limited due to their fixed range of operation (Ghosh & Ledwich 2002, p. 19).

#### 1.3.3 Power System Compensation

Uncontrolled flow of Vars and imbalances in transmission networks can lead to system instability and overvoltage problems, voltage fluctuations and transmission system power transfer limitations. Var sources within power systems include the inductances in electrical machines, loaded transmission lines, transformers and reactors, and the capacitances in cables and unloaded transmission lines. The relationship between real and reactive power is indicated in Figure 1.9.

To balance or control system Vars requires the use of power system compensation. Compensation devices are used for harmonic filtering, load balancing, power factor correction and voltage regulation. These devices can be connected in both shunt and series, although shunt devices are more popular than series devices due to ease of protection. Some devices are used as load compensators to correct unbalance and distortion in load currents such that compensated loads draw balanced sinusoidal current. Compensation devices include, but are not limited to:

- Mechanically switched reactors and capacitors;

- Synchronous capacitors;

- Thyristor controlled shunt and series compensation, and;

- Converter controlled shunt and series compensation.

Figure 1.9: Power Triangle

Power system compensation is achieved by counteracting the Vars with a reactive power source of the opposite 'polarity'. The connection of a shunt reactor, or inductor, will lower system voltage by counteracting long or lightly loaded transmission line capacitance, whereas the connection of a shunt capacitor will raise or support system voltage by counteracting voltage drop associated inductive transmission lines or poor power factor.

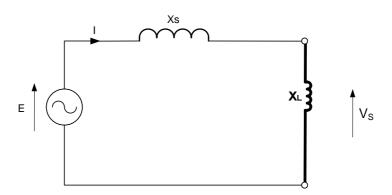

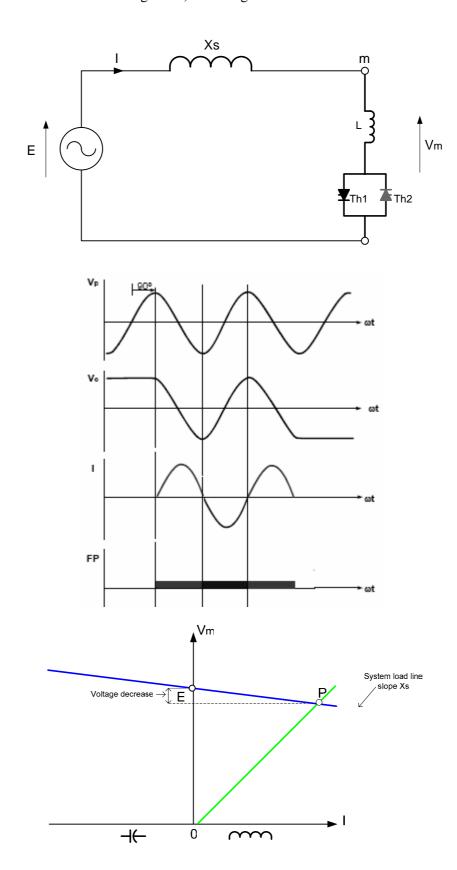

An equivalent circuit of power system load conditions may be represented as in Figure 1.10 as a voltage source E, a transmission line, which may be represented as an inductance  $X_s$ , due to the high reactance to resistance ratio of the transmission network, and load  $X_L$ .

Figure 1.10: Power System equivalent circuit

Using the voltage divider rule the voltage appearing at the load terminals is defined by:

$$V_{S} = E \cdot \frac{X_{L}}{X_{S} + X_{L}} \tag{1.2}$$

$V_S$  will always be less than the generated voltage E as inductive reactance  $X_S$  is positive and the term  $\frac{X_L}{X_S + X_L}$  will always be less than one.

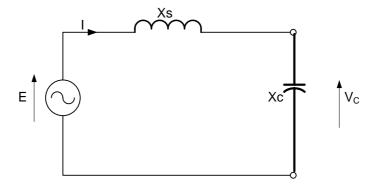

An equivalent circuit of power system compensation may be represented as in Figure 1.11 as a voltage source E, a transmission line reactance  $X_s$ , and a capacitive reactance  $X_c$ .

Figure 1.11: Power System compensation equivalent circuit

Now, the compensated voltage appearing at the load terminals is defined by the equation:

$$V_c = E \cdot \frac{X_c}{X_s - X_c} \tag{1.3}$$

$V_C$  will be greater than the generated voltage E as capacitive reactance  $X_C$  is negative and the term  $\frac{X_C}{X_S - X_C}$  will be a value greater than one.

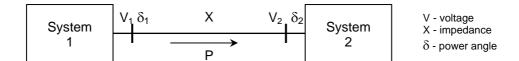

Power transmission limitations may be quantified by means of the power transfer equation, with variables as defined in Figure 1.12.

$$P = \frac{V_1 V_2}{X} \sin \left( \delta_1 - \delta_2 \right) \tag{1.4}$$

Figure 1.12: Power Transfer

Var imbalance or lack of power system compensation will result in a reduction in the receiving end voltage  $V_2$  and a poor power factor angle  $\delta_2$ , both attributes reducing the power transfer capability of the transmission line.

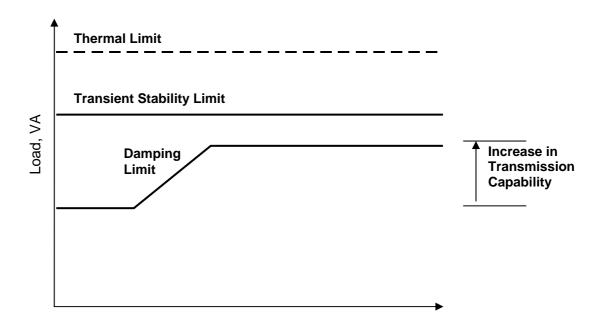

In theory, a transmission system can carry power up to its thermal loading limits. However in practice, loading to its thermal limits is not possible due to the following constraints:

- <u>Transmission stability limit</u>: the limits of transmittable power through which a transmission system can endure major faults on the system with transmission capability intact defines the transient stability limit as per Figure 1.13;

- <u>Voltage limit</u>: the limits of power transmission where system voltage can be kept within permitted deviations from nominal, that is +10%, -6% (NEC 2002).

- <u>Loop flow</u>: power flowing from one point to another may not always take the most direct path, possibly generating additional line losses or unintentionally overloading portions of the transmission network.

Figure 1.13: Power Transmission Capability

The voltage limits are governed by reactive power, in turn dependent on the physical length of the transmission circuit. The longer the line or the heavier the loading, the more reactive power will be present and the greater the magnitude of voltage drop due to that reactive power. Voltage will continue to drop as a consequence until a critical point is reached where the voltage collapses altogether.

Use of power system compensation will reduce reactive power present, decreasing voltage drop and increasing power system stability. Therefore the power transmission capability will be increased.

Traditional methods of power system compensation utilise fixed reactive plant such as capacitor banks and reactors. This is referred to as static compensation, and is unable to adapt to changes in power system configuration and generation patterns. Therefore dynamic compensation capable of adapting to changes in power system conditions is advantageous in that it can adjust the amount of compensation delivered.

# 2. Power System Compensation

## 2.1 Dynamic Power System Compensation

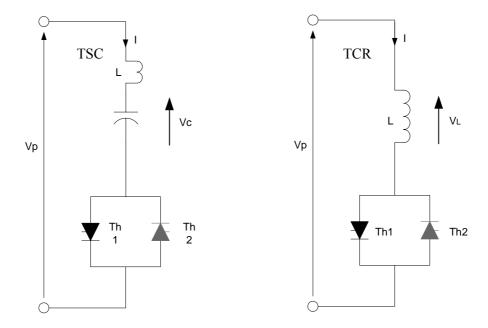

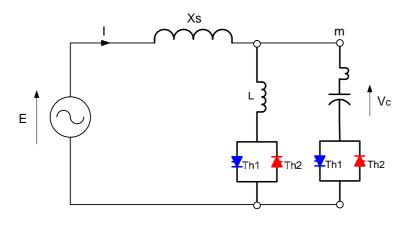

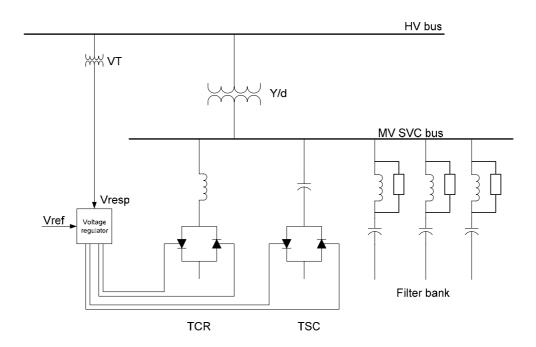

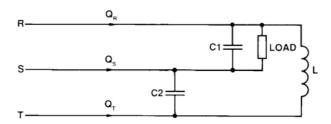

Dynamic power system compensation may be achieved by the use of Thyristor Switched Capacitors (TSC) and Thyristor Controlled Reactors (TCR) whose schematic representation is displayed in Figure 2.1.

Figure 2.1: TSC and TCR line diagram (ABB 1999a)

#### 2.1.1 Thyristor Controlled Reactor

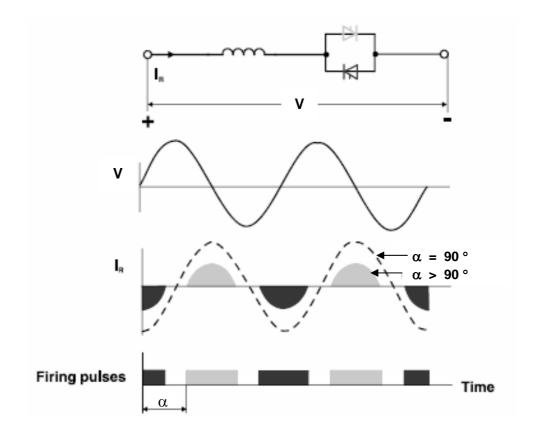

Current in a thyristor controlled reactor can be continuously varied from zero to maximum by phase angle controlling the gating or conducting signal to the thyristors. The reactor is connected in series with two opposite poled thyristors. One of these thyristors conducts in each positive half cycle of the supply frequency, while the other conducts in the corresponding negative half cycle (Tyll 2004, p. 4).

The gating or 'turn on' signal to each thyristor is delayed by  $\alpha$ , the firing or conduction angle, from the zero crossing of the source voltage as illustrated in Figure 2.2. As current lags the voltage across the reactor by ninety degrees, so a firing angle of ninety degrees results in maximum, that is, continuous reactor current. For a firing angle of 180°, the reactor current will be zero. As the thyristor firing angle is increased from 90 towards 180 degrees, the current in the reactor is reduced (Hingorani & Gyugyi 2000, p. 146). Therefore, the firing angle must be in the range  $90 \circ \leq \alpha \leq 180 \circ$ .

Figure 2.2: Thyristor Controlled Reactor current waveform (ABB 1999a).

Figure 2.3 indicates TCR arrangement, switching waveforms and characteristics.

Figure 2.3: TCR Characteristic (ABB 1999b)

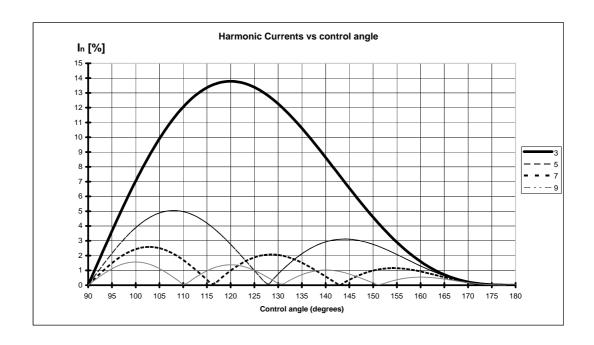

A current or voltage waveform that deviates from a pure sinusoid at fundamental frequency contains harmonics. For thyristor controlled reactors, as the areas under the positive and negative half cycles of the current and voltage waveforms are of equal size and shape, the wave form includes only odd harmonics (ABB 1999b). Thus harmonics of order 3, 5, 7, 9, 11 and so on will be generated by the TCR with the amplitude of the harmonics varying with the firing angle (Tyll 2004, p. 8). The third harmonic component is the most significant as highlighted in Figure 2.4.

Figure 2.4: TCR Fundamental current and harmonic magnitude (ABB 1999a)

#### 2.1.2 Thyristor Switched Capacitor

A thyristor switched capacitor (TSC) is a capacitor connected in series with two opposite poled thyristors so that one thyristors conducts in each positive half cycle of the supply frequency, while the other conducts in the corresponding negative half cycle. The current flowing through the capacitor may be controlled by blocking the thyristors. To achieve controlled reactive power a TSC is always configured in groups (ABB 1999a).

One disadvantage in utilising a TSC is the switching transients produced. Since a TSC blocks current when the thyristors are blocked and allows current to flow when the thyristors are gated, severe transients will occur if a TSC is switched off while the current through it is not zero (Tyll 2004, p. 9). Similarly, to avoid generation of transients during switch on, the thyristor must receive its firing pulse at a particular instant of the voltage cycle. That is, transient free switching may be obtained when the voltage across a capacitor is either at its positive peak or negative peak such that the current through the capacitor is zero.

A TSC exhibits a relationship between current and voltage as shown in Figure 2.5.

Figure 2.5: V/I performance of TSC (ABB 1999b)

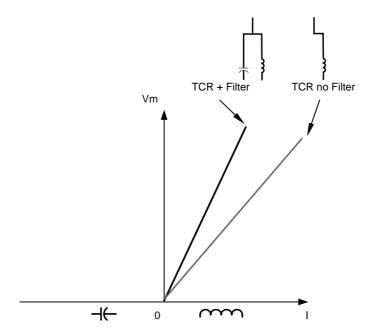

### 2.1.3 Combined Dynamic Characteristics

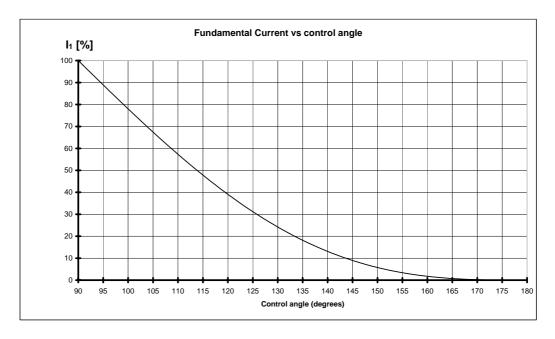

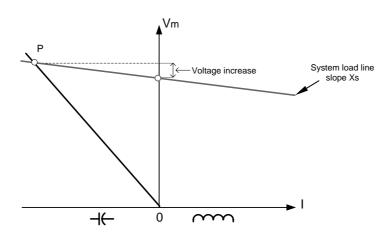

A Thyristor Controlled Reactor (TCR) and capacitor combination exhibits a relationship between current and voltage as indicated in Figure 2.6.

Figure 2.6: V/I performance of TCR with/without filter (ABB 1999a)

The inductive reactance  $X_L$  is defined

$$X_L = j \omega L, \qquad (2.1)$$

and capacitive reactance  $X_{C}$  is defined

$$X_C = -\frac{j}{\omega C} , \qquad (2.2)$$

therefore the combined reactance  $X_{\mathit{SVC}}$  is

$$X_{SVC} = j \omega L - \frac{j}{\omega C_{FC}}. \qquad (2.3)$$

Therefore the arrangement indicated in Figure 2.7 will provide dynamic compensation over the combined inductive and capacitive Var range with the relationship between current and voltage as shown.

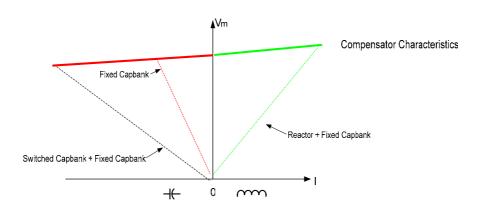

Figure 2.7: Combined TCR / TSC Characteristic (ABB 1999b)

### 2.2 Static Var Compensation

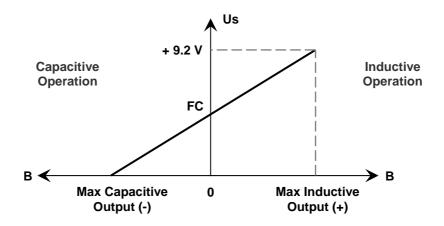

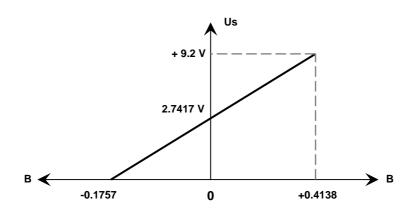

A Static Var Compensator (SVC) consists of thyristor controlled reactive plant, either capacitor banks, reactors or both, in combination with fixed reactive plant. This variable static equipment provides continuously variable reactive power injection or absorption to the network, facilitating dynamic Var balancing and so improves the efficiency, controllability and quality of power systems.

SVCs are commonly connected at transmission substations via star-delta vector group step down transformers, and consist of shunt connected inductors or capacitors, or more commonly a combination of the two, where at least one is variable (ABB 1999a). Variable inductors take the form of thyristor controlled reactors. Within an SVC, capacitors usually take the form of fixed or mechanically switched banks which may also be subdivided into harmonic filtering circuits tuned to the dominant frequencies. Thyristor switched capacitors are used when fast or varied frequency capacitor switching is required (Janke 2002, p. 4).

The main purpose of an SVC is to regulate and control substation bus voltage to the desired level, providing fast control of steady state and dynamic voltages and improving system stability by reactive power control of dynamic loads (Janke 2002, p. 7). This will result in increased power transfer capacity as SVCs present a variable impedance of controllable power angle (ABB 1999b) and maintain a stable voltage profile along the transmission line. SVCs also provide dynamic compensation of variable, unbalanced loads.

Damping of system electro-mechanical oscillations between generators is enhanced by controlling the power oscillations in transmission lines (ABB 1999b). Therefore SVCs enhance 'First Swing' stability by maintaining system voltages during large disturbances, providing active damping of power swings between weak interconnecting power systems (Hingorani & Gyugyi 2000, p. 139). Dynamic, fast response reactive power compensation following system contingencies such as network short circuits, line and generator disconnections and load shedding is also established by SVCs.

The use of SVCs for power system compensation provide the added benefit of reducing required insulation levels by providing fast overvoltage control and suppression of voltage fluctuations caused by disturbing loads such as large thyristor drives and electric arc furnaces. This provides improvement of the efficiency of industrial processes by voltage stabilization and fast power factor correction (ABB 1999b).

There are two main SVC types in common use, and are defined by the manner in which the reactive power is utilised for compensation. SVCs are primarily used for compensation of transmission lines and for balancing of single-phase railway loads, that is, voltage imbalance.

Static Var Compensators for transmission applications are required to:

- Regulate and control voltage at the point of connection;

- Enhance damping of system electro-mechanical oscillations, and;

- Provide fast reactive Var support following system contingencies.

Static Var Compensators for load balancing applications are required to:

- Convert single phase load into balanced three phase load;

- Reduce negative sequence components in system voltage, and;

- Regulate positive sequence components in system voltage.

SVCs utilised for transmission applications generally have symmetrical phase control and the same swing range in all three phases. Compensators for load balancing are single phase controlled and may have different swing ranges in different phase groups (ABB 1999b).

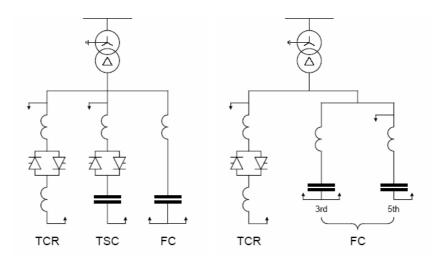

Single line drawings of a typical transmission application SVC and a typical load balance SVC are shown in Figure 2.8.

Figure 2.8: Single Line Drawings of Typical SVCs (Janke 2002, p. 6)

Both SVC types have a TCR branch and a FC branch, whereas only transmission application SVCs utilise a TSC branch. The composition and arrangement of an SVC is determined during the specification and design process (ABB 1999a).

TCRs must be delta connected to allow the current through the reactors to be continuously controlled from zero to full conduction. The TSC branch has a current inrush limiting reactor and is also connected in delta. The fixed capacitor (FC) branch is arranged as one or more tuned filters and may be connected in star or delta (ABB 1999a). If the fixed capacitor is specified as balanced on all three phases, a star connection is more economical. If the swing range of the SVC, that is the range of reactive power that the SVC provides, is unbalanced then one or more of the filters may be delta connected.

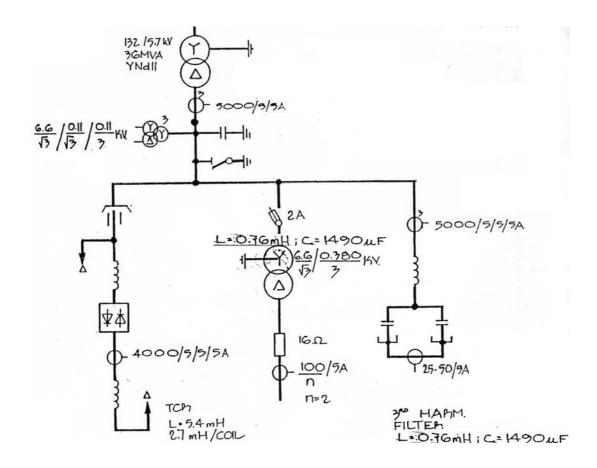

A load balancing type SVC will usually operate with asymmetrical phase swing ranges, and the triplen harmonics generated by the thyristor switching will not be suppressed in the delta winding of the transformer. Therefore, this type of SVC will require a third harmonic filter (Janke 2002, p. 7).

### 2.3 Load Balancing Static Var Compensation

#### 2.3.1 Load Balancing Requirements

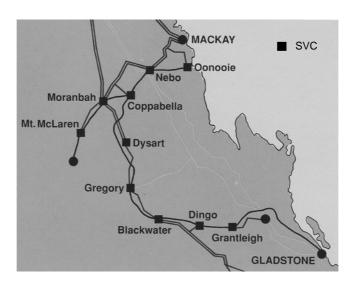

Queensland Rail (QR) operates an AC electrified railway in the central Queensland region. The railway is a heavy haul system comprising over 1000 km of track and is used to transport coal from inland mines to export and generation facilities on the east coast. Supply is provided from a 132kV network via 13 railway substations, each of which has two or three separate 30MVA single phase 132 / 50 kV transformers (ABB 1999b).

The traction system is supplied via a 25kV catenary provided by 50 / 25 kV autotransformers located at intervals along the track. Traction loads are single phase with time dependent characteristics and may reach short duration peaks of between 20 and 40 MVA (ABB 1998). As this region is located at some distance from generating stations, most parts of the system used to supply the railway loads possess low fault levels due to high source impedance. This would result in unacceptable levels of NPS voltages and currents in the power system if no compensation was applied (Janke 2002, p. 6).

A fully loaded locomotive imposes a 50 A load at 50 kV (ABB 1998). As a heavy coal train consists of four such locomotives it imposes a 10 MW unbalanced load upon the supply system. Several coal trains may be present upon a particular section of the rail system at any time. Harmonics are generated by the locomotive thyristor drives, and NPS is generated due to the unbalanced nature of traction loading. Therefore, 3<sup>rd</sup>, 5<sup>th</sup> and 7<sup>th</sup> harmonic filters are required on the 50kV system to mitigate the effect of the traction loading (ABB 1999b).

The Australian Standard for induction motor design AS1359.31 specifies that motors should be designed to withstand 1.0 % NPS only, with the NEMA standard of the USA similar to this. EDF, the French standard for traction loading, also allows a maximum 1.0 % NPS under normal system conditions but with an increased limit of 1.5 % under contingency situations. The UK standards BS2613, BS4999 and BS5000 allow NPS levels of 2.0 % for one minute only under contingency conditions.

The German VDE0530 standard allows 0.7 % NPS for 10minutes such that

$$k_{u} = \sqrt{\frac{1}{T} \int_{i=0}^{T} V^{2}_{NPS} dt} < 0.7 \% , \qquad (2.4)$$

and the limits imposed by QR of

- 0.7 % for half hour maximum demands;

- 1.0 % for five minute peak loads, and

- 2.0 % for one minute peak loads,

are almost identical to the German Standard.

Nine load balancing type SVCs are used throughout Central Queensland, as shown in Figure 2.9, to provide voltage support and reduce NPS voltages caused by the unbalanced loads.

Figure 2.9: Load Balancing SVC location (ABB 1998)

The SVCs are required to balance the single phase traction load and to provide power system voltage regulation. Each SVC is configured to ensure that the overall NPS voltage at the various railway substations does not exceed the regulatory limits (ABB 1998).

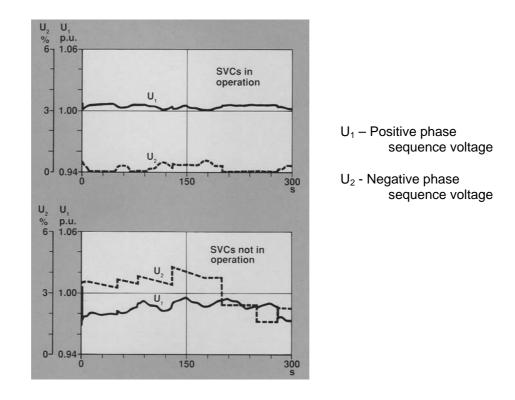

Figure 2.10 shows the impact of the SVCs on voltage balancing as well as voltage support of the 132kV supply system.

Figure 2.10: Positive and Negative Sequence voltage balancing (ABB 1998)

In addition to the nine SVCs, a total of 28 single phase harmonic filters have been installed in the 13 railway substations, tuned to the 3<sup>rd</sup>, 5<sup>th</sup> and 7<sup>th</sup> harmonics (Ghosh & Ledeich 2002, p. 38), to prevent the injection of substantial amounts of harmonics generated by locomotives into the 132kV Power system.

#### 2.3.2 Load Balancing SVC Substations

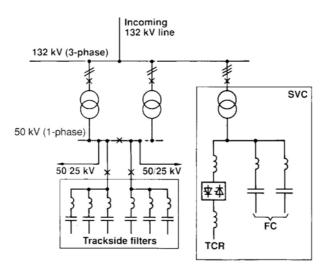

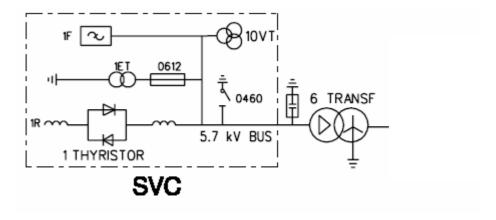

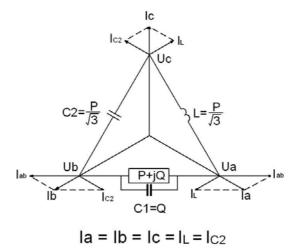

A typical traction substation arrangement is in accordance with Figure 2.11. The SVC usually comprises a TCR operating in parallel with a fixed capacitor bank configured as a third or fifth harmonic filter (Janke 2002, p. 9).

Figure 2.11: Typical Traction Substation arrangement (Janke 2002, p. 13).

The thyristor valve of the TCR is water cooled and consists of a number of thyristors connected in series. Thyristor control circuitry is of the magnetic firing type which supplies trigger pulses from the ground potential without the need to obtain auxiliary power from the voltage across the thyristors. This firing system is very simple and reliable and is used in SVC systems worldwide (Bacha et. al. 2004, p. 2).

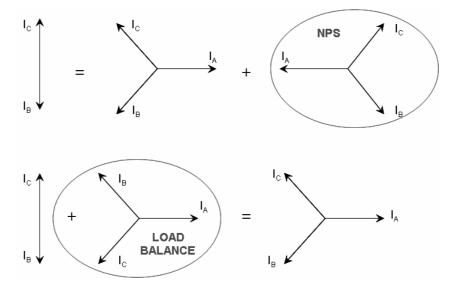

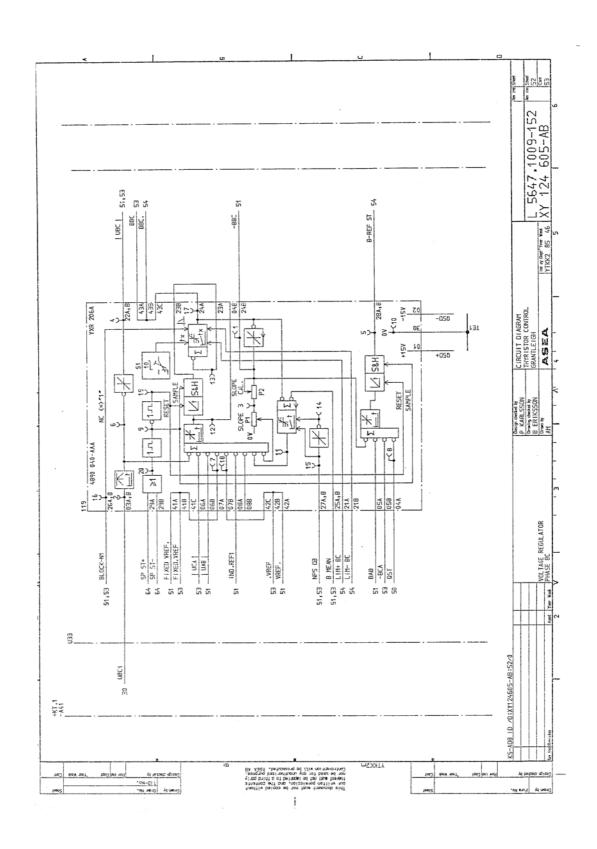

To enable load balancing, each phase of the SVC is controlled individually by dedicated voltage regulators. As the SVC phases operate independently, each phase may possess a different swing limit. The TCR rating is determined by the highest inductive requirement per phase plus the necessary inductive reactive power to provide bias for the capacitive requirement (Janke 2002, p. 38). Ratings and swing ranges of the central Queensland load balancing SVCs are listed in Table 2.1.

Table 2.1: Load Balancing SVC range and ratings (Janke 2002, p. 41)

| Load Balance<br>SVC Location | Swing Range<br>+ Capacitive MVar, - Inductive MVar |                                                                                  | Transformer & Reactor<br>Ratings                         |