# Behaviour and Refinement of Port-Based Components with Synchronous and Asynchronous Communication

Stephan Janisch

# Dissertation

an der Fakultät für Mathematik, Informatik und Statistik der Ludwig-Maximilians-Universität München zur Erlangung des Grades Doctor rerum naturalium (Dr. rer. nat.)

Erster Gutachter: Prof. Dr. Rolf Hennicker, LMU München, IFI, PST

Auswärtiger Gutachter: Prof. Dr. Stephan Merz, INRIA Lorraine, LORIA

Dritter Gutachter: Prof. Dr. Martin Wirsing, LMU München, IFI, PST

Abgabedatum: 18. Juni 2010 Tag der mündlichen Prüfung: 27. Juli 2010

#### **Abstract**

Component-based development is an established discipline of Software Engineering. It focuses on the development of strongly encapsulated components to support reuse within the construction of hierarchical systems by assemblies of components and their connectors. Software component models define concepts for the construction of component-based systems. Formal software component models additionally define a model of dynamic component behaviour and support formal analysis which is of paramount importance for the verification of behavioural properties and component correctness. This holds in particular for the development of concurrent component-based systems.

Existing formal component models usually use a synchronous rendezvous mechanism to define the global behaviour of communicating concurrent components. However, in order to support the specification and analysis of concurrent systems an asynchronous communication timing, as prominent for example in FIFO buffered communications of message-passing systems, must also be taken into account. Moreover, in order to support component-based development of hierarchical systems with top-down or bottom-up design approaches, it is crucial to distinguish between behaviour specifications and behaviour implementations. Still, an integrated view of specification and implementation of component behaviour must be provided.

In this thesis, we develop a formal software component model with hierarchical portbased components, providing an integrated approach for the static and dynamic modelling of concurrent message-passing systems with synchronous and asynchronous message exchange. We consider components that execute in parallel to each other and communicate solely by message exchange via ports. Binary connectors between ports are utilised for synchronous (rendezvous) or asynchronous (FIFO buffered) message exchange. Components and connectors are used for a compositional construction of assemblies. Assemblies in turn can be used for the implementation of composite components by delegating messages between the ports of the composite component and the open ports of the assembly.

The proposed model distinguishes abstract models for component implementations and component specifications. We call the former "component behaviours" and the latter "component frames". Behaviours and frames are formally related by a definition of implementation correctness. We show that our model supports top-down and bottom-up design approaches, and component-wise evolution [dAH01b] in hierarchical systems. As a formal model of behaviours we use I/O-transition systems (IOTSs) and for frames we use input-persistent I/O-transition systems (PIOs). IOTSs are in fact a special case of PIOs that in turn are a specialisation of modal I/O automata of Larsen and Nyman [LNW07].

We develop a theory for refinement and compatibility of PIOs with synchronous and asynchronous communication and show that our refinement relation, called blackbox refinement, satisfies fundamental properties such as transitivity and compositionality. Motivated by the aim to detect communication errors we take into account the asymmetry of sending (output) and receiving (input) messages and develop different notions of output compatibility with varying degrees of freedom for the interleaving of local, non-shared component actions. Based on an encoding of FIFO buffers we show that blackbox refinement is transferable to asynchronously communicating components. Moreover, we develop a notion of asynchronous output compatibility that is a natural extension of synchronous

output compatibility and show its preservation by blackbox refinement. The resulting theory is an interface theory in the sense of [BMSH10]. Concerning more general properties we define a greybox variant of blackbox refinement. Greybox refinement allows to distinguish internal labels and we show that greybox refinement preserves safety properties with regard to the communication traces of a composed system.

As a concrete syntax we use UML components with ports for the specification of static structures, state machines for the specification of behaviours, and protocol state machines for frames. By combining an industry-strength modelling language with a formal theory we obtain both a precise and well-understandable specification as well as an unambiguous meaning of dynamic system aspects.

With regard to verification we must take into account that systems of buffered PIOs are potentially infinite-state systems which makes most verification problems undecidable. We consider foremost the verification of asynchronous compatibility and discuss a criterion for closed systems based on synchronous compatibility. For the general verification support of buffered PIO systems we discuss a translation to Communicating Finite State Machines (CFSM) [vB78]. We develop a CFSM correspondence of asynchronous compatibility and sketch the application of a symbolic CFSM-based approach to its verification.

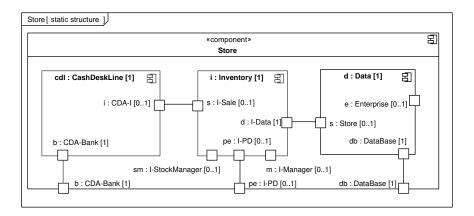

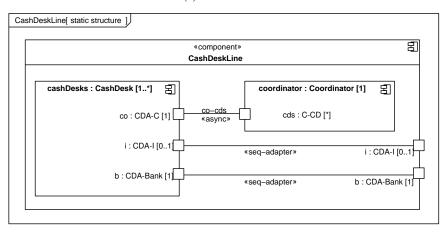

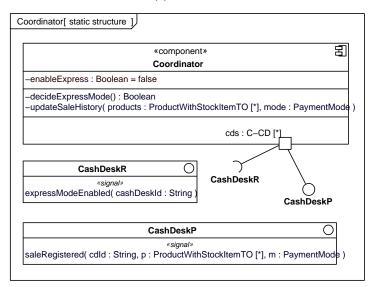

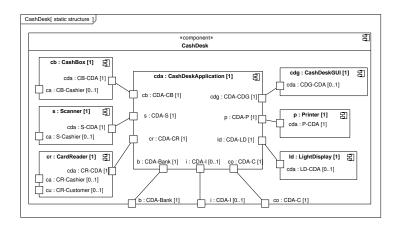

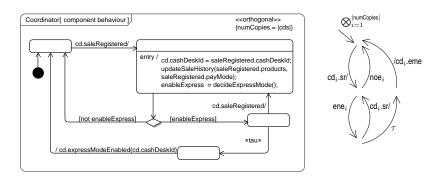

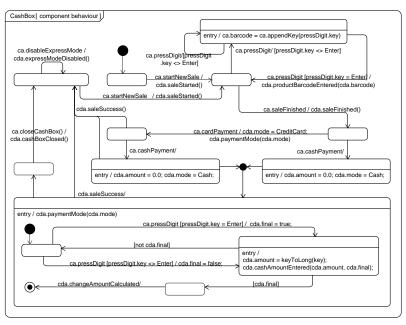

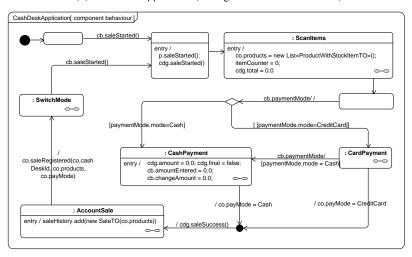

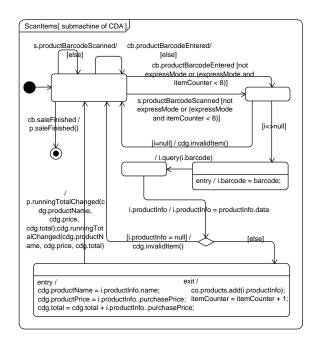

Finally, we illustrate the model developed within this thesis, using the Common Component Modelling Example (CoCoME). The CoCoME, initiated as a GI-Dagstuhl research seminar, aimed at a comparison of existing component models using a common requirement specification and reference implementation of a point-of-sale system. We consider UML specifications of static and dynamic system aspects, illustrate their translations to transition systems, and discuss proof obligations arising from behaviour, correctness, and frame analysis.

# Acknowledgements

I would like to thank my supervisor Rolf Hennicker for his guidance and support during all the years. The countless discussions about both, concepts and theory, often resulted in new ideas to extend and improve the results of this thesis. Rolf continously insisted on a conceptional sustainable and formally precise development and, by this means, contributed to a component model which is hopefully precise about concepts and, at the same time, in touch with practical applicability.

I am also deeply indebted to Alexander Knapp for many fruitful discussions and the joint work on our publications. Alexander's help in technical, but also in conceptional questions was invaluable. His intuition in formal reasoning repeatedly helped me to move on with the theoretical parts of my research. Moreover, I would like to thank Stephan Merz and Martin Wirsing for their reviews and critical reading of this thesis and the whole PST team for providing a perfect working atmosphere with lots of discussions, especially during the days we spent at our yearly "hut seminar".

Finally, I thank my wife Clarissa da Costa and my whole family for their encouragement and support. I am especially grateful to Gudrun da Costa for her language corrections of the informal parts of this thesis.

# **Contents**

| Chapt | er 1. Introduction                                             | 1   |

|-------|----------------------------------------------------------------|-----|

| 1.    | Component-Based Software Engineering                           | 1   |

| 2.    | Component Models and Distributed Systems                       | 4   |

| 3.    | Contribution and Overview                                      | 9   |

| Chapt | er 2. A Formal Model for Components with Behaviours            | 15  |

| 1.    | Port-Based Components and Behaviours                           | 15  |

| 2.    | I/O-Transition Systems (IOTS) with Queues                      | 22  |

| 3.    | Components with (A)Synchronous Communication                   | 26  |

| 4.    | Implementation using Message-Oriented Middleware               | 31  |

| Chapt | er 3. Behavioural Neutrality in Synchronous Assemblies         | 35  |

| 1.    | Syntactical Reduction of Synchronous Assemblies                | 35  |

| 2.    | Port-Based Views of Component Behaviour                        | 39  |

| 3.    | Application to the Compressing Proxy System                    | 43  |

| 4.    | Discussion and Related Work                                    | 44  |

| Chapt | er 4. A Theory for Refinement and Compatibility                | 47  |

| 1.    | Input-Persistent I/O-Transition Systems (PIO)                  | 48  |

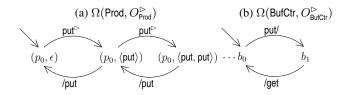

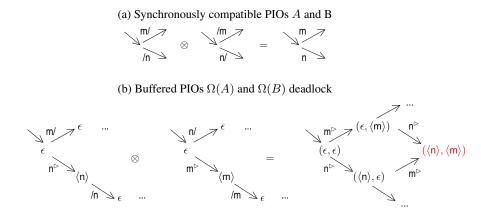

| 2.    | Asynchronous Communication                                     | 58  |

| 3.    | Compatibility and N-ary Composition                            | 64  |

| 4.    | Greybox Refinement and General Properties                      | 66  |

| 5.    | Discussion and Related Work                                    | 73  |

| Chapt | er 5. On the Verification of PIO Systems                       | 75  |

| 1.    | Verification Based on Finite-State PIOs                        | 76  |

| 2.    | Correspondence with Communicating Finite State Machines (CFSM) | 81  |

| Chapt | er 6. Frames for the Specification of Component Behaviours     | 99  |

| 1.    | Frame Specifications for Port-Based Components                 | 99  |

| 2.    | Compressing Proxy Revisited                                    | 103 |

| 3.    | Supporting Component-Based Development                         | 107 |

| 4.    | Port-Based Frame Verification of Communication-Safety          | 110 |

| 5.    | Related Work                                                   | 112 |

| Chapt | er 7. UML2 – Applied Features and Extensions                   | 113 |

| 1.    | Static Structure of Components and Assemblies                  | 113 |

| 2.    | Component Behaviour and UML State Machines                     | 117 |

| 3.    | Frame Specifications and UML Protocol State Machines           | 119 |

| 4.    | From State Machines to Transition Systems                      | 120 |

| Chapt | er 8. The Common Component Modelling Example (CoCoME)          | 125 |

| 1.    | Modelling of the CoCoME                                        | 125 |

| 2.    | Static Structures                                              | 126 |

| 3.    | Component Behaviours and their Translation                     | 129 |

| •••  | CONTENTE |

|------|----------|

| V111 | CONTENTS |

| 4. Hierarchical Component Behaviours                       | 131 |

|------------------------------------------------------------|-----|

| 5. Frame Specifications of Simple and Composite Components | 136 |

| 6. Analysis and Proof Obligations                          | 137 |

| Chapter 9. Conclusion                                      | 143 |

| 1. Related Work                                            | 143 |

| 2. Evaluation and Prospects                                | 152 |

| Bibliography                                               | 155 |

#### CHAPTER 1

### Introduction

| 1. | Component-Based Software Engineering     | 1 |

|----|------------------------------------------|---|

| 2. | Component Models and Distributed Systems | 4 |

| 3  | Contribution and Overview                | 0 |

The thesis starts with an introduction into component-based software engineering as a sub-discipline with distinct characteristics which allows us to separate it from other paradigms such as, for instance, object-oriented software engineering. In particular, we identify the specifics of component-based development to which the provision of an appropriate software component model is fundamental. A software component model defines what exactly components are and how they have to be composed in order to support the construction of larger systems. Software component models differ in variable classes of systems. Within this thesis we examine concurrent message-passing systems with synchronous and asynchronous message exchange and develop a formal software component model with a focus on modelling and behavioural analysis. After a discussion of what we believe constitutes a formal software component model, we summarise the contributions of this thesis and provide an overview of the single chapters.

#### 1. Component-Based Software Engineering

Component-based software engineering (CBSE) has emerged as a sub-discipline of software engineering aiming at the development of reusable components and component-based systems. Reusability might be achieved by composing systems out of prefabricated components which can be considered as key aspect of the paradigm underlying CBSE. In this context it is an important goal to be able to compose *without* reference to a certain implementation [Som06, Chap. 19]. Components are supposed to be delivered by third-parties, or at least by independent project teams, as binary units so that there is no necessity to compile a component before it is composed with other components to be integrated into a larger system. Therefore, it is important to develop components as encapsulated entities that are equipped with a precise specification of their static structure as well as their dynamic behaviour.

CBSE is rooted in a promise of software engineering with off-the-shelf components, developed by third-parties and composable for system construction without too much knowledge of component implementation details but with enough knowledge to judge appropriateness with regard to given requirements [NR68]. It turned out that it is extremely difficult to find the appropriate abstraction level for the unambiguous description of components. We believe that there is still no consensus of what constitutes a *complete* component description including an integration of control- and data-related specifications as well as an integration of non-functional properties. However, focused research on each of these issues is promising and it seems that an integrated description is not out-of-reach. In contrast, agreement seems to exist concerning the description of functional component properties that relate to the control behaviour of components. Control behaviour of components is usually specified by protocols describing temporal orderings of message exchange

1

or method calls. Then the relation to an implementation is either by a formal implementation relation or by code generation. Since implementations are equipped with data, these relations usually include an abstraction step.

Regardless of the concrete relation between specification and implementation, the specification of control behaviour is used for two complementary development concerns in CBSE. On the one hand, specifications are composed to compute the behaviour of an assembly of components. Moreover, they are abstracted, hiding internal details, to effectively construct behavioural specifications for hierarchical component-based systems. On the other hand, these descriptions are also used as a design specification for the *independent* development of components as mentioned above. Therefore, it is crucial to obtain a precise understanding of the interplay between composition and independent refinement respectively implementation. Formal software component models examined hereafter (cf. Sect. 3) aim at providing exactly such an understanding.

Besides system construction, also maintenance and evolution focus on components and their specification. Components are either replaced by new versions or existing components are modified. In both cases it is important to know about the effects of the modification before any part of the original system is indeed touched. Unambiguous specifications again may serve as a helpful tool. Altogether, CBSE is characterised as follows:

- (1) Independent development of reusable components

- (2) System development by assembly and hierarchical composition

- (3) Maintenance and evolution by substitution (and adaption) of components

Component development should be independent to support reuse, be it internal reuse within some given project or external in the sense that commercial prefabricated components are used. Moreover, independent development also leads to looser coupling of an integrated system and therefore helps in understanding the structure and behaviour of large component-based systems. The key to CBSE is composition. Systems are developed by composition of components and connectors, resulting in what is called an assembly. Assemblies in turn can be encapsulated within a composite component that can again be used for composition with other components and connectors. In this way, CBSE features a form of hierarchical composition. Finally, maintenance and evolution of a component-based system proceeds mainly by component substitution. Of course, also adaption of existing components, or more precisely, of existing component implementations plays an important role. However, such an adaption might also be understood as a substitution using a new component with an equivalent specification, but modified implementation.

Component-Based Development. We refer to the development process embedded within CBSE by *component-based development* (*CBD*). In general, system construction often follows either a top-down approach where initial system requirements are decomposed into parts that are refined stepwise until an executable system is finally obtained, or bottom up where first the parts of a system are designed in detail and then the parts altogether are composed to achieve an implementation with respect to given requirements. CBD often follows a mixture of top-down and bottom-up steps during system development. While one starts with general system requirements and proceeds top-down to construct a component architecture appropriate for the given requirements, one also searches for existing components that might be reusable for the construction of the given system. If such a component indeed exists, it is integrated into the existing architecture in a bottom-up way. The following (simplified) steps might be considered to be characteristic for component-based system development; cf. [Crn03, p.155] or [Som06, Sect. 19.2]:

<sup>&</sup>lt;sup>1</sup>CBD is sometimes also denoted as component-based system development (CBSD). The notion of CBSE is usually used in the broader sense of an engineering discipline; cf. [Crn03] for instance.

- (1) Identify usable components (e.g. repository)

- (2) Select components; refine or modify requirements

- (3) Adapt or implement missing components

- (4) Compose and deploy components (after validation)

- (5) Maintain system by replacing or modifying components

The identification of usable components is guided by the initial requirements for the system under construction. Since CBSE aims at reuse of existing components, this activity appears quite early in the development process. The components are selected, and according to component availability, requirements might be modified (if a system is constructed faster due to reused components, clients might be willing to accept modifications of their initial requirements). It is unlikely that all required components are already available, hence it is necessary to adapt existing or implement new components in order to fill gaps due to missing components. After that, the final set of components is validated, composed, and deployed. Note that the previous step of component implementation may already involve component composition for the realisation of composite components. Finally, and as mentioned in the more general context of CBSE above, maintenance is characterised by substitution of existing components. Either we replace a complete component, or we may modify its implementation.

Fundamental to the CBD process is the general component model chosen as an appropriate means to model the given system under construction. More precisely and following Lau and Wang [LW07], it is the *software component model* which plays a key role during component-based development. A software component model defines the syntax, the semantics, and the composition of components relating to the following questions: How are components represented? What exactly are components? How are components composed? Software component models (SCM) are supposed to answer these questions for the complete life cycle of a component: design, deployment, and runtime.<sup>2</sup>

Concerning the design of components, there is a long-standing research direction in the context of architectural description languages (ADL). Research within this area usually focused on the design and analysis of systems composed of "architectural units". Two prominent ADLs, Darwin [MDEK95] and Wright [AG97], using components and connectors as their architectural units are considered more detailed in our comparison with related work in Chap. 9. Opposed to the design focus of ADLs, there exist industrial component-based frameworks with an implementation focus such as CORBA [OMG] or Microsoft .NET [Mic, TGG+05]. Since the component models of these frameworks do usually not fully support the component concepts underlying the models of ADL approaches, a number of frameworks, e.g. Fractal [BCL+06] or SOFA [BHP06], and architectural programming languages, e.g. Java/A [Hac04], ComponentJ [SC00] or ArchJava [ACN02], emerged that try to close the conceptual gap between design and implementation of component-based systems.

All of the component models mentioned above have in common that a particular software component model is defined and used. However, since the concepts of the models differ sometimes considerably, one may ask to what extend the main CBSE characteristics stated above are indeed supported within the respective approach. Lau and Wang discuss this issue with a focus on the life cycle of components and use a slightly extended list of characteristics that is already biased by their notion of *software* component model and therefore provides a useful reification of the more general characteristics for CBSE: "[..] components should be produced and used by independent parties", "[..] components should be composable into composite components", "[..] it should be possible to copy and instantiate components"

<sup>&</sup>lt;sup>2</sup>In terms of programs one may think of a program design, an installed program and a running program

and "Composition means [..] also a systematic approach to system construction" [LW07, p. 709].

The first three requirements directly translate the general characteristics of reusability, independent implementation, and hierarchical composition as discussed in CBSE context above. The remaining aspects, however, provide more detailed requirements. First, instantiation of components calls for a notion of declarations to be used for system construction. For this reason, component type descriptions are needed that may be (re)used within a declaration similar to attribute declarations within a class of some object-oriented language. Second, the aim of a "systematic approach to system construction" based on composition obviously entails their requirement on hierarchical composition with composite components, but may additionally be considered to be a call for the general support of top-down and bottom-up approaches to system development. Due to their explicit distinction between design-time, deployment and runtime entities, a systematic approach should provide a link between deployed and running entities (at the bottom of a system development) and their design specifications (at the top of a system development). Therefore, if an entity on either level is touched (e.g. replaced or modified), the consequences for the other level should be clear. Such a notion of software component models gives rise to characteristics of component-based development along a certain SCM as shown in Fig. 1.1.

- (1) Independent development of reusable component types

- (2) Reusability of component types along declarations

- (3) System development by assembly and hierarchical composition

- (4) Maintenance/Evolution by substitution (and adaption) of component types

- (5) Support for top-down and bottom-up system development

FIGURE 1.1. Characteristics of component-based development

Lau and Wang point to the necessity to have a composition theory available that allows a formal reasoning about composition [LW07, p. 711]. One of the aims is to be able to predict the effect of component composition. We think that this remark directly leads to the notion of *formal* software component models as discussed in Sect. 3 below. A formal software component model is a SCM that supports formal reasoning about the behaviours of components and their composition.

#### 2. Component Models and Distributed Systems

Any software component model must be precise about the mechanisms of component composition within the particular model. Depending on what a component exactly consists of, such a composition means that components are somehow connected allowing to interact respectively to communicate with each other. Note that here and in the following text we will use *interaction* and *communication* synonymously. There is no hidden means of interaction in component-based systems. Components must provide a public interface<sup>3</sup> that describes the possibilities to interact with that component. Due to this strict encapsulation, it does not seem to make much difference if we talk either of interacting or of communicating components.

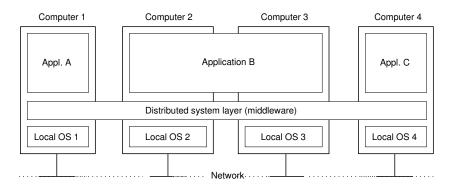

One particular class of systems whose development might take the most advantage out of a component-based approach are distributed systems. Andrew S. Tanenbaum provides the following loose characterisation of this class of systems: "A distributed system is a collection of independent computers that appears to its users as a single coherent system" and gives a schematic view as depicted in Fig. 1.2 [TM07].

One of the important characteristics of distributed systems is the possibility of uniform interaction between different applications despite possibly different operating systems or particular network services. *Middleware* aims, amongst others, at providing this means

<sup>&</sup>lt;sup>3</sup>Here we do not yet refer to the technical notion of UML or Java interfaces

FIGURE 1.2. Distributed systems and middleware (from [TM07, Fig. 1-1])

and is realized by a software layer that spans over all machines which should be integrated into a distributed system. The software then provides communication facilities for the particular applications hiding away heterogeneous operating systems or network services.

The given figure shows that systems of this kind fit well with the characteristics of component-based systems. The different applications correspond to components and the middleware providing the communication facilities implements connectors that are used by the particular applications to communicate with each other. The distributed application B could be modelled by a composite component that consists of two subcomponents executing on computer 2 and 3 respectively.

Communication in distributed systems is always based on message passing [TM07, p. 115] which is mainly due to the fact that there is no shared memory in a distributed system. Applications send and receive messages using the given middleware. Even though the availability of concrete communication facilities depends on the implementation of the middleware, there are important general properties of communication that can be discussed independently from concrete implementations. Amongst others one may distinguish synchronous and asynchronous communication. With synchronous communication a "sender is blocked until its request is known to be accepted" whereas with asynchronous communication the "sender continues immediately after it has submitted its message for transmission" [TM07, p. 125]. Two important corresponding communication mechanisms are remote procedure call (RPC) and message-oriented middleware (MOM). The former aims at providing a more convenient way of interprocess communication than the latter. In fact, message-oriented communication is considered as a low-level mechanism that might be used as a mechanism to realize remote procedure calls. The basic idea of RPC is simple: instead of calling a procedure on the same machine, it is possible to call a procedure on a different machine. There are a number of technical difficulties, but the basic concept remains. Concerning synchronisation, as in local calls, the sender is blocked until the result returns. There is also a notion of asynchronous RPC that we do not further elaborate here and refer to [TM07] instead. The notion of remote method invocation (RMI) is principally equivalent to RPC. The main difference is that RMI applies to object-based distributed systems. Thus, methods are invoked on remote objects using global object references. While RPC is usually used to enable synchronous communication between distributed applications, message-oriented middleware allows for asynchronous communication that completely decouples the sender and receiver of messages. The receiver of a message must not even exist at the time some application sends out a message. In case

<sup>&</sup>lt;sup>4</sup>Note that this notion of synchronicity could be interpreted in the sense of process algebraic rendezvous synchronisation: if several outputs are available, the sender is blocked before committing to any output and released as soon as it is known which outputs are accepted

of so-called persistent communications, the middleware will store the particular message until some receiver comes back to live again.

Message-oriented systems usually allow for message exchange following a point-to-point or a publish/subscribe pattern. For instance, Java Message Service (JMS) [Mic02], a specification for message-oriented middleware implementations in Java, exactly considers these two models of message exchange. With point-to-point communication the sender and receiver of messages use queues for buffered communication. With the publish/subscribe model so-called topics are used to which a receiver subscribes. In case a sender publishes a message related to this topic the receiver is notified accordingly. A more detailed description of these modes of communication is given in [Mic02], and more concretely in the context of the reference implementation of JMS in [Mic07].

The publish/subscribe model is directly related to the support of *group communication* in distributed systems. Following the terminology used by [**Kaa92**], group communication denotes sending of messages from 1 to *n* destinations; with *broadcast*, a group communication is implemented that requires all destinations to receive the message, while *multicast* requires reception only by those that indeed had announced interest before.

As apparent from a further study of the goals of distributed systems [TM07, pp. 3– 15], the communication mechanisms mentioned find their counterpart in the behavioural descriptions of components and their composition. Formal software component models provide a perfect match with the goal of "openness". An open distributed system is a system that provides services through interface definitions. These specifications must not only cover syntactical issues, such as available operation signatures, but they are also expected to provide semantical information such as the effect of a particular service. In [TM07, p. 8] the importance of proper interface specifications in order to support "interoperability" and "portability" is stressed. The former relates to interaction between different applications that relies solely on the interface specifications, and the latter refers to the possibility to reuse an application in distributed systems that implement the same interfaces. We would claim that these characteristics are covered by independently developed component types that are reused and composed based on their behavioural specifications only. Portability may additionally require support for bottom-up system development which allows to first develop a single component in great detail and then to put this component into a larger context again by composition that relies on the specification of the particular component.

Since, in comparison with RPC, message-oriented communication is considered the more basic, low-level communication mechanism [TM07, Kaa92], labelled transition systems seem to provide an appropriate formalism for a precise abstract representation of these specifications. Indeed, transition systems are an established and widely used operational model for the modelling and analysis of parallel systems, in particular for message-passing systems. Baier and Katoen define two basic mechanisms for the description of communication in the context of transition systems; messages are either transferred synchronously using a handshake mechanism (rendezvous) or asynchronously by buffered message exchange using channels [BKL08, pp. 35 ff.]. Analysis of systems with buffered message exchange is notoriously difficult. If the channels are assumed unbounded (for more convenient modelling purposes), the underlying transition systems are potentially infinite-state making nearly any verification problem undecidable [BZ83]. However, even if the channels are bounded by some fixed capacity, the state-space soon becomes too large to apply finite-state verification techniques effectively. This is one of the reasons why synchronous communication based on a handshake mechanism, as prevalent in most process algebraic theories, is an important means of modelling and analysing the behavioural aspects of component-based systems. The transition systems resulting from the synchronous composition of communicating components consist only of successful communication traces and thus are usually much smaller with regard to the global state space. Note that "successful"

7

is defined independently from the communication direction. If a sender may choose nondeterministically among a set of alternative output transitions, all of these outputs are considered for synchronisation with corresponding input transitions of a potential receiver. In this vein only the successful synchronisations show up in the composed transition system. Since these transitions correspond to the potential communications between components, the synchronous mechanism yields a correct but incomplete representation. In particular, when it comes to analysing communication errors like messages sent that are not received, this issue of incompleteness is of major importance.

The combination of the characteristics of concurrent message-passing systems such as distributed systems and a formalisation of communication based on transition systems yields a *formal component model* with a precise definition of static entities and their means of interaction. Components represent possibly hierarchically structured applications that communicate with each other via synchronous and asynchronous connectors. Communication consists of sending and receiving messages, and is described by behavioural specifications based on transition systems. The composition of components and connectors is called an assembly whose behaviour is a derived transition system. Composite components use assemblies for their implementation again showing a derived behaviour that is based on the behaviour of the encapsulated assembly.

The following example illustrates a specification of a simple component-based system, exemplifying the concepts introduced so far. In particular, we would like to illustrate the relation to distributed systems as an example for an implementation within the general class of concurrent message-passing systems.

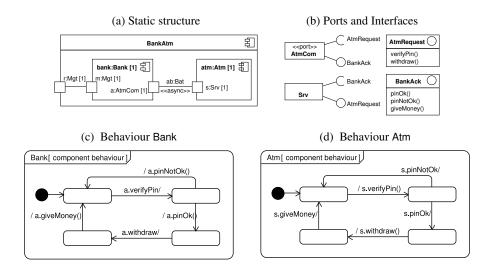

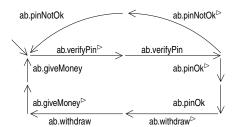

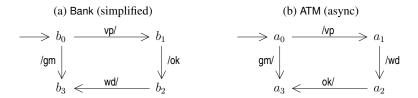

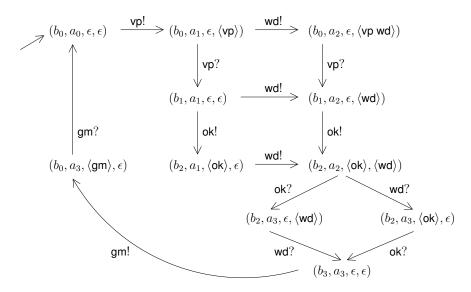

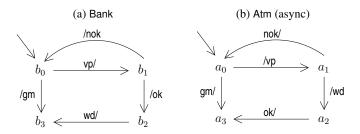

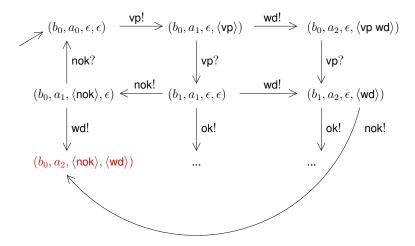

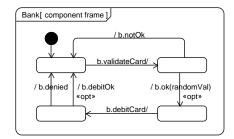

**Bank/ATM System.** In the following we specify a simple Bank/ATM system using the UML2 for static structure specification and UML state machines for the behavioural descriptions. We do not aim at illustrating or explaining available modelling features in detail. We rather would like to give a small example to clarify some of the main concepts of component-based systems introduced so far.

Figure 1.3 shows the specification of the system. A composite component with type BankAtm contains an assembly of two simple components with types Bank and Atm used for the component declarations bank:Bank and atm:Atm. Ports specify typed interaction points of a component. The simple component types Bank and Atm have port declarations a:AtmCom, m:Mgt and s:Srv respectively that are connected with an asynchronous assembly connector called ab and type Bat and an anonymous delegate connector. The two simple component declarations and the assembly connector form an assembly with open port m:Mgt. The provided and required interfaces of the port types AtmCom and Srv with their operations are depicted using the UML ball-and-socket notation on the right-hand side of Fig. 1.3. The port type Mgt is specified analogously and not further described. If two ports are connected by an assembly connector, the provided interface of one port has to match the required interface of the other and vice versa. The open port of the assembly is connected to the port declaration r:Mgt of the composite component BankAtm. Here, we reused the same port type, but in general one may also use a different type as long as the particular interfaces match.

Our behavioural descriptions are based on transition systems with distinguished input, output, and internal actions focusing on the temporal order of messages sent and received interspersed with local internal computations. For the concrete specification we use a simple subclass of UML state machines. Hence, any existing UML modelling tool can be used for the design of port-based components. Behaviours for the component types Bank and Atm are given in Fig. 1.3. Input and output messages are indicated by p.m/ and /p.m, respectively, where p is the port name on which the message m is sent or received respectively. The behaviours are slightly simplified as they do not show internal actions and the bank behaviour does not make use of the port m:Mgt. The behaviour of the assembly and

FIGURE 1.3. Specification of a simple Bank/ATM system

the composite component is derived from a combination of the behaviours for the components Bank and Atm. The behaviour at the ports m:Mgt and r:Mgt, however, is trivial due to the simplified presentation of the bank behaviour sending and receiving messages via port a:AtmCom only.

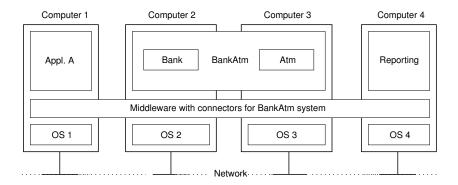

Figure 1.4 illustrates a possible realisation as a distributed system. Note that the figure is not supposed to specify a formal deployment view to the given system, but merely takes up the schematic view of Fig. 1.2 neglecting any questions related to types, instances, or concrete connections. The composite component BankAtm is realised as a distributed application. The application Report is assumed to be realised by a component that connects to the open port r:Mgt of BankAtm.

FIGURE 1.4. Bank/ATM distributed system

Now immediately the important question arises about what exactly is the role of the component behaviours given above with regard to such a realisation? Obviously the behaviours should be used for formal reasoning about the given system, but what are the properties of interest? What are notions of correct implementations allowing to replace a component of the given system without effect on the remaining components? These and similar questions will be addressed in the context of this thesis on the basis of an appropriately defined and formally precise software component model.

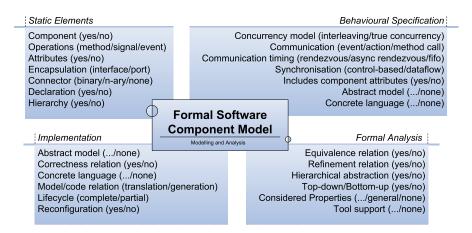

FIGURE 1.5. Aspects of formal software component models

#### 3. Contribution and Overview

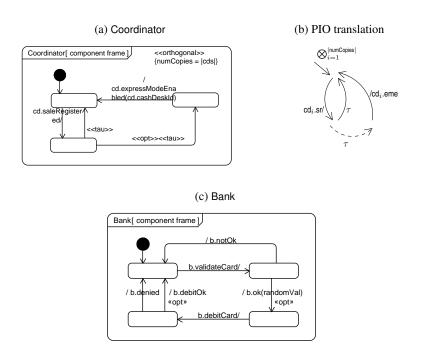

Within this thesis we develop a formal software component model with a focus on modelling and general behavioural analysis. Figure 1.5 provides an overview of what we think are fundamental categories and aspects in this context (values given in parentheses are used for a comparison with related work in Chap. 9). The given categories can be aligned to the notion of software component model as discussed above (cf. Sect. 1). The static elements define how components are represented, and together with behaviour and implementation it is also defined what is represented. Moreover, the execution model underlying the behavioural aspects additionally defines how components are composed and hence the categories indeed cover all information that constitute a software component model in the sense of Lau and Wang. However, we draw a sharper line between component and software component models, since we require an explicit distinction between specification and implementation of component behaviour to qualify as a software component model. In contrast, our requirements on support for formal analysis again may be put into line along the notion of *composition theory* [CSSW04] mentioned by Lau and Wang; cf. [LW07, p. 711]. A composition theory formally describes the result of applying component composition. We understand composition here in a broader sense, including a form of hierarchical composition using blackbox views of component behaviour.

As evident from Fig. 1.5, formal software component models integrate aspects from different but closely related domains. For instance, we use the UML2 [RJB05] for the concrete specification of structural and dynamical aspects of port-based components. Inspired by ROOM [SGW94] we favour port types as an explicit means for structural specification of interaction points, which is in contrast to strictly interface-based component models. Our component model is a formally defined software component model aimed at being used for architectural design specifications of concurrent systems that rely on messageoriented communication. This choice is directly reflected in our execution model that uses an interleaving model of concurrent message exchange. In contrast to most other approaches we do not restrict to synchronous rendezvous communication, but also consider asynchronous FIFO buffered communication. The behavioural model is backed by input-persistent I/O-transition systems (PIO) being a specific class of modal I/O automata [LNW07]. Implementations are represented abstractly by completely persistent PIOs coinciding with I/O-transition systems that in turn are based on interface automata of de Alfaro and Henzinger [dAH01a]. To illustrate specifications with a concrete language we will use a restricted class of simple UML state machines for implementations and protocol state machines for specifications. In order to illustrate implementations along a concrete

programming language we discuss the implementation of port-based components based on the Java Message Service specification JMS [Mic02].

We define equivalence relations similar to process algebraic approaches such as Wright, Darwin, and more recently PADL [BCD02]. Most importantly, we define refinement relations for specifications related to [dAH01a, LNW07] as well as a correctness relation between specifications and abstract models of implementations methodologically related to [PV02]. Finally, we aim at providing *formal* support for component-based design which in particular means to allow hierarchical abstraction, to support top-down and bottom-up approaches to system design, and to support "component-wise evolution" as discussed in [dAH01b] and similar also in [PV02]. As a concrete property being preserved during top-down or bottom-up development steps we consider communication-safety. This property implies the absence of architectural incompatibilities in the sense of [BOR04] or [AP05]. Concerning general properties we discuss the preservation of safety properties based on finite and infinite execution traces of a system, showing similarities with Tracta [Gia99].

Even though each of the mentioned aspects is covered by a number of related works, a formal software component model addressing an integrated view on the different aspects together with support for asynchronous message exchange as prevalent, for instance, in distributed systems is still missing. Especially, the formal relation between abstract models of behaviour specifications and models of implementations is often neglected. However, a precise theory for specification refinement and implementation correctness is crucial for a proper support of hierarchical system construction in the context of component-based system development. Moreover, a statement on specific and general properties that are preserved by correct hierarchical system construction is important to indicate the applicability of the developed theory. Here, the integration of asynchronous communication imposes particular difficulties. The contributions of this thesis in these aspects are as follows:

- (1) An integrated formal software component model is developed that covers both, static and dynamic aspects of hierarchical system development. Ports play an important role for the structural definition of components' interaction points.

- (2) Models for the specification and implementation of component behaviours are distinguished and a theory for refinement and implementation correctness is developed. The models take asynchronous communication into account by an integration of FIFO queues for buffered message exchange. It is shown that hierarchical component-based system development is properly supported by the formal part of our component model.

- (3) Notions of synchronous and asynchronous compatibility are developed, exemplifying specific properties that are of interest in the context of formal behavioural analysis. The preservation of safety properties is examined as an example for more general properties. The verification of asynchronous compatibility in closed systems is addressed by a criterion based on synchronous compatibility. General verification of systems with asynchronous communication is addressed by a translation to Communication Finite State Machines (CFSM).

**Overview.** Table 1.1 shows an overview of the definitions for syntax and formal models used by our component model. The numbers in parentheses refer to the corresponding chapter. An abstract syntax and formal model for static specifications is defined by a metamodel and a set-theoretical (algebraic) model in Chap. 2. For dynamic system aspects we distinguish the implementation and specification of component behaviours by "behaviours" and "frames". The formal model of behaviours uses I/O-transition systems (IOTSs) and is developed in Chap. 2. Before our component model is extended with an abstract syntax for frames in Chap. 6, we develop a refinement theory based on input-persistent I/O-transition systems (PIOs) in Chap. 4. The concrete syntax is defined in Chap. 7, using UML components with ports for static structures, and simplified variants of UML state machines (STMs) and protocol state machines (PSMs) for behaviours and frames. In the following

we give a more detailed overview of the mentioned and the remaining chapters of this thesis.

| Component | Abstract Syntax            | Formal Model          | Concrete Syntax              |

|-----------|----------------------------|-----------------------|------------------------------|

| Static    | Metamodel (2)              | Algebraic model (2)   | UML Components (7)           |

| Dynamic   | Behaviour (2)<br>Frame (6) | IOTSs (2)<br>PIOs (4) | UML STMs (7)<br>UML PSMs (7) |

TABLE 1.1. Syntax and formal models

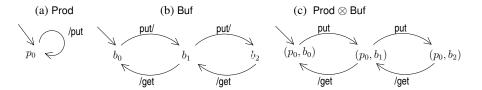

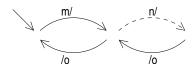

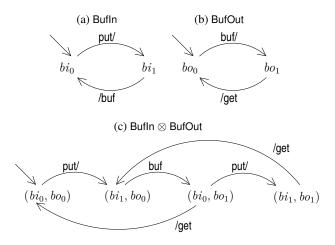

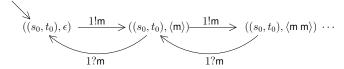

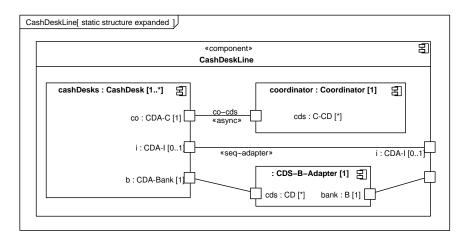

In Chapter 2 we develop a formal model for port-based component behaviours with synchronous and asynchronous communication. The general concepts are defined by a metamodel and illustrated using the example of a compressing proxy system. The metamodel is complemented by an algebraic model, making precise the core structural elements and behavioural features of port-based component systems. Component behaviours are formally represented by I/O-transition systems which are equipped with basic operators and equivalence relations as known from process algebraic languages such as CCS [Mil89] or FSP [KM06]. Message queues are encoded by I/O-transition systems and composed with component behaviour, resulting in systems with FIFO buffered message exchange. On this basis we define a formal model for components with behaviours that communicate by synchronous and asynchronous message exchange. We include guidelines for implementations based on message-oriented middleware using JMS and its reference implementation Open Message Queue [Mic07].

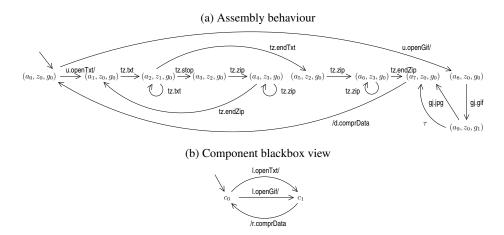

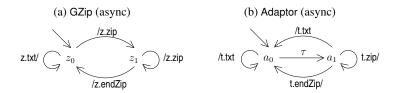

Support for the construction and behavioural analysis of large scale component-based systems that communicate solely by synchronous communication is developed in Chapter 3. In this way, also an application of the formal model of Chap. 2 is illustrated. The crucial concept is a notion of neutral component behaviour. Component behaviour can be considered to be neutral within a given assembly if its composition does not show an effect on the assembly behaviour apart from the synchronisation of shared transitions without loosing any transition of the original assembly behaviour. A major result of this chapter is an algorithm that shows how to remove neutral components for the computation of a syntactically reduced but behaviourally equivalent assembly. A reduced assembly may then be used to implement a given composite component in a more efficient way. Moreover, we show that it is sufficient to perform neutrality checks using the projection of a component behaviour to one of its ports, provided that the projected behaviour is a weakly deterministic I/O-transition system. The port projection is usually a simpler and smaller transition system, at least after minimisation with respect to greybox respectively blackbox equivalence. The approach is illustrated with the compressing proxy system introduced in Chap. 2.

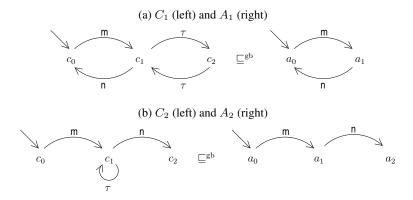

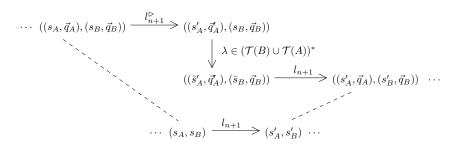

Chapter 4 elaborates a theory for refinement and compatibility of PIOs with synchronous and asynchronous communication. In order to support hierarchical system development and analysis of component behaviours, the refinement relation should satisfy fundamental properties such as reflexivity, transitivity, and compositionality. Moreover, the relation should, on the one hand, preserve as much properties as possible, but on the other hand leave enough freedom for concrete design decisions. Our study is motivated by the aim to detect behavioural incompatibilities as discussed in Chap. 2, taking into account the asymmetry of sending (output) and receiving (input) messages. We develop different notions of output compatibility with varying degrees of freedom for the interleaving of local, non-shared component actions. It turns out that, in order to preserve output compatibility, we need additional information that allows to couple the message transfer with the refinement of the transition that specified the transfer. On this account our approach extends I/O-transition systems to input-persistent I/O-transition systems (PIO) and defines a blackbox refinement relation that demands the preservation of persistent transitions. The

relation is denoted "blackbox" because it ignores differences of internal labels. PIOs can be considered as a special case of modal I/O automata (MIO) and then, blackbox refinement corresponds to weak modal refinement.

Our theory is required to cope with FIFO buffered message exchange. Based on an encoding of FIFO buffers we show that blackbox refinement is indeed transferable to asynchronously communicating components. Moreover, we develop a notion of asynchronous output compatibility that is a natural extension of synchronous output compatibility to an asynchronous setting and show its preservation by blackbox refinement. The resulting theory is an interface theory in the sense of [BMSH10], which is briefly discussed in Sect. 5 of Chap. 4.

Additionally, we define communication-safety as a notion of output compatibility for n-ary compositions of PIOs. We show that blackbox refinement of single transition systems preserves communication-safety of their composition and, moreover, investigate to what extend pairwise analysis of output compatibility implies communication-safety. Finally, we consider more general properties and a greybox variant of our refinement relation. Greybox refinement distinguishes internal labels. We show that greybox refinement preserves safety properties with regard to the communication traces of a composed system and briefly discuss counter-examples for the preservation of liveness properties.

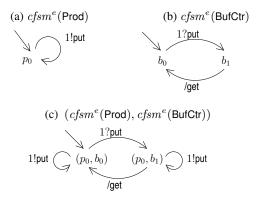

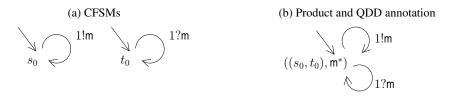

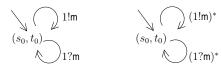

In *Chapter 5* we consider foremost the verification of asynchronous communication-safety. Due to the modelling with unbounded FIFO queues, we must take into account that systems of buffered PIOs are potentially infinite-state systems which makes most verification problems undecidable. We investigate a criterion for asynchronous communication-safety in closed systems based on synchronous compatibility. An important additional assumption, input-separation of the underlying transition systems, is conceptionally related to single-threaded components. For the general verification support of buffered PIO systems we discuss a translation to Communicating Finite State Machines (CFSM) [vB78]. CFSM systems consist of finite state machines communicating with each other via unbounded, full-duplex, and error-free FIFO channels. Thus, there is a close relationship of systems of buffered PIOs and CFSM systems. We describe a translation of IOTSs to CF-SMs and develop a CFSM correspondence of asynchronous communication-safety. After that we sketch the application of a symbolic CFSM-based approach to the verification of asynchronous communication-safety. Finally, necessary extensions to verify PIOs instead of IOTSs are briefly discussed.

With the basic formal model in Chap. 2 components are equipped with behaviours (formalised by I/O-transition systems) that are supposed to represent the implementation of a component. Chapter 6 extends this model by a specification layer with so-called component frames using the theory developed in Chap. 4. Frames are formally related to behaviours by a correctness relation: the semantics of a frame is the class of all behaviours which are a blackbox refinement of the frame. We illustrate the completed component model using the compressing proxy system from Chap. 2. After that, we show that the model supports important characteristics of component-based development. We examine support for top-down and bottom-up design approaches and, moreover, show that component-wise evolution [dAH01b] is supported in hierarchical systems. Top-down design starts with a frame F that is refined to a composition of several frames. Then, support for top-down design allows to conclude that the composition of component-wise correct blackbox refinements yields a correct implementation of the original frame F. By this kind of support it is shown that the definitions of refinement and implementation relations work smoothly together.

Bottom-up design first details the implementation of single components. If the behaviours are correct, i.e. they are a blackbox refinement of the frame of the respective component, then support for bottom-up design allows to conclude that the behaviour composition yields a greybox refinement of the corresponding frame composition. In this way it

is shown that the implementation relation preserves "greybox properties" of compositions and thus supports, for instance, analysis of communication traces in composed systems.

Finally, we discuss a port-based approach for the verification of compatibility and communication-safety based on frames and port protocols illustrating the fundamental difficulty of making effective use of port protocols that hide too much of the component behaviour.

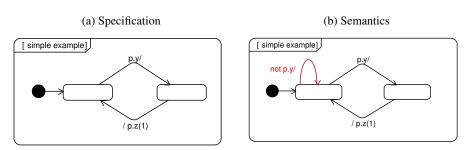

In *Chapter 7* we define a concrete syntax for our component model using UML2 components with ports, state machines and protocol state machines. We summarise applied UML2 features and explain the meaning of additional notations and stereotypes. We relate static structure elements with our formal model and discuss an informal pattern-based translation from state machines to transition systems. Based on this translation we define the relation between UML state machines and protocol state machines, and component behaviours and frames as considered in Chap. 6. In this way, we may apply our theory as a formal underpinning for the definition of a UML-based theory of refinement (protocol conformance) and compatibility.

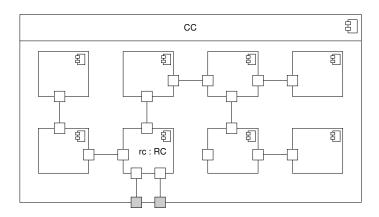

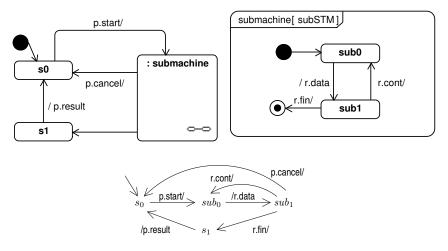

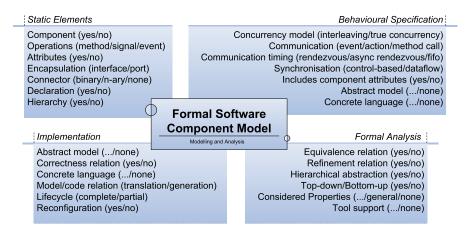

Availability of a concrete specification language was of particular importance for the modelling of the Common Component Modelling Example  $^5$  (CoCoME) in  $[{\bf KJH}^+{\bf 08a}]$ . CoCoME was initiated as a modelling contest aiming at a comparison of existing component models based on a common requirement specification and reference implementation of a point-of-sale system. Chapter 8 revises our initial submission and illustrates features of our component model that were not available at the time of writing [KJH+08a]. The formal model sketched in [KJH+08a] considered only synchronous communication along a rendezvous mechanism. It did not distinguish between behavioural specification (frames) and implementation (behaviours) of components and it did not feature a theoretical model for refinement and compatibility. We provide a brief introduction to the CoCoME requirements and elaborate on our static structure specifications using UML class and component diagrams, and on our modelling of component behaviours using UML state machines. We illustrate the modelling of more complex component behaviours using hierarchical UML submachine states and translate selected behaviours to IOTSs based on Chap. 7. We specify component frames for simple and composite components using UML protocol state machines and discuss the analysis of compatibility, implementation correctness and refinement on the level of the corresponding transition systems.

The main part of the conclusion in *Chapter 9* discusses related work with respect to the aspects of formal software component models given by Fig. 1.5. We consider as relevant for a more detailed comparison only those component models from the literature that have similar objectives like Sofa 2.0 [BHP06], GCM/Fractal [HKR08, BABC+09], STSLib [FR08], FSP/Tracta [KM06, GKC99], and Wright [AG97]. We conclude with remarks on prospects, limitations and future work.

**Publications.** The thesis is based on publications as listed below. In (P1) we modelled and analysed the CoCoME using the Java/A component model. The study in (P2) focused on the detailed development of a behavioural theory using I/O-transition systems. Finally, in (P3) we extended the model to take into account asynchronous communication. In the following we briefly relate the publications to the chapters of this thesis.

(P1) Alexander Knapp, Stephan Janisch, Rolf Hennicker, Allan Clark, Stephen Gilmore, Florian Hacklinger, Hubert Baumeister, and Martin Wirsing. Modelling the CoCoME with the Java/A Component Model. In Andreas Rausch, Ralf Reussner, Raffaela Mirandola, and Frantisek Plasil, (Eds.): The Common Component Modeling Example: Comparing Software Component Models, LNCS 5153, pp. 207–237. Springer, Heidelberg (2008).

<sup>5</sup>http://www.cocome.org

- (P2) Rolf Hennicker, Stephan Janisch, and Alexander Knapp. On the Observable Behaviour of Composite Components. Electronic Notes in Theoretical Computer Science (5th FACS'08), Vol 260 (1) Jan 2010, pp. 125–153.

- (P3) Rolf Hennicker, Stephan Janisch and Alexander Knapp. Refinement of Components in Connection-Safe Assemblies with Synchronous and Asynchronous Communication. Christine Choppy and Oleg Sokolsky (Eds.): Monterey Workshop 2008, LNCS 6028, pp. 154–180. Springer, Heidelberg (2010).

The Java/A component model described in (P1) provided the basis for a metamodel in (P2) for components with (observable) behaviours and synchronous communication. Parts of the modelling of the CoCoME in (P1) appear in Chap. 8. The formal approach to deadlock analysis of (P1) evolved into the formal behavioural model based on I/O-transition systems in (P2), yet without asynchronous communication. The analysis techniques developed in (P2) appear in revised and aligned form in Chap. 3

(P3) extends the behavioural component model of (P2) with asynchronous communication. The resulting metamodel and algebraic model appears in revised and slightly extended form in Chap. 2. Furthermore we developed a compositional theory for refinement, defined a notion of asynchronous compatibility (called buffered compatibility) and showed for closed systems with two components the preservation of compatibility under further assumptions like input-separated component behaviours. However, the approach did not carry over to open systems. Even though we believe that a generalisation to arbitrary closed systems is possible, we did not pursue the approach of (P3). Instead, we developed a new theory using input-persistent I/O-automata that appears in Chap. 4. The criterion for asynchronous compatibility in Chap. 5 was inspired by a corresponding theorem in (P3).

#### CHAPTER 2

## A Formal Model for Components with Behaviours

| <b>1.</b> ] | Port-Based Components and Behaviours               | 15 |

|-------------|----------------------------------------------------|----|

| 1.1.        | Concepts of Port-Based Components                  | 16 |

| 1.2.        | Example: Compressing Proxy System                  | 17 |

| 1.3.        | Composition and Behavioural Incompatibilities      | 20 |

| 2.          | I/O-Transition Systems (IOTS) with Queues          | 22 |

| 2.1.        | Transition Systems with Partitioned I/O-Labellings | 22 |

| 2.2.        | Operators on I/O-Transition Systems                | 23 |

| 2.3.        | Greybox and Blackbox Equivalence                   | 24 |

| 2.4.        | Encoding of FIFO Queues                            | 26 |

| 3.          | Components with (A)Synchronous Communication       | 26 |

| 3.1.        | Ports, Components, and Connectors                  | 26 |

| 3.2.        | Assemblies and Composite Components                | 28 |

| 4.          | Implementation using Message-Oriented Middleware   | 31 |

| 4.1.        | Java Message Service and Open MQ                   | 31 |

| 42          | Implementation of Port-Based Components            | 32 |

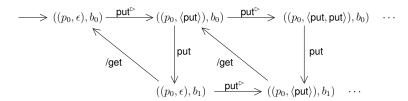

This chapter develops a formal model for systems of port-based components with synchronous and asynchronous communication. The general concepts are defined by a metamodel and illustrated using the example of a compressing proxy system. The metamodel is complemented by set-theoretical definitions stating precisely the core structural elements and behavioural features of port-based component systems. Component behaviours are formally represented by I/O-transition systems that are equipped with basic operators and notions of equivalence as known from process algebraic languages such as CCS or FSP. Message queues are encoded by I/O-transition systems and composed with component behaviour, resulting in systems with FIFO buffered message exchange. On this basis we define a formal model for components with behaviours that communicate by synchronous and asynchronous message exchange. We close the chapter with guidelines for implementations based on message-oriented middleware using the Java Message Service specification and its reference implementation Open Message Queue. Related formal component models are discussed in Chap. 9.

### 1. Port-Based Components and Behaviours

We consider components to be strongly encapsulated behaviours. Encapsulation is achieved by ports that regulate any interaction of components with their environment. Components can be hierarchically structured containing an assembly of components and connectors that link components using their ports. Interaction consists of synchronous or asynchronous message exchange and we therefore distinguish synchronous and asynchronous connectors. By synchronous communication we understand a rendezvous mechanism where sender and receiver synchronise on message exchange. In contrast, asynchronous communication works with FIFO-buffering where the messages issued by a sender are buffered and can be taken (and processed) later on by the receiver. Sending and receiving

messages with synchronous and asynchronous communication timing are basic primitives of general message-passing systems [**Tuc04**, Sect. 96.3.4].

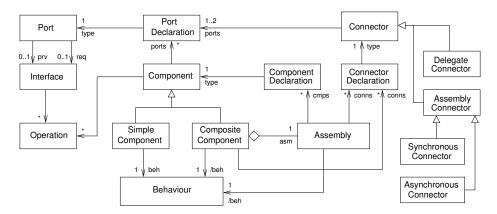

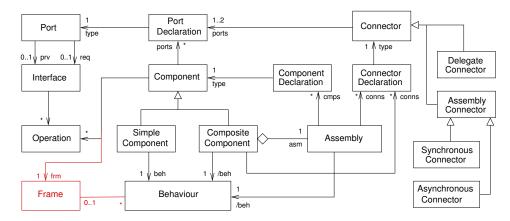

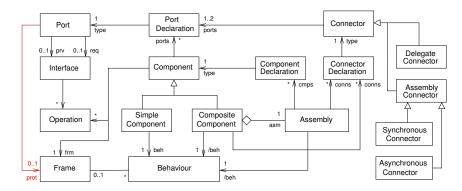

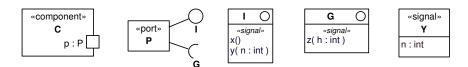

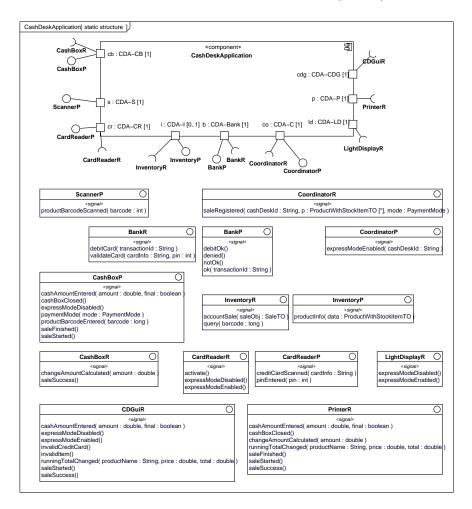

**1.1. Concepts of Port-Based Components.** Figure 2.1 shows the metamodel of our component model. A *port* describes a (partial) view on a component. The operations offered by a port are summarised in its *provided interface*; the operations needed in its *required interface*. An operation declares the signature to be used for message exchange along this port. Ports as well as components and connectors are in fact considered as types that can be used in local declarations of components and assemblies respectively. A *declaration* consists of a name and a type.

FIGURE 2.1. Component metamodel

There are two kinds of components, *simple components* and *composite components* which are abstracted in the metaclass *component*. Any kind of component has a set of *port declarations* that introduce locally unique port names with corresponding port types. Components can be used in component declarations for the construction of assemblies.

An assembly defines the internal structure of a composite component in terms of a set of local component declarations and local connector declarations using binary assembly connectors that link local components using their port declarations. Assembly connectors can be synchronous or asynchronous indicating which kind of communication timing is used for the message exchange along this connector. In a composite component, non-connected (open) ports of local components may be connected to so-called relay ports of the composite component, using declarations of delegate connectors. Unary connectors can be used to close ports of a component that should not be available, neither for connection nor for delegation. This feature is used in Chap. 3 to reduce assemblies with so-called neutral leaf components.

For each simple component a given *behaviour* is supposed to represent the implementation of a component. Behaviours describe the temporal order of receiving messages (input), sending messages (output) and executing local actions (internal). Composite components encapsulate an assembly as an implementation of their behaviour. Therefore, the behaviour of a composite component is a derived behaviour (indicated by the preceding slash symbol in Fig. 2.1). An assembly in turn has an associated derived behaviour that depends on the behaviours of its local components and the types of its assembly connectors.

We use UML2 notation for the concrete specification of the static structure of component-based systems, in particular we make use of UML structured classifiers, components, ports, interfaces and connectors. Since all these entities except interfaces own so-called structural properties, for instance the port declarations of a component is a structural property, it is also allowed to specify multiplicities indicating how many instances of a component or port may exist at runtime [**RJB05**, property]. However, we will use singletons only

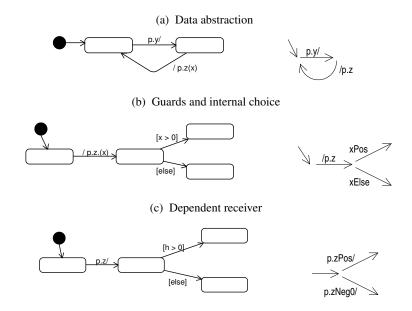

(multiplicity 1) and leave an extension of our formal component model supporting arbitrary multiplicities, especially an extension of the semantics on the level of global behaviours in hierarchically structured component-based systems, to future work. Moreover, we restrict the components of our models to binary communication. UML2 would allow for arbitrary n-ary connectors. However, these kinds of connectors would complicate our formal treatment of behaviours based on I/O-transition systems while being not strictly necessary from the semantical point of view: An n-ary connector is perfectly described by a component whose behaviour reflects the desired connector behaviour. Such a "connector-component" is then linked in between the n components along n binary connectors. Finally, note that we usually do not consider messages with different parameter values for the specification of a component behaviour while operations in interfaces in general may show formal parameters.

The behaviours will be described directly on a semantic level using (finite) I/O-transition systems (IOTSs, see Sect. 2) and represented by graphs with labelled transitions and states. We do not intend to propose a particular, e.g., process algebraic or state machine, syntax for specifying behaviours. In fact, any concrete syntax could be used as long as an interpretation using IOTSs is provided. This interpretation may also provide the construction of messages with different values according to the parameter types of the respective operation. In the graphical representation we indicate that a message m is received (input label, provided) by the visual representation m/ and, symmetrically, that a message m is sent (output label, required) by m. Internal, local actions are represented by transitions labelled without slash. An initial state is indicated by an incoming arrow without source state.

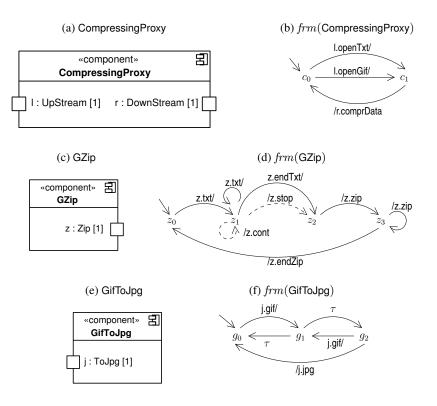

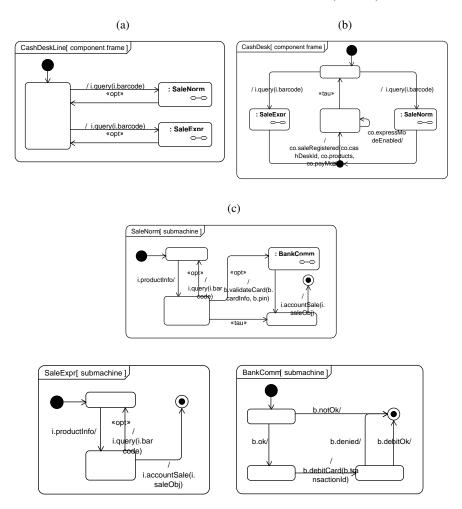

**1.2. Example: Compressing Proxy System.** We illustrate our component model by a compressing proxy system.<sup>1</sup> An HTTP proxy server mediates connections between a web server and its clients. In order to increase network bandwidth, the proxy server may apply different compression techniques depending on the kind of information transferred. The proxy server distinguishes between textual (txt) and graphical (gif) data and applies different compression tools before sending the data further downstream.

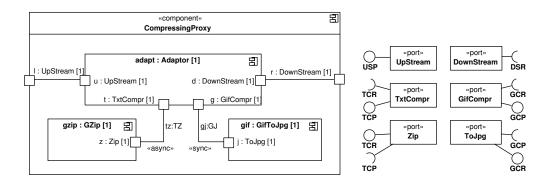

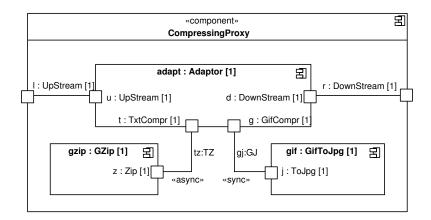

We describe the static structure of the compressing proxy system by a composite component type CompressingProxy that consists of an assembly of three simple components with types Adaptor, GZip, and GifToJpg introduced by the respective component declarations adapt:Adaptor, gzip:GZip, and gifToJpg:GifToJpgas shown in Fig. 2.2. The adaptor receives uncompressed data upstream, delegates the textual data for compression to gzip, which employs the gzip utility, and the graphical data to gifToJpg, a tool to convert GIF- to JPG-images. The compression result will then be sent downstream.

The simple components as well as the composite component show port declarations such as t:TxtCompr or I:UpStream. The port declarations of composite components are called relay ports. Port declarations inside the assembly are connected by synchronous and asynchronous assembly connectors while delegate connectors link port declarations of inner components and relay ports of the composite component. Communication timing is specified by stereotypes «sync» and «async». The connector tz between t:TxtCompr and z:Zip is an asynchronous assembly connector, the connector gj is synchronous, and the anonymous connector between u:UpStream and I:UpStream is a delegate connector.

The provided and required interfaces of the port types of the compressing proxy system are depicted with the UML ball-and-socket notation on the right-hand side of Fig. 2.2.

<sup>&</sup>lt;sup>1</sup>This example is to some extend identical with an example originally used by [IU01] (and also by [BCD02]) to illustrate an approach to prove deadlock-freedom in component assemblies.

FIGURE 2.2. Static structure of a compressing proxy server

If two ports are connected by an assembly connector, it is required that the provided interface of one port is equal to the required interface of the other, and vice versa.<sup>2</sup> The operations of these interfaces are assumed to be given as follows:

```

\begin{aligned} \mathsf{USP} &= \{\mathsf{openTxt}, \mathsf{openGif}\}, & \mathsf{TCR} &= \{\mathsf{txt}, \mathsf{endTxt}\}, & \mathsf{GCR} &= \{\mathsf{gif}\}, \\ \mathsf{DSR} &= \{\mathsf{comprData}\}, & \mathsf{TCP} &= \{\mathsf{stop}, \mathsf{zip}, \mathsf{endZip}\}, & \mathsf{GCP} &= \{\mathsf{jpg}\}. \end{aligned}

```

We do not consider operations with parameters here, thus the operation names coincide with the messages used for communication.

Based on the static structure of the compressing proxy system, the informal description of its intended behaviour reads as follows: A proxy of type CompressingProxy receives stream-based data on its port I that is delegated to the port u of the contained component adapt. The adaptor distinguishes textual and graphical data received at port u and forwards data for textual compression via port t and graphical compression via port g. After receiving the compression result, the component sends the data further downstream using port d which is relayed to port r of the composite component.

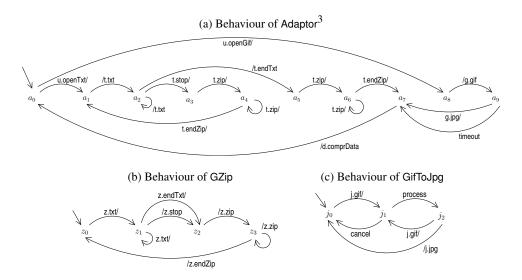

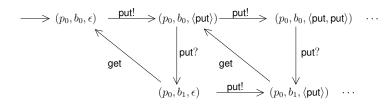

The behaviour of simple components, which are basic building blocks of port-based component systems, are assumed to be given by IOTSs provided by the component implementor respectively designer. Figure 2.3 shows behaviours of the simple components Adaptor, GZip and GifToJpg. Since components communicate only via ports, any label representing a message received or sent has the form p.m where p is a port name and m is a message according to the provided or required interface of the port. Behaviours also show internal actions represented by internal transition labels without prefix. Additionally we allow an anonymous internal action  $\tau$  to reflect a possible internal choice of the component that can or should not be further detailed.

For instance, the behaviour of the component Adaptor shows label for receiving messages u.openTxt, u.openGif, t.zip, t.stop, t.endZip, and g.jpg, and for sending messages d.comprData, t.txt, t.endTxt, and g.gif. The only internal action is timeout. The adaptor component receives requests for either text or gif compression u.openTxt or u.openGif resp. at the upstream port u. After having sent an initial part of textual data t.txt via port t, there is a choice between sending further text until the end of the text is reached (signalled by t.endTxt), or the message t.stop is received, for example indicating a buffer overflow of the component attached for text compression. In the first case, the component waits to receive zip data (t.zip) until transmission end is signalled by t.endZip. In the second case,

<sup>&</sup>lt;sup>2</sup>In general, one could use a more flexible condition so that the required interface of one port is included in the provided interface of the other one. However, it is technically more convenient to use the more restrictive condition from above.

<sup>&</sup>lt;sup>3</sup>The adaptor behaviour corresponds exactly to the adaptor behaviour in [BCD02] if we remove the communication concerning the port g for compression of graphical data.

FIGURE 2.3. Behaviour of simple components

the component retrieves compressed data via t.zip and the communication proceeds until eventually the end of the text will be reached. In both cases a new communication can be started by sending again an initial piece of textual data to be compressed via t.txt. After the text compression is finished, the component sends the compression result comprData further downstream at port d.

Note that the communication between Adaptor and GZip is asynchronous, therefore the behaviours are not blocked until a message sent is received. Instead, the sender may continue immediately, analogously to the execution of local actions. An asynchronous connector is equipped with two FIFO queues, one for each communication direction. For the given protocol this means, e.g., that the adaptor may continue to send text even though the GZip component has sent a stop request in the meantime. This is not an immediate defect, since it is the FIFO buffer which is flooded by txt messages, not the communication partner. If we assume that the adaptor eventually receives the message stop then the communication may proceed indeed as required.

Graphical compression consists only of sending the GIF input further on via g.gif at port g and then to receive the JPG result back again. In case the compression takes too long, an internal timeout transition is triggered and the adaptor sends instead of a JPG the uncompressed data further downstream via d.comprData. The behaviour of the GZip component mirrors the corresponding part of the adaptor. In fact the design process following a bottom-up approach would probably start with the behaviour of the tool component GZip and then mirror this behaviour in the design of the adaptor component. The component GifToJpg shows an internal choice within its behaviour. After having received gif at port j, the component either processes the given GIF or returns without processing to its initial state. In the former case either the JPG result is sent back via j.jpg or another GIF is received at port g which transits back to the given internal choice. In this case a previous result is dismissed and JPGs are delivered only for the latest given GIF.

The behaviours of assemblies and composite components are derived behaviours. Assemblies use component declarations showing a name and a component type. In order to distinguish the different components inside an assembly, the labels of their behaviours are prefixed by the name of the component declaration, thus turning, e.g., u.openGif of the component Adaptor into adapt.u.openGif w.r.t. the declaration adapt:Adaptor. The overall

behaviour of an assembly shows both, the interaction behaviour of the composed components that are connected within the assembly via their ports, and the communication potential at the open ports of components that are not connected within the assembly. Hence, an assembly behaviour is a derived behaviour, given by the composition of the component behaviours of all declared components and connectors of the assembly.