#### A Thesis Submitted for the Degree of PhD at the University of Warwick

#### **Permanent WRAP URL:**

http://wrap.warwick.ac.uk/93459

#### **Copyright and reuse:**

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

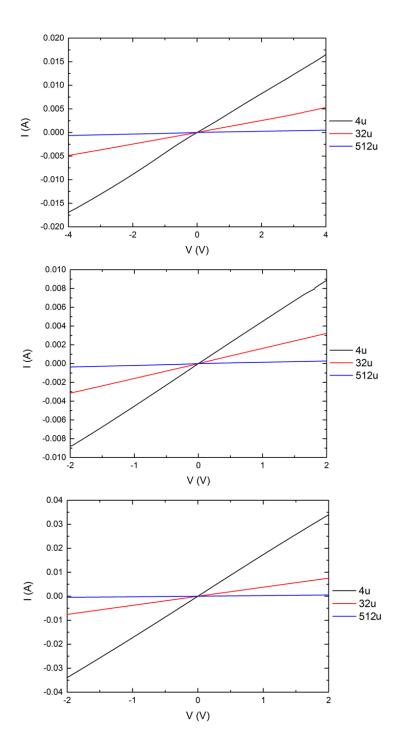

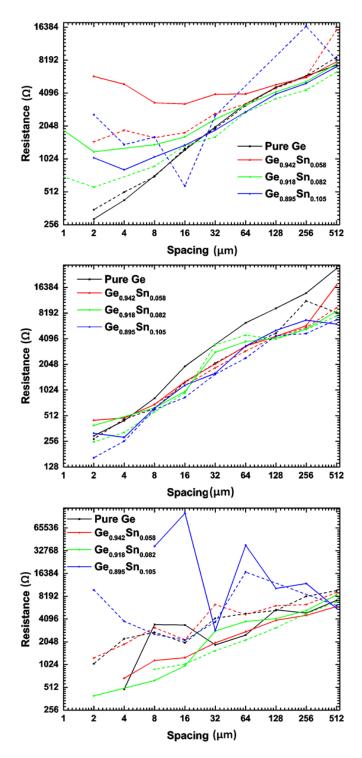

Please refer to the repository record for this item for information to help you to cite it.

Our policy information is available from the repository home page.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

# Germanium-Tin-Silicon Epitaxial Structures Grown on Silicon by Reduced Pressure Chemical Vapour Deposition

by

# David Patchett Thesis

Submitted to the University of Warwick

in partial fulfilment of the requirements

for admission to the degree of

Doctor of Philosophy

Department of Physics

# **Declaration**

This thesis is submitted to the University of Warwick in support of my application for the degree of Doctor of Philosophy. All experimental work presented was carried out by the author, or (where stated) by specialists under the author's direction.

### **Acknowledgments**

I would like to thank my PhD supervisors Dr. Maksym Myronov and Prof. David Leadley for providing me with the opportunity to pursue my passion, provide guidance when it was needed, and the patience to let me learn from my mistakes. Special thanks to Dr. Maksym Myronov for producing the many samples investigated in this work.

Many thanks also to the members of the Nano-Silicon research group past and present including: Jamie Foronda, Phil Allred, Gerard Colston, Oliver Newall, Alan Burton, Ali Julian, Dr. John Halpin, Dr. Steven Rhead and Dr. Vishal Shah. Between you all, you have been friends, mentors and councillors at one time or another.

A huge thank you also to my partner, Ms Hannah Hickman, who has supported me in many ways throughout my studies. You have put up with my many ramblings wearing a smile. I honestly do not know how you managed.

Lastly, thank you to my family. My mother and father Susan and Paul Patchett, who encouraged me from a young age to be curious and showed me support as I pursued those curiosities. And thanks to my siblings Clare, John and Ruth for their continual support and for keeping me grounded.

#### **Abstract**

Crystalline germanium-tin (GeSn) binary alloys have been subject to a significant research effort in recent years. This research effort is motivated by the myriad of potential applications that GeSn alloys offer.

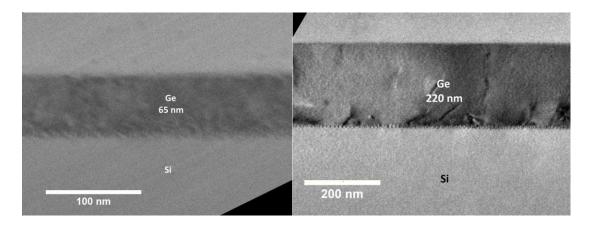

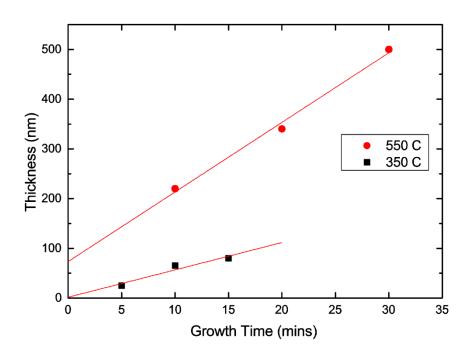

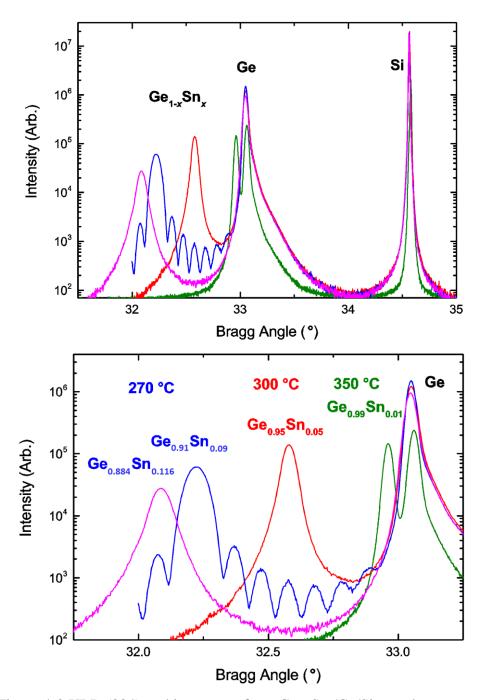

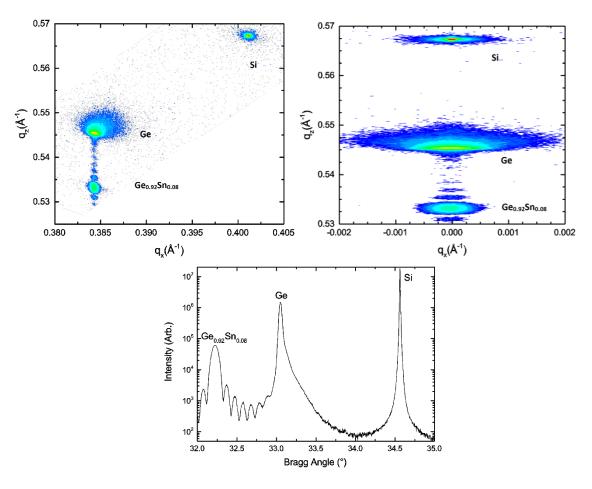

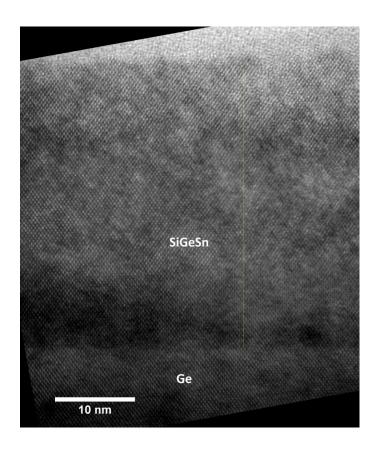

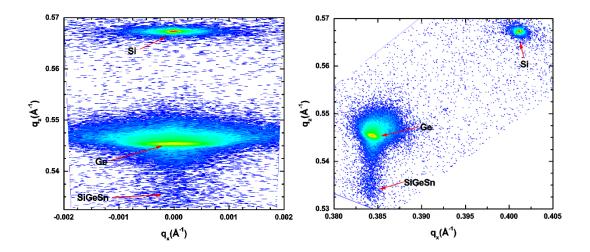

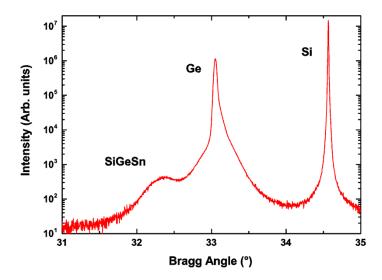

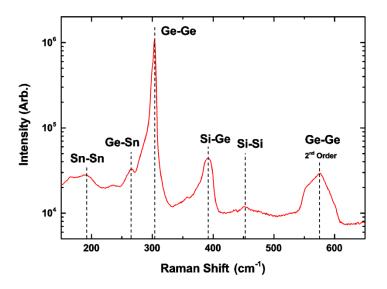

Crystalline epitaxial layers of GeSn and silicon-germanium-tin (SiGeSn) have been grown onto Si(001) substrates on a relaxed Ge buffer using reduced pressure CVD and commercially available precursors. X-ray diffraction, transmission electron microscopy, atomic force microscopy, secondary ion mass spectrometry and Raman spectroscopy were used to determine layer composition, layer thickness, crystallinity, degree of strain relaxation, surface features and roughness of the samples investigated in this work.

The epilayers produced have been both fully strained to their growth platform and partially relaxed. The Sn fraction of the alloy layers varied from 1 to 12 at. % Sn. Using  $N_2$  as the carrier gas during growth is observed to inhibit  $Ge_{1-x}Sn_x$  growth. Offaxis substrates are determined to hinder the production of crystalline layers of GeSn. *In-situ* material characterization of GeSn layers during thermal treatment has identified the existence of a critical temperature for higher Sn fraction layers, beyond which the material quality degrades rapidly. This critical temperature is dependent on the layer composition, layer thickness, layer strain state and annealing environment. Layers of germanium-tin-oxide are produced by thermal oxidation and shown to have similar oxide formation rates to pure Ge.

The low thermal budget limit for the high Sn fraction alloys has driven research into forming Ohmic metal contacts on GeSn layers with processes limited to low temperatures. Gold is determined to be the optimum electrical contact material.

#### **Publications and Presentations**

#### **Journal Publications**

- 1. Rhead, S., Halpin, John E., Shah, V. A., Myronov, Maksym, **Patchett, D. H.**, Allred, Phil, Kachkanov, V., Dolbnya, I. P., Reparaz, J. S., Wilson, Neil R., Sotomayor Torres, C. M. and Leadley, D. R. (2014) *Tensile strain mapping in flat germanium membranes*. Applied Physics Letters, 104, 17

- Fabio Pezzoli, Anna Giorgioni, David Patchett, and Maksym Myronov

"Temperature-dependent photoluminescence characteristics of GeSn epitaxial layers", Submitted

- 3. David Patchett, Stephen Rhead, and Maksym Myronov "Thermal treatments of GeSn Epilayers with *in-situ* and *ex-situ* materials characterization", Thin Solid Films.

- 4. David Patchett, Stephen Rhead, and Maksym Myronov "Thermal oxidation of GeSn Epilayers with high levels of control"

- 5. David Patchett, Gerard Colston, Oliver Newall, and Maksym Myronov "*Insitu* characterization of GeSn epilayers at high temperatures using synchrotron radiation"

- 6. David Patchett, Thomas Walker, Maksym Myronov "Low temperature formation of electrical contacts to GeSn epitaxial layers"

#### **Conference Presentations**

- 1. **D. Patchett**, S.D. Rhead, M. Myronov, and D.R. Leadley "Challenges in Epitaxial Growth by RP-CVD of Strained and Relaxed GeSn Epilayers on a Si Substrate" *International SiGe Technology and Device Meeting (ISTDM 2013)*, Singapore, June, 2013.

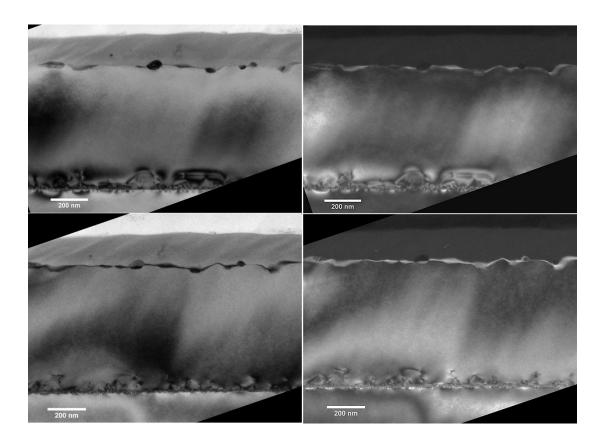

- 2. **D.H. Patchett**, M. Myronov, S.D. Rhead, G. Colston, and D.R. Leadley "Challenges of growth and sample preparation of GeSn for electron

microscopy" *Microscopy of Semiconducting Materials* (MSM 2015), Cambridge, March, 2015

# **Table of Contents**

| User's Declaration Error! Bookmark not defined               |      |  |  |  |

|--------------------------------------------------------------|------|--|--|--|

| Title Page                                                   | i    |  |  |  |

| Declaration                                                  | iii  |  |  |  |

| Acknowledgments                                              | iv   |  |  |  |

| Abstract                                                     | v    |  |  |  |

| Publications and Presentations                               | vi   |  |  |  |

| Table of Contents                                            | viii |  |  |  |

| 1 Introduction                                               | 1    |  |  |  |

| 1.1 Semiconductors in the Wider World                        |      |  |  |  |

| 1.2 Germanium-Tin and Silicon-Germanium-Tin                  | 2    |  |  |  |

| 1.2.1 Applications of (Silicon-)Germanium-Tin                | 3    |  |  |  |

| 1.2.2 Strained Germanium-Tin                                 |      |  |  |  |

| 1.2.3 Relaxed Germanium-Tin                                  |      |  |  |  |

| 1.3 Motivation                                               |      |  |  |  |

| 1.4 Summary                                                  |      |  |  |  |

| 2 Theoretical and Background Discussion                      | 12   |  |  |  |

| 2.1 Basic Material Properties of Binary Germanium-Tin Alloys | 13   |  |  |  |

| 2.1.1 Band Properties                                        |      |  |  |  |

| 2.1.2 Crystal Lattice                                        | 16   |  |  |  |

| 2.1.3 Thermal Stability                                      | 21   |  |  |  |

| 2.1.4 Summary of GeSn                                        | 25   |  |  |  |

| 2.2 Ternary Silicon-Germanium-Tin Alloys                     |      |  |  |  |

| 2.2.1 Band Properties                                        |      |  |  |  |

| 2.2.2 Lattice Parameter                                      |      |  |  |  |

| 2.2.3 Thermal Stability                                      |      |  |  |  |

| 2.2.4 Summary of SiGeSn                                      |      |  |  |  |

| 2.3 Epitaxial growth                                         |      |  |  |  |

| 2.3.1 Thin Film Growth                                       |      |  |  |  |

| 2.3.2 Molecular Beam Epitaxy                                 |      |  |  |  |

| 2.3.3 Chemical Vapour Deposition                             |      |  |  |  |

| 2.3.4 Novel Growth Methods                                   |      |  |  |  |

| 2.3.5 Relaxation and Critical Thickness                      |      |  |  |  |

| 3 Experimental Techniques                                    | 49   |  |  |  |

| 3.1 Introduction to Experimental Techniques                  | 49   |  |  |  |

| 3.2 Chemical Vapour Deposition                               | 51   |  |  |  |

| 3.3 Atomic Force Microscopy                                  | 54   |  |  |  |

| 3.3  | 3.1 AFM Image Analysis          | 56                         |

|------|---------------------------------|----------------------------|

| 3.3  | 3.2 Measurement Attributes      | 57                         |

| 3.4  | Secondary Ion Mass Spectrometr  | y57                        |

| 3.4  | 4.1 Measurement Attributes      | 60                         |

| 3.5  | X-ray diffraction               | 60                         |

| 3.5  | 5.1 Theory                      | 61                         |

| 3.5  | 5.2 Lab Based X-ray Sources     | 62                         |

| 3.5  | 5.3 The Reciprocal Lattice      | 64                         |

| 3.5  | 5.4 Structure Factors           | 64                         |

| 3.5  | 5.5 Rocking Curves and Recipro  | ocal Space Maps65          |

| 3.5  |                                 | 67                         |

| 3.5  | 5.7 Measurement Attributes      | 68                         |

| 3.6  | Synchrotron Based X-ray Diffrac | etion69                    |

| 3.6  | •                               | erature Control70          |

| 3.6  |                                 | 72                         |

| 3.7  | Transmission Electron Microsco  | oy73                       |

| 3.7  | -                               | 74                         |

| 3.7  |                                 | 77                         |

| 3.7  |                                 | 78                         |

| 3.7  | C C                             | ndition79                  |

| 3.7  | 5 5                             | 79                         |

| 3.8  |                                 | 80                         |

| 3.8  |                                 | pectroscopy83              |

| 3.8  |                                 | 84                         |

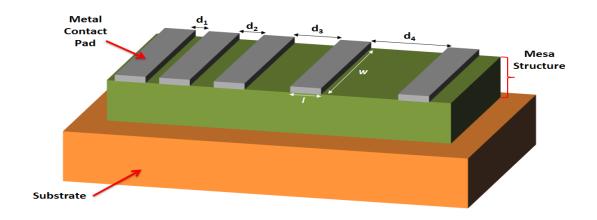

| 3.9  |                                 | 1 Lines85                  |

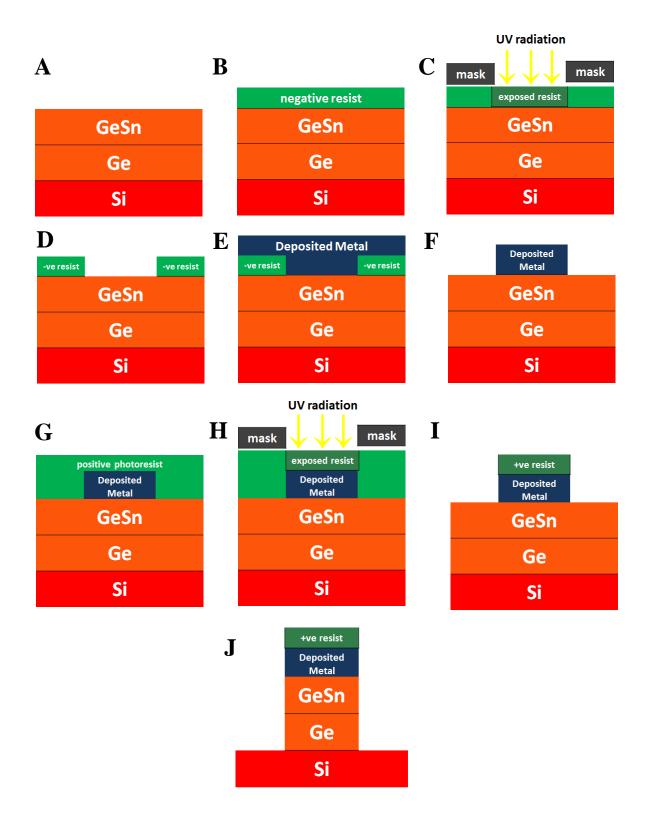

| 3.9  |                                 | prication86                |

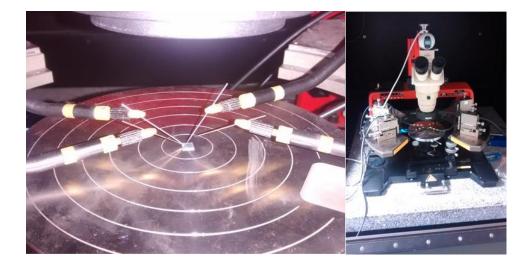

| 3.10 |                                 | 90                         |

| 3.11 |                                 | 92                         |

| 4 G  | •                               | vth and Characterization93 |

| , 00 |                                 |                            |

| 4.1  |                                 | 93                         |

| 4.2  |                                 | Sn/Ge/Si structures94      |

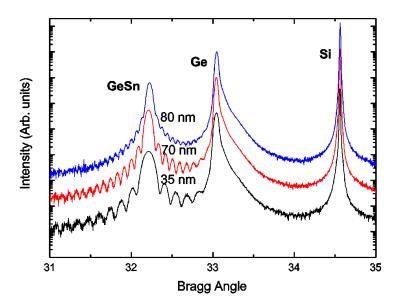

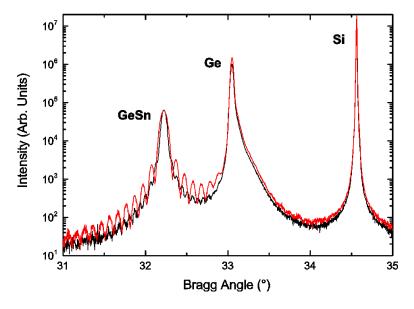

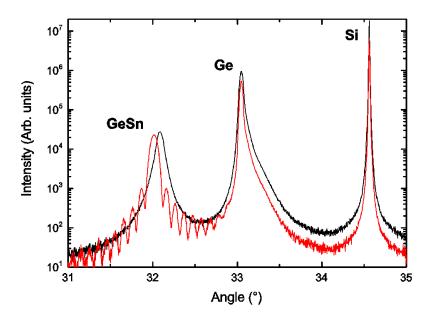

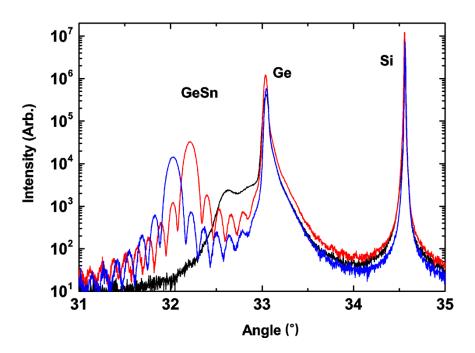

| 4.2  |                                 | e/Si by XRD94              |

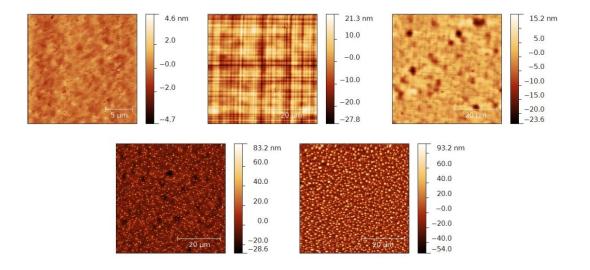

| 4.2  | 2.2 Surface Characterisation    | 98                         |

| 4.3  | Calibration of Ge Grown at Low  | Temperature99              |

| 4.4  | Influence of Temperature on Ges | Sn Growth102               |

| 4.5  | Carrier Gas                     | 107                        |

| 4.6  | •                               | 110                        |

| 4.7  |                                 | 115                        |

| 4.8  |                                 | 119                        |

| 4.8  |                                 |                            |

| 4.8  |                                 |                            |

| 4.8  | 3.3 Summary of Off-Axis GeSn    | Growth                     |

| 4.9  |                                 |                            |

| 5 TV | hermal Stability of GeSn Epilo  | yers127                    |

|      | -                               |                            |

| 5.1  |                                 |                            |

| 5.2  | <u> </u>                        | dies                       |

| 5.2  |                                 | ion130                     |

| 5 7  |                                 |                            |

|      |                                 |                            |

| 5.2.4 Relaxation                             | 141                               |

|----------------------------------------------|-----------------------------------|

| 5.2.5 Thermal Treatment Surface Change       | es142                             |

| 5.2.6 Alloy Composition, Epilayer Thic       | ckness and Strain State Effect on |

| Critical Temperature                         | 146                               |

| 5.3 Thermal stability study at a Synchrotron |                                   |

| 5.3.1 Motivation                             |                                   |

| 5.3.2 Experimental Details                   |                                   |

| 5.3.3 Critical Temperature                   |                                   |

| 5.4 Oxidation                                |                                   |

| 5.5 Summary                                  | 161                               |

| 6 Electrical Contact Formation               | 163                               |

| 6.1 Interpreting Results                     | 163                               |

| 6.2 Contact Metals                           |                                   |

| 6.3 Annealing Metal Contacts                 |                                   |

| 6.3.1 Contacts on intermediate Sn fraction   | n layers169                       |

| 6.3.2 Contacts on high Sn fraction layers    | 170                               |

| 6.4 Sn fraction                              | 172                               |

| 6.5 Strain Relaxation                        | 174                               |

| 6.6 Conclusions                              | 176                               |

| 7 Conclusions and further work               | 178                               |

| 7.1 Conclusions                              | 178                               |

| 7.2 Further work                             | 179                               |

| 7.2.1 Increasing Sn Fraction                 | 179                               |

| 7.2.2 Strained and Relaxed GeSn Layers.      | 180                               |

| 7.2.3 Thermal Stability of GeSn              | 181                               |

|                                              | 182                               |

| 7.2.5 SiGeSn                                 | 182                               |

| 8 References                                 |                                   |

#### 1 Introduction

#### 1.1 Semiconductors in the Wider World

Semiconductor technology is fundamental in the modern world, and its role is likely to only increase over time. A pivotal point for the widespread usage of semiconductors came with the invention of the first (widely recognised) transistor at Bell labs, which led to the awarding of the 1956 Nobel Prize in physics to William Shockley, John Bardeen and Walter Brattain "for their researches on semiconductors and their discovery of the transistor effect". However, it should be noted that previous work on transistors had been undertaken by Lilienfeld and later Heil. The first transistor at Bell Labs was made using crystalline germanium, and it's function was reliant on what was at the time the only recently developed quantum theory.

However, due to its high bulk cost, germanium was not to be the dominant material used in semiconductor devices. Silicon became the material of choice largely due to being more widely available, the excellent quality and non-water-soluble nature of the native oxide and significantly more economical semiconductor material for the expanding semiconductor industry.

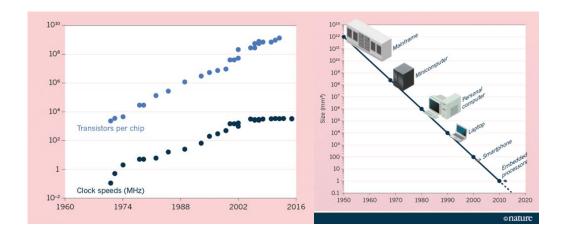

Since its conception in 1965 and subsequent revision in 1975 "Moore's Law" has been both a predictor and driving force for advancement in the semiconductor microprocessor industry. Moore's law has several variations, but commonly interpreted as "the number of transistors on an integrated circuit will double approximately every two years", see Figure 1-1 which is adapted from a *Nature* news article [1]. This is possible due to the continuing reduction in the scale of individual transistors which allows the transistor density of computer chips to be increased,

which in turn increases the available processing power. However, Moore's law is not a physical law, and the scaling methodology is approaching its limits in pure silicon; as the dimensions of individual transistors approach the atomic scale, detrimental behaviour occurs such as transistor source-drain current leakage and device heating. Even if these issues are overcome, the single atom transistor is a hard limit for bulk materials, as using fractions of atoms for transistors is not a viable option.

To continue to improve the capabilities of available microprocessors and other semiconductor based technologies it is necessary to utilize the properties of more novel materials beyond pure silicon. In past decades this work has been investigated with great vigour, including III-V semiconducting alloys, epitaxial and bulk germanium and silicon-germanium ( $Si_{\nu}Ge_{1-\nu}$ ) alloys.

Figure 1-1 The historical trend of Moore's law, showing the number of transistors on a chip increasing in a logarithmic trend, agreeing with the doubling of transitors approximately every two years since the midsixties/early seventies.

#### 1.2 Germanium-Tin and Silicon-Germanium-Tin

The germanium-tin  $(Ge_{1-x}Sn_x)$  binary alloy was first proposed by Soref as a potential material composed solely of group IV constituent elements which would possess a direct bandgap [2,3]. It is an alloy of the diamond cubic lattice  $\alpha$ -phase Sn and Ge, which also has a diamond-like cubic lattice [4].

Increasing the Sn fraction produces  $Ge_{1-x}Sn_x$  alloys with a larger lattice parameter and narrower bandgap than that of pure Ge, thus expanding the available parameter space of group IV alloys, such as lattice parameter, bandgap, thermal expansion coefficient, dielectric constant, charge carrier mobility, etc [5].

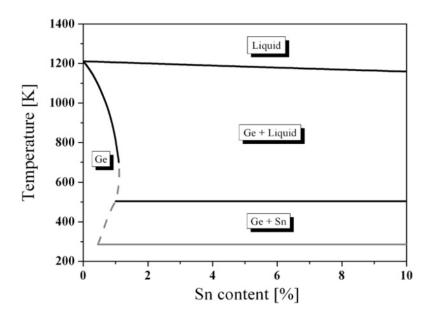

The significant obstacle to the development and implementation of  $Ge_{1-x}Sn_x$  alloys is its metastability; under equilibrium conditions the maximum Sn fraction is ~1 at. % Sn in Ge-rich alloys, whereas incorporating any Ge into the Sn matrix to form a single phase Sn-rich alloys is also extremely challenging [6].

The binary  $Ge_{1-x}Sn_x$  alloy has a single degree of freedom of composition, thus a particular alloy composition has a unique relaxed lattice parameter and a unique fundamental bandgap, and knowledge of one parameter can be used to infer the others. The ternary silicon-germanium-tin  $(Si_yGe_{1-x-y}Sn_x)$  alloy, however offers two degrees of freedom in composition space which allows lattice parameter and bandgap to be independently altered. For a single lattice parameter, the bandgap can be altered by ~0.2 eV, by tuning the composition [7].

The incorporation of silicon into the  $Ge_{1-x}Sn_x$  matrix increases the alloy bandgap and increases the  $\Gamma$ -L conduction band separation, making the bandgap of such alloys further from a direct bandgap nature. The incorporation of silicon also increases the thermal stability of the alloy, which is desirable for many device applications [8].

#### 1.2.1 Applications of (Silicon-)Germanium-Tin

The extension of parameter space of group IV semiconductors provided by binary  $Ge_{1-x}Sn_x$  alloys and ternary  $Si_yGe_{1-x-y}Sn_x$  alloys facilitates increasing the existing range of device applications for group IV semiconductors in addition to potential enhancements to existing applications.

By increasing the upper limit on lattice parameter from group IV materials,  $Ge_{1-x}Sn_x$  epitaxial layers can use to improve upon existing structures. The larger lattice parameter of  $Ge_{1-x}Sn_x$  means it can be grown lattice matched to a range of III-V alloy semiconductors, reducing the defect density in active layers of hybrid devices [9,10] and thus improving their performance. The high crystal quality, including low density of threading defects, high crystal order and sufficiently low surface roughness, makes  $Ge_{1-x}Sn_x$  alloy epitaxial layers a suitable platform for subsequent growth of crystalline epitaxial layers [5,11–15]. Indeed studies have shown  $Ge_{1-x}Sn_x$  layers are better able to absorb significant amounts of lattice stress than stiffer Si-rich alloys by forming lattice dislocations, this is supported by theoretical predictions which indicate  $Ge_{1-x}Sn_x$  alloys have a particularly high plasticity compared to other group IV semiconducting alloys [9,16].

By using  $Ge_{1-x}Sn_x$  layers as a platform for further epitaxial growth  $Ge_{1-x}Sn_x$  can act as a stressor for thin Ge layers grown epitaxially on top of the alloy [17,18]. Inducing biaxial tensile strain in Ge has multiple benefits – the hole mobility increases, the bandgap shifts towards a more direct nature due to relative lowering of the  $\Gamma$  minima compared to the L minima, for these reasons tensile strain is used to improve the performance of Ge FETs [17,19].

The  $Ge_{1-x}Sn_x$  alloys have either a direct bandgap or a smaller difference between their indirect and direct bandgap energy (L- $\Gamma$  energy separation) compared to other group IV semiconducting materials, which makes epilayers favourable for applications such as photodetectors, avalanche photodiodes and emitters [20,21]. These structures can be grown on a silicon platform, enabling  $Ge_{1-x}Sn_x$  growth processes developed to be more readily reproducible with current industry setups and keeping production costs low.

The narrowing of the bandgap and increased photonic efficiency of  $Ge_{1-x}Sn_x$  layers compared to Ge and Si, particularly at longer wavelengths, makes the alloy a potential candidate for fabricating photodetectors and photoemittors well into IR region, extending the existing work done with inducing tensile strain in Ge layers for this purpose [22]. Of particular interest are  $Ge_{1-x}Sn_x$  alloys with a bandgap suitable for photon emission and detection wavelength of approximately  $1.5 \, \mu m$ , approximately  $0.8 \, eV$ , which is in the centre of the range currently used in long distance telecommunications. This wavelength is used because  $1.55 \, \mu m$  gives the best signal transmission in the IR range in optical fibres [23–25], although there is also potential applications for  $Ge_{1-x}Sn_x$  based optical devices operating at even longer wavelengths [26].

Many of the proposed devices using the ternary  $Si_yGe_{1-x-y}Sn_x$  alloy utilize the decoupling between lattice parameter and bandgap. By having such a large range of lattice parameters,  $Si_yGe_{1-x-y}Sn_x$  layers can be grown lattice-matched to a large range of materials, theoretically spanning the full range from Si (5.43102 Å) to  $\alpha$ -Sn (6.493 Å) if a wide range of compositions are attainable.  $Si_yGe_{1-x-y}Sn_x$  has proposed applications as an active layer in multi-junction photovoltaics, with the layer covering a photon energy range which is not sufficiently covered by existing materials, also reducing abrupt lattice mismatch between Ge and III-V layers [27,28]. This would increase the possible collection efficiency of the device. The  $Si_yGe_{1-x-y}Sn_x$  alloy also has applications in FETs as a stressor, with the composition being tuned to produce layers with a desired lattice parameter which can be larger or smaller than bulk Ge [29].

#### 1.2.2 Strained Germanium-Tin

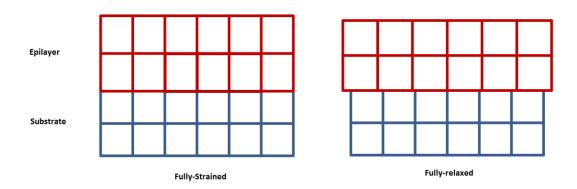

Very thin epitaxial  $Ge_{1-x}Sn_x$  layers will be strained to their growth platform. Typical growth platforms are Si or Ge, and due to the smaller lattice parameter these substrates the  $Ge_{1-x}Sn_x$  epilayer are typically compressively strained in-plane.

Lattice strain alters multiple material properties of all crystalline semiconductors,  $Ge_{1-x}Sn_x$  included. Strain, either biaxial or uniaxial, also lifts the symmetry of the x, y and z axis found in bulk cubic materials, thus strain leads to the splitting of conduction and valence bands which can mean that charge carriers of the same type possess different properties, for example producing non-degenerate heavy hole and light hole bands [30,31].

In a compressively strained  $Ge_{1-x}Sn_x$  alloy epilayer, the in-plane lattice parameter matches that of the smaller lattice growth platform, while the  $Ge_{1-x}Sn_x$  out-of-plane lattice parameter expands as the unit cell volume acts to try to maintain the relaxed lattice cell volume following Poisson's rule.

For  $Ge_{1-x}Sn_x$  epitaxial layers, compressive strain raises both the  $\Gamma$  and L conduction band minima – increasing the fundamental bandgap. The direct  $\Gamma$  band increases to a greater extent with compressive strain than the indirect L band, thus increasing the  $\Gamma$ -L conduction band separation and therefore producing a material further from a direct bandgap [32].

#### 1.2.3 Relaxed Germanium-Tin

Lattice stain relaxation of  $Ge_{1-x}Sn_x$  epilayers is important for achieving an indirect-to-direct bandgap transition and narrowing the fundamental bandgap, which is desirable for devices functioning in the IR region [33].

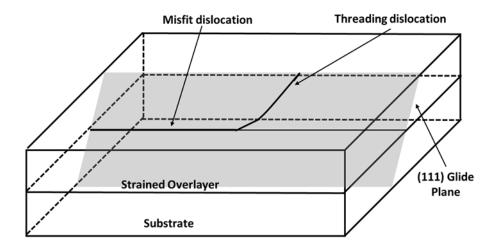

However, for heteroepitaxial structures this strain relaxation can only be achieved by the formation of strain-relieving lattice dislocations. In  $Ge_{1-x}Sn_x$  heterostructures, these strain-relieving dislocations are typically Lomer edge dislocations, rather than threading dislocations which are typical in silicon-germanium heterostructures [7,9]. For many devices, the tendency to form edge dislocations is preferable to threading dislocations as the lattice defect does not propagate upwards through the layer material; which degrades the material and thus can degrade the electrical, mechanical, and optical properties. The tendency to form edge dislocations in  $Ge_{1-x}Sn_x$  epitaxial layers therefore enhances the potential of this material to be used for devices and as a superior platform for subsequent growth.

Lattice strain relaxation initiates when the thickness of the layer being grown increases above the threshold critical thickness. This critical thickness depends on the degree of lattice mismatch between the layer and the substrate (i.e. alloy composition and growth platform), the growth temperature and thermal expansion mismatch between the epilayer and substrate (which alters the lattice mismatch upon cooling post-growth). Ultimately, as the initially strained layer thickness increases, strain energy accumulates in the epilayer until the threshold is reached whereupon the formation of misfit dislocations in the lattice release the strain energy with further increases in layer thickness increasing the degree of relaxation until the layer has adopted its bulk state.

#### 1.3 Motivation

The growth of  $Ge_{1-x}Sn_x$  alloy epitaxial layers by CVD, the growth method used in this work, is a novel process and successful growth has been reliably achieved in only a limited number of chemical vapour deposition (CVD) reactors. Upon the

initial demonstration of Ge<sub>1-x</sub>Sn<sub>x</sub> CVD growth in 2002 [34], a single research group dominated research for the first decade, with a publication demonstrating CVD growth using an alternative growth method by a separate research group not being produced until 2011 [35]. The current range of CVD growth methodologies have significant differences, including precursor sources utilized, CVD chamber working pressure and CVD geometry, all of which affect the growth parameters necessary to reproduce growth results. Due to the limited scope of research, the details of growth conditions on produced alloy properties are yet to be fully explored.

Pseudomorphic, or fully strained,  $Ge_{1-x}Sn_x$  layers are an important research area, covering epilayers without any lattice relaxation and therefore in this work are compressively strained in-plane to be lattice matched to the underlying strain relaxed Ge-buffer lattice. Compared to their lattice relaxed counterparts, fully strained  $Ge_{1-x}Sn_x$  epilayers exhibit fewer lattice defects, as many defects are generated during lattice relaxation in the form of misfit dislocations.

The lower concentration of lattice defects in strained layer structures makes them favourable for many optical devices, as defects act as centres for non-radiative charge carrier recombination, inhibiting photonic device efficiency. Lattice strain modifies the bandstructure of the material, influencing charge carrier mobility [36]. Sufficiently strained layers may also exhibit significant band splitting, where the inand out-of-plane lattice parameter differ producing two distinct conduction bands and two distinct valence bands, charge carriers within the split bands have different properties such as effective mass and mobility [37,38]. Strain induced bandstructure modifications can be utilized to enhance devices performance, for example increasing mobility in FETs [39].

Strain relaxed  $Ge_{1-x}Sn_x$  layers are also an important area of research. In this work,  $Ge_{1-x}Sn_x$  epilayer compressive strain relaxation increases the in-plane and reduces the out-of-plane lattice parameter, shifting towards a bulk cubic lattice. This is desirable for applications of  $Ge_{1-x}Sn_x$  as a platform for subsequent lattice matched growth of III-V semiconductors, with lattice parameters larger than Ge, such as AlAs and InP.  $Ge_{1-x}Sn_x$  layer relaxation from compressive strain also modifies the bandstructure, narrowing the bandgap and reducing the L- $\Gamma$  separation [40], of great use in many applications such as IR photodevices and explored in detail previously.

Off-axis Si substrates are being researched as a potential method to integrate III-V semiconductor alloys onto group IV platforms and reduce the formation of anti-phase domains of the III-V epilayer [41,42]. As  $Ge_{1-x}Sn_x$  epilayers are being investigated as potential platform for III-V materials, particularly low defect density layers for photonic devices.

Altering the carrier gas used during CVD growth was investigated with the aim of increasing the  $Ge_{1-x}Sn_x$  growth rate. While many  $Ge_{1-x}Sn_x$  growth investigations have used the  $H_2$  carrier gas, growth of pure Ge at low temperatures has shown that switching to the  $N_2$  carrier gas increases the growth rate. However, whether this will be seen in  $Ge_{1-x}Sn_x$  growth is uncertain due to the different reaction chemistry [43]. The ternary  $Si_yGe_{1-x-y}Sn_x$  alloy is also investigated, as discussed in section 7.2.5.3 the decoupled bandgap and lattice parameter makes it suitable for strain and bandstructure engineering in heretostructures.

## 1.4 Summary

Semiconducting alloys of group IV elements which incorporate tin have many fascinating properties, with the expansion of available parameter space offering the

exciting potential to enlarge and enhance the capabilities of existing semiconductor devices; however, our understanding and ability to produce these alloys is not yet well established.

Many challenges remain to be overcome in order to achieve reliable growth of semiconducting crystalline group IV alloys incorporating Sn. Prior to the widespread use of  $Ge_{1-x}Sn_x$  and  $Si_yGe_{1-x-y}Sn_x$  alloy epitaxy, it will be necessary to develop methods which supress alloy segregation during growth. These include growth at low temperatures with novel gas precursors that have still to be developed and fully-characterized. Methods to minimise the negative consequences of low growth rates at these reduced growth temperatures will also need to be developed.  $Ge_{1-x}Sn_x$  alloys grown in this way will be metastable, which also limits post-growth thermal treatments and the subsequent growth of additional layers to low temperatures, to prevent loss of crystallinity of the  $Ge_{1-x}Sn_x$  layer. The details of these thermal limits require further investigation.

Material characterization of the ternary  $Si_yGe_{1-x-y}Sn_x$  alloys is more complicated than the established methods to characterize binary  $Si_yGe_{1-y}$  alloys and  $Ge_{1-x}Sn_x$  alloys. The ternary alloy composition cannot be determined solely from x-ray diffraction, as is common for binary alloys. Thus alternative characterization methods are required to determine the composition, but parameter extraction can be more difficult in these less-standard methods, the equipment is less prevalent, and there are fewer established results with which newly acquired results could use for comparison.

This work details the investigation of the effect on material properties due to changes in several growth parameters. The material properties of strained and relaxed  $Ge_{1-x}Sn_x$  epilayers will be explored. The response of  $Ge_{1-x}Sn_x$  epilayers to thermal treatments is examined, to determine the existence and nature of any material

degradation, epilayer relaxation and oxidation and their relation to the Pre-thermal treatment materials properties. Finally, the formation of Ohmic contacts while minimising the damage to the  $Ge_{1-x}Sn_x$  alloy epilayer will also be investigated.

## 2 Theoretical and Background Discussion

In this chapter the background knowledge regarding semiconducting crystalline germanium-tin alloys and silicon-germanium-tin-alloys relevant to this work is discussed including: the alloys' constituent elements (Si, Ge and Sn); the formation of crystalline epitaxial layers of alloys, with a focus on the binary  $Ge_{1-x}Sn_x$  alloy; and the material properties of the elements and alloys and their inter-relation are explored, identifying the interdependence between alloy composition, lattice parameter, lattice relaxation, bandstructure and thermal stability.

As previously mentioned bulk silicon, germanium and alpha-tin all have a facecentred cubic lattice, commonly referred to as diamond cubic.

Regarding Si<sub>y</sub>Ge<sub>1-y</sub> alloys, Si and Ge are completely miscible and any composition of this binary alloy can be produced at fairly high growth temperatures [44]. Despite the fairly large mismatch between the lattice parameter bulk Si and Ge lattice parameter of approximately 4.2%, any composition can be grown under equilibrium conditions and is thermally stable.

However, Ge and  $\alpha$ -Sn are not fully miscible. At almost the opposite extreme a very limited compositional range of  $Ge_{1-x}Sn_x$  alloys can be grown under equilibrium conditions and there exists a significant lattice mismatch of approximately 14% between the bulk lattices of Ge and  $\alpha$ -Sn.

# 2.1 Basic Material Properties of Binary Germanium-Tin Alloys

Germanium-Tin (GeSn) alloys expand the potential range of properties achievable with group IV materials, expanding available parameter space with narrower bandgap, larger lattice parameter with a tuneable thermal expansion coefficient.

The expansion in material properties makes  $Ge_{1-x}Sn_x$  alloy based devices superior to the current range of group IV alloys  $-Ge_{1-x}Sn_x$  can be used to tensile strain Ge which improves carrier mobility and shifts the bandgap to a more direct nature.  $Ge_{1-x}Sn_x$  layers have many potential applications in photonics devices - including applications in photovoltaics, photodectectors, and light emitting diodes [7,24,27,45,46]. The narrowing of the bandgap with increasing Sn fraction pushes  $Ge_{1-x}Sn_x$  photon absorption region well into the  $1.5 \, \mu m$  range, which is used in telecommunications, with the potential for operating at even longer wavelengths [47,48].

The majority of  $Ge_{1-x}Sn_x$  epilayers grown by CVD using the SnCl<sub>4</sub> precursor utilize Ge-buffered Si substrates in order to minimise the lattice mismatch. Growth directly onto a Si substrate leads to massive lattice mismatch, this mismatch is reduced though not eliminated, by growing onto a relaxed Ge layer. However, Ge substrates are prohibitively expensive, therefore it is more economic to use a Ge buffer on Si substrates, which reduces the lattice mismatch with  $Ge_{1-x}Sn_x$  with a low dislocation density at the growth surface, minimising the buffer/epilayer interface roughness and ensure epilayer quality is maintained.

#### 2.1.1 Band Properties

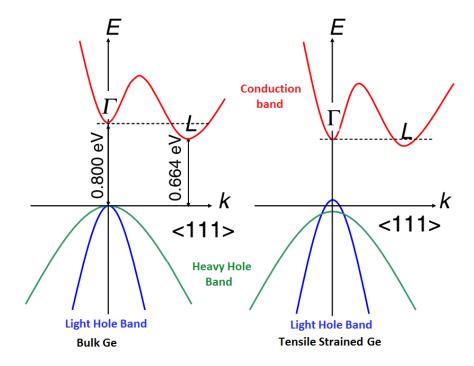

Si and Ge are indirect bandgap semiconductors, the lowest energy part of the band are the L-minima, as such carrier excitation by photon absorption requires interacting with a lattice phonon, which is an inefficient process and so requires thick layers for significant absorption. However, it has been recognised for some time that the energy separation between the Ge L-minima (indirect L band gap 664 meV [32]) and Ge  $\Gamma$ -minimum (direct gap of 800 meV) is very slight, with recent investigations indicating it is as narrow as 136 meV and therefore only relatively slight bandstructure modifications are necessary to close this gap [49]. A schematic diagram of the bandstructure of pure Ge in a relaxed and tensile strained state, which is indicative of the and the potential bandstructure of a  $Ge_{1-x}Sn_x$  alloy, is shown in Figure 2-1, figure adapted from [32].

The novel aspect of  $Ge_{1-x}Sn_x$  alloys is the effect of incorporating tin, specifically the cubic lattice phase called alpha-tin (grey tin). In isolation pure  $\alpha$ -Sn has metallic

Figure 2-1 Schematic diagrams of the bandstructure of (left) pure relaxed Ge, with the indirect, L, gap being smaller than the direct,  $\Gamma$ , gap. (right) The bandstructure of tensile strained Ge, where the direct  $\Gamma$  gap has been reduced relative to relaxed Ge and the L- $\Gamma$  separation has been reduced. A similar change in bandstructure is seen with the incorporation of Sn into Ge. For sufficient Sn incorporation the effect bandgap becomes direct in nature.

electrical properties. However, when regarding  $Ge_{1-x}Sn_x$  alloys  $\alpha$ -Sn is referred to as a semiconductor with a negative direct bandgap of -0.4 eV [50]. This is because it is the  $\alpha$ -Sn direct  $\Gamma$  band which dictates the influence of Sn incorporation into Ge, and therefore the aspect of the bandstructure of  $\alpha$ -Sn which must be considered when predicting the material properties in Ge-rich  $Ge_{1-x}Sn_x$  alloys.

For some years it has been predicted that for a sufficiently high Sn fraction in the  $Ge_{1-x}Sn_x$  alloy the  $\Gamma$ -minima will be at the same energy as the L-minima and thus the alloy will transition from an indirect-to-direct bandgap. The exact composition at which this transition is predicted to occur has changed with recent research. A simple linear interpolation would indicate a crossover at  $x \approx 0.20$ , with other compositions also predicted based on a range of theoretical models combined with experimental results from grown materials giving a large range of crossover compositions with x = 0.06, 0.065, 0.08, 0.105 [33,51–55].

However,  $Ge_{1-x}Sn_x$  layers are typically grown on either Si or Ge and even thick layers retain some residual compressive lattice strain which in effect has the opposite impact on the alloy bandgap as greater Sn incorporation, increasing the magnitude of the  $\Gamma$  and L bandgaps and increasing their separation. Therefore to achieve a transition to direct bandgap material it is necessary to either grow an alloy which is compressively strained with a very high Sn fraction or induce compressive strain relaxation in a lower Sn fraction  $Ge_{1-x}Sn_x$  layer. The effect of Sn fraction on the bandgaps of  $Ge_{1-x}Sn_x$  alloys is non-linear for both strained and relaxed layers [15,51].

#### 2.1.2 Crystal Lattice

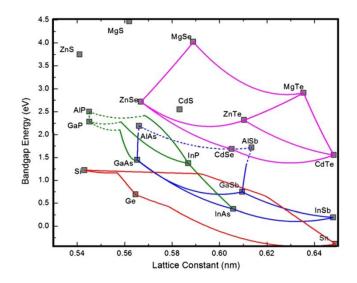

Figure 2-2 The range of lattice parameters and bandgaps of Si, Ge and alpha-Sn and for comparison those of many III-V semiconductor alloys. This highlights the board range of materials Si-Ge-Sn alloys can potentially be lattice matched to in order to produce low defect density heterostructures. This image is adapted from G. Sun, *et al.*, [143]

Of the materials studied in this work, Si has smallest lattice parameter at 5.43102 Å, the next smallest is Ge at 5.6579 Å, and  $\alpha$ -Sn has by far the largest lattice parameter at 6.493 Å. Historically, it was challenging to determine the lattice parameter of  $\alpha$ -Sn due to the difficulties with obtaining crystalline samples of sufficient size to obtain meaningful x-ray diffraction data. Additionally, after producing large enough sample for X-ray data the sample must be stored below room temperature in order to prevent the material transitioning to beta phase Sn.

The range of lattice parameters which can be attained with alloys of these three components is huge, with  $Ge_{1-x}Sn_x$  alloys covering the greatest range. In combination these materials have the ability to lattice match with many III-V alloys, as illustrated in Figure 2-2, which would significantly aid the production of high quality hybrid structures with lattice matching to reduce defect densities. For the full scope of this

potential to be utilized, it is necessary to be able to produce a wide range of  $Ge_{1-x}Sn_x$  alloy compositions.

As previously detailed, creating high Sn fraction  $Ge_{1-x}Sn_x$  alloys is challenging due to the low,  $\leq 1$  at. %, equilibrium solid solubility of Sn in crystalline Ge. The propensity for alloy segregation is in large part due to the aforementioned huge lattice mismatch between  $\alpha$ -Sn and Ge, in addition to the large difference in atomic radius of Sn from 15-16% [56,57].

In unstrained, i.e. bulk, cubic crystal lattice structures the lattice parameters in all 3 crystal directions are equal, i.e.  $a_0 = b_0 = c_0$ , additionally the base crystal lattice vectors equal and orthogonal, hence  $\alpha = \beta = \gamma = 90^{\circ}$ . This significantly simplifies conceptualising crystal lattice modifications.

For many binary alloys the lattice parameter of the alloy of a specific composition can to the first approximation be regarded as a linear relation between the bulk lattice parameter for the two component elements, weighted by the proportional composition of the alloy. This is a 'pure' or 'unmodified' Vegard's law, as given in equation 2-1.

$$a_{ij} = x \cdot a_i + (1 - x) \cdot a_i \tag{2-1}$$

Where ' $a_{ij}$ ' is the lattice parameter of the alloy, ' $a_i$ ' and ' $a_j$ ' are bulk lattice parameters of elements 'i' and 'j' respectively and 'x' is the fraction of element 'i' in the alloy. Real crystals are not represented by a perfectly linear relation. There is typically a non-linear component to the relation between lattice parameter and alloy composition, the general form of this is given in equation 2-2.

$$a_{ij} = x \cdot a_i + (1 - x) \cdot a_i + b_{ij} \cdot x \cdot (1 - x)$$

(2-2)

Where ' $b_{ij}$ ' is degree of the non-linear behaviour of the lattice parameter, the alloy bowing parameter. In crystal physics this relation referred to as Vegard's law. For  $Si_yGe_{1-y}$  alloys and other semiconductor alloys the bowing parameter is negative,  $b_{SiGe} = -0.02733$  [58]. However for  $Ge_{1-x}Sn_x$  alloys the bowing parameter is positive,  $b_{GeSn} = 0.041$  Å, [59], with the full Vegard's law for  $Ge_{1-x}Sn_x$  given in equation 2-3.

$$a_{GeSn} = x \cdot a_{\alpha - Sn} + (1 - x) \cdot a_{Ge} + 0.041 \cdot x \cdot (1 - x)$$

(2-3)

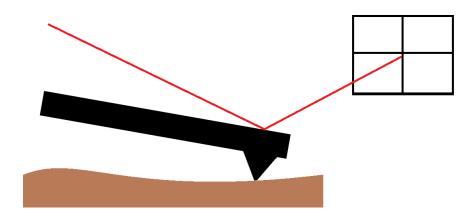

The bowing parameter of  $Ge_{1-x}Sn_x$  required experimental determination. For this X-ray diffraction (XRD) data is used to determine the lattice parameter of a sample, and combined with an independent measurement of the composition of the same sample and the results compared. This process is repeated for many samples with a range of alloy compositions to determine the bowing parameter. Secondary ion mass spectroscopy (SIMS), Rutherford back scattering (RBS) and Energy dispersive X-ray spectroscopy (EDS) measurements provide composition information, but each characterization method has its own source of measurement error. These methods must therefore be used with some caution, so it is common to use multiple methods to determine the composition, such that the results from each method can be compared very reliable verification.

Different publications report a range of  $Ge_{1-x}Sn_x$  alloy bowing parameters, with initial values ranging from 0.00882 Å to 0.65 Å, but after a series of systematic studies it is generally being accepted as  $b_{GeSn} = 0.041$  Å [12,55,59–61]. The majority of research is in agreement that the sign of the  $Ge_{1-x}Sn_x$  bowing parameter is positive, which is opposite of that found in the  $Si_yGe_{1-y}$  and  $Si_{1-z}C_z$  systems, indeed all other group IV semiconductor alloy systems have small negative bowing parameters

[58,62]. This difference is attributed to the comparatively huge difference in Ge and  $\alpha$ -Sn atomic radii and lattice parameters.

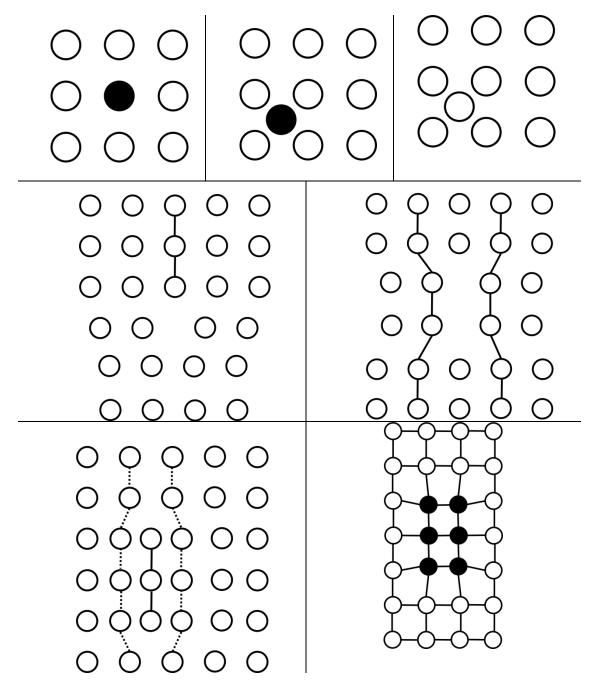

Figure 2-3 Schematic diagrams of several crystal defects in 2D with a square lattice. Unfilled circles represent bulk crystal atoms, filled circles represent impurity atoms. Lines denoting bonds are shown to illustrate interruptions in crystalline order. Defect types shown: (Top left) A substitutional impurity atom. (Top centre) An interstitial impurity atom. (Top right) An interstitial bulk atom – where the atom comprises a significant proportion of the bulk. (Middle left) An edge dislocation, with a partial plane of atoms inserted into the crystal from the edge of the crystal. (Middle right) A vacancy dislocation. (Lower left) Interstitial dislocation. (Lower right) Impurity precipitation

Fully-strained  $Ge_{1-x}Sn_x$  layers have been reported that are thicker than would be thought possible without undergoing some strain relaxation [59]. The out-of-equilibrium, i.e. low temperature, nature of  $Ge_{1-x}Sn_x$  growth is believed to supresses the formation of misfit dislocations, and consequently the experimental critical thickness for relaxation is larger than expected for group IV semiconductor alloys grown at higher temperatures [58,59]. This suppression of the formation of strain-relieving misfit dislocations may contribute to the challenge of reaching high degrees of lattice strain relaxation by growing very thick  $Ge_{1-x}Sn_x$  layers.

Figure 2-4 Schematic of the formation of a threading dislocation from a misfit dislocation generated at the interface between two mismatched layers of a heterostructure.

The misfit dislocations that are predominantly observed appear to be Lomar edge dislocations, which are confined to the  $Ge_{1-x}Sn_x/Ge$  interface and do not propagate upwards through the  $Ge_{1-x}Sn_x$  epilayer [5,7].

The deformation of the crystal lattice in response to lattice strain is determined in part by the material's elastic constants. The values of which are given for Si, Ge and  $\alpha$ -Sn in Table 1, note the  $\alpha$ -Sn Poisson ratio is comparable to that of Ge.

Figure 2-3contains schematic diagrams of a range of crystal defects. Point defects include impurity atoms in substitutional and interstitial sites, and atoms of the

element(s) which compose the bulk crystal which are in interstitial lattice sites. Line defects, or dislocations, are generated when a partial plane of atoms is present in or absent from the crystal, disrupting the local symmetry and causing localised strain. A volume defect of particular interest to this work is a precipitate of impurity atoms with a crystal structure different to the bulk crystal, which is also shown schematically.

Misfit dislocations form between lattice mismatched layers when the lattice strain energy exceeds a threshold and crystal defects are formed in order to relieve this strain energy. Misfit dislocations can lead to the formation of a threading dislocation, a line defect which propagates in both the in plane and out of plane directions as shown schematically in Figure 2-4. An additional mechanism for misfit dislocations is to form a Lomar edge dislocation, a line defect which is constrained to the interface between the mismatched crystal layer as it has no out of plane component, a detailed exploration can be found in ref [63].

#### 2.1.3 Thermal Stability

The diamond-like cubic alpha-Sn phase is only stable up to a temperature of 13 °C; at higher temperatures the tin crystal structure will change phase to  $\beta$ -Sn, which has a non-cubic lattice and a metallic nature. However, the epitaxially grown  $\alpha$ -Sn onto low lattice mismatched substrates increased the temperature limit to ~70 °C [64]. The melting temperature of Sn is relatively low, 505 K, compared to those of Ge and Si shown in Table 1. The Sn bulk melting temperature is close to the typical  $Ge_{1-x}Sn_x$  CVD growth temperature which is typically 520 K and above. This may be expected to have implications for the interdiffusion of Sn atoms between the  $Ge_{1-x}Sn_x$  epilayer and the Ge buffer, with the Sn atoms being mobile relative to the Ge atoms and

readily diffusing across the  $Ge_{1-x}Sn_x/Ge$  interface, leading to a less abrupt interface. However, this is not reported in the literature, where even high Sn fraction  $Ge_{1-x}Sn_x$  layers grown on a Ge buffer have been demonstrated which do not exhibit interdiffusion when annealed at 300 °C [65].

The maximum equilibrium solid solubility Sn fraction is ~1 at. %, the alloy phase diagram is shown in Figure 2-5, with two distinct phases being thermodynamically favourable at higher Sn fractions. Thus, growth of single phase alloys with a higher Sn fraction requires out-of-equilibrium conditions; with the need for conditions to be increasing far from equilibrium as the target Sn fraction increases.

Due to the equilibrium state being phase separation, once grown single crystalline epitaxial layers of  $Ge_{1-x}Sn_x$  alloys are metastable; any post-growth treatments at sufficiently high temperatures will induce alloy segregation into Sn-rich and Ge-rich regions and is no longer monocrystalline. The thermal stability of alloy layers is dependent on multiple factors, including the Sn fraction [66,67].

Thermal treatments are used for annealing epilayers to improve crystal quality [30]. As grown material will typically have atoms not just in substitutional sites, but there will also be atoms in interstitial sites and the crystal will have vacancies where a lattice atom should be located. Treatment of the sample at high temperatures provides the thermal energy necessary for atoms to move, allowing interstitial defects and vacancies to move and annihilate, thus improving the crystal quality. The increased thermal energy can also allow small crystal imperfections to re-orientate to the match the rest of the crystal. Thermal cycling has been used to reduce the density of threading dislocations in Ge epilayers [68]. These processes improve the crystal quality, but excessive thermal treatments can cause alloy segregation [69].

In addition to improving material quality, thermal treatments are also necessary for Ohmic contact formation; the increased thermal energy facilitates atoms from the metal contact to diffuse into the  $Ge_{1-x}Sn_x$  epilayer, forming a high quality contact. Again this must be done without significantly degrading the crystal quality of the whole layer [70].

The coefficient of thermal expansion is an important material parameter as it contributes to lattice strain after growth, for example it causes the over relaxation of Ge buffers grown on Si substrates. This effect of different expansion coefficient of heteroepitaxial layers has been used to induce strain in Si-Ge epilayers with multiple thermal cycles [32]. The  $\alpha$ -Sn linear thermal expansion coefficient, given in Table 1, is intermediate between Ge and Si, but how the coefficient changes with alloy composition has yet to be investigated.

Metastable high Sn fraction crystalline  $Ge_{1-x}Sn_x$  alloys heated to high temperatures

Figure 2-5 The phase diagram of Ge-rich  $Ge_{1-x}Sn_x$  alloys. Note the maximum Sn fraction that can be incorporated into the Ge matrix is ~1 at. %. At the opposite range, essentially no Ge fraction can be incorporated into the Sn matrix. Image obtained from Kasper *et al.* [6].

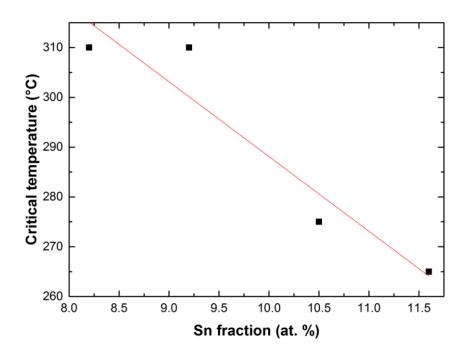

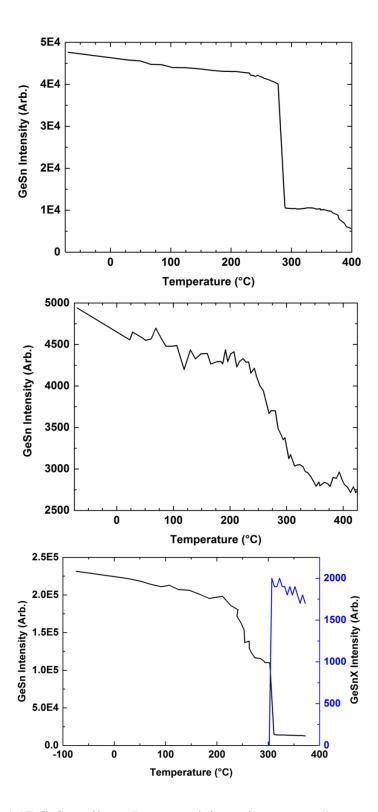

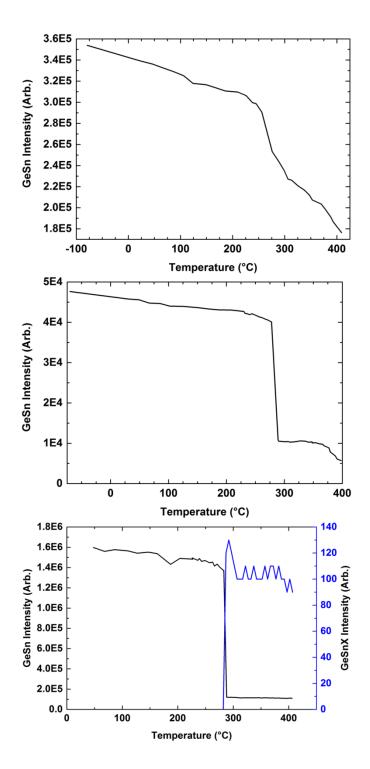

exhibit Sn segregation, with Sn features appearing on the sample surface. As the Sn fraction of the alloy increases the temperature at which this segregation takes place decreases, as the original alloy is further from equilibrium [19]. It has been suggested that there exists a critical temperature, where a  $Ge_{1-x}Sn_x$  alloy layer is relatively stable below this temperature but the crystallinity severely degraded with Sn segregation above this temperature [69]. Understanding the nature of the  $Ge_{1-x}Sn_x$  response to thermal treatments, whether the critical temperature does exist and if so what material parameters influence it, is vital for optimal material processing without causing critical damage to the crystal quality. However, a sufficient level of understanding has yet to be reached. Currently, the critical temperature has only been suggested, but not confirmed, and additionally there are conflicting published results of whether strain relaxation can be achieved with thermal treatments before the onset of material degradation [67].

The melting temperatures of Si, Ge and  $\alpha$ -Sn are given in Table 1. All temperatures used for  $Ge_{1-x}Sn_x$  alloy growth and thermal treatments are significantly below the melting points of Si and Ge, thus it can be safely assumed that the Ge buffer and Si substrate layers will be stable. The melting temperature for Sn is above the temperature at which Sn undergoes a phase change to  $\beta$ -Sn. As mentioned previously, the Sn melting temperature is close to that of typical growth temperatures and below the thermal treatment temperatures used in this work. It is anticipated therefore that the response of  $Ge_{1-x}Sn_x$  alloys to high temperatures will vary from the response of silicon-germanium materials.

|                                                                       | Silicon (Si)                     | Germanium<br>(Ge)                | Alpha-Tin<br>(α-Sn)             |

|-----------------------------------------------------------------------|----------------------------------|----------------------------------|---------------------------------|

| Lattice<br>parameter (Å)<br>[5]                                       | 5.431                            | 5.658                            | 6.493                           |

| Elastic<br>constants (GPa)<br>[5]                                     |                                  |                                  |                                 |

| C <sub>11</sub>                                                       | 165.8                            | 128.8                            | 66                              |

| $C_{12}$                                                              | 63.9                             | 48.3                             | 34                              |

| C <sub>44</sub>                                                       | 79.6                             | 66.8                             | 29                              |

| Poisson Ratio ((100) Orientation)[59]                                 | 0.28                             | 0.26                             | 0.263                           |

| Melting point<br>(K)[71]                                              | 1687                             | 1211                             | 505                             |

| Linear thermal<br>expansion<br>coefficient (K <sup>-1</sup> )<br>[71] | 2.92×10 <sup>-6</sup><br>(293 K) | 5.90×10 <sup>-6</sup><br>(293 K) | 4.7×10 <sup>-6</sup><br>(293 K) |

| Atomic<br>Covalent<br>Radius (pm)<br>[71]                             | 117                              | 122                              | 140                             |

| Energy band<br>gap (eV) [71]                                          | 1.1242<br>(at 300 K)             | 0.664<br>(at 291 K)              | -0.4                            |

Table 1- Several of the material properties of bulk Si, Ge and  $\alpha$ -Sn

#### 2.1.4 Summary of GeSn

Crystalline  $Ge_{1-x}Sn_x$  epitaxial layers expand the existing parameter space of group IV materials; with larger lattice parameters and narrower bandgaps becoming attainable. Additionally there is the potential for an indirect-to-direct bandgap transition in  $Ge_{1-x}Sn_x$  for higher efficiency photonic devices than found in existing group IV materials.

Several of the significant initial challenges of epitaxial growth incorporating Sn into other group IV materials have begun to be overcome by the research to date.  $Ge_{1-x}Sn_x$

alloys have routinely been grown with Sn fractions far exceeding the low equilibrium Sn solid solubility in Ge. Recently, direct bandgap  $Ge_{1-x}Sn_x$  has been demonstrated experimentally with a high Sn fraction epilayer, with significant but not complete degree of strain relaxation by the growth of a very thick  $Ge_{1-x}Sn_x$  epilayer [72].

## 2.2 Ternary Silicon-Germanium-Tin Alloys

Similar to the binary germanium-tin alloy, the ternary silicon-germanium-tin (Si<sub>v</sub>Ge<sub>1-x-v</sub>Sn<sub>x</sub>) alloy is composed solely of group IV elements. Attempts have even been made towards producing the quaternary SiGeSnC alloy, but making progress is challenging [73]. An appropriate comparison of a ternary group IV alloy is with quaternary alloys in III-V semiconductor systems. Bulk binary III-V semiconductors, such as GaAs, have fixed bandgaps and composition, similar to elemental group IV semiconductors, such as Si and Ge. As the proportion of two elements of a ternary III-V semiconductor alloy can be altered in a coupled way, either the two group III or group V constituent elements must sum to constitute half of the total atoms in alloy, such as varying the indium and gallium content in In<sub>x</sub>Ga<sub>1-x</sub>As [74]. Altering the composition of a ternary III-V alloy alters the bandgap and lattice parameter in a coupled way, providing a single degree of freedom, analogous to binary group IV alloys, such as Si<sub>v</sub>Ge<sub>1-v</sub>. Finally quaternary III-V alloys, for example In<sub>x</sub>Ga<sub>1-x</sub>As<sub>1-v</sub>P<sub>v</sub>, have two degrees of freedom; allowing lattice parameter and bandgap to be independently altered [75]; though still confined by the properties of the constituent elements. Ternary alloy group IV semiconductors, such as Si<sub>v</sub>Ge<sub>1-x-v</sub>Sn<sub>x</sub>, have two degrees of freedom in composition, and lattice parameter and bandgap can be altered in an uncoupled way, though again to a limited degree, which is comparable to quaternary III-V semiconductors [29,76,77]. The two degrees of freedom of the alloy

composition decouples lattice parameter and bandgap, such that alloys with the same lattice parameter can have different bandgaps.

The use of a ternary  $Si_yGe_{1-x-y}Sn_x$  alloys makes available a wider range of lattice parameters, bandgaps, and degree of directness of the effective bandgap [78]. These properties make this alloy very promising for lattice matching to layers of many other materials. The material parameters can be varied by changing composition and lattice strain.  $Si_yGe_{1-x-y}Sn_x$  is also more thermally stable that binary  $Ge_{1-x}Sn_x$ , with the incorporation of Si atoms acting to stabilize the alloy, which may facilitate more device processing methods [8].

It should be noted that the properties and growth of  $Si_yGe_{1-x-y}Sn_x$  are regarded as the incorporation of Si into  $Ge_{1-x}Sn_x$  and not the incorporation of Si into  $Si_yGe_{1-y}$ . Consequently, the growth of  $Si_yGe_{1-x-y}Sn_x$  requires the low growth temperatures used in  $Ge_{1-x}Sn_x$  alloy growth.

#### 2.2.1 Band Properties

The incorporation of Si into  $Ge_{1-x}Sn_x$  makes the formation of a direct bandgap increasingly difficult, as increasing the Si content increases both the L and  $\Gamma$  bandgaps, with the  $\Gamma$  bandgap increasing more rapidly with Si fraction than the L gap; reducing the degree of directness of the bandgap [78]. At the extreme case of a binary  $Si_{1-x}Sn_x$  alloy, theoretical predictions suggest that a direct bandgap is not possible [79].

#### 2.2.2 Lattice Parameter

The decoupling of the  $Si_yGe_{1-x-y}Sn_x$  lattice parameter and bandgap means that for a given lattice parameter the bandgap can be altered by  $\sim 0.2$  eV by tuning the

composition [7]. The lattice parameter range covers that of several III-V alloys alloying for high quality integration, as shown in Figure 2-2.

The decoupling of alloy composition and lattice parameter means that it is not possible to determine a unique composition using many common characterization methods, such as XRD. Determining composition therefore requires using the more complex methods such as RBS, which is less prevalent than XRD, or composition from SIMS which is both less prevalent than XRD and which requires high surface quality and the precision of SIMS measurements diminishing with increased probing depth.

The incorporation of Si into the  $Ge_{1-x}Sn_x$  matrix reduces the lattice parameter of the alloy. It is therefore possible to produce a SiGeSn alloy lattice matched to pure Ge, with an Si-to-Sn ratio of ~4 : 1. The ability to lattice-match to pure Ge means that strain relaxed  $Si_{4x}Ge_{1-5x}Sn_x$  can be grown onto pure Ge without the formation of strain reliving lattice dislocations [76,77,80].

## 2.2.3 Thermal Stability

Increasing the Si alloy fraction at a constant Sn fraction increases the thermal stability [8,77]. The increase in stability is attributed to the Si atoms partially counteracting the mismatch effects of the Sn when incorporated into a Ge-rich matrix. The increased thermal stability is important for applications where it is desirable for the layer to have a high thermal budget; for example if subsequently grown epitaxial layers would require a high growth temperature, if there are device processing steps which require high temperatures, or if the desired device will be exposed to high temperatures.

#### 2.2.4 Summary of SiGeSn

Widespread research of  $Si_yGe_{1-x-y}Sn_x$  is challenging due to the difficulties involved in both the material growth and the subsequent materials characterization. The effect of decoupling lattice parameter, composition and bandgap by incorporating both Si and Sn into the Ge matrix is both a large advantage for potential device applications of the alloy and a challenge to its development. Determining a unique composition is not possible solely with XRD measurements, which is the standard method for much of group IV semiconductor development.

As the incorporation of Si atoms in several ways counteracts the effect of incorporating Sn atoms into Ge, many of the potential advantages of the binary  $Ge_{1-x}Sn_x$  alloy, such as a narrower bandgap with a greater degree of directness, are more challenging to achieve with the ternary alloy. Thus, the major characteristics of epitaxial layers of  $Si_yGe_{1-x-y}Sn_x$  alloys that are exploitable for applications are lattice matching and band engineering which take advantage of the decoupling of bandgap and lattice parameter. However, a large range of potential devices are possible with direct bandgap or almost-direct bandgap  $Si_yGe_{1-x-y}Sn_x$  alloy based devices [78].

## 2.3 Epitaxial growth

Epitaxy is the process of growth of a single-crystal film on a crystalline substrate, where the film adopts the crystalline structure and orientation of the substrate. Homoepitaxy is the case where the film composition and substrate composition are essentially identical, such as a silicon epilayer grown on a silicon substrate. In homoepitaxy, the film may have a variable doping profile or may be of a higher crystal quality than the growth substrate.

Heteroepitaxy is the case where the crystal film has a different composition than the substrate, for example a germanium epilayer grown on a silicon substrate. A different substrate to the epilayer may be used for application functionality reasons – the substrate may have useful properties for the intended application of the structure, but also the substrate may be chosen for economic reasons. Many structures are grown on silicon with the major motivation being that high quality silicon substrates are cheap and relatively easy to acquire with a reasonable mechanical strength and moderate thermally conductivity.

Heteroepitaxy can lead to lattice strain, the formation of lattice defects, the modification of the electrical properties of epitaxial layers compared to their bulk state, and modifications to the different layers thermal properties. The different layers may have sufficiently different chemical properties to allow for preferential chemical etching [81].

#### 2.3.1 Thin Film Growth

The aim of semiconductor thin film growth is to produce high quality, single crystal thin semiconductor films. It is desirable to be capable of growing layers with thickness in the range of a several nanometers to few microns, for all layer thicknesses the film must be evenly spread over entire growth substrate – which can be up to 450 mm in diameter.

The ideal growth produces a structure which is essentially identical across the growth substrate. This requires complete film coverage, with constant thickness and composition of the film across the substrate. Ideally, the growth target should have as low a defect density, with the minimum lattice dislocations. The (multi)layers should be monocrystalline, with a very smooth surface. These material properties are

optimal for quality semiconductor devices, and are desirable for measurement accuracy for several characterization methods.

## 2.3.1.1 Growth Morphologies

There are three potential growth morphologies in thin film growth.

Firstly, there is ideal two dimensional film growth (Frank—van der Merwe). In this growth morphology adatom-substrate interactions dominate over adatom-adatom interactions, leading to perfect 2D film growth. Each atomic layer of the crystal is completed before any growth of subsequent layers is initiated. This growth morphology leads to the formation of pristine monocrystalline layers, with a very smooth surface. This is therefore the ideal growth morphology for thin film growth. Secondly, there is three dimensional island growth (Volmer—Weber). In this growth morphology adatom-adatom interactions dominate and are stronger than adatom-substrate interactions. This leads to the growth of multiple separate crystalline areas on the growth substrate, which merge as growth progresses and in some circumstances form a polycrystalline layer with multiple crystal grain boundaries and defects. This growth morphology can produce a comparatively rough surface. This is therefore an undesirable growth mechanism.

Finally, there is a combination of the previously mentioned two dimensional film growth and three dimensional island growth (Stranski-Krastanov). In this growth morphology, the initial crystal growth is the perfect 2D layer Frank-van der Merwe growth morphology; however, after several crystal layers have been grown imperfections begin to form as distinct clusters and 3D islands form in Volmer-Weber type mechanism.

#### 2.3.2 Molecular Beam Epitaxy

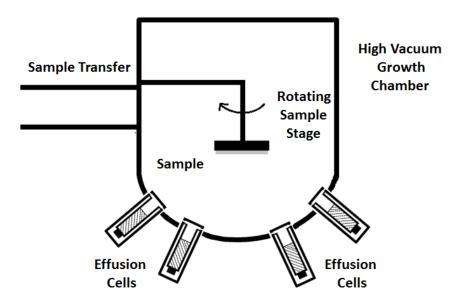

Molecular beam epitaxy (MBE) is a widely used method for growing crystalline thin film epitaxial layers, the technique was first developed at Bell Labs in 1975 producing this layers of III-V alloys [82]. In MBE, the growth substrate is placed in a vacuum chamber and molecular beams of the desired elements are directed at the substrate surface to produce the target structure with high levels of control on layer thickness and composition. A schematic diagram of a MBE growth chamber is given in Figure 2-6.

For the MBE growth of  $Ge_{1-x}Sn_x$  layers it necessary to grow at low temperatures, typically ranging from 50 °C to 250 °C, to prevent Sn segregation due to metastable nature of high Sn fraction  $Ge_{1-x}Sn_x$  alloys [17,60,83,84].

MBE was the first growth method to produce crystalline  $Ge_{1-x}Sn_x$  epilayers, and

Figure 2-6 A schematic diagram of the molecular beam epitaxy growth chamber. A vacuum chamber is used for growth, in order to minimise contamination. The growth substrate is loaded onto a stage, which can be rotated during growth for improved layer homogenaity. Molecular beam elemental sources are provided by effuision cells directed at the growth substrate.

growth on non-standard substrates, which is useful for lattice matching the substrate to higher Sn fraction alloys, has also been demonstrated [85,86].

MBE has been used to produce epitaxial layers of high Sn fraction crystalline alloys, with Sn fractions significantly greater than the equilibrium limit of  $Ge_{1-x}Sn_x$  alloys [60,66,84]. The crystal quality of recent MBE grown  $Ge_{1-x}Sn_x$  layers has been sufficiently good to produce devices [19,45,46]. This is matched with additional capacity to introduce dopants in-situ now becoming well developed [19,87].

However, the production volume cannot be effectively scaled, as MBE is a relatively low throughput method, with large run times needed to produce individual wafers. It is therefore necessary to transition to an alternative growth method if production is to be scaled to significant volumes required for the production of consumer devices.

## 2.3.3 Chemical Vapour Deposition

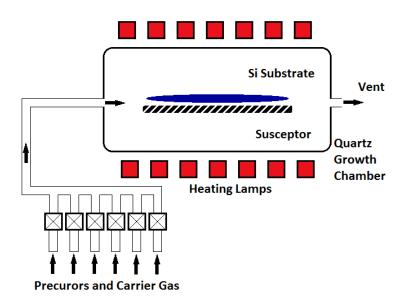

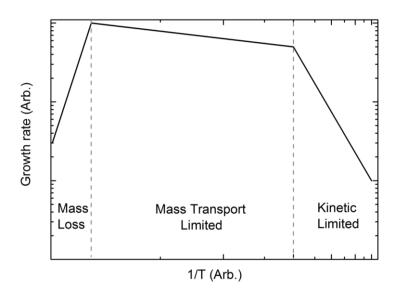

As its name suggests, chemical vapour deposition (CVD) is a method of epitaxial crystal growth by chemical processes. CVD is the growth method used to produce the samples which are investigated in this work. Chemical reactions between gas phase precursors are used to produce epitaxial layers on a variety of growth substrates. In this section I will discuss the progress, challenges and methodology of crystalline  $Ge_{1-x}Sn_x$  alloy growth by CVD.

# 2.3.3.1 Progress of Chemical Vapour Deposition growth of Germanium-Tin Epilayers

Growth of crystalline  $Ge_{1-x}Sn_x$  epitaxial layers by CVD was first demonstrated in 2002, utilizing Ultra-High-Vacuum CVD (UHV-CVD) configuration at Arizona state university [34]. In order to produce single crystal  $Ge_{1-x}Sn_x$ , several Sn precursor

gases were trailled. SnH<sub>4</sub> was recognised as too unstable, and attempts at growth using SnD<sub>3</sub>CH<sub>3</sub> proved unsuccessful [14]. Growth was finally achieved with tindeuteride, SnD<sub>4</sub>, which can be stabilised by storing in gas canisters and diluting with H<sub>2</sub> gas. Digermane, Ge<sub>2</sub>H<sub>6</sub>, gas was used as the Ge source. In this work growth temperatures from 250 – 350 °C were used, above what is typical for MBE growth of  $Ge_{1-x}Sn_x$  but significantly below what is found in Si or Ge CVD growth.  $Ge_{1-x}Sn_x$ layers were produced with Sn fractions from 13-17 at. % were produced using the lower temperature range from 250 to 290 °C, with the lower Sn fraction alloys, from 2 to 12 at. % Sn, being produced at the higher range of growth temperatures from 300 to 350 °C. The Ge<sub>1-x</sub>Sn<sub>x</sub> epilayers in this work were fully strained relaxed and grown directly onto Si(001) substrates, with thicknesses in the range from 50 to 500 nm. The crystallinity of the low Sn fraction alloy layers was very good, with Rutherford backscattering spectroscopy (RBS) channelling yields of  $\chi_{min} = 4\%$  for a Ge<sub>0.98</sub>Sn<sub>0.02</sub> layer, where min is the ratio between the ratio of peak heights when aligned to a lattice planed and when at a random angle for RBS spectra, which is comparable to high quality epitaxial Ge. However, the crystallinity dropped to for higher Sn fraction alloys, with  $\chi_{min} = 35\%$  for the  $Ge_{0.88}Sn_{0.12}$  layer, this high value is indicative of significant degradation of the crystallinity attributed to mosaic spread within the layer reducing the determined crystallinity. A higher  $\chi_{min}$  value indicates a greater proportion of atoms in the material under investigation are not positioned at lattice sites, hence a lower crystallinity.

In 2003 the same group expanded this work producing alloys with Sn fractions up to 20 at. % Sn, but again a low fraction of substitutional Sn was found for higher Sn fraction alloys ( $\chi_{min} = 50\%$  for  $Ge_{0.86}Sn_{0.14}$  layer), indicating that crystallinity is becoming a serious issue at high Sn fractions. Work was initiated to construct a

modified Vegard's law for the fundamental bandgap of crystalline  $Ge_{1-x}Sn_x$ , by comparing x-ray diffraction data and RBS data to ellipsometry data from samples with a range of  $Ge_{1-x}Sn_x$  alloy compositions, and examining the effect of Sn incorporation on the materials' bandstructure [14,88]. In the same year research was published on the successful growth of crystalline layers of the ternary  $Si_yGe_{1-x-y}Sn_x$  alloy using the same UHV-CVD growth method, with the  $SiH_3GeH_3$  precursor being used as the Si source. These ternary alloy layers were grown onto  $Ge_{1-x}Sn_x$  alloy (x = 0.03-0.04) buffers. The  $Si_yGe_{1-x-y}Sn_x$  epilayer and  $Ge_{1-x}Sn_x$  buffer were both grown at 350 °C. Two layers with different compositions,  $Si_{0.14}Ge_{0.84}Sn_{0.02}$  and  $Si_{0.14}Ge_{0.80}Sn_{0.06}$  as determined by RBS, were produced by varying the Sn precursor concentration at a constant growth temperature [89].

The Arizona university group was the sole institution producing crystalline  $Ge_{1-x}Sn_x$  layers using the CVD growth for some time - to a large extent the reluctance of other institutions to reproduce the growth method was due to the difficulty and high expense of acquiring the  $SnD_4$  gas used as the Sn precursor. Additionally, it remained uncertain whether crystalline growth was possible at higher growth chamber pressures. In 2011, nine years after the initial publication of CVD growth, both of these issues were addressed by Atmospheric-Pressure CVD (AP-CVD) growth of crystalline  $Ge_{1-x}Sn_x$  layers on thick-Ge buffer on Si(001) substrates at IMEC, using the commercially available and thermally stable  $SnCl_4$  precursor, commonly used for tin-oxide growth, as the Sn source [35]. As  $SnCl_4$  is liquid at room temperature, a bubbler system is required to deliver the precursor in the gas phase.  $Ge_{1-x}Sn_x$  layer growth was conducted at a fixed 320 °C temperature, which is within the temperature range used in the previous research by the Arizona group. With these growth conditions, a peak  $Ge_{1-x}Sn_x$  alloy Sn fraction of Sn at. % was

achieved. Rapid thermal anneals (RTA) were conducted on these structures at 400 °C and 500 °C for both 10 and 30 minutes in  $N_2$  atmosphere. The 30 minute anneals at 500 °C were found to degrade the  $Ge_{1-x}Sn_x$  epilayer, with the Sn atoms diffusing in the Ge buffer. The  $Ge_{1-x}Sn_x$  Bragg peak was observed in x-ray diffraction scans of all samples – indicating that even after the most intense anneal the  $Ge_{1-x}Sn_x$  epilayer crystallinity was not completely lost. The authors note that if any  $Ge_{1-x}Sn_x$  layer strain relaxation was observed, it was not to a significant degree. Also investigated in this work was *in-situ* B doping of the  $Ge_{1-x}Sn_x$  layer, it was found that the boron precursor competes with the Sn precursor during growth, with the doped  $Ge_{1-x}Sn_x$  layers having a lower Sn fraction to undoped layers grown under otherwise similar growth conditions. These are the initial results of the thermal (in)stability of  $Ge_{1-x}Sn_x$  epitaxial layers grown by CVD.

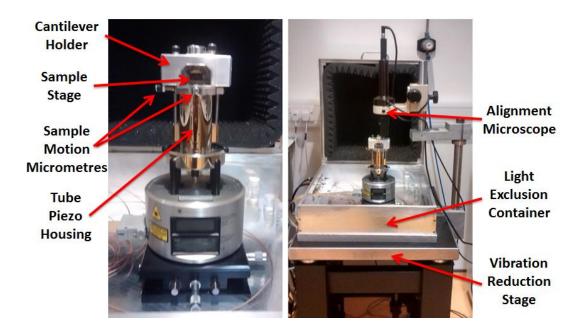

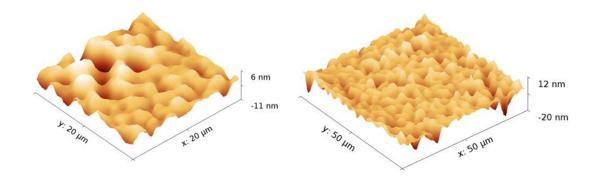

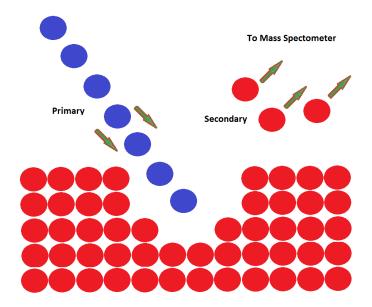

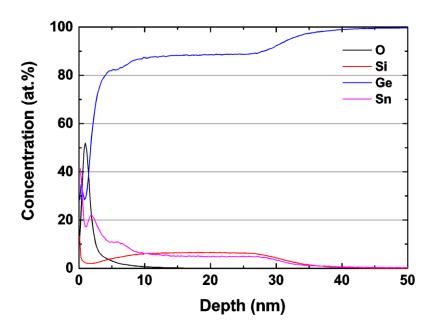

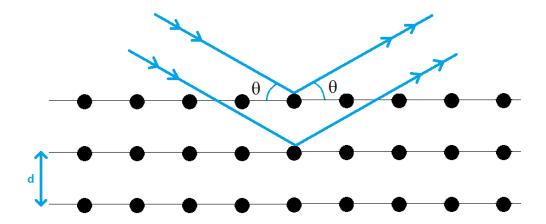

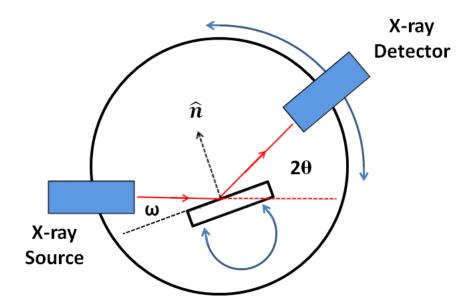

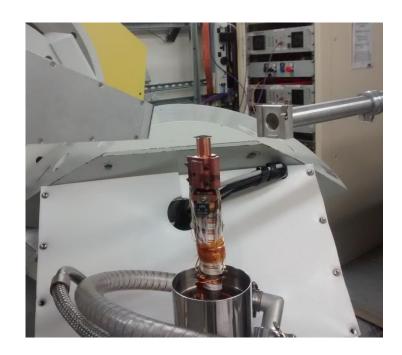

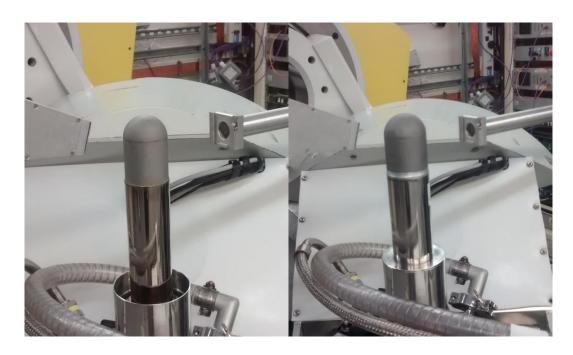

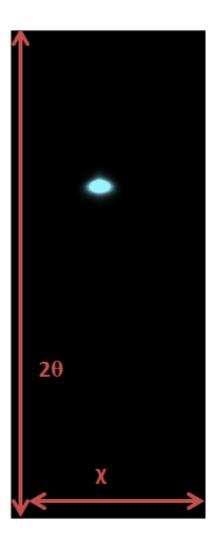

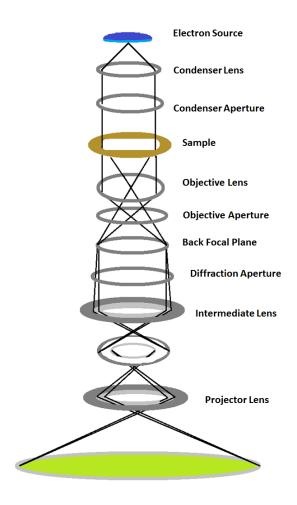

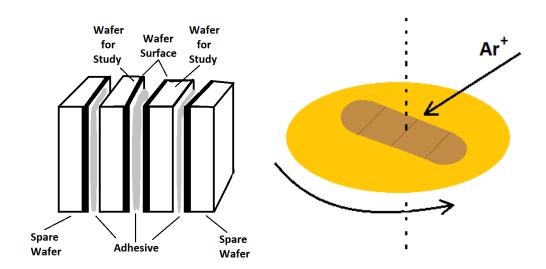

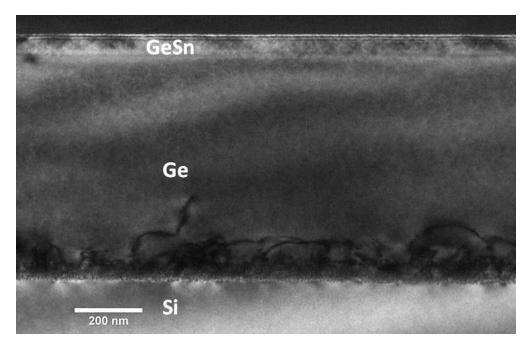

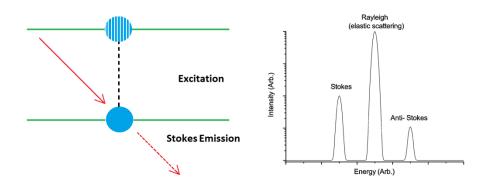

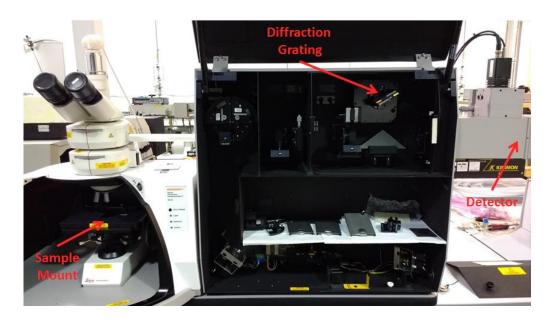

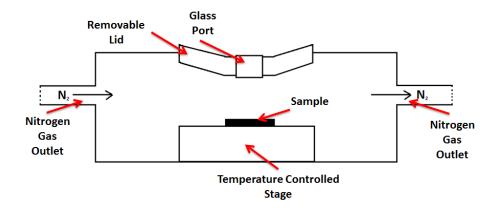

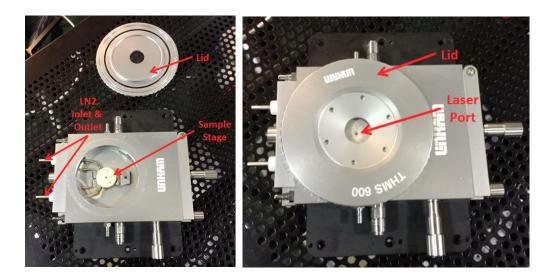

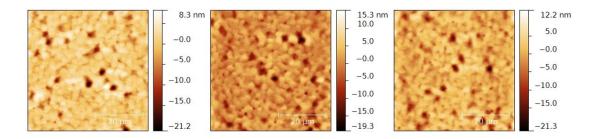

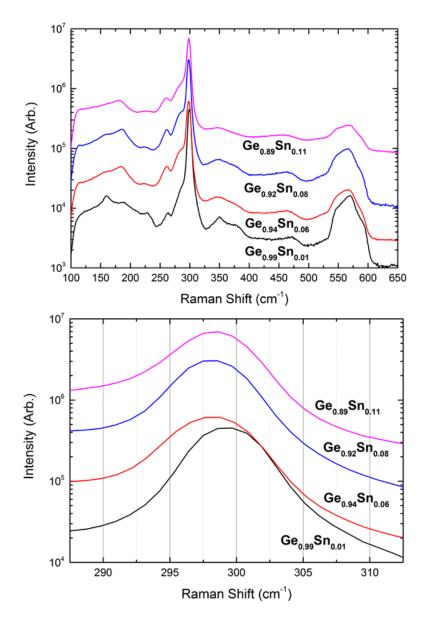

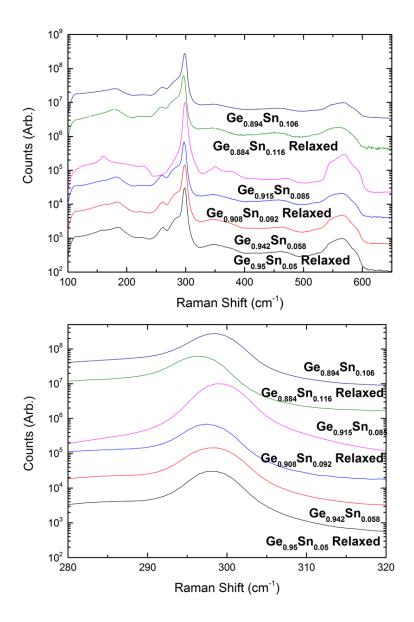

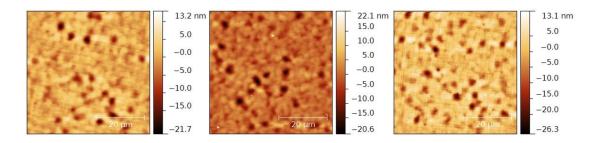

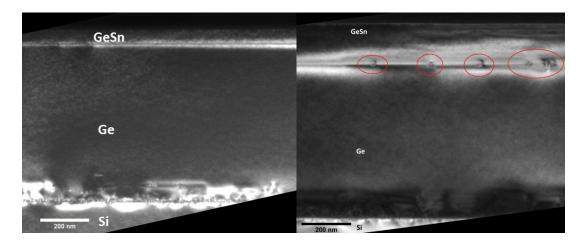

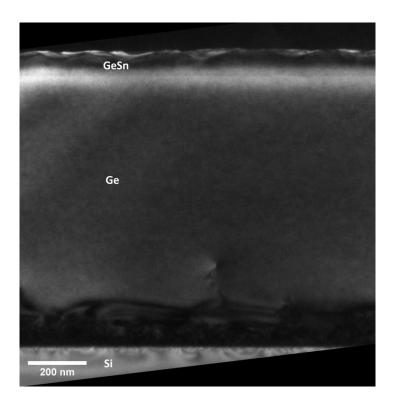

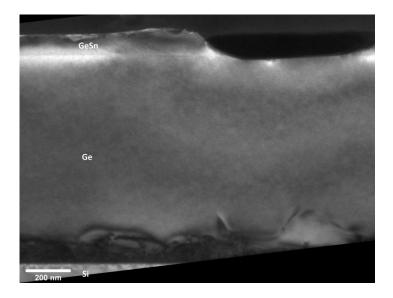

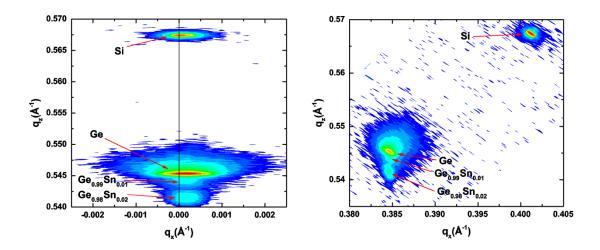

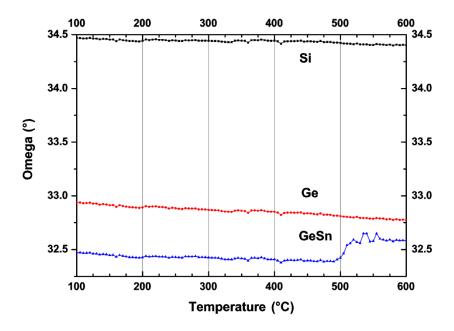

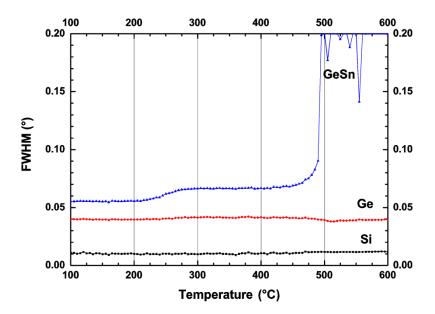

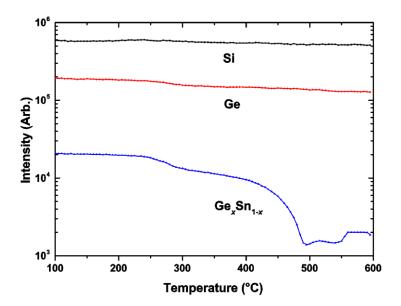

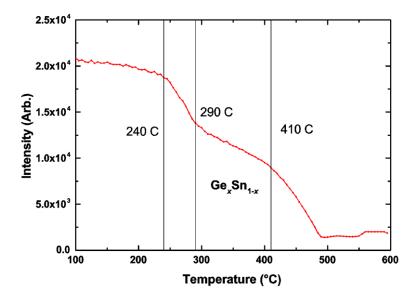

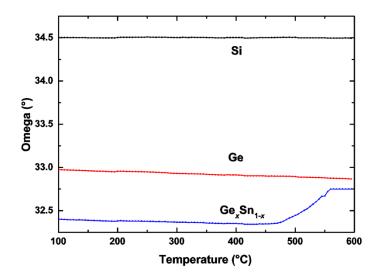

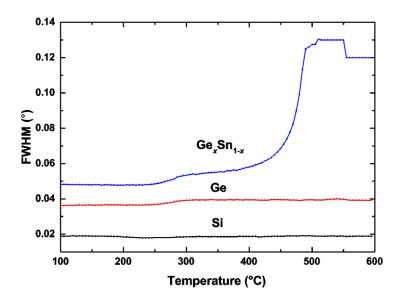

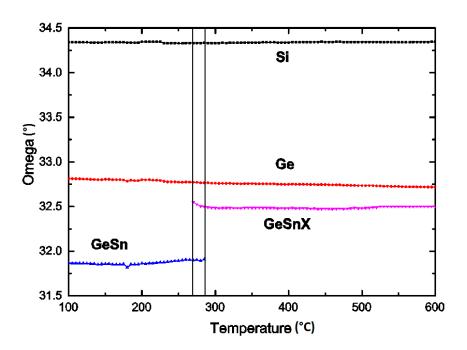

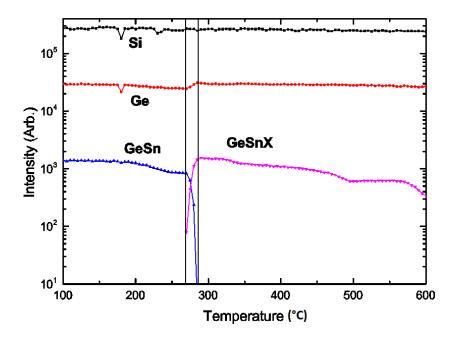

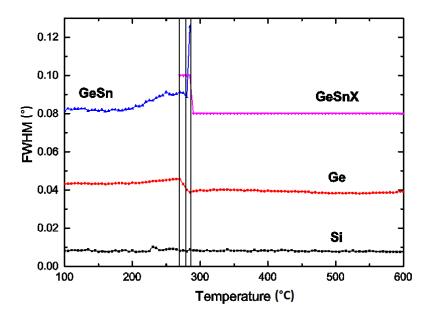

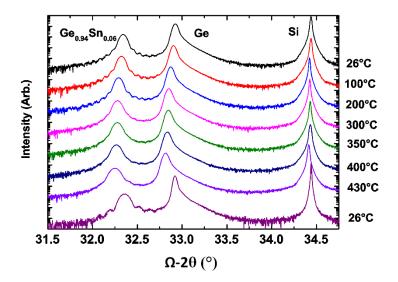

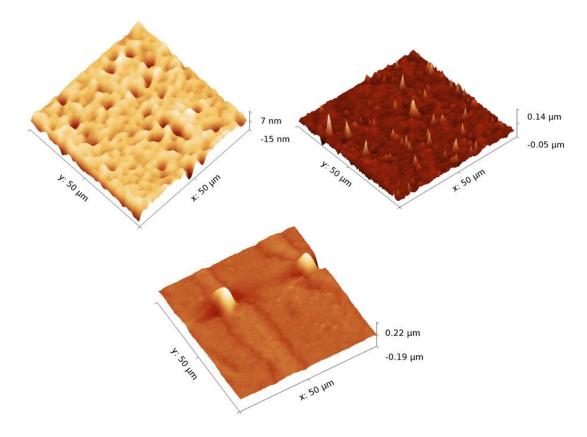

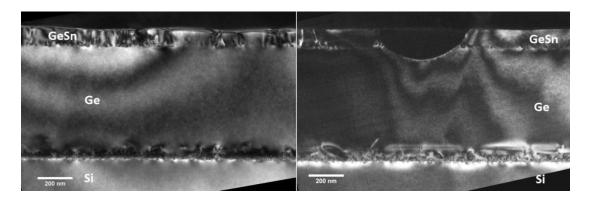

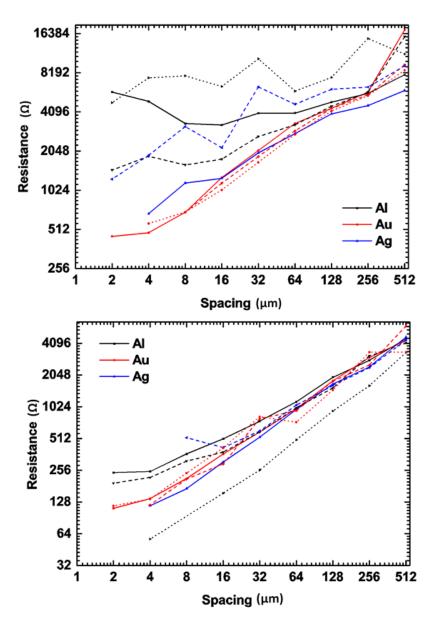

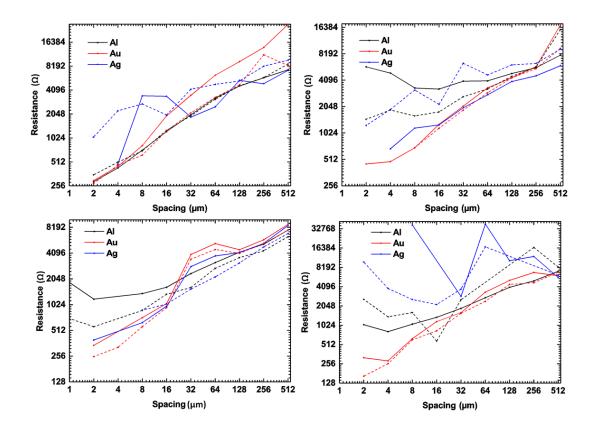

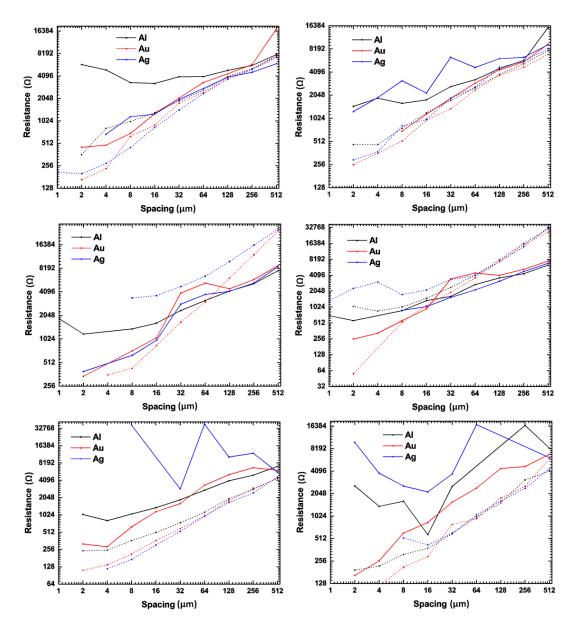

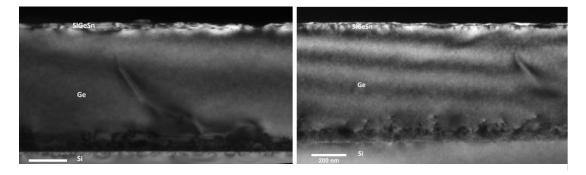

The growth of crystalline  $Ge_{1-x}Sn_x$  epilayers by Reduced-Pressure CVD (RP-CVD) was first demonstrated in 2012 in Juelich. This work demonstrated the growth of  $Ge_{1-x}Sn_x$  alloys with a Sn fractions up to 10 at. %. For  $Ge_{1-x}Sn_x$  growth this work used the now established  $Ge_2H_6$  and  $SnCl_4$  precursors. The CVD uses a vertical 'showerhead' set-up in order to improve layer growth uniformity and reduce precursor gas consumption [43]. In this work the  $Ge_{1-x}Sn_x$  growth temperature range used was higher than reported previously, from 375 °C to 475 °C, this apparent discrepancy is attributed to the substrate temperature being measured by thermocouples encased in a graphite susceptor with heating provided by IR lamps leading to incorrect temperature measurements. This work demonstrated that the low temperature growth rate of pure Ge can be increased by using  $N_2$  carrier gas instead of  $H_2$  carrier gas and using  $Ge_2H_6$  rather than  $GeH_4$  as the Ge precursor source.  $Ge_{1-x}Sn_x$  layers were grown directly onto a Si(001) substrate, without a Ge buffer.