# **Durham E-Theses**

Modelling and analysis of failures in CMOS integrated circuits.

Johnson, Simon

#### How to cite:

Johnson, Simon (1993) Modelling and analysis of failures in CMOS integrated circuits., Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/1562/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# Modelling and Analysis of Failures in CMOS Integrated Circuits

## Simon Johnson

## **Abstract**

The research presented in this thesis is concerned with the failure mechanisms and faults that arise in CMOS VLSI circuits. The aim of this work is to demonstrate that currently accepted methods used for the testing of CMOS integrated circuits, are inadequate for a significant proportion of defects that can occur. Failure mechanisms that occur in these circuits are investigated. A number of faults that are not covered by current testing techniques are identified. These can be characterised by their tendency to cause changes in device and circuit parameters, rather than logical faults. The parameters that are commonly affected are transistor threshold voltages, logic gate propagation delays and quiescent supply current requirements.

One of the most common faults in this category occurs when a signal track on an IC becomes open circuit. This fault, which we term the *floating gate* fault, is investigated in detail. Analysis is presented to show that the fault represents a large proportion of all possible photolithography faults. Mechanisms which can lead to this fault occurring during the operation of ICs are identified. Experimental analysis of test devices and circuits indicates that the characteristics of this fault can result in non-logical errors in circuits. Standard stuck-at and stuck-open test techniques are shown to be inadequate for a large number of these failures.

A theoretical model of the floating gate MOS transistor is developed. This provides a physical understanding of the operation of the device. It also enables prediction of the characteristics of floating gate transistors for a wide range of device parameters. The model is used to develop a circuit simulation model. Analysis of a wide range of CMOS circuits is presented to demonstrate the effect of the floating gate fault on circuit operation. The fault is shown to be undetectable by stuck-at and stuck-open testing for a wide range of device parameters. The results of this analysis enable a testing method to be identified for the floating gate fault. To ensure detection of these faults, quiescent power supply monitoring is necessary in addition to thorough stuck-open testing. Provision of this method of testing can improve the detection of faulty circuits by three to four percent.

The copyright of this thesis rests with the author.

No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

# Modelling and Analysis of Failures in CMOS Integrated Circuits

## Simon Johnson

This thesis is submitted to the University of Durham in candidature for the degree of Doctor of Philosophy

School of Engineering and Computer Science

University of Durham

1993

## **Declaration**

The material contained within this thesis is the sole work of the author and has not been submitted previously for a degree in this or any other University.

## **Statement of Copyright**

The copyright of this thesis rests with the author. No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

## Acknowledgements

I would like to thank my supervisors, Professor Phillip Mars and Dr. Martin Morant, for their constructive criticism and careful reading of this thesis. I would also like to thank Martin for many helpful discussions on the work over the past years.

I must also thank my wife, Eleanor, for reading every word of this thesis, and, despite not understanding a word of it (she claims!), correcting my grammar impecably. The time that Eleanor and David and Rosie have given to this work will always be appreciated.

# Contents

| Cn  | iapier i                                                      |     |

|-----|---------------------------------------------------------------|-----|

| Int | roduction                                                     | 1   |

| 1.1 | Aims of the Thesis                                            | 2   |

| 1.2 | An Outline of the Thesis                                      | 2   |

| Ch  | apter 2                                                       |     |

| Fai | ilure Mechanisms and Fault Models                             | 4   |

| 2.1 | Terminology                                                   | 4   |

| 2.2 | Failure Mechanisms                                            | 5   |

|     | 2.2.1 Production Defects                                      | 5   |

|     | 2.2.2 Lifetime or Field Failures                              | 7   |

|     | 2.2.3 Faults and the Electrical Effects of Production Defects | 10  |

|     | 2.2.4 The Electrical Effect of Field Failure Defects          | .19 |

|     | 2.2.5 Summary of Failure Mechanisms                           | 24  |

| 2.3 | Fault Models                                                  | 25  |

|     | 2.3.1 Classical Fault Models.                                 | 25  |

|     | 2.3.2 CMOS Stuck-Open Fault Model                             | 28  |

|     | 2.3.3 Parametric Fault Models                                 | 30  |

| 2.4 | The Correlation Between Failure Mechanisms and Fault Models   | 33  |

| 2.5 | Chapter Summary                                               | 38  |

| Ch  | apter 3                                                       |     |

| Th  | e Floating Gate Fault                                         | 39  |

| 3.1 | Causes of the Floating Gate Fault                             | 39  |

| 3.2 | The Significance of the Floating Gate Fault                   | 44  |

|     | 3.2.1 Layout Design Errors                                    | 44  |

|     | 3.2.2 Photolithography Defects                                | 44  |

|     | 3.2.3 Photolithography Fault Distribution Experiments         | 46  |

|     | 3.2.3.1 Generation of Defects                                 | 46  |

|     | 3.2.3.2 Assessment of Defects                                 | 48  |

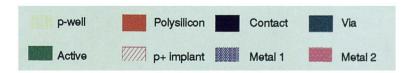

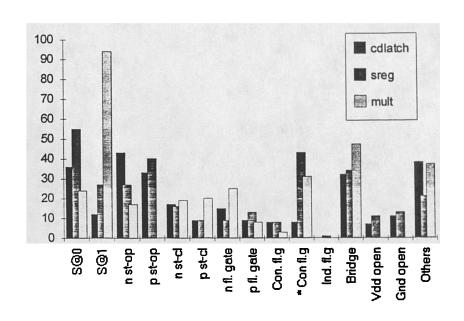

|     | 3.2.3.3 Defect Simulations                                    | 52  |

|     | 3.2.3.4 Results of the Simulations                            | 57  |

|     | 3.2.3.5 Summary of Fault Distribution Experiments             | 58  |

|     | 3.2.4 Electromigration                                        | 52  |

|     | 3.2.5 Contact Migration                                                        | 60  |

|-----|--------------------------------------------------------------------------------|-----|

|     | 3.2.6 Stress Migration                                                         | 60  |

|     | 3.2.7 Summary of the Significance of Floating Gate Faults                      | 61  |

| 3.3 | The Electrical Effect of the Floating Gate Fault                               | 61  |

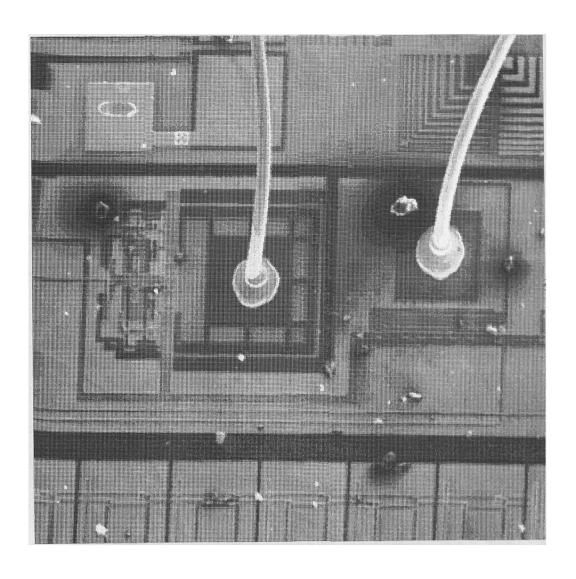

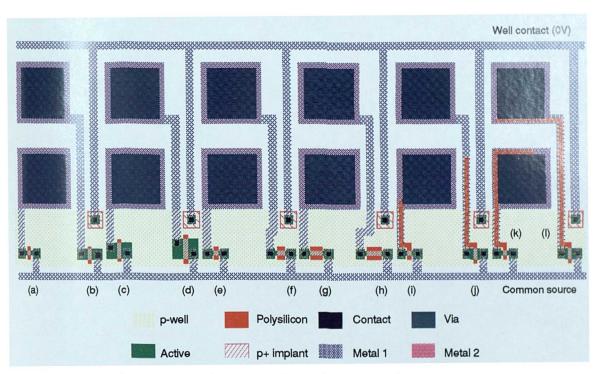

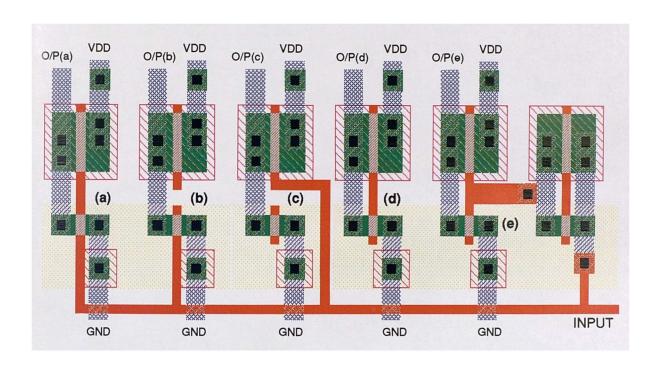

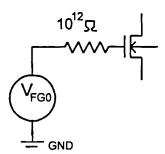

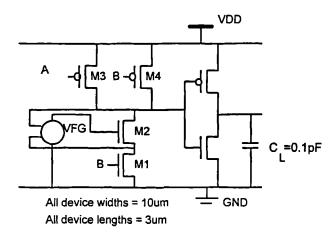

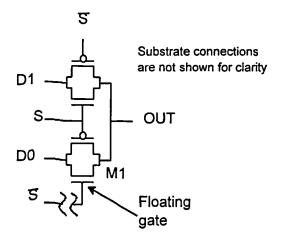

| 3.4 | Test Circuits for the Analysis of the Floating Gate Fault                      | 65  |

| 3.5 | Chapter Summary                                                                | 70  |

| Ch  | napter 4                                                                       |     |

| Vo  | oltage Contrast Microscopy of Integrated Circuits                              | 72  |

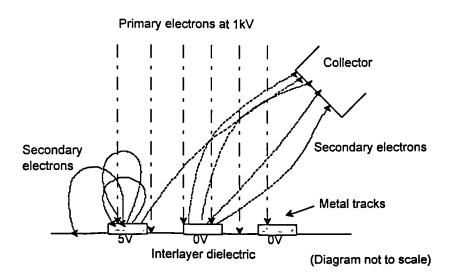

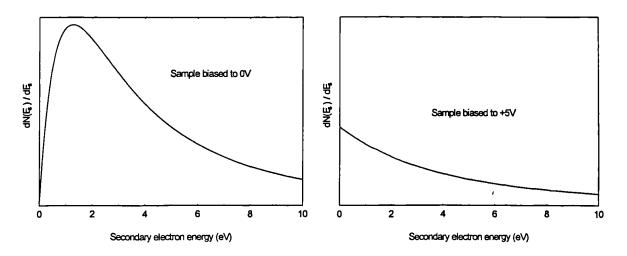

|     | Scanning Electron Microscopy Analysis                                          | 72  |

|     | 4.1.1 The Principles of Voltage Contrast in the Scanning Electron Microscope   |     |

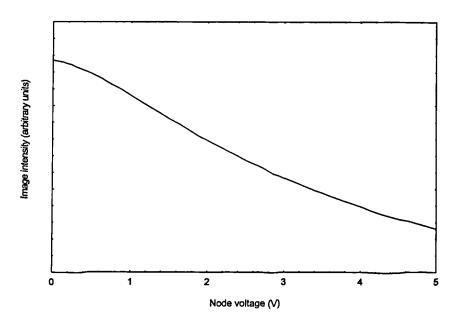

|     | 4.1.2 Quantitative Voltage Measurements using Image Contrast                   | 76  |

|     | 4.1.3 Voltage Measurements using Secondary Electron Energy Analysis            | 77  |

|     | 4.1.4 Voltage Measurements on Buried Nodes                                     | 78  |

| 4.2 | The Measurement System                                                         | 81  |

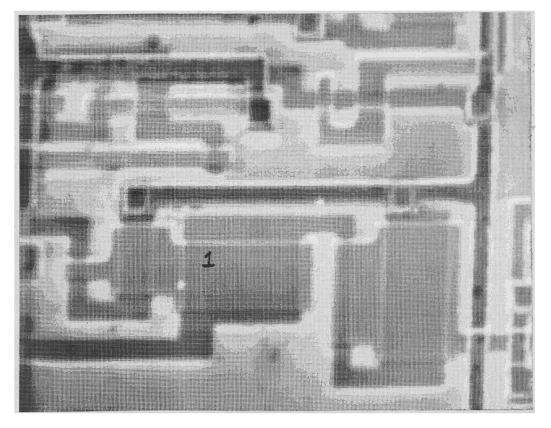

| 4.3 | Intensity Analysis for Quantitative Voltage Contrast                           | 81  |

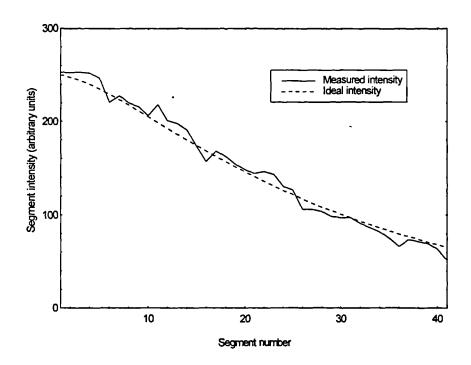

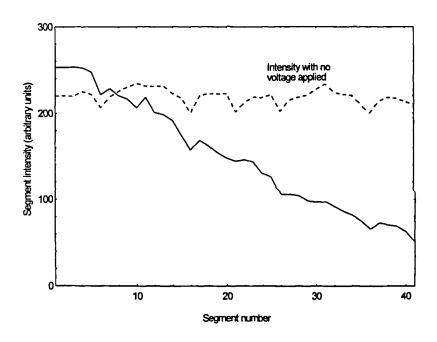

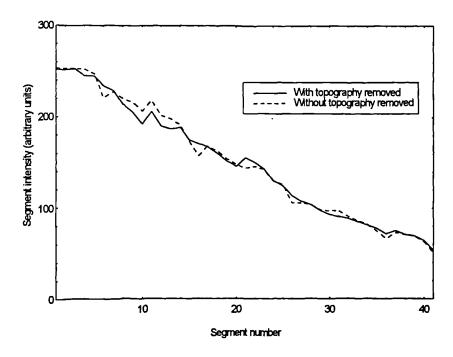

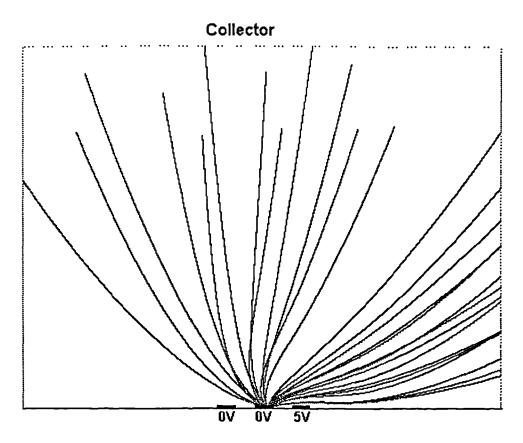

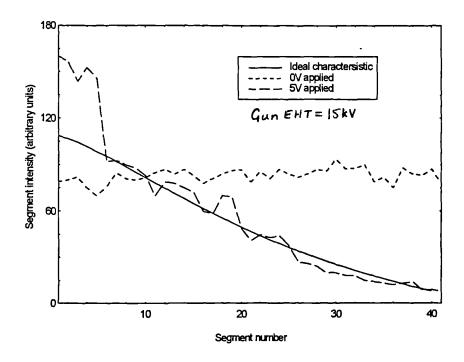

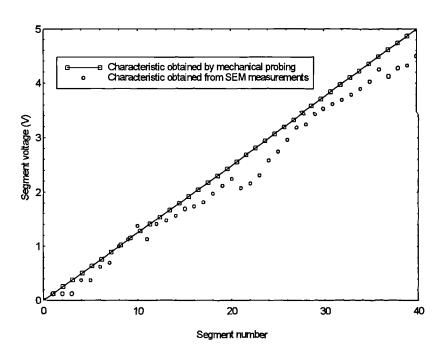

|     | 4.3.1 Voltage Contrast Intensity Measurements for the Contact Chain            | 83  |

|     | 4.3.2 Obtaining Track Voltages from Intensity Measurements                     | 89  |

|     | 4.3.3 Conclusions on the use of Intensity Measurements for Qualitative Voltage | ;   |

|     | Contrast                                                                       | 90  |

| 4.4 | Voltage Measurements on Floating Gate Devices                                  | 90  |

| 4.5 | Chapter Summary                                                                | 91  |

| Ch  | apter 5                                                                        |     |

| Ex  | perimental Analysis of Floating Gate Transistors                               | 93  |

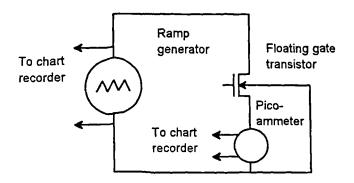

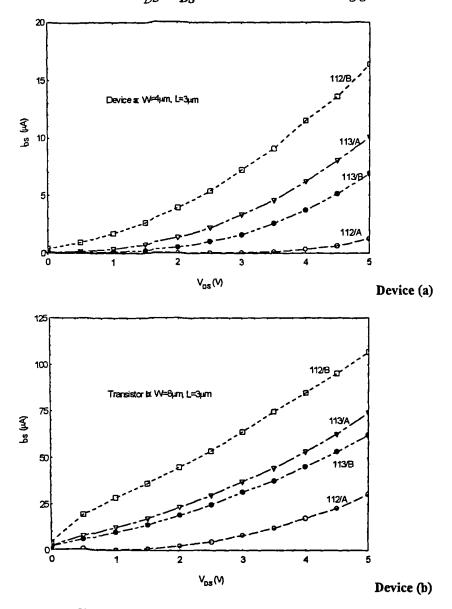

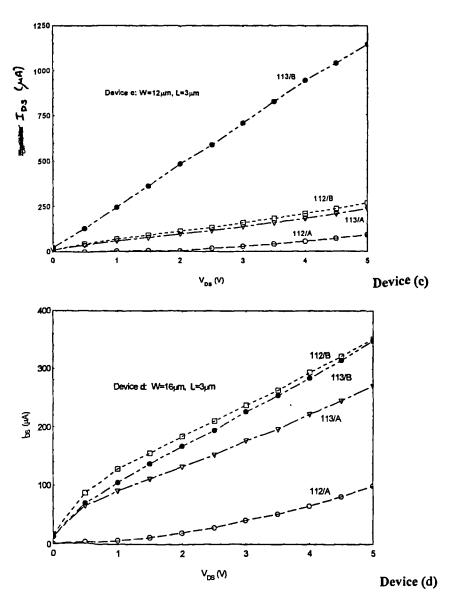

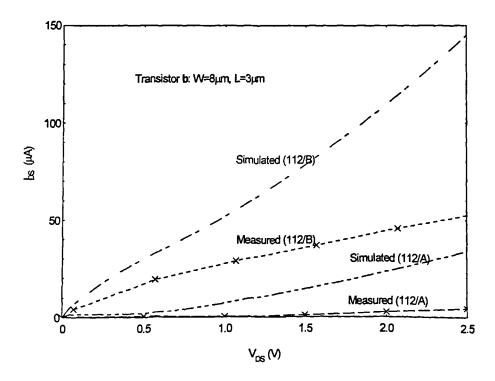

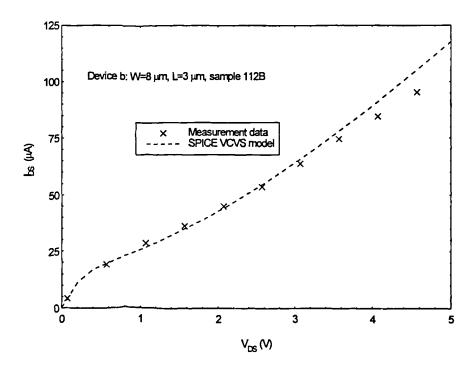

|     | Analysis of Floating Gate Transistors                                          |     |

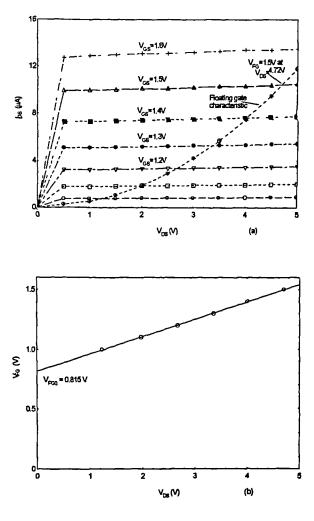

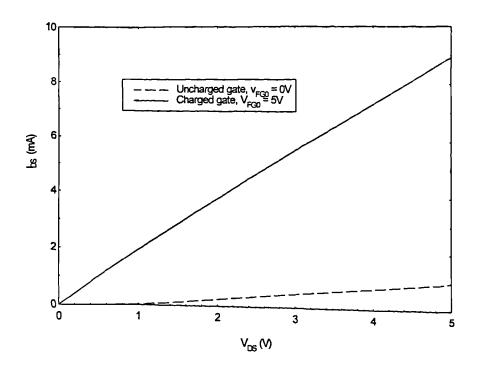

|     | 5.1.1 $I_{DS}$ - $V_{DS}$ Characteristics for Floating Gate Transistors        |     |

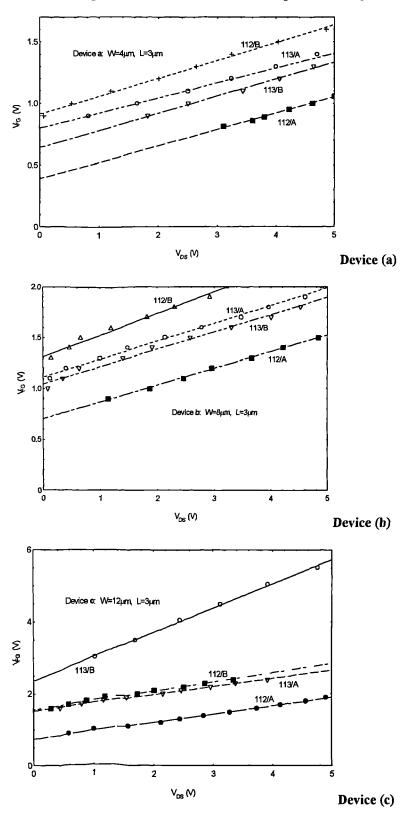

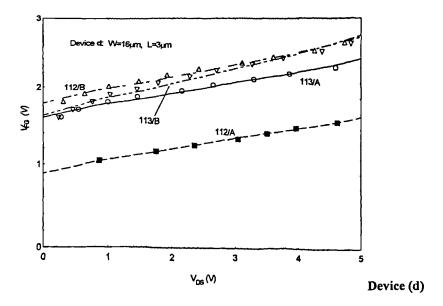

|     | 5.1.2 The Floating Gate Potential and the $V_{FG}$ - $V_{DS}$ Relationship     |     |

|     | 5.1.3 Measurements on p-channel Floating Gate Transistors                      |     |

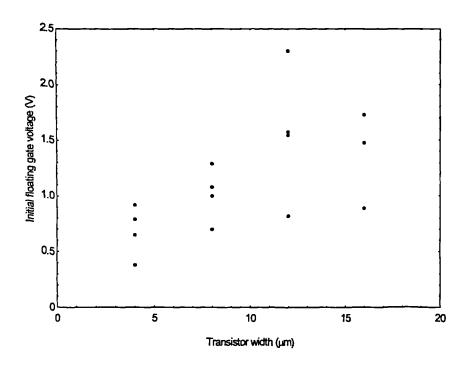

|     | 5.1.4 The Measured $V_{FG0}$ Values and the Source of Residual Charge          |     |

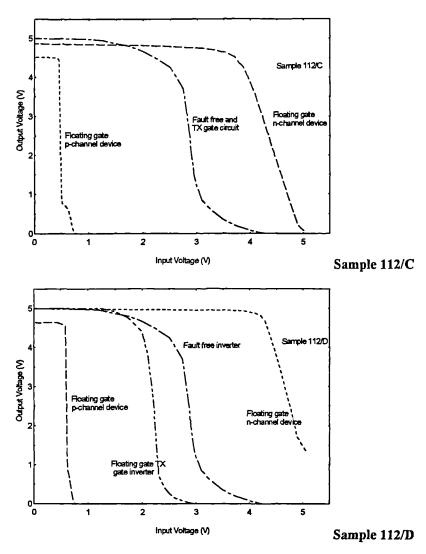

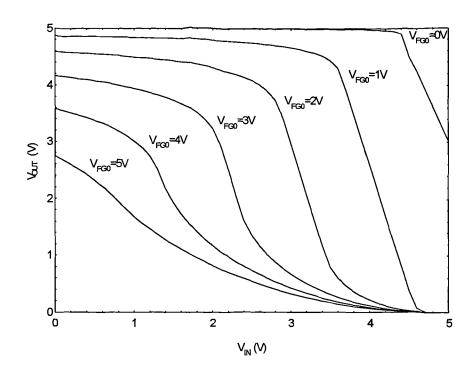

| 5.2 | Operation of Inverters with Floating Gate Faults                               |     |

|     | 5.2.1 Output Characteristics for the Inverter Circuits                         |     |

|     | 5.2.2 Floating Gate Voltages in the Inverter Circuits                          |     |

| 5.3 | Operation of Logic Gates with Floating Gate Faults                             | 113 |

|     | 5.3.1 Problems with the Electrical Testing of the Logic Gates                  |     |

|     | 5.3.2 Logical Operation of Gates with Floating Gate Faults                     |     |

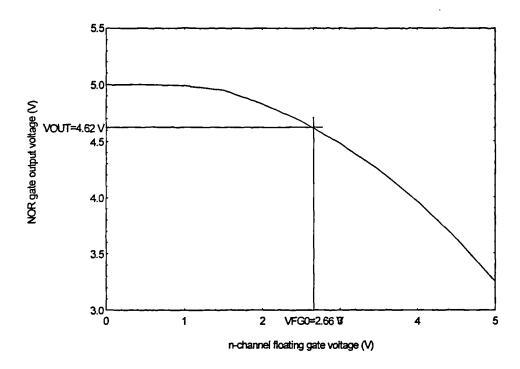

|     | 5.3.3 Floating Gate Voltage Measurements                                       | 117 |

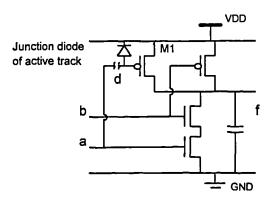

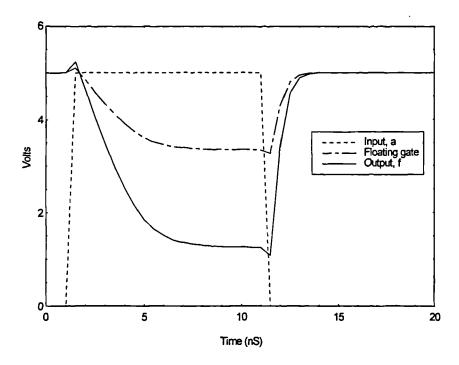

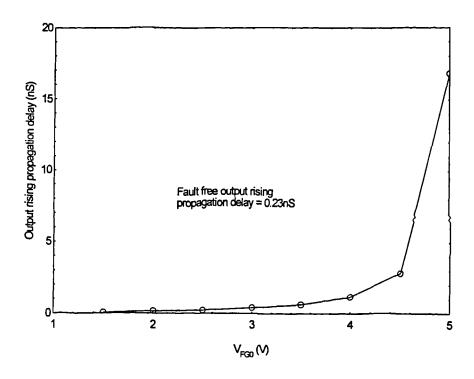

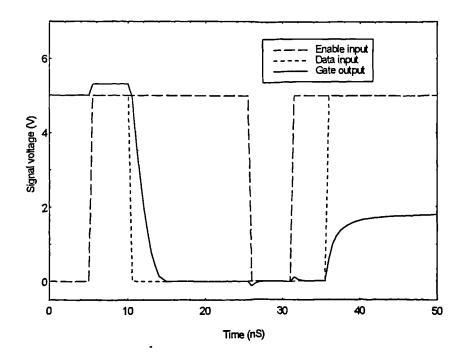

|     | 5.3.4 Dynamic Testing of Logic Gates with Floating Gate Faults                 | 110 |

| 5.4 | Chapter Summary                                                             | 120 |

|-----|-----------------------------------------------------------------------------|-----|

| Ch  | napter 6                                                                    |     |

| A   | Model Of The Floating Gate MOS Transistor                                   | 122 |

| 6.1 | Existing Models                                                             | 122 |

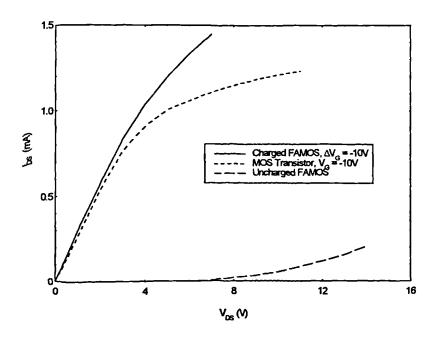

|     | 6.1.1 The Floating Gate Avalanche MOS Transistor                            |     |

|     | 6.1.2 The Experimental Analysis of Circuits Containing Floating Gate Faults |     |

| 6.2 | Operation of the Faulty Floating Gate MOS Transistor                        |     |

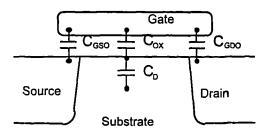

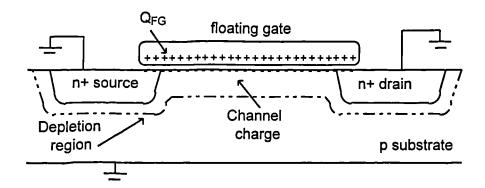

|     | 6.2.1 The Floating Gate Potential with Zero Drain Bias                      |     |

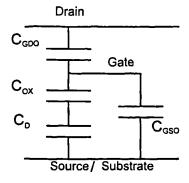

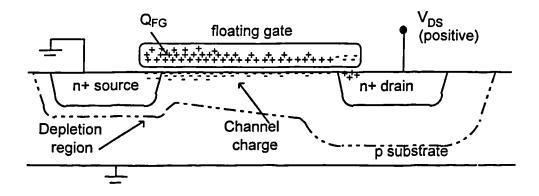

|     | 6.2.2 The Floating Gate Potential with Applied Drain Bias                   | 131 |

| 6.3 | Refinements of the Model                                                    | 134 |

| 6.4 | Analysis of the Floating Gate MOS Transistor Operation                      | 130 |

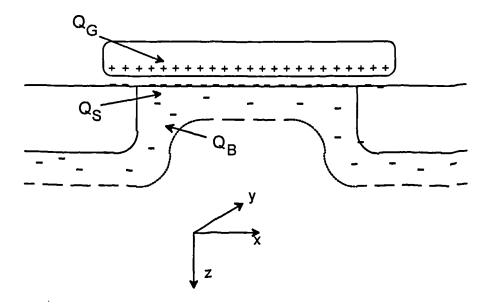

|     | 6.4.1 Floating Gate Transistor Charge Distributions                         | 137 |

|     | 6.4.2 Channel Potential Distribution                                        | 139 |

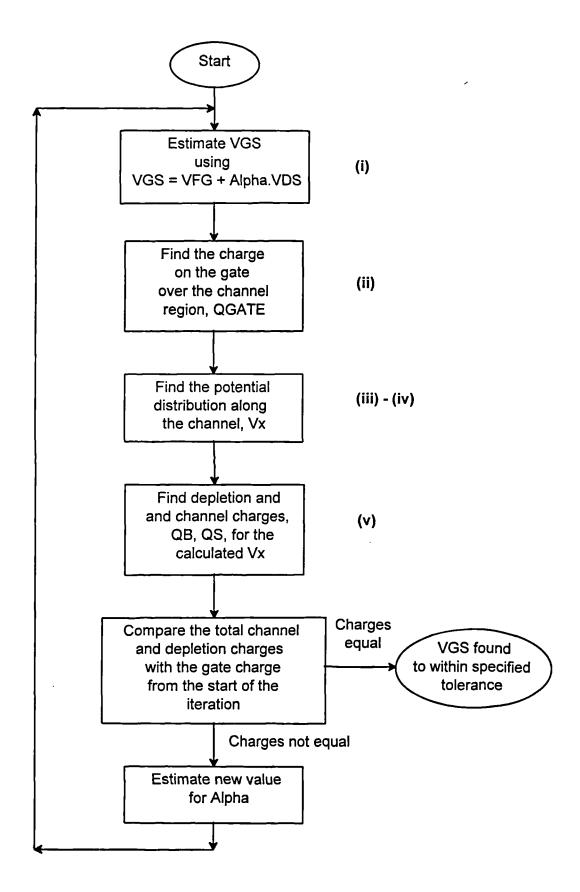

| 6.5 | An Algorithm for the Calculation of the Floating Gate Voltage               | 141 |

| 6.6 | The Floating Gate MOS Transistor Model Program, FLGMOD                      | 146 |

| 6.7 | Some Basic Results of the Model                                             | 147 |

| 6.8 | Chapter Summary                                                             | 149 |

| Ch  | apter 7                                                                     |     |

| CN  | MOS Circuit Performance and Testing for Floating Gate Faults                | 150 |

|     | Circuit Simulation Models For The Floating Gate Transistor                  |     |

|     | The Operation of Logic Gates with Floating Gate Faults                      |     |

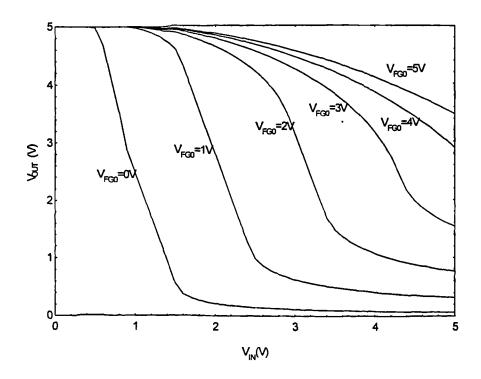

|     | 7.2.1 Static Operation of a CMOS Inverter                                   |     |

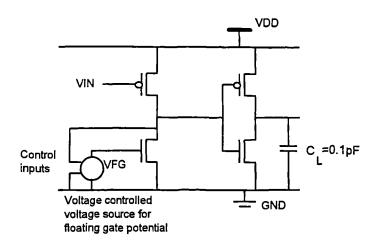

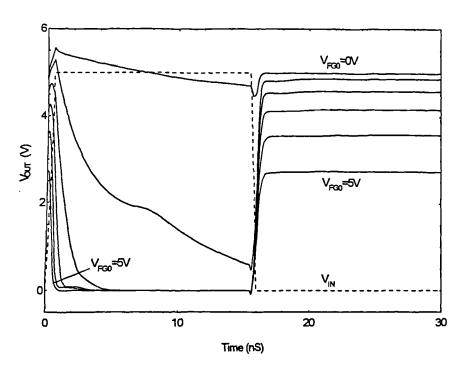

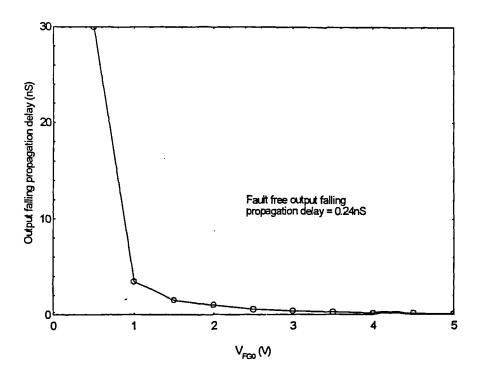

|     | 7.2.2 Dynamic Operation of a CMOS Inverter                                  |     |

|     | 7.2.3 Multiple Input Logic Gates                                            |     |

|     | 7.2.4 Summary of Logic Gate Operation with Floating Gate Faults             |     |

| 7.3 | Transmission Gates and Other Circuits.                                      | 172 |

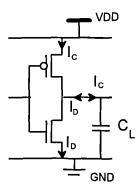

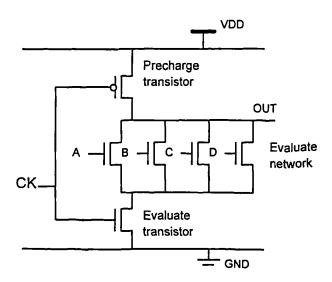

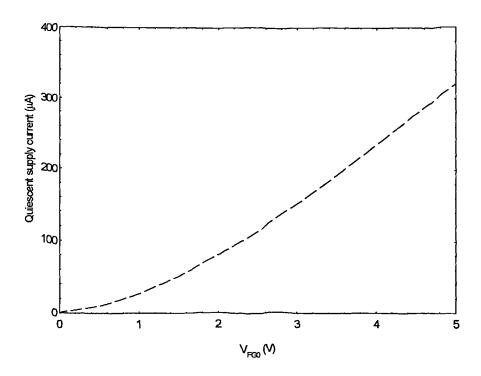

|     | 7.3.1 Dynamic Circuits and Floating Gate Faults                             | 175 |

| 7.4 | Testing for Floating Gate Faults                                            | 176 |

|     | 7.4.1 The Stuck-At Fault Model                                              | 176 |

|     | 7.4.2 The Stuck-Open Fault Model                                            | 177 |

|     | 7.4.3 The Stuck-Closed Fault Model                                          | 178 |

| 7.5 | The Implications of Inadequate Testing.                                     | 180 |

| 7.6 | Chapter Summary                                                             | 183 |

# Chapter 8

| Summary and Conclusions           | 184 |

|-----------------------------------|-----|

| 8.1 A Summary of the Thesis       | 184 |

| 8.2 The Conclusions of the Thesis | 188 |

| 8.3 Suggestions for Further Work  | 189 |

| 8.4 Some General Conclusions      | 190 |

| Appendix A                        |     |

| Listing of the FLGMOD Program     | 191 |

| References                        | 203 |

# Chapter 1

# Introduction

The testing of integrated circuits is a problem that does not diminish as the complexity of devices continues to increase. Higher levels of integration result in an increase in the ratio of the number of transistors to input and output pins. This makes access to the core of the chip, and therefore testing, more difficult. The problem is increased by a raised level of concern over the reliability of VLSI circuits. Decreasing feature size and increasing circuit density, increase the probability of failure due to wearout mechanisms in such circuits. Thorough testing is important for improved reliability, as any undetected faults that remain on a chip after testing can result in early failure of a circuit in the field.

The ability of production tests to detect defects in CMOS integrated circuits (ICs) has improved as understanding of the failure mechanisms in these has increased. This has been one of the factors that has resulted in improved reliability of ICs [1.1], despite many other factors which should reduce the mean-time-to-failure for these circuits [1.2]. It would, however, be short sighted to assume that the current state of knowledge of failure mechanisms and testing techniques are sufficient to guarantee reliable circuits as the level of integration increases. Indeed, it may be insufficient to assume that current testing techniques are adequate even for today's circuits.

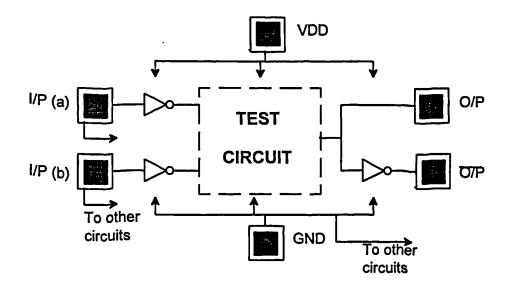

Improved reliability is one incentive for thorough testing of ICs. A second is the use of built-in-self-test on VLSI circuits. We have already seen that the testing problem increases as the level of integration rises. One solution to this problem is to build testing circuits onto the chip itself, thus overcoming the input / output bottleneck that VLSI circuits present in testing [1.3]. One of the requirements for such circuits is fully automated testing which should cover as many types of defect as possible and so we see a further need for thorough, and simply automated, testing techniques. Built-in-self-test circuits also provide a route to fault-tolerant ICs. Incorporation of redundant units or components and a comprehensive test system can allow a circuit to continue to operate correctly, even with many faults present [1.4].

In extending the ability of tests to detect physical defects, it is becoming necessary to think beyond simple logical faults. Timing faults [1.5], which only cause a circuit to fail above (or below) a certain operating speed, are an example of this extension from logical to parametric faults. It is no longer sufficient to use the logical function of a circuit as proof that it is free from faults. The use of other parameters, such as timing or supply current [1.6] is seen as a necessity to cover the range of subtle faults that exist in complex VLSI circuits.

#### 1.1 The Aims of this Thesis

The aim of this thesis is to demonstrate that current testing techniques for CMOS VLSI circuits are inadequate for a significant proportion of the physical defects that can occur. We intend to demonstrate that a particular class of fault, the *floating gate fault*, is not detected in a large number of cases by the tests commonly used for CMOS circuits. Furthermore, it will be shown that such faults represent a relatively large fraction of the range of possible faults that can occur.

In order to understand the effects of the fault, test structures have been designed and fabricated. A theoretical model of the faulty device will be developed in this thesis to provide an understanding of the floating gate transistor. This will enable the effects of the fault on circuit operation to be established.

Finally we will demonstrate that current logical testing techniques do not reveal the fault in a large number of cases. Consequently, a testing strategy to improve the coverage of the floating gate fault must be identified. It is the aim of this work to improve CMOS fault coverage for both production test and for future built-in-self-test systems. In this way it is hoped that a contribution can be made to improving integrated circuit reliability and the goal of the completely fault tolerant IC.

## 1.2 An Outline of the Thesis

The thesis starts with a survey and investigation of failure mechanisms in CMOS circuits. The relationship between the physical defects that can occur and the resulting faults is established. The effect of such faults on device and circuit performance is analysed and the failures that may result are identified. A distinction is made between circuit failures resulting from production defects and those that occur through intriginsic mechanisms over the lifetime of a component. Although different sources of physical defects exist, many of the resulting faults and failures are seen to be similar. The details of failure mechanisms are generally abstracted into fault models which can be used to simplify the generation of tests. The adequacy of such models for describing defects is investigated. We demonstrate that some defects are poorly represented by these models and that such defects are not uncommon. It is clear that certain forms of failure require more detailed investigation.

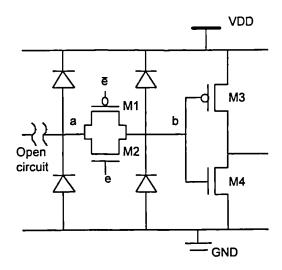

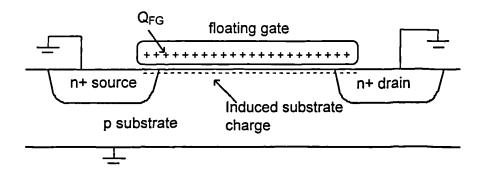

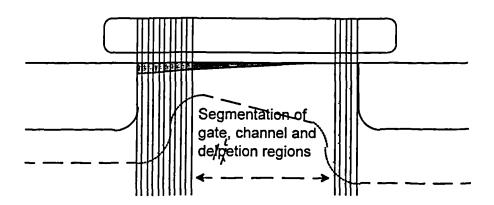

In Chapter 3, the most significant fault that is not adequately represented by existing models is investigated. This fault arises when an open circuit occurs in a signal line on a CMOS chip. This results in the gates of any transistors driven by this signal becoming isolated. We refer to this as a *floating gate fault*. The processes which give rise to this form of failure are identified and the significance of the fault is quantified by analysis of defect distributions in typical cell layouts. The effect of this type of fault is outlined and the need for experimental analysis is established. Test structures for the investigation of the fault are then described.

Chapters 4 and 5 describe the analysis of the test devices that have been fabricated for this work. In Chapter 4, the use of the voltage contrast technique in the scanning electron microscope is investigated as a method of obtaining floating gate device characteristics. This is found to be inadequate to provide the information required. Electrical measurements on floating gate devices and circuits are described in Chapter 5. The characteristics of floating gate transistors are established and various device parameters investigated. Two significant parameters associated with the device are identified. The effect of floating gate faults on simple CMOS circuits is analysed. Wide variations in the significance of the effect of the fault on circuit operation is observed.

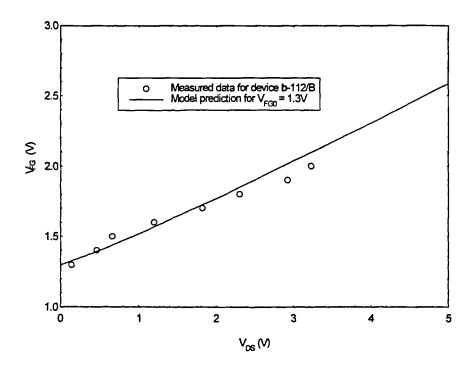

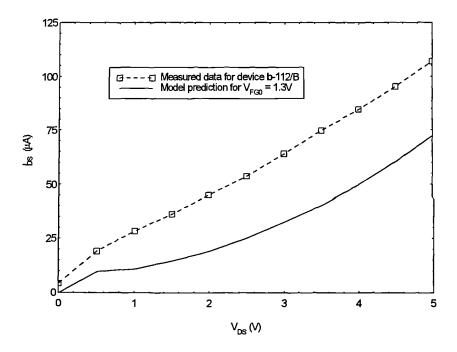

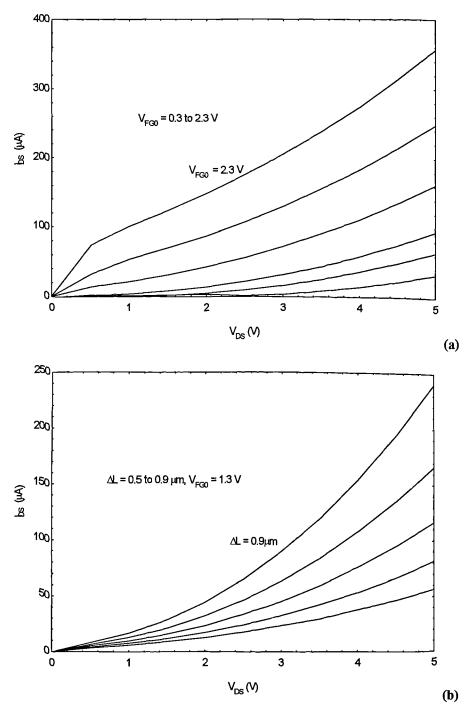

Chapter 6 describes the development of a theoretical model for the floating gate MOS transistor. This is done to provide a physical understanding of the operation of the device, which is essentially a normal MOS transistor with a fixed gate charge. A computer program which has been used to calculate various device characteristics is described, and the predictions of the model are compared with the measurements reported in Chapter 4.

In Chapter 7 the results of the experiments and theoretical model are used to analyse the effect of floating gate faults on CMOS circuits. A simulation model is developed to assist in the analysis. The static and dynamic operation of a range of logic gates is investigated. The conclusions that are drawn are used to identify testing techniques for floating gate faults and a recommendation is made for satisfactory testing of these faults. Finally, the implications of inadequate testing for floating gate and other faults is discussed.

We conclude the thesis in Chapter 8 with a summary of the work and consideration of the significance of the results. Some suggestions for further research in this area are also made.

# Chapter 2

# Failure Mechanisms and Fault Models

Failure mechanisms in integrated circuits are generally well understood and electrical models of the effect of failures have been established for many years. The dominance of CMOS as the technology for VLSI circuits has led to a refinement in the models used for fault analysis. This has occurred because the electrical effect of some faults is not accurately represented by the more traditional fault models. Some failure mechanisms, however, are still incorrectly modelled in CMOS resulting in inadequate test generation and fault coverage. Consequently, circuits may pass stringent testing procedures and still contain significant faults which can lead to failures in the operation of devices.

In this chapter we will review the current understanding of defects as it is described in the literature. From this we will establish the most common forms of defect that arise in CMOS IC's, both from production and during operation of the circuits. We will then analyse the effects of these defects on circuit performance and investigate the effectiveness of existing fault models for detecting the resulting faults. It will be shown that some failure mechanisms produce faults that may not be detected by existing fault models. The aim of later chapters will be to show how this situation can be improved by the addition of fault models for a particular class of defect - the open circuit gate.

## 2.1 Terminology

Various terms are used to describe faults in electronic circuits and these are not always used consistently by different authors. It is therefore worthwhile defining the terms that will be used in this thesis.

Defect:

the physical deviation of a feature from the required form. For example, a gap in a feature or a deviation from the specified width of a feature.

Fault: the effect of a defect on a circuit or component. For example, a defect

such as a gap in a feature may lead to the fault of an open circuit track; a defect such as an oxide pinhole may lead to the fault of a

conductive path from gate to channel in an MOS transistor.

Fault effect: the effect of a fault on a component or circuit. For example, a fault

which creates a conductive path between the gate and channel of an MOS transistor will have the effect of decreasing the charge storage

time on the gate.

Failure: incorrect operation of a component or circuit due to the presence of a

fault. For example an open circuit track may lead to the failure to

discharge a circuit node when required within the specified time.

Failure mechanism: the process by which a failure occurs in a component or circuit.

This term encompasses all of the above terms i.e. a defect must be present to cause a fault in a component. This may affect the

performance causing a failure to occur.

It is important to note that a defect will not always result in a fault occurring in a circuit and that the consequential effect of that fault may not lead to a failure of the device or circuit.

### 2.2 Failure Mechanisms

Failures in an integrated circuit may arise during the fabrication of the IC or during its operational lifetime. Failures that occur during fabrication result in a less than perfect yield figure for the circuit and should be detected during the many testing procedures that take place during the fabrication and packaging of the IC. Failures occurring during the operational lifetime of the IC constitute a reliability hazard for the component. They will probably be detected by the failure of the complete system containing the device. Alternatively, failures may be detected during circuit operation by built-in-test circuits if the latter have been included on the circuit. In both cases the result is a system failure unless fault tolerance has been built into the system or device.

The defects which can occur in production are generally different from those that occur during the operation of the device. We will now consider the two cases.

#### 2.2.1 Production Defects

The term "production failures" is used to indicate any failure that may occur in the IC before it leaves the manufacturer. The defects that cause these failures may arise from

incorrect processing, or contamination of the wafers or chemicals that are used. A defect may lead to a fault in a circuit and this will generally have an effect on the electrical performance of the circuit.

The effects of physical defects that can arise in integrated circuits have been investigated by many workers. Fewer papers have been published on the actual defects that can occur. However, one interesting paper in this area by Fantini and Morandi [2.1] includes failure data from a range of sources. Defects are classified into the following categories: i) crystal defects; ii) charge trapping in the gate oxide; iii) gate oxide pinholes; iv) contact surface defects; v) conductor thinning, contamination, and hillock formation; vi) poor wire bonding; vii) poor die attach. These defects all result from imperfections in the fabrication process generally associated with the material layer or surface preparations. The authors do not mention photolithographic errors due to particulate contamination, or uneven etching or deposition over a wafer. The authors identify some fault effects which do not have a corresponding physical defect. These include random ionising radiation events, electrostatic discharge damage and hot carrier problems. These will be discussed in a later section when fault effects are considered.

Another paper which discusses defects, Burgess et al [2.2], is based on analysis of failed NMOS circuits from a British Telecom production line. Many of the defects illustrated arise from photolithographic errors caused by particulate contamination, the source of defect found to be insignificant by Fantini and Morandi. From this we may surmise that the distribution of production defects among the various classifications can be quite specific to a production line. Consequently, a single source of information on IC defects is not a sufficient basis for the formation of general conclusions.

In another paper [2.3], the same authors identify a list of MOS faults which includes device length and width variations. The defects that are most likely to give rise to these faults are uneven etching or poor photolithography. Further support for particulate contamination leading to photolithographic related defects is provided by Kemp, Poole and Frost [2.4]. In this paper the effect of track narrowing due to particulate contamination during photolithography is investigated. This defect is found to result in early lifetime failures of metal tracks resulting in a reliability hazard. This is an example of a production defect leading to a latent fault which subsequently causes failure during circuit operation.

Other papers on the subject of physical failures and defects ([2.5], [2.6], [2.7], [2.8]) do not reveal any further categories of defect. The following list summarises the defects identified in the literature survey described above. All of the defects listed may occur in a standard CMOS process.

i) Crystallographic defects: these appear in the substrate regions of transistors.

The defects result in incomplete bonding within the crystal structure producing

sites for charge trapping and for the accumulation of dopants. These can lead to increased substrate and leakage currents.

- ii) Particulate contamination: this causes errors in the photolithographic process used to define features in the layers of the integrated circuit. Particles may result in additional or missing material on a layer causing malformed features or the complete absence of small features, such as interlayer contact cuts.

- Surface contamination: this can result in poor definition of features and contamination of interfaces such as interlayer contacts. This defect is particularly difficult to identify as the surface contaminant often disappears in subsequent processing.

- vi) Oxide defects: in homogeneous growth of thermal oxide can result in "pin holes" in oxide layers, particularly in thin gate oxides. The holes, although very small (typically less than 0.01μm), can have a serious effect on circuit performance. The gate oxide thickness may also deviate from the required value altering transistor characteristics. Charge trapping in oxides can also occur resulting in mirror charges in device structures.

- v) Packaging defects: these can include a) poor wire bonding, resulting in open circuit input / output pins or short circuits between adjacent pins; b) poor die attach, leading to broken bonds during lifetime and overheating of the circuit;

c) damage to package (e.g. cracks), which can result in non-hermeticity giving rise to corrosion of bond wires and other circuit layers.

#### 2.2.2 Lifetime or Field Failure Defects

The term "lifetime failure" or "field failure" is used to indicate any failure that may occur in a device once it has been put into service in a system or simply stored on a shelf after purchase from a supplier. Many of the mechanisms associated with lifetime failures, such as electromigration, occur over an extended time period while others, such as electrostatic discharge damage or ESD, happen in a very short space of time. Some mechanisms are more common at the start of a component lifetime while others occur more frequently after many years of operation.

Information on the causes of field failures of integrated circuits appears only occasionally in the literature. It is often associated with specific components or environments and requires careful scrutiny to extract any general information. Many papers on the subject of reliability failure mechanisms therefore base their analysis on theoretical consideration of materials and device structures, although other papers do discuss field failure data.

One of the earliest papers with emphasis on MOS circuits is by Courtois [2.9]. The author identifies six categories of phenomena that can result in field failures of ICs. The categories are based on a classification issued by the International Council of Scientific Unions [2.10] which has not apparently been used by other workers in this field. The field failure categories identified by Courtois are:

- i) Transport phenomena or the movement of atoms, impurities or faults within a structure. This phenomena is generally referred to as electromigration and Courtois notes that the typical consequences are hillocks and voids and that step-coverage and misalignment are the primary causes;

- ii) Surface growth such as dendrites and whiskers. This is initiated by electrochemical reactions and is primarily a problem confined to devices with fusible links (such as programmable read only memory);

- iii) Dielectric breakdown. Courtois describes this as resulting from the movement of positive ions within the oxide which accumulate and hence increase the electric field locally to the point at which the intrinsic electric field breakdown threshold for the oxide is reached. The process is time and temperature dependent.

- iv) Conductor breakdown can occur due to electrical overstress and results from excess current flow which causes fusing of metal tracks. Electromigration is not-discussed by Courtois.

- v) Thermomechanical effects result from the differing thermal expansion coefficients of layers in the IC structure and cause fractures and stresses in various layers of the circuit.

- vi) External agents. Courtois groups together all extrinsic failure mechanisms and latent instrinsic failure mechanisms as external agents. These include oxide contamination and pinholes (already discussed). Extrinsic factors include radiation (causing soft errors) and vibration (causing mechanical failure of bonds and die attach). Chemical corrosion is also given as an external agent which can cause failures. This is caused by high humidity which can occur as a result of non-hermeticity of packages.

A paper by Woods [2.11] identifies four primary life-time failure mechanisms, two of which (radiation induced soft-errors and oxide breakdown) are covered by Courtois. Woods extends the category of *conductor breakdown* to include electromigration. This is an intrinsic form of defect that occurs in polycrystalline aluminium tracks and will be discussed in more detail in a later section. Woods notes that *contact electromigration* is activated by somewhat different mechanisms from track electromigration and treats it as a separate though related failure.

A new failure mechanism described by Woods is hot carrier degradation. This effect becomes more significant as device dimensions are reduced and electric fields within devices increase. It is understandable that in 1980 Courtois did not consider this effect to be significant but by 1986 hot carrier injection was generally recognised as a problem, particularly as device dimensions are scaled. Hot carrier (or more specifically hot electron) effects have been noted by many workers in the field of MOS circuit reliability. A recent book on the subject [2.12] emphasises the significance of the effect on current and future submicron MOS devices.

Woods also identifies *electrical noise* on ICs as a source of failure. The noise may originate from the circuit itself or from the external environment. Internal sources of noise include capacitive cross-coupling of signals, power supply fluctuations, radiation generated or thermal noise. External sources include electromagnetic interference and power supply noise. These factors are rarely considered in the literature. Electrostatic discharge damage, a specific case of electrical over-stress, is also noted as a source of field failure in MOS ICs.

The previous papers provide useful theoretical analysis to help to predict the probable sources of defects in CMOS IC's. An alternative source of information is field failure data which is discussed by several authors. Boulaire et al [2.13] present field failure data from ICs operating in telecommunications equipment. Three of the four mechanisms described as being of primary concern have been noted in the previous papers (Electrical over-stress and electrostatic discharge damage, electromigration and corrosion).

The new failure found from analysis of failed ICs returned from operations is the loss of program information in EPROM memory circuits. The causes of the EPROM failures are discussed in the literature (for example Crisenza [2.14]). While this thesis is concerned with failures in standard CMOS IC's, the EPROM failures do provide some relevant information. One cause of the failures in dielectric breakdown and this is noted by Hawkins and Soden [2.15] for more standard ICs. Latent defects have been identified as the dominant failure mechanism in radiation hard CMOS ICs fabricated on a particular production line.

The defects identifed by Boulaire (and by other field failure analysis such as Sinnadurai [2.16]) confirm, to a large extent, the conclusions presented by Courtois and Woods. However, the conclusions on the significance of the defects do differ. The field failure data that is presented indicates that corrosion is one of the most significant defects that gives rise to field failures. Electrical overstress is also a major concern. In the more theoretical analyses, the effects that are considered to be of primary importance are oxide breakdown, electromigration and hot electron effects. These two conclusions are not contradictory as the field failure data is, by its nature, historical (dating back to 1980 for Boulaire's earliest samples) and the effects currently being discussed in the literature become more significant with reduced device dimensions [2.11]. A further factor, as we shall see in

the next sections, is that the latter set of defects do not always cause catastrophic failures of circuits and are therefore more difficult to identify in failure analysis.

#### 2.2.3 Faults and the Electrical Effect of Production Defects.

The electrical effects of the defects identified in the previous sections are wide ranging. The defects may lead to a total malfunction of the chip or to a slight shift in a transistor parameter. The electrical effect of the defect depends on various factors: the type of defect, the extent of the defect, its physical location on the circuit and its position within the electrical configuration of the surrounding components. The electrical effect of faults has been extensively investigated and reported in the literature.

We will now consider the faults arising from each of the production defects described and the electrical effect of these faults. The defects to be considered are:

- i) Crystal defects

- ii) Particulate contamination

- iii) Surface contamination

- iv) Oxide defects

- v) Packaging defects

i) Crystal defects. These give rise to fault effects located in the device substrates. Field data on integrated circuits from a range of technologies (NMOS, CMOS, bipolar) presented in [2.1] indicate that only a small percentage (between 0 and 4%) of failures can be attributed to this kind of fault.

**Defect:** Crystallographic faults, e.g. stacking faults.

**Fault:** An accumulation of interstitial and lattice dopants in the region.

Fault effect: High substrate currents which can appear as junction leakage currents if they are located within a p-n junction.

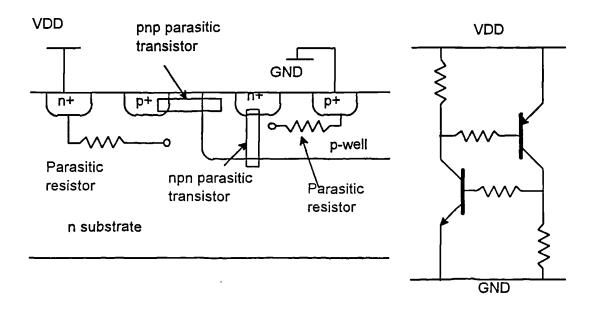

Failure: The effect of leakage is not always apparent. The most serious result is that the refresh time of dynamic circuits, and in particular memory circuits, may be significantly shortened. This can lead to a logical error if the refresh time cannot be reduced. Increased substrate current leakage can also result in an increased quiescent supply current requirement which can be a serious problem in IC's required for use in low power or standby systems. Furthermore, it is feasible that the increased substrate currents due to crystal defects may raise the substrate potential sufficiently in critical regions so that latch-up can occur.

Strack et al [2.17] have made measurements on MOS capacitor structures with oxidation induced stacking faults. These indicate an increase for the reverse saturation current for a particular p-n junction of two orders of magnitude. While the measurements were for a large area diode with a fault free current of  $10^{-10}$ A they do indicate the relative increase that might be expected in the current. From these results it can be seen that the increase in substrate current due to crystal defects, is insufficient to create a significant substrate potential where the relevant resistances are of the order of kilo-ohms.

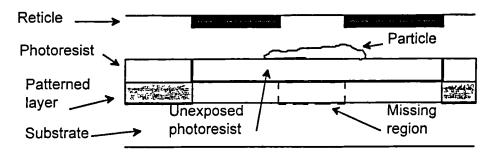

ii) Particulate contamination. The fault effects produced by particulate contamination during photolithography or layer deposition are varied. They depend on the layer or layers affected, and on the position and size of the defect with respect to device features. We will consider some examples of particulate contamination and attempt to draw some general conclusions from these.

Generally, particulate contamination during photolithography or layer deposition will result in additional or missing material. Missing material can result in an open circuit in, for example, a track in active, polysilicon or metal. For an open circuit to occur the defect must completely cross a track. Alternatively, a defect which leaves a thin section of a track remaining might result in a high series resistance in a track which would normally have a negligible resistance. The effect of this fault could be to increase an RC time constant associated with a track which will slow down the circuit response and cause a failure.

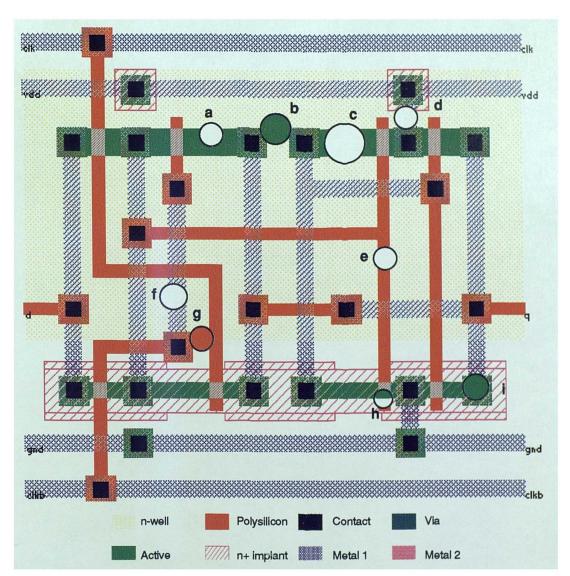

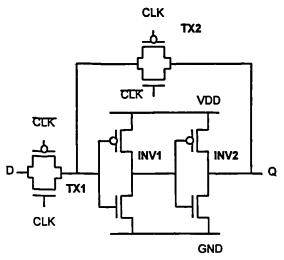

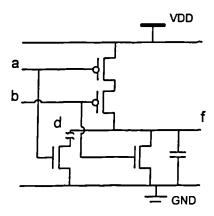

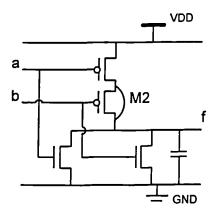

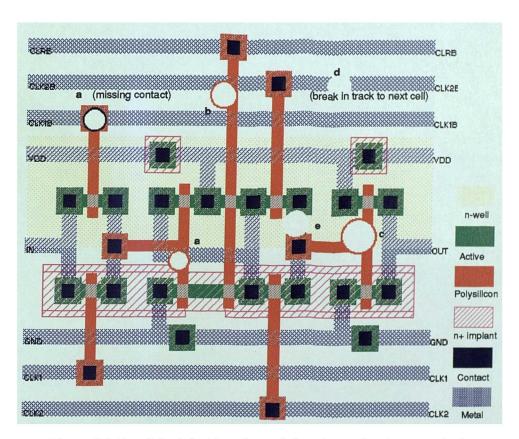

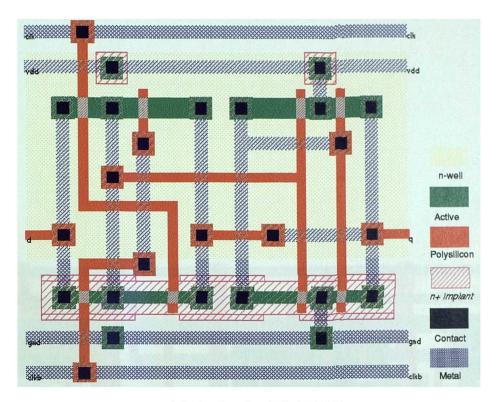

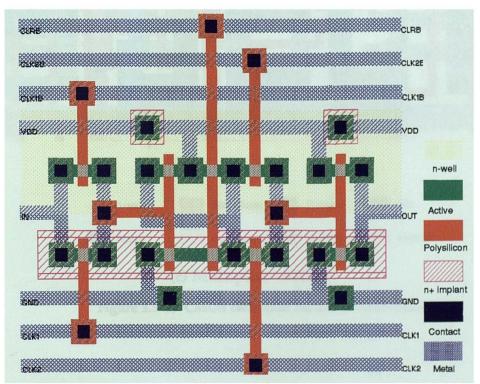

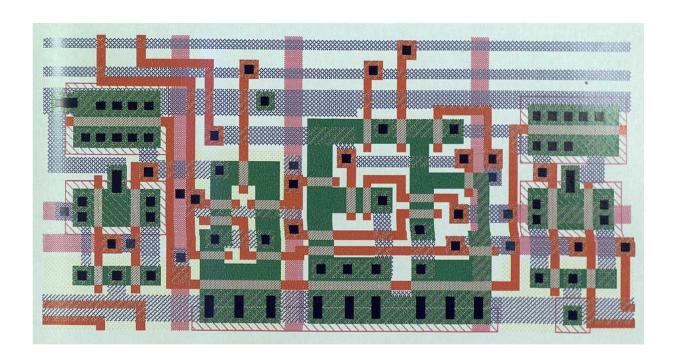

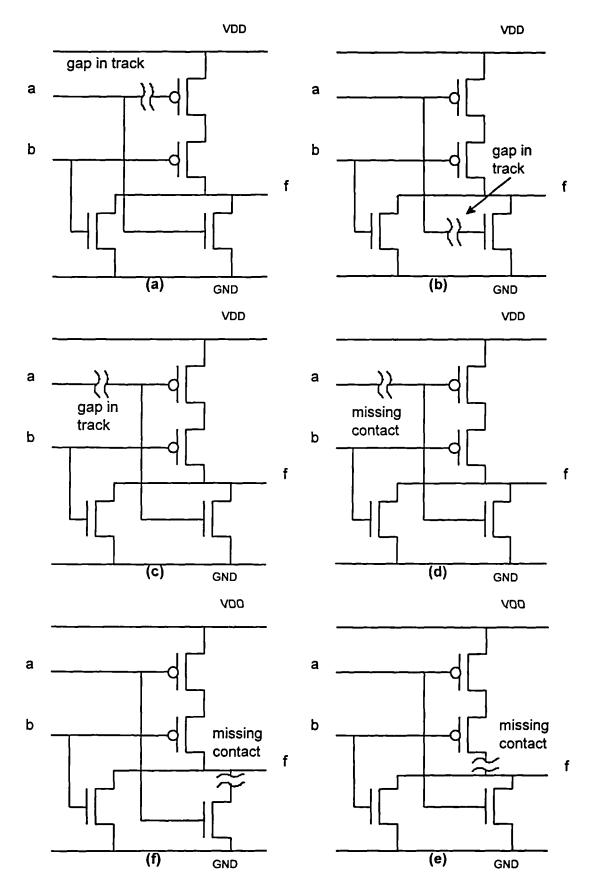

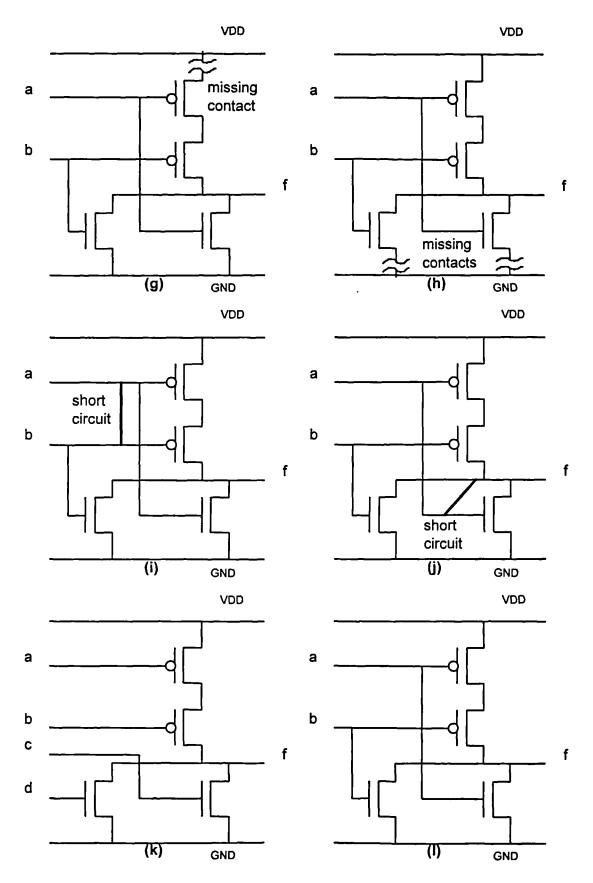

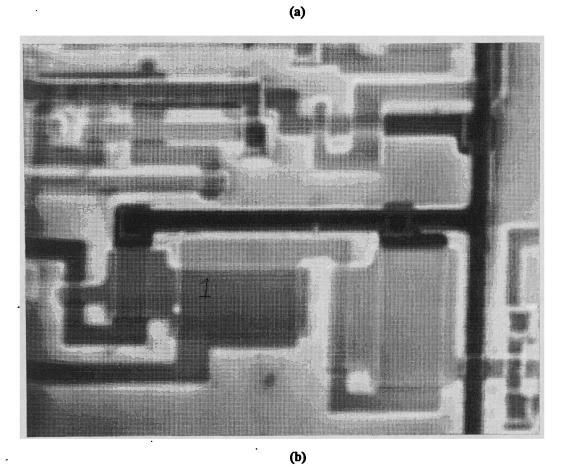

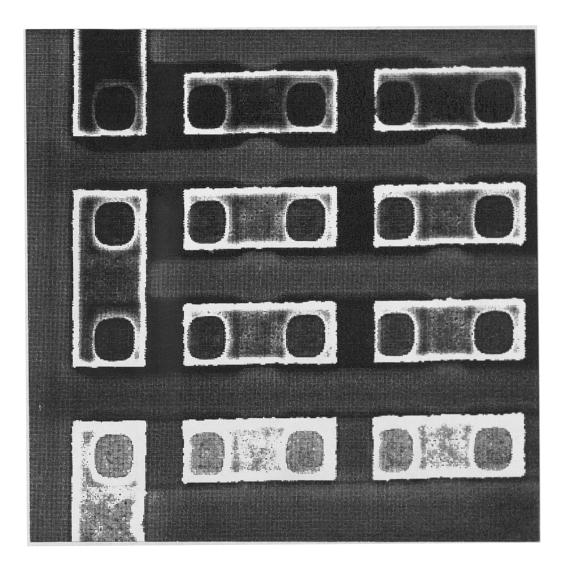

Figure 2.1 illustrates the effect of a circular particle at a few example locations on a typical CMOS cell. At this point we only wish to illustrate the range of possible defects that may arise. More detailed analysis of particulate contamination is discussed in Chapter 3. The cell used for the current analysis is a transparent D-latch circuit fabricated in a 1.5 µm n-well technology. The circuit of the cell is shown in figure 2.2. A D-type has been chosen as it is representative of many cells that occur on a typical IC. Also, it is more complex in its operation than a simple logic gate and illustrates some of the subtle effects that can occur. The choice of circular particles is quite arbitrary but serves to illustrate the effect of particulate contamination on CMOS circuits and devices.

Figure 2.1 Particulate contamination of a D-latch cell

Figure 2.2 The D-latch circuit

The failures caused by the defects labelled (a) to (i) on Figure 2.1 are now described in order to show the wide range of effects that may occur.

(a) **Defect:** Narrowing of active track.

Fault: High resistance in drain/source of p-channel transistor in TX2 (transmission gate 2)

Fault effect: There is little effect on the circuit operation even if the fault becomes an open-circuit. In this case the fault makes the input of INV1 (inverter 1) dynamic for the voltage range  $V_{DD}$  to  $V_{DD}$  -  $V_{Tn}$  (where  $V_{Tn}$  is the *n*-channel threshold voltage) because the transmission gate acts as a simple *n*-channel pass transistor with its inherent  $V_{Tn}$  drop when  $V_{DS} = V_{GS}$ . Therefore the input of INV1 is not driven in the voltage range  $V_{DD}$  to  $V_{DD}$  -  $V_{Tn}$  and hence the circuit is acting dynamically. This would not be a problem under normal operating conditions, for even if the inverter input voltage decayed to  $V_{DD}$  -  $V_{Tn}$  the *n*-channel device in TX2 would switch on to prevent further discharging ensuring that a logic 1 appears at the input to INV1 as required.

Failure: No failure occurs.

(b) **Defect:** Additional active region causing bridge between two areas.

Fault: Low resistance path between input and output of INV2.

Fault effect: The output high voltage for the latch will be less than  $V_{DD}$  and the output low voltage will be greater than 0V. If the inverters are designed for symmetric operation (same rise and fall propagation delays) then the output voltage would be close to  $V_{DD}/2$  in both cases. The actual output voltage would be determined by the relative resistances of the bridging resistance and the device channels.

Failure: A timing failure may occur if the bistable is in a critical path. If the resistance of the bridge is sufficiently low, the output may appear to be stuck at logic 0 or logic 1.

(c) **Defect:** Missing active region causing break in a track.

**Fault:** Open circuit in the drain of the *p*-channel transistor in INV2.

Fault effect: The Q output of the latch cannot be charged to  $V_{DD}$  through the p-channel device. However, TX2 provides a possible path for charge sharing from the input of INV1. The output high voltage for Q will be less than  $V_{DD}$  but may be sufficient to appear as a logic 1.

Failure: Possible logic fault at the latch output - may appear to be stuck at logic 0.

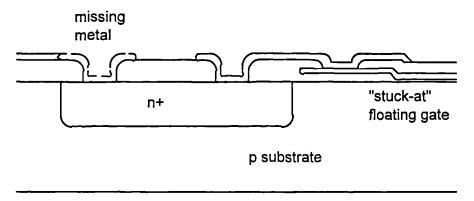

(d) **Defect:** Missing metal causing a break in a track.

**Fault:** Open circuit in the  $V_{DD}$  supply to the inverters.

Fault effect: The latch output cannot be charged to logic 1. Charge sharing may occur as described for defect (c).

Failure: Possible logic fault at the latch output - may appear to be stuck at logic 0.

(e) **Defect:** Missing polysilicon causing a break in a track.

Fault: Unconnected gate of *n*-channel transistor in INV1

**Fault effect:** Unknown gate voltage and conductance of *n*-channel transistor.

Failure: The transistor may be in a conducting or non-conducting state. Capacitive coupling from adjacent tracks or circuit nodes may cause gate potential to vary. Failure mode is difficult to predict.

(f) **Defect:** Missing metal causing break in a track.

**Fault:** Open circuit in the gate terminal of the p-channel transistor in TX2.

Fault effect: The gate terminal is unconnected resulting in an indeterminate conductivity for the device. The transistor may remain open circuit resulting in the extreme case described for defect (a).

Failure: No failure occurs.

(g) Defect: Extra polysilicon causing bridge between two tracks.

Fault: Low resistance path between the CLK and CLKB (the inverted clock signal).

Fault effect: The CLK and CLKB signals will be at the same potential of approximately  $V_{DD}/2$  resulting in both transmission gates being permanently on.

Failure: The latch will be permanently transparent with the CLK signal appearing to be stuck at logic 1.

(h) **Defect:** Missing polysilicon resulting in shortened gate track.

Fault: Drain-source short circuit on the *n*-channel transistor of INV1.

Fault effect: Low resistance of the drain-source region will prevent the output high voltage from reaching  $V_{DD}$ . The extent of the degradation will depend on the width of the short circuit region.

**Failure:** The latch output may be stuck at logic 1.

(i) **Defect:** Missing contact cut.

**Fault:** Drain connection missing on the *n*-channel device of INV2.

Fault effect: When the INV2 output should discharge to 0V it will only do so through charge sharing with the INV1 input node through TX2. It is likely that the latch output node will have a larger capacitance than the INV1 input and therefore the output will stay close to  $V_{DD}$ .

**Failure:** The output will possibly be stuck at 1.

The faults that have been described are a random selection, but illustrate the wide range of fault effects and failures that can arise from "simple" particulate contamination. The defects all affected a single layer and yet the same defect in two locations can produce very different failures. Even if the faults produced by the defects are the same, the resulting failures can be very different. Consider, for example, defects (a) and (c). An extreme case of (a) causes an open circuit in the drain of the TX2 p-channel transistor, the same fault as (c), but in a different device. In the case of defect (a) no failure is detected by electrical testing. For defect (c) the fault may be detected by a functional failure as the output appears to be stuck at logic 0 irrespective of the D input value.

From this example it is clear that an analysis of the effect of particle defects on circuit performance cannot be undertaken without considering the topology of the circuits concerned.

This, however, is a time consuming task. To reduce the complexity of the problem, the failures caused by defects can be abstracted to simpler "fault models" which represent the electrical effect of a defect.

From the above brief discussion, it is apparent that the effectiveness of simple models in describing failures must be questioned, as the situation is by no means simple. This is the main subject of this thesis and will be discussed in depth in later sections.

*iii)* Surface contamination. The defects that arise from surface contamination will tend to be specific to a process line. They will primarily depend on the cleaning and layer removal processes that are used. Some examples are given below.

(a) **Defect:** Regions of chemical residue on the wafer surface.

Fault: Poor adhesion of photoresist or deposited layers.

Fault Effect: Missing or extra material within or between features on a layer. The faults effects are therefore very similar to those arising from particulate contamination.

**Failure:** As for particulate contamination.

(b) **Defect:** Poor layer removal, for example, metal oxides in contact windows.

Fault: High resistance or rectifying contacts.

Fault effects: Increase in contact resistance, possibly for only one direction of current flow. If this occurs in a signal line, one of the signal transitions (rising or falling) may be more significantly affected than the other, leading to a timing defect on one signal transition.

**Failure:** Possible timing failure if the contact resistance is high enough.

iv) Oxide defects. Imperfections in oxide layers can take several forms resulting in low resistance paths, ionic contamination and layer thickness variations. The fault effects caused by oxide defects are often parametric rather than logical. The various forms of defect will now be discussed.

(a) **Defect:** "Pin-hole" in gate oxide over channel.

Fault: Low resistance path from gate to channel. The resistance may be terminated by a junction diode in the channel region due to dopant diffusing from the polysilicon gate. The formation of the diode will depend on the doping received by the substrate and the polysilicon which may or may not be of the same type.

Fault effect: The effect of this fault depends on the position of the defect with respect to the drain and source, and on the resistance of the conducting path between channel and gate. The first parameter will determine whether the gate potential is

more strongly influenced by the drain or source potential. The resistance of the short will determine the strength of the interaction of drain/source and gate potential. For example, if the defect creates a very low resistance path close to the drain end of the channel then the gate potential will be close to the drain potential when a channel exists. This assumes that the impedance of the source driving the gate (i.e. another logic gate) is high compared to the resistance of the short. A similar effect will occur if the defect is close to the source. If the resistance of the oxide short is high then the channel potential at the defect location will have less effect on the gate voltage.

In most circuit configurations the fault will introduce negative feedback into a logic circuit. The effect of negative feedback generally in logic circuits is to induce "weak" output voltages for logic levels. The effect depends on the strength of the feedback, but it does not necessarily result in logical errors or even timing errors.

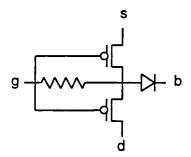

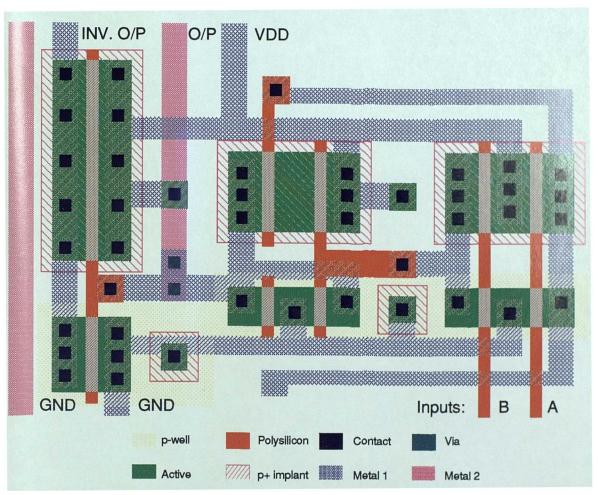

SPICE simulations have been performed using a simple model of a gate oxide short as shown in Figure 2.3. Results show that even for negligible resistance of the gate oxide short (as these defects are often called), the worst case feedback only results in weak logic levels that are restored to full strength after two subsequent gates. From these results it can be seen that pin hole defects in gate oxide do not generally result in significant fault effects. Gate oxide shorts have been modelled in detail by Syrzycki [2.18]. The sophisticated model used in this work confirms the results obtained using the simple model shown in Figure 2.3.

Dimensions of the devices can be varied to alter the position of the short in the channel. The resistance of the short can also be changed.

Figure 2.3 A model for a p-channel device with gate oxide short used in SPICE simulations.

A further effect of this form of defect is also noted by Syrzycki. The quiescent power supply current to circuits containing gate oxide shorts is significantly increased above the normal leakage current. Two paths exist for this current:

- i) current flow between the supply rails (not noted by Syrzycki) due to negative feedback to the gate that will cause both n- and p-channel networks of the faulty logic gate to be conducting for one input state (i.e. logic 0 or logic 1);

- ii) current flow from the defective device channel, through the gate oxide short to the gate of the driving logic circuit and hence to the appropriate supply rail through the driving gate network.

Raised quiescent supply current is also reported by Hawkins and Soden [2.19] although more in the context of reliability failures. The increased current can be of the order of 100  $\mu A$  or more and so is significant in the operation of low power CMOS circuits.

Failure: Excess quiescent power supply current for some input conditions. Timing errors may occur if logic gates are in critical delay paths.

(b) Defect: Pin hole in gate oxide over source or drain overlap region.

**Fault:** Low resistance path from gate to drain or source. The resistance may be terminated with a junction diode as for defects over the channel.

Fault effect: The effect is similar to that described for the pin hole defect located over the channel region, the main difference being that the channel does not have to be present for the negative feedback to occur. The strength of the feedback is again determined by the resistance of the gate oxide short.

**Failure:** Timing failures may occur. The quiescent power supply current will be increased for some input conditions.

(c) **Defect:** Ionic contamination in gate and thick oxides. This form of defect is generally thought to be insignificant but is still reported as the source of failures in recent papers (for example [2.1]).

Fault: Ionic contamination will cause a shift in the threshold voltage of a device from the required value if the contamination occurs in gate oxide. Contamination in field oxide can result in parasitic MOS transistor formation.

Fault effect: Threshold voltage variation will cause devices to switch at different gate voltages resulting in changes in propagation delays for logic gates. Transistors may also be conducting when required to be off causing excess current flow.

Failure: Timing failures may occur if threshold voltage shifts are significant. Also excess quiescent power supply current will flow for some input combinations.

(d) **Defect:** Gate oxide thickness variations.

Fault: MOS transistor threshold variation.

Fault effect: Effects are as for ionic contamination in gate oxide.

Failure: Timing failures possible and increased quiescent power supply current may occur for some input combinations.

v) Packaging defects. Packaging defects arise as a result of production errors and should be detected by the many test procedures that are executed before an IC leaves the production plant. They generally give rise to gross faults which have a catastrophic effect on circuit performance. The defects can be categorised as follows.

(a) **Defect:** Poor wire bonding.

Fault: Signal or power supply bond wire open circuit, high resistance or short circuited to nearby circuits.

Fault effect: Output signals may be missing and input signals ignored.

**Failure:** Incorrect operation of circuit, possibly stuck-at 0 or 1 on faulty inputs. Power supply faults will cause the complete circuit to fail.

(b) **Defect:** Poor die attach.

Fault: The die may move in the package.

**Fault effect:** Broken bond wires which can cause open or short circuits as described above.

Failure: As for poor wire bonding.

(c) **Defect:** Package damage, for example cracks.

Fault: Mechanical stress in the die, broken bond wires or pins and also to non-hermeticity.

Fault effect: Mechanical stress in the die can effect electrical performance of the semiconductor and broken bond wires and pins result in the failures previously described. Non-hermeticity is not generally detected until devices have been in operation in the field for some time.

Failure: Normally gross failure of the circuit, possibly after some considerable delay.

The detection of the defects discussed in this section depends to a large extent on the testing procedures and the fault models that are used to generate and assess the tests. Fault models will be discussed in detail in Section 2.3.

#### 2.2.4 The Electrical Effects of Field Failure Defects

The defects to be considered in this section are:

i) Electrical overstress;

- ii) Electrostatic discharge damage;

- iii) Corrosion

- iv) Electromigration

- v) Gate oxide shorts

- vi) Hot carrier effects

The first two are often characterised as *extrinsic* failures, the latter four as *intrinsic* failures. The defects which give rise to extrinsic failures are external to the IC and so will not be described in the following discussion.

- i) Electrical overstress. (EOS) This title encompasses a wide range of conditions, each of which may be transient or continuous. The most common of these will now be described.

- (a) Fault: Excess supply voltage.

Fault effect: The effects produced depend on the strength and duration of the event. They include latch-up, increased electric fields in devices and increased supply currents.

Failure: Power supply tracks or bond wires may fuse causing total failure of the circuit. Failure due to electromigration is more likely due to increased currents. Threshold voltage shifts, caused by charge injection into the oxide, may cause increases in propagation delays and hence timing failures. However, increased supply voltage will tend to decrease propagation delays, possibly reducing the above effect.

(b) Fault: Excess input voltage.

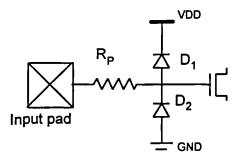

**Fault effect:** The effect of overstress on signal inputs depends on the *input* protection structures that are present. A simple circuit commonly used for CMOS ICs is shown in figure 2.4.

Figure 2.4 Typical input protection circuit for CMOS ICs

Most input protection circuits that are used on CMOS ICs operate by clamping the input voltage ( $D_1$  and  $D_2$ ) and limiting the input current ( $R_p$ ). With such circuits present, the effect of excess input voltages either as transient pulses, or static levels

are minimised. The maximum voltage that can appear on the gate of the input transistor is  $V_{DD} + V_F$  where  $V_F$  is the forward diode drop (typically 0.6V). A 0.6V overstress on the gate of an MOS transistor will not normally cause any undesirable effects. Other protection circuits would have a similar effect on the stress.

If the electrical overstress on a protected input is severe, the protection diodes may suffer damage resulting in a short circuit across the junction.

Failure: Possible stuck-at 0 or 1 faults if the input protection devices are damaged.

(c) Fault: Output short to the supply rails.

Fault effect: The output transistors will pass excessive current.

Failure: Fusing of power supply tracks or of the bond wire may occur if the output driver is of sufficiently low output impedance. In such cases, the output will appear to be stuck at the logic value corresponding to the remaining power supply rail.

ii) Electrostatic discharge (ESD) damage. This can be distinguished from electrical overstress by two factors: i) EOS is generally used to describe modest stresses which may be encountered by incorrect connection, power supply noise or other events that generate a few volts of noise. For ESD the over voltage stress is generally over 100V; ii) EOS may be a transient or static phenomenon, ESD is a purely transient effect. ESD occurs when a static charge is suddenly deposited onto the gate of an MOS transistor. The accumulated charge may be generated by the human body or by equipment.

Fault: A very high voltage pulse, in the range of hundreds to tens of thousands of volts, is applied to a signal input. Extremely high electric fields (of up to  $10^{12} \text{ Vm}^{-1}$ )/are produced across the gate oxide.

Fault effect: The effect of ESD on a CMOS circuit input depends on the strength of the discharge event. Events which develop a gate voltage of more than 20V are potentially hazardous for a gate oxide thickness of 25nm, as the intrinsic breakdown field strength for SiO<sub>2</sub> (8x10<sup>8</sup> Vm<sup>-1</sup>) is exceeded at this voltage. Oxide breakdown by this means results in a conductive path from the gate electrode to the source, drain or substrate of the device.

The effect of a gate oxide short is to increase the input current significantly and also possibly to induce timing or logical errors depending on the severity of the short as described in section 2.2.3.

Failure: Input may be stuck at logic 0 or 1. Increased propagation delays may occur on input stages.

*corrosion.* This may affect individual tracks or large regions of a circuit. The defect may be precipitated by external agents, such as moisture, or may be a purely instrinsic phenomenon. Some examples are given.

**Defect:** Electrochemical reaction catalysed by impurities such as chlorine in passivation layers resulting in corrosion, or the interaction of gold and aluminium at wire bonds [2.20]. Phosphorus may also lead to corrosion of aluminium, which is unfortunate, as it is present in phosphosilicate glass which is used as a passivation layer.

Fault: Open circuits and high resistance in aluminium tracks and at bond pads. The fault is equally likely to occur in signal and power supply tracks.

Fault effect: Increased signal propagation and open circuit faults.

**Failure:** Timing faults, signals stuck at logic 0 or 1.

*iv)* Atomic transport phenomena. There are a number of mechanisms which result in atomic transport. The most important occur in metal tracks.

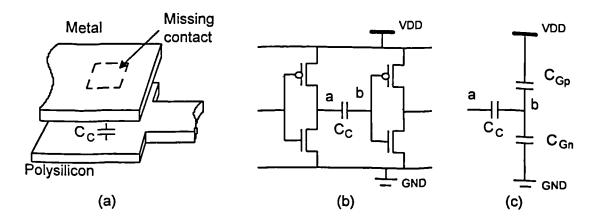

**Defect:** The most commonly discussed transport phenomena is *electromigration*. This is the movement of atoms in conductors resulting from momentum transfer from electron flow [2.21]. A similar defect is stress migration which is the movement of atoms in conductors due to a stress gradient in the track. Contact migration is caused by concentration gradients of different materials at interface regions which produce a diffusion of atoms to reduce such gradients. This effect occurs in aluminium to silicon contacts where aluminium can migrate into silicon and vice versa.

Fault: Voids or hillocks in tracks producing open circuits and possibly short circuits. Contact migration may result in the formation of rectifying contacts [2.22].

Fault effect: Voids in tracks generally act as an open circuit. It has been demonstrated [2.23] that tunnelling conduction can occur across such voids. The current flow in such cases is insufficient to maintain correct operation of the circuit at normal operating frequencies. However, this can affect the operation of "floating" nodes as will be shown later. The effect of the open circuit will depend on its location and the function of the track that is affected.

The effect of an open circuit in a signal track is generally assumed to cause the circuit node being driven to, remain at a logic level (either 0 or 1). This is an unrealistic representation of the effect of the failure and one of the main aims of this thesis is to establish theoretically and experimentally the effect of open circuit defects in signal lines.

**Failure:** Timing failures, floating nodes and signals stuck at logic 0 or 1.

the drain, source or substrate (channel) of an MOS transistor. The production sources of this defect and its electrical effect were discussed in detail in earlier sections. The defect was also considered in the current section, where it arises as a result of electrical overstress or ESD. A further cause of gate oxide shorts is a gradual wearout mechanism generally referred to as time dependent dielectric breakdown (TDDB). This is the mechanism described by Courtois [2.9]. Anolick and Nelson [2.24] have demonstrated both electric field and temperature dependence of this phenomenon. Further studies [2.25, 2.26] have shown it to be an intrinsic breakdown mechanism resulting from Fowler-Nordheim tunnelling of carriers into the gate oxide. The effect of the fault has been described in section 2.2.3.

vi) Hot carrier effects. Degradation of MOS transistors due to the generation of hot carriers has only recently become a significant phenomenon. Despite the considerable literature on the subject at the time (for example Hess and Sah, 1974 [2.27], Ning et al., 1977 [2.28] and Hu, 1979 [2.29]) Courtois did not recognise the effect and it has not been identified explicitly in other field failure data studies. There are two probable reasons for this: i) the devices being analysed date from before 1980 and up to 1985. Most CMOS devices at this time were not susceptible to hot carrier effects due to the relatively low electric fields present in the device channel; ii) the effects of hot carriers on device performance may be attributable to other causes making identification difficult. However, as device dimensions have been reduced, hot carrier effects have been recognised as a potentially dominant failure mechanism and have received considerable attention in the literature (for example Eitan and Frohman-Bentchkowsky [2.30], Tam et al [2.31], Hsu and Tam, [2.32]). Despite the lack of field failure data for this mechanism, the effect has been studied both experimentally and theoretically from around 1982 (for example Takeda et al [2.33], Katto et al, [2.34]).

Hot carriers are generated in the inversion and pinch off regions of MOS transistors under the influence of high lateral electric fields. Under such conditions, the energy of electrons and holes is greater than would generally be expected - such carriers are referred to as *hot* carriers. These can degrade devices in several ways.

(a) Fault: Impact ionisation in the inversion layer or pinch off region of an MOST can create electron-hole pairs.

Fault effect: Holes are swept into the substrate under the influence of the device electric fields and constitute a substrate current.

Failure: Increased power consumption.

(b) Fault: Photons may be generated by electron-hole recombination, or by Brehmstralung from high energy electrons.

Fault effect: Re-absorption of photons in the charge storage region of dynamic RAM circuits can cause loss of charge.

Failure: Transient or intermittent logical failure of such devices.

(c) Fault: Hot carriers may enter the gate oxide by tunnelling or surmounting the Si-SiO<sub>2</sub> potential barrier.

Fault effect: Gate oxide breakdown or threshold voltage shifts.

Failure: Failures associated with gate oxide breakdown as previously described. Also parametric failures such as degradation of transistor transconductance resulting in timing failures. The consequences of parametric shifts and other effects resulting from hot electron injection are discussed in the literature, for example Aur et al [2.35], Pimbley [2.36], but precise details will depend on circuit configurations.

#### 2.2.5 Summary of Failure Mechanisms

We have seen that a wide range of defects can arise in CMOS integrated circuits and that the electrical effect of such faults can range from insignificant to total chip failure. Some production defects are latent, resulting in lifetime failures. Others, while being a significant departure from the designed structure, have little, if any, effect on circuit performance.

Field failure defects may cause parametric shifts to occur, for example, threshold voltage shifts due to hot electron injection, resulting in intermittent faults. Alternatively, complete failure of the circuit may occur in a very short time as in the case of electrical overstress or electrostatic discharge damage.

The complex physical nature of IC defects and the often subtle electrical effects that are produced require abstraction to a high degree to enable the efficient design of tests for their detection. This is the purpose of *fault models* which will now be discussed in relation to the defects identified in this section.

## 2.3 Fault Models

The aim of fault models is to simplify the wide range of effects that arise from the large number of possible defects in integrated circuits. This allows test generation to become a practical task instead of the time consuming procedure that would result from detailed physical analysis of all possible defects in a circuit, and their consequences. As shown in the previous section, the physical mechanisms that produce defects, and their subsequent electrical effect are very wide ranging. To derive a test for a defect based on the physical processes of its evolution would be immensely time consuming because of the large amount of detail involved. It is therefore necessary to abstract the fault to a simple electrical effect that can be detected by simple observation of, for example, the logic levels at the output pins of the circuit under test.

Ideally, a fault model should encompass many physical defects. This allows a test generation methodology based on the model to be applied to many faults. In fact, the dominant techniques for test generation do not consider defects at all. They simply aim to establish that fault effects, represented by models of defects, can be identified if present. This has the advantage that the physical analysis of defects can be ignored thus greatly simplifying the test generation procedure.

The disadvantage of this methodology is that information is lost by the high level of abstraction. Consequently, a test failure does not identify or locate the defect that is present, but simply notes that one (or more) of a wide range of possible defects is present. Generally this information is sufficient however and the detailed failure analysis is left to specialists if required. In production testing it is sufficient to know that a chip has a fault and must be discarded.

Throughout this discussion of faults and fault models, we will only consider the case of a single fault in the circuit. Multiple fault detection and test generation is not considered, as it is generally thought to be an intractable problem. The number of possible multiple stuck-at faults (this term is explained in the next section) in an n node circuit is  $3^n - 1$ . Even for modest circuits this number of faults cannot be considered as the test generation process would simply take too long and be too complex. For example, a circuit containing 40 nodes has more than  $10^{19}$  possible multiple fault conditions. The assumption that only single fault occurs will therefore be used in this discussion and throughout the thesis.

## 2.3.1 Classical Fault Models

The most commonly used fault models for digital systems are the stuck-at 0 and stuckat 1 models. In these, defects are abstracted to the logic level. All detectable faults are assumed to cause an output or input to be stuck at the appropriate logic level for all input combinations. The model is used to generate tests in the following way.

To test for a circuit node being stuck-at 0, for example, the inputs are set to establish a logic 1 on the node. If, when the test is applied, the node does not adopt its fault free value (logic 0) then a defect is present which is causing the node to be stuck at logic 0.

Each node in a circuit has two possible fault conditions: stuck-at 0 or stuck-at 1. Both inputs and outputs of logic gates are tested for the fault and so for an m input logic gate there are 2(m+1) faults to test for; for example, a three-input NAND gate has eight possible fault conditions. This is considerably smaller than the total number of possible defects that could arise in the circuit. The reduction is achieved because of the high level of abstraction of the failure modes.

In fact it is unnecessary to generate individual tests for each of the fault conditions possible. The complete set of faults can be *collapsed* to a minimal set which still covers the complete set while requiring fewer tests. Consider a three input NAND gate with inputs a, b, c and output f. The faults aSO (a stuck-at 0), bSO, cSO and fSI (f stuck-at 1) are said to be equivalent because, if any of these faults are present the output will be at logic 0, the fault conditions cannot be distinguished. This will occur because if any input of a NAND gate is at logic 0 the output will be logic 1. A single test can therefore be used to detect all of these faults simultaneously. For the NAND gate the only possible test vector for these faults is (abcf) = (1110) (i.e. all inputs set to logic 1 and the fault free output is logic 0).

Of the remaining faults only aSI, bSI and cSI need to be tested because each of these dominates the fault fSO. For example, the only test for aSI is (abcf) = (0111). This test will cause the output to be at logic 1 if the fault aSI is not present and so the test will also cover fSO. The same argument applies to the b and c inputs. The faults, however, are not equivalent because there are three possible tests for fSO (i.e. (abcf) = (0111) or (1011) or (1101)) and selecting any one of these to cover fSO will only cover one other fault, not all three. A sufficient set of tests for the three-input NAND gate are shown in Table 2.3

| Test: abcf | Faults covered                   |

|------------|----------------------------------|

| 1110       | aS0, bS0, cS0, fS1               |

| 0111       | aS1, fS0<br>bS1, fS0<br>cS1, fS0 |

| 1011       | bS1, fS0                         |

| 1101       | cS1, fS0                         |

Table 2.3 Fault coverage for a two input NAND gate

Based on the stuck-at model, the tests for a NAND gate are simple to generate and apply. The compression of testing in this way can be extrapolated to complete chips and this to a large extent explains the popularity of the stuck-at fault model. We should however investigate how thorough this reduced testing is on a real circuit.

The adequacy of the stuck-at fault model has been investigated by many workers in this field, for example Wadsack [2.37], Al-Arian [2.5], Abraham [2.38], Banerjee and Abraham [2.7], Galiay et al [2.6], Hayes [2.39]. The analysis is generally performed by introducing faults at the electrical level i.e. into a transistor level circuit diagram. Simulation or analysis is then used to show that certain defects do not produce a stuck-at node on input or output. The papers listed above do not take the analysis to the point at which the percentage of faults that are not covered by the tests generated using the stuck-at model, can be determined. They simply identify some defects that are not detected and then concentrate on establishing a fault model for those cases.

To perform the quantitative analysis suggested, two further stages of refinement are required. A distribution of defects must be determined and these must be introduced randomly into the *physical layout* of the circuit. A study of this kind has been reported by Shen et al [2.40] in which a technique called Inductive Fault Analysis is described. The technique is used to investigate the effect of circular defects of varying diameter on the lithography of integrated circuits. These effects are then translated into circuit behaviour. The technique has only been applied to photolithography defects and so the results cannot necessarily be extrapolated to the host of defects which were identified in the previous section. However, the paper presents some interesting results which will now be summarised.

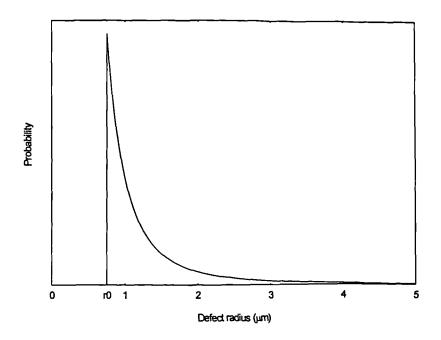

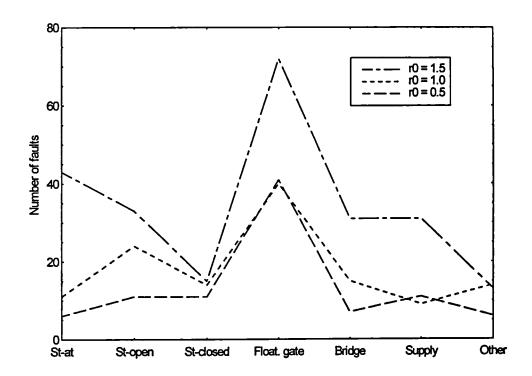

The defect size density distribution (often misleadingly called the *defect density distribution*) that is used for the analysis is described in a paper by Maly, [2.41], and is based on production line data reported by Stapper [2.42]. Clearly some caution is needed here as the precise form of the defect size probability density function is dependent on local conditions in a cleanroom. However, other publications on the subject (for example [2.43]) show an approximate  $1/d^3$  (where d is the defect diameter) form for the distribution function which can be modified to fit most production line data that has been published. (The probability density function actually consists of two regimes: a linearly increasing region from d = 0 to  $d_0$  and the  $1/d^3$  region for  $d > d_0$ . The parameter  $d_0$  varies with production lines but is always smaller that the smallest feature size.)

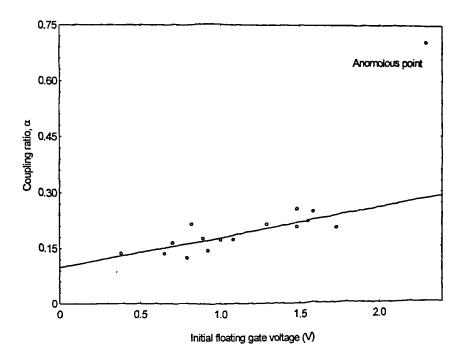

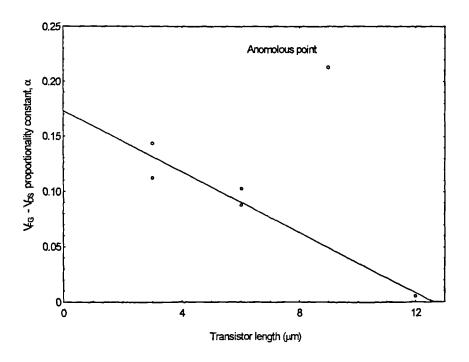

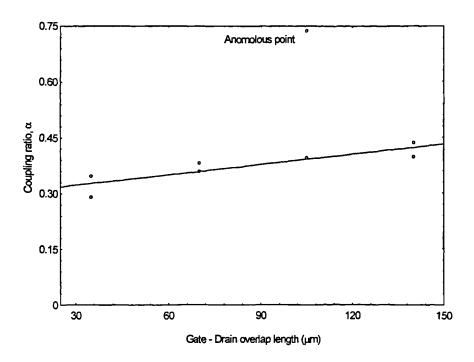

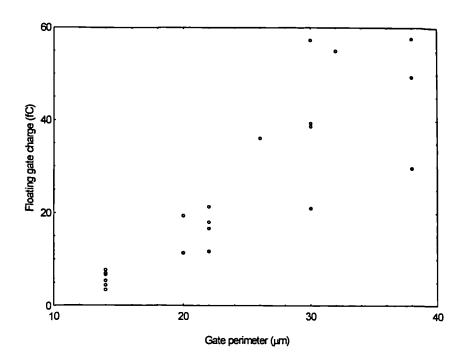

Shen considered defects to be generated according to the distribution function and scattered randomly over the metal, contact, polysilicon and active layers of a simple nMOS circuit containing 29 transistors. It was assumed that a defect may add material to a layer or remove it. In the simulation reported, only 10% of the 4800 physical defects that were