# Radim HERCIK<sup>1</sup>, Roman SLABY<sup>1</sup>, Zdenek MACHACEK<sup>1</sup>

VSB Technical University of Ostrava, FEECS (1)

# Image Processing for Low-power Microcontroller Application

Abstract. This paper focuses on the signal processing of the image signal from the camera system, which is applied to the low-power microcontroller. Image signal loading and processing is realized on the low-power Freescale DSP56F805, which is combination of the digital signal processor and the controller. There are described data and control signals connected from the digital camera and connection to specified pins of the digital signal processor. The number of scanning images per second depends on the clock signal frequency that is generated inside digital signal processor. The defined synchronization clock ensures correctly data capturing form the camera. An external RAM memory is necessary to use because of the insufficient size of the storage space for scanned images. There is implemented algorithm of frequency analyses for verification of low-power microcontroller capability. The amplitude and phase frequency spectrum of the scanned image signal is obtained by 2D FFT (Fast Fourier Transform) application. The amplitude frequency spectrum contains information about colors and the phase frequency spectrum contains information about colors and the phase frequency spectrum contains information about colors and transitions in the analyzed image. Key parameters and elements of the image can be analyzed by frequency spectra results. Mainly it is important for the classification and sorting of image data. The programming implementation is realized in CodeWarrior programming environment with the ProcessorExpert tool using, which are supplied by Freescale Company.

Streszczenie. Artykuł ten skupia się na przetwarzaniu obrazu z systemu kamer zaimplementowanym w mikrokontrolerze niskiej mocy. Ładowanie i przetwarzanie obrazu jest realizowane na mikrokontrolerze Freescale DSP56F805, który jest połączeniem przetwornika sygnału cyfrowego i kontrolera. Opisany został sposób w jaki dane i sygnały sterujące z aparatu cyfrowego są podłączone do określonych pinów cyfrowego przetwornika sygnału. Programowanie odbywa się w środowisku CodeWarrior z narzędziami wykorzystującymi ProcessorExpert, dostarczanymi przez firmę Freescale. (Przetwarzanie obrazu z systemu kamer zaimplementowanym w mikrokontrolerze niskiej mocy)

**Keywords**: Low-power Microcontroller, Image Processing, Digital Signal Processor, Fast Fourier Transform, Frequency Spectrum. **Słowa kluczowe**: Mikrokontroler Niskiej Mocy, Przetwarzanie Obrazu, Procesor Sygnału Cyfrowego, Szybka Transformata Fouriera, Widmo Częstotliwości.

#### Introduction

The methods and principles of digital video signal loading and processing by low-power microcontrollers are described. The application is presented by the digital signal processor, which is not primarily applicable for video image processing, because of its low-level parameters. The application is tested by calculation of the FFT algorithm implemented on the image signal. The camera microchip OV6620 is used as a source of digital video signal. Digital signal processor DSP56F805 contains 2D FFT special MAC instructions calculation, ensuring a sufficient frequency rate for instruction execution. The calculated frequency spectrum results are transmitted via RS232 communication interface to user application on the PC for visualization. The amplitude frequency spectrum contains information about the colors. The phase frequency spectrum contains information about edges and transitions in the analyzed image. The correct image processing is verified by implemented programs, which are created in CodeWarrior programming environment especially ProcessorExpert tool, ANSI C and Assembler language.

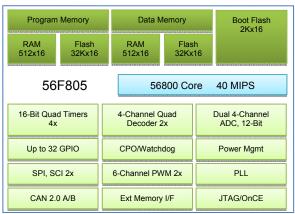

Fig.1. Block diagram DSP56F805

## Low-power digital signal processor parameters

There is chosen hybrid of microcontroller and digital signal processor Freescale DSP56F805. The programming

design is optimized for algorithms of digital video signal processing. The crystal works on the frequency of 8MHz, the processor frequency is 80MHz. It contains three cores with each core is capable process in a single clock cycle two instruction. DSP is able to perform 40 MIPS (Mega Instructions per Second).

There is possible to expand computing capabilities of the large data size by using the external data RAM memory of 32 kilobytes, which is connectable directly to the data bus and address bus of the Freescale DSP56F805.

## Video image signal loading process

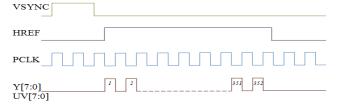

Data and control wires of the digital camera are connected to individual pins of the digital signal processor. The digital signal processor generates a clock for the camera microchip OV6620. It reads the value of the synchronization signal VSYNC (vertical sync), HREF (horizontal sync) and PCLK (pixel clock), which indicates the beginning of the relevant data output from the camera microchip. [1], [2]

Fig.2. Synchronization signals OV6620 camera chip

At the moment of the VSYNC signal detection, the digital signal processor handles specific sequence of commands in assembler with a strictly defined number of instructions so that the data port reading is exactly synchronized with the camera microchip. This method is implemented with usage of the digital signal processor synchronization clock for camera microchip synchronization. The PCLK synchronization output signal from camera is not applied, because it is substituted by presented assembler sequence code. The HREF signal from the camera defined next row of the image 2D field.

The assembler sequence code for data reading from camera and saving to RAM memory of digital signal processor is composed of necessary four instructions. Assembler sequence code for the image pixel loading is implemented [3]:

IN RG,PINC; // 1 instruction

ST Y+,RG; // 2 instruction

NOP; // 1 instruction

The camera resolution is specified by 356 pixel columns and by 292 pixel rows. Thus, the implemented code performs these four instructions 356 times in 292 cycles.

This camera is equipped by CMOS technology colored microchip. The sensor contains approximately 101,376 pixels. The white balance, exposure, gamma correction and gain can be modified by the serial interface communication. The algorithm for electronic exposure control is based on the size of the image brightness. The exposure parameter is set for good subject illumination due compare to the background in the elementary mode. Logical 1 on the RESET pin of the microchip can caused original microchip settings. This procedure invokes complete hardware reset, with all files erasing or registry factory setting. The microchip is powered by 5V. In standby mode, the sensor consumption is less than  $10\mu A,$  in active mode the maximum consumption is 80 mA. Microchip OV6620 contains an analog signal processor, two eight-bit A/D converters, I2C serial communication interface for setting the sensor registers a frequency divider. [4],[5]

## Frequency analysis transform description

There is possible to use same as for 1 dimensional signal the combination of the Fourier transform for video image 2 dimensional signal. The frequency domain of the signal is very important for detection of the various signal aspects and parameters, which are not detectable in original domain. The Fourier transform is type of integral transformation, which is usable to convert signals from time domain to the frequency domain. The transformed signal have to be periodical and satisfy the Dirichlet conditions. The original analyzed signal can be defined as continuous or discrete in time domain.

The original signal w(t) in time domain is transformed to the spectral function  $W(\omega)$  in frequency domain by Fourier transform implementation. The frequency spectrum presents the signal in frequency domain, which is realized with finite energy. The basic equation for Fast Fourier transform is defined:

(1)

$$W(\omega) = F\{w(t)\} = \int_{-\infty}^{+\infty} w(t) \cdot e^{-j\omega t} dt$$

$$\omega \in (-\infty, +\infty)$$

The inverse Fast Fourier transform is given by equation:

(2)

$$w(t) = F^{-1}\{w(t)\} = \frac{1}{2\pi} \int_{-\infty}^{\infty} W(\omega) \cdot e^{j\omega t} d\omega$$

Frequency analysis implementation for transform the image by 2D Fast Fourier Transform (FFT) can be defined by given equation:

(3)

$$2DFFT = FFT(FFT(x).').'$$

This equation presents computation of the onedimensional FFT for each row x of the image and of each column of the image. The process time for FFT computation depends on the length of the original signal. The most common Fast Fourier Transform FFT method is the Cooley–Tukey algorithm. This is a divide and conquer algorithm that recursively breaks down a DFT of any composite size  $N = N_1.N_2$  into many smaller DFTs of sizes  $N_1$  (matrix row) and  $N_2$  (matrix column), along with O(N) multiplications by complex roots of unity traditionally called twiddle factors.

This algorithm method (and the general idea of FFT) was popularized by a publication of J. W. Cooley and J. W. Tukey in 1965, but it was later discovered (Heideman & Burrus, 1984) that those two authors had independently reinvented an algorithm known to Carl Friedrich Gauss around 1805 (and subsequently rediscovered several times in limited forms).

The most well-known the Cooley–Tukey algorithm is to divide the transform into two pieces of size N/2 at each step, and is therefore limited to power-of-two sizes, but any factorization can be used in general (as was known to both Gauss and Cooley/Tukey). These are called the radix-2 and mixed-radix cases, respectively (and other variants such as the split-radix FFT have their own names as well). Although the basic idea is recursive, most traditional implementations rearrange the algorithm to avoid explicit recursion. Also, because the Cooley–Tukey algorithm breaks the DFT into smaller DFTs, it can be combined arbitrarily with any other algorithm for the DFT. [6], [7]

#### Frequency analysis of video image signal

Frequency analysis of the image is important image processing method for obtain key parameters and elements inside. The result of the analysis is the amplitude frequency spectrum and the phase frequency spectrum, which can be created from any two-dimensional image. The basic rules for results of the frequency analysis in case of the original real signal are:

- the amplitude frequency spectrum is even function

- the phase frequency spectrum is odd function

- the even signal spectrum is even real function

- the odd signal spectrum is imaginary odd function

b) Original input image 2

Fig.3. Original input image signals

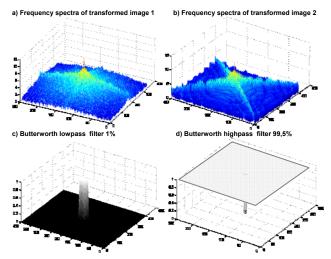

The frequency spectra of the original images are calculated by FFT2 functions in the mathematical programming environment MATLAB. The frequency spectra are calculated from the brightness component of the image (Y). FFT algorithm calculates the negative frequency band, but it is because of the symmetry of spectra and it is same as the positive frequency band. Thus there is no necessary to store this redundant information.

The result of the FFT algorithm is two-dimensional matrix 2D FFT points (for amplitude or phase frequency spectrum). Visualization frequency spectra of the transformed test images and filters characteristic of Butterworth lowpass and high pass filters are shown in Figure 4. The filters values are chosen for clear presentation of results from inverse transformed images.

Fig.4. Frequency spectra of transformed images and Butterworth lowpass and highpass filters characteristic

The result of the inverse transform, respectively the reconstruction of the amplitude or phase frequency spectra is the reconstructed image. Examples of the reconstructed images from frequency spectra with filters are shown in Figure 5, where are gained or damped sharpness edges.

Lowpass Filtering 1% signal from amplitude and phase frequency spectra of transformed image

Fig.5. Reconstructed image from frequency spectra with filters

# Time consumption of image processing

The low-power digital signal processor Freescale DSP56F805 is usable for FFT algorithm implementation because the processor includes a special data type Frac16 and Single-cycle 16×16-bit parallel Multiplier-Accumulator (MAC), thereby achieving a sufficient calculation speed. The calculation is performed with fixed point data type operation. The data structure is 16,16 format, where16-bit number is integer part, and 16-bit number is fractional part). Therefore, the complex number occupies 8 Bytes in the memory.

The calculation of FFT algorithm for one row (356 pixels) of the image signal takes approximately 125,000 cycles, which corresponds to 750,000 digital signal processor instructions. The required time for image signal reading is derived from the camera clock signal, in our case  $f_{FPS}$ =20 FPS (figures per second). The limiting parameter is the connected communication speed rate. The asynchronous serial communication is settable to the maximum bit rate  $v_T$ =115,200 kb/s, thus there is necessary

to set the divider register  $r_{div}$  , which is given by the oscillator frequency  $f_{osc}$  and by presented functional relation:

$$r_{div} = \frac{f_{osc}}{16 \cdot v_T} - 1$$

The time consumption for frequency analyses calculation (around units of milliseconds) is inconsiderable compare to the transmission channel speed which is given by the size of the image (356x292) and size of complex number occupies 8 Bytes of transmit packet

(5)

$$t = \frac{356 \cdot 292 \cdot 8}{v_T} = 7s$$

The analyses system is limited by the time of transmission channel speed rate, where for each of the FFT frequency spectra analyses result is necessary 7 second delay, what is given by presented relation.

### Verification of signal processing implementation

The verification of signal processing in the processor Freescale DSP56F805 is implemented by the visualization application in PC and the serial communication interface between PC and the processor. The specific visualization application is developed in C# for Microsoft operating systems XP/Vista/7. It is designed to visualize the input original signal in time domain and transformed signal in frequency domain. FFT algorithm for double-side frequency spectra signal processing is implemented in the digital signal processor DSP56F805. For less time consumption, the implemented application sends the only half of the frequency spectra, because of redundant and reverse data.

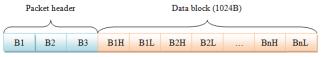

The visualization application communicates with the digital signal processor via a serial communication interface RS232. The application allows setting the basic parameters of the communication channel, such as the port name, baud rate, parity, stop bits and data. Data packets from the processor are sent as a continuous data stream. The visualization application identifies data packets recognizable by data header (bytes B1,B2,B3). The representation of signal data is connected after packet header as data stream (B1H, B1L,...).

Fig.6. Structure of communication data packet

Sampling frequency of the processor A/D converter is set on 10kHz. The input signal highest frequency of the harmonic component is at least twice smaller than the sampling frequency of the processor A/D converter, which is given by the Shannon - Kotelnik theorem.

Fig.7. Designed testing system block diagram

The designed testing system block diagram is presented in Figure 7. The signal generator is connected to the A/D converter of the digital signal processor. There is processed input signal by FFT algorithm inside the digital signal processor. The analyzed signal data are sent over the communication channel covered in form of packets to the

PC. The sent data are displayed in the designed user application.

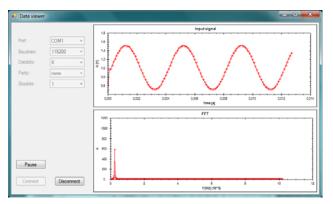

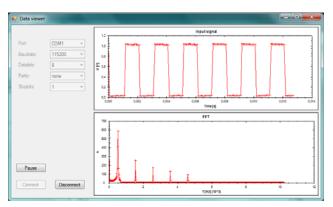

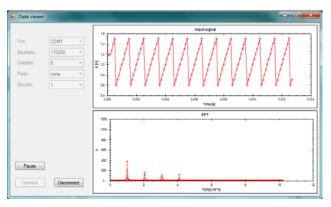

The example of the generated and analyzed signal for verification is set to amplitude value  $U_{pp}$ =1V and offset value  $U_{offset}$ =1V. The verification process was applied for different shape type of input signals and for various frequencies of the signals. The examples of the visualization application and analyses results are shown in Figures 8,9,10.

Fig.8. Result of sinusoidal input signal of frequency equal to 250Hz

Fig.9. Result of square input signal of frequency equal to 500Hz

Fig.10. Result of saw input signal of frequency equal to 1000Hz

# Conclusion

The paper is focused on the principles of loading a digital image signal from camera microchip by low-power microcontroller Freescale DSP56F805. The other main discussed issue is image signal processing by the microcontroller with example of the FFT (Fast Fourier

Transform) algorithm implementation on the image signal and results visualization.

There is explained measurement and testing function for one-dimensional FFT continuous analog signals, parallel Multiplier-Accumulator (MAC) instructions, which allows exploit the potential power of the microcontroller computing. The image signal loading is performed by synchronous clock signal from the microcontroller CLK\_OUT pin for the camera microchip timing. This process ensures time-deterministic sequence of the data stream from the camera. The loading sequence of each input image signal (356x292) is equal to  $1/f_{FPS} = 50ms$ .

The developed analyses system is able to transfer data through the RS232 communication interface of the loaded input image signal, amplitude and phase frequency spectra in time equal to 21 seconds. Time consumption of image loading and FFT analyses is proceed in less than 100 ms. The realized signal processing system is suitable for one-dimensional and two-dimensional signals processing.

Frequency analyses were applied as image signal processing examples in low-power microcontrollers, because of their wide usage in many areas and applications. For example image filters applications, where the high frequency gain in the image modifies sharpening and the high frequency suppression removes transitions and edges. The frequency analyses are also applicable in image compression methods.

#### **Acknowledgements**

The work was supported by project SP2012 /111 - Data collection and data processing of large distributed systems "

Grand – aided student R. Hercik, Municipality of Ostrava, Czech Republic

#### **REFERENCES**

- [1] Gibson J. D. Handbook of Image & Video Processing. Academic Press London, 2000. – 891 p.

- Machacek Z., Hercik R., Slaby R. Smart user adaptive system for intelligent object recognizing // Studies in Computational Intelligence – Berlin Heidelberg, 2011. – No. 351. – P.197–206.

- [3] Salomon D. A Guide to Data Compression Methods. Springer, 2002. – 304 p.

- [4] Salomon D. A Concise Introduction to Data Compression. Springer, 2008. – 314 p.

[5] Holst G., Lomhein T. CMOS/CCD Sensors and Camera

- [5] Holst G., Lomhein T. CMOS/CCD Sensors and Camera Systems. – Society of Photo Optical, 2011. – 392 p.

- [6] Krejcar O., Frischer R. Detection of Internal Defects of Material on the Basis of Performance Spectral Density Analysis. Journal of Vibroengineering. 2010 - vol. 12,- P.541-551.

- [7] Krejcar O. Problem Solving of Low Data Throughput on Mobile Devices by Artefacts Prebuffering. EURASIP Journal on Wireless Communications and Networking. 2009, 2009.

Author: Ing. Radim Hercík, VŠB - Technical university of Ostrava, Department cybernetics and biomedical engineering, 17.Listopadu 15, Ostrava Poruba, Czech Republic, E-mail: radim.hercik@vsb.cz; Ing. Zdeněk Macháček, Ph.D. VŠB - Technical university of Ostrava, Department cybernetics and biomedical engineering, 17.Listopadu 15, Ostrava Poruba, Czech Republic, E-mail: zdenek.machacek@vsb.cz; Ing. Roman Slabý, VŠB - Technical university of Ostrava, Department cybernetics and biomedical engineering, 17.Listopadu 15, Ostrava Poruba, Czech Republic, E-mail: roman.slaby@vsb.cz;