# Purdue University Purdue e-Pubs

Birck and NCN Publications

Birck Nanotechnology Center

10-1-2012

# Frequency response of LaAlO3/SrTiO3 all-oxide field-effect transistors

Qingmin Liu University of Notre Dame

Lin Dong Purdue University, Birck Nanotechnology Center, lindong@purdue.edu

Yiqun Liu Harvard University

Roy Gordon *Harvard University*

Peide D. Ye Purdue University, Birck Nanotechnology Center, yep@purdue.edu

See next page for additional authors

Follow this and additional works at: http://docs.lib.purdue.edu/nanopub Part of the <u>Nanoscience and Nanotechnology Commons</u>

Liu, Qingmin; Dong, Lin; Liu, Yiqun; Gordon, Roy; Ye, Peide D.; Fay, Patrick; and Seabaugh, Alan, "Frequency response of LaAlO3/ SrTiO3 all-oxide field-effect transistors" (2012). *Birck and NCN Publications*. Paper 890. http://docs.lib.purdue.edu/nanopub/890

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

## Authors

Qingmin Liu, Lin Dong, Yiqun Liu, Roy Gordon, Peide D. Ye, Patrick Fay, and Alan Seabaugh

Solid-State Electronics 76 (2012) 1-4

Contents lists available at SciVerse ScienceDirect

# Solid-State Electronics

journal homepage: www.elsevier.com/locate/sse

# Frequency response of LaAlO<sub>3</sub>/SrTiO<sub>3</sub> all-oxide field-effect transistors

Qingmin Liu<sup>a</sup>, Lin Dong<sup>b</sup>, Yiqun Liu<sup>c</sup>, Roy Gordon<sup>c</sup>, Peide D. Ye<sup>b</sup>, Patrick Fay<sup>a</sup>, Alan Seabaugh<sup>a,\*</sup>

<sup>a</sup> Department of Electrical Engineering, University of Notre Dame, Notre Dame, IN 46556, USA

<sup>b</sup> School of Electrical and Computer Engineering and Birck Nanotechnology Center, Purdue University, West Lafayette, IN 47906, USA

<sup>c</sup> Department of Chemistry and Chemical Biology, Harvard University, Cambridge, MA 02138, USA

#### ARTICLE INFO

Article history: Received 5 January 2012 Received in revised form 13 May 2012 Accepted 18 May 2012 Available online 1 July 2012

The review of this paper was arranged by S. Cristoloveanu

Keywords: Field-effect transistor Heterojunction Lanthanum aluminate Strontium titanate

### 1. Introduction

Since Ohtomo and Hwang reported a high-mobility two-dimensional electron gas (2DEG) can be formed at the crystalline LaAlO<sub>3</sub>/ SrTiO<sub>3</sub> heterointerface in 2004 [1], this 2DEG has received increasing attention [2–7]. Dong et al. demonstrated the first all-oxide FETs based on modulation of the 2DEG at the interface of amorphous LaAlO<sub>3</sub> and crystalline SrTiO<sub>3</sub> [8,9]. These reported transistors showed an on-current of 10  $\mu$ A/ $\mu$ m with an on-off ratio around 1000, and exhibited gate leakage below 10 fA/ $\mu$ m<sup>2</sup>. The room temperature mobility was estimated to be approximately 4 cm<sup>2</sup>/Vs [9], which can be expected to limit the speed of these transistors. However, until now no direct measurements of the frequency response of all-oxide FETs have been reported. The application space for all-oxide transistors is still to be determined.

## 2. Experiment

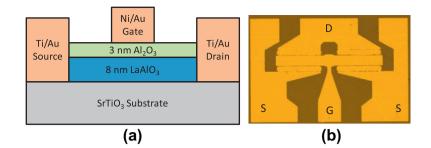

The measured LaAlO<sub>3</sub>/SrTiO<sub>3</sub> FETs in this paper incorporated a 3 nm Al<sub>2</sub>O<sub>3</sub> capping layer on top of 8 nm LaAlO<sub>3</sub>, both of which were deposited by atomic layer deposition (ALD) on a crystalline SrTiO<sub>3</sub> substrate. The schematic cross section and a microscope image of the transistor is shown in Fig. 1. The details of the fabrication process are reported in [9]. Three sets of devices fabricated using

## ABSTRACT

The frequency response of all oxide field-effect transistors with amorphous LaAlO<sub>3</sub> on a crystalline SrTiO<sub>3</sub> substrate is reported. The intrinsic cut-off frequencies of 4  $\mu$ m gate-length devices are found to be approximately 17 MHz indicating that with gate length scaling gigahertz cut-off frequency is possible. The low cut-off frequency is primarily limited by the low effective mobility. The estimated effective mobility value determined from the S-parameter measurement is 3.8 cm<sup>2</sup>/Vs, which is consistent with previous reports. Small-signal equivalent circuit model parameters are extracted by fitting to on-wafer measured S-parameters. Good agreement is obtained between measured and simulated S-parameters based on the equivalent circuit model.

© 2012 Elsevier Ltd. All rights reserved.

slightly different LaAlO<sub>3</sub> deposition conditions were characterized. Sample A was initiated with La in the first cycle of an 8 nm LaAlO<sub>3</sub> film; sample B was the same except the first cycle was Al; and in sample C the SrTiO<sub>3</sub> substrate was annealed in O<sub>2</sub> at 1000 °C for 10 min prior to the La-first-cycle 8 nm LaAlO<sub>3</sub> deposition.

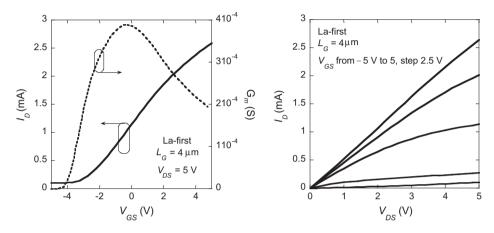

The frequency response of the transistors was characterized by on-wafer S-parameter measurements using 150- $\mu$ m pitch groundsignal-ground (GSG) coplanar probes. The S-parameters were measured from 30 kHz to 30 MHz using an Agilent 8753E vector network analyzer. An open-short-load-through calibration was performed using a CS-5 calibration substrate from GGB Industries to establish reference planes at the probe tips. The dc bias was supplied by an Agilent 4155C semiconductor parameter analyzer connected through network analyzer bias tees. Current voltage (*I–V*) measurements were performed through the GSG probes on the same S-parameter test structure. Measured common source characteristics are shown in Fig. 2. The dc *I–V* characteristics are similar to those reported in [9].

#### 3. Results and discussion

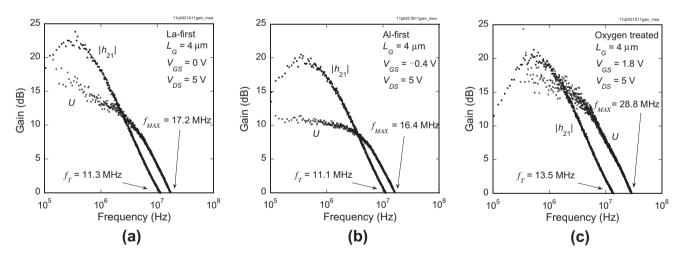

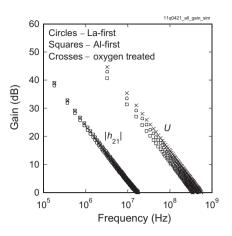

The current gain,  $h_{21}$ , and the unilateral power gain, U, of typical 4 µm gate length transistors for each of the three LaAlO<sub>3</sub>/SrTiO<sub>3</sub> interface conditions is shown in Fig. 3, where all transistors are biased at their peak current gain cut-off frequency,  $f_T$ . Relatively modest differences are observed for the frequency response among these three samples, with the oxygen-treated sample performing

<sup>\*</sup> Corresponding author. Tel.: +1 5746314473; fax: +1 5746314393. *E-mail address:* Seabaugh.1@nd.edu (A. Seabaugh).

<sup>0038-1101/\$ -</sup> see front matter © 2012 Elsevier Ltd. All rights reserved. http://dx.doi.org/10.1016/j.sse.2012.05.044

Fig. 1. (a) Schematic cross section and (b) a microscope image of the LaAlO<sub>3</sub>/SrTiO<sub>3</sub> all-oxide FET.

Fig. 2. Measured (a) drain current vs. gate-source voltage, I<sub>D</sub>-V<sub>CS</sub>, and (b) drain current vs. drain-source voltage, I<sub>D</sub>-V<sub>DS</sub>, for a representative LaAlO<sub>3</sub>/SrTiO<sub>3</sub> FET.

Fig. 3. Small-signal RF performance of the transistors with 4-µm gate length on three samples: (a) La-first, (b) Al-first, and (c) oxygen treated.

slightly better than either of the un-annealed samples. The low cut-off frequency and maximum oscillation frequency of the transistors is primary due to the low effective channel mobility, which leads to low transconductance,  $g_m$ , and high source and drain access resistances.

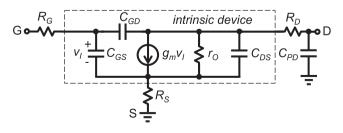

In order to investigate the transistors' intrinsic frequency response, a small-signal equivalent circuit model was constructed and the extrinsic parasitics were extracted following the procedure outlined in [10]. The small-signal equivalent circuit model is shown in Fig. 4; in this conventional transistor model,  $R_G$ ,  $R_S$ , and  $R_D$  represent the gate, source, and drain resistances, and  $C_{GS}$ ,  $C_{GD}$ , and  $C_{DS}$  represent the gate-source, gate-drain, and drain-source capacitances.  $r_O$  is the small-signal output resistance. The

Fig. 4. Small-signal equivalent circuit of the all-oxide FET.

voltage-controlled current source is expressed in terms of the transconductance,  $g_m$ , and the voltage  $V_1$  appearing across the

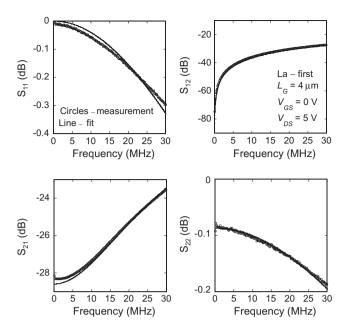

Fig. 5. Comparison of measured (line) and simulated (circles) S-parameters showing quality of fit.

intrinsic gate-source capacitance. The capacitance  $C_{PD}$  represents the parasitic capacitance of the contact pads. The extracted parameter values of a typical transistor on sample A (La-first) are  $R_G \approx 0 \Omega$ ,  $R_S = R_D = 643.5 \Omega$ ,  $C_{CS} = 4.34$  pF,  $C_{CD} = 2.24$  pF,  $g_m = 592$  $\mu$ S,  $r_O = 6.29$  k $\Omega$ , and  $C_{PD} = 1.31$  pF; similar values were obtained for devices on the other two samples. A parasitic drain-to-source capacitance in the picofarad range is needed to account for the excess capacitance associated with the drain pad in these non-isolated devices. A similar value of parasitic capacitance was also measured in an open-circuit coplanar structure on each sample, indicating that this is a layout-induced parasitic and is not related to the intrinsic device structure.

Good agreement between measured S-parameters and the equivalent circuit model fits was obtained for all the transistors on three samples. Fig. 5 shows a typical example for a typical transistor on sample A; as can be seen, the frequency response of all of the S-parameters tracks closely the model behavior. The extracted transconductance from the small-signal equivalent circuit was compared to the derivative of the measured dc I-V curve. Good agreement between the small signal equivalent circuit model extraction and the dc measurement supported the validity of the equivalent circuit model. For example, for the three samples A, B, and C, the measured transconductance from S-parameter measurements was 0.37, 0.35, and 0.30 mS, while the transconductance from dc measurements at the same bias condition was 0.39, 0.40, and 0.35 mS.

The extracted source resistance and drain resistance are between 120 and 180 k $\Omega$ -µm at a gate width of 200 µm and the gate-source/drain spacing of 1 µm for all three samples. This extracted resistance can be accounted for by the high sheet resistance in the 2DEG, which is estimated to be in the range of 120–180 k $\Omega$ / sq, and is close to the reported values in [9]. In general, it is challenging to minimize parasitic resistance in all-oxide transistors.

By mathematically removing the effects of the extrinsic resistances,  $R_G$ ,  $R_S$ , and  $R_D$ , and capacitance,  $C_{PD}$ , the intrinsic device RF performance can be projected, as shown in Fig. 6. The maximum frequency of oscillation,  $f_{max}$ , increases by a factor of ~20, due to significantly reducing the output *RC* time constant with estimated values of 13–15 ns for the three samples. The cut-off frequency, on the other hand, does not increase as much because it is limited

**Fig. 6.** Calculated the intrinsic RF performance of the transistors based on the small-signal equivalent circuit in Fig. 3 on three samples. Sample A: La-first (circles); sample B: Al-first (squares); and sample C: oxygen treated (crosses).

primarily by the low effective mobility with estimated values of  $4-6 \text{ cm}^2/\text{Vs}$  and the long channels. With scaling the channel length below 50 nm, we may expect the cut-off frequency over 1 GHz.

To estimate the effective mobility, we employ a first-order approximation. Assuming the transistor is biased in the triode region and the charge and the electric field are uniformly distributed in the channel, the drain current can be estimated as  $I_D = Qv/L = Q\mu E/L = Q\mu [V_{DS} - I_D (R_S + R_D)]/L^2$ , where Q is the total charge in the channel, v is the velocity, L is the gate length, and  $\mu$  is the effective mobility. The charge Q can be estimated by the ac measurement as  $Q = C_G V_{GS}$ , where  $C_G$  is the total gate capacitance. Therefore the effective mobility can be estimated as  $\mu = I_D L^2 / \{ C_G V_{GS} [ V_{DS} - I_D \ (R_S + R_D) ] \}.$  The effective mobility of the transistor on sample A (La-first) is estimated to be 3.8 cm<sup>2</sup>/Vs, which is consistent to the previous reported value of 3.9 cm<sup>2</sup>/Vs in [3]. Similar results are obtained on the other structures, with 3.8 and 5.6  $\text{cm}^2/\text{Vs}$  for sample B and C, respectively. The effective mobility can also be extracted based on the Y-function,  $Y = I_D / \sqrt{g_m}$ , or peak transconductance after Ghibaudo [11]. The extracted mobilities based on these two techniques for all three wafers are in the range of  $2-4 \text{ cm}^2/\text{Vs}$ , with good agreement between extraction methods.

From the mobility and sheet resistance, the charge density in the 2DEG can be estimated as  $N = 1/q\mu R_{SH}$ , where  $R_{SH}$  represents the sheet resistance of the 2DEG and can be extracted from transmission line measurements. As an example, the extracted sheet resistance on sample A (La-first) is approximately 117 k $\Omega$ /sq, which is close to the reported value of 140 k $\Omega$ /sq in [9]. Therefore, the charge density is estimated to be  $1.4 \times 10^{13}$  cm<sup>-2</sup>.

#### 4. Conclusion

The frequency response of the LaAlO<sub>3</sub>/SrTiO<sub>3</sub> all-oxide FETs is measured for the first time. The extracted parameters from the small-signal equivalent circuit are consistent with the dc characteristics. The effective mobility extracted from the ac measurements is also consistent with the dc measurements and confirms a value of approximately 4 cm<sup>2</sup>/Vs. The intrinsic cut-off frequencies on 4 µm gate-length devices are found to be approximately 17 MHz indicating that with gate length scaling gigahertz cut-off frequency is possible in all-oxide transistors.

#### Acknowledgements

This work was supported by the Semiconductor Research Corporation's Nanoelectronics Research Initiative and National Institute of Standard & Technology through the Midwest Institute for Nanoelectronics Discovery (MIND).

[5] Susaki T, Makishima A, Hosono H. Work function engineering via LaAlO<sub>3</sub>/ SrTiO<sub>3</sub> polar interfaces. Phys Rev 2011;84:115456.

#### References

- Ohtomo A, Hwang HY. A high-mobility electron gas at the LaAlO<sub>3</sub>/SrTiO<sub>3</sub> heterointerface. Nature 2004;427:423–6.

- [2] Brinkman A, Huijben M, Van Zalk M, Huijben J, Zeitler U, Maan JC, et al. Magnetic effects at the interface between non-magnetic oxides. Nature Mat 2007;6:493-6.

- [3] Park JW, Bogorin DF, Cen C, Felker DA, Zhang Y, Nelson CT, et al. Creation of a two-dimensional electron gas at an oxide interface on silicon. Nature Com 2010;1:1–6.

- [4] Singh-Bhalla G, Bell C, Ravichandran J, Siemons W, Hikita Y, Salahuddin S, et al. Built-in and induced polarization across LaAlO<sub>3</sub>/SrTiO<sub>3</sub> heterojunctions. Nature Phys 2011;7:80–6.

- [6] Chambers SA. Understanding the mechanism of conductivity at the LaAlO<sub>3</sub>/ SrTiO<sub>3</sub> (0 0 1) interface. Surf Sci 2011;605:1133-40.

- [7] Schlom DG, Mannhart J. Interface takes charge over Si. Nature Mat 2011;10:168–9.

- [8] Dong L, Xu M, Liu YQ, Wu YQ, Colby R, Stach EA, et al. All oxide field-effect transistors formed at atomic-layer-deposited LaAlO<sub>3</sub>/SrTiO<sub>3</sub> interface. DRC Tech Dig 2010:29–30.

- [9] Dong L, Liu YQ, Xu M, Wu YQ, Colby R, Stach EA, et al. Atomic-layerdeposited LaAlO<sub>3</sub>/SrTiO<sub>3</sub> all oxide field-effect transistors. IEDM Tech Dig 2010:588–91.

- [10] Dambrine G, Cappy A, Heliodore F, Playez E. A new method for determining the FET small-signal equivalent circuit. IEEE Trans Microw Theory Tech 1988;36:1151–9.

- [11] Ghibaudo G. New method for the extraction of MOSFET parameters. Electron Lett 1988;24:543–5.