© 2012 Adam Clay Faust

#### ANALOG AND MIXED-SIGNAL CIRCUITRY FOR SYSTEM-ASSISTED HIGH-SPEED I/O LINKS

BY

#### ADAM CLAY FAUST

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2012

Urbana, Illinois

Doctoral Committee:

Professor Elyse Rosenbaum, Chair Professor Milton Feng Professor Naresh Shanbhag Professor José Schutt-Ainé

# ABSTRACT

The state-of-the-art design methodology for high-speed I/O links is to specify component-level design requirements to achieve high-fidelity component-level performance. While designing each component in the link with high fidelity guarantees a reliable link, it does not inherently optimize the link for metrics such as the power, design complexity, or bit error rate performance. Recently, due to the increased demand for data bandwidth in backplane I/O, a system-assisted design methodology has been developed to optimize the system for a given set of metrics. By optimizing on the system level rather than the component level, the performance at the component level can be reduced from high quality to sufficient when the component is deployed within the I/O link. The new system-level design methodology encourages the utilization of novel circuit architectures. In this dissertation, novel analog and mixed-signal circuitry for system-assisted high-speed I/O links is presented. The novel circuitry expands upon traditional analog and mixed-signal circuit architectures in order to achieve system-level design goals and requirements without significant power or area overhead. To my family and friends

# ACKNOWLEDGMENTS

When I look back at the student I was upon entering graduate school and compare to the student I have become, I am astounded at the change. Along the path, I have been aided by so many, and I thank all who have been there for me. At this time, I would like to thank a few individuals who have had a significant impact on my studies.

I would like to thank my adviser, Professor Elyse Rosenbaum. Next, I would like to thank Professor Shanbhag for his dedicated involvement in the system-assisted mixed-signal (SAMS) project which I have been fortunate to participate in. For their friendship and assistance through the years, I would like to thank my colleagues Dr. Karan Bhatia, Dr. James Di Sarro, Dr. Farzan Farbiz, Dr. Nicholas Olson, Ankit Srivastava, Jeffrey Lee, Nathan Jack, Vrashank Shukla, Arjun Kripanidhi, Min-Sun Keel, Nick Thomson, Kuo-Hsuan Meng, Robert Mertens, Dr. Rajan Narasimha, Chhay Kong, Yingyan Lin, Pavle Milosevic, Wen-Yi Chen, and Dr. Richard Tseng. I would especially like to thank Karan and Ankit for guiding me through my first two years of learning how to design analog circuits. I would like to thank Dr. Hyeon-Min Bae and Jonathan Ashbrook for donating their time and sharing their industrial experience.

Thank you to the Semiconductor Research Corporation, Texas Instruments, the Department of Electrical and Computer Engineering, and the Micron Foundation for their financial support during my studies. Thank you to NVIDIA, Micron Technologies, Advanced Micro Devices, and Texas Instruments for hosting me for summer internships.

# **TABLE OF CONTENTS**

| CHAPT | ER 1 HIGH-SPEED I/O BACKGROUND                                  | 1  |

|-------|-----------------------------------------------------------------|----|

| 1.1   | Motivation for High-Speed I/O                                   | 1  |

| 1.2   | Serial I/O Links                                                | 1  |

| 1.3   | NRZ Signal Power Spectral Density                               | 2  |

| 1.4   | Backplane Transmission Lines                                    | 3  |

| 1.5   | ESD Protection                                                  | 8  |

| 1.5   | .1 Circuits                                                     | 8  |

| 1.5   | .2 ESD Protection Event Standards and Testing                   | 9  |

| 1.6   | Intersymbol Interference and Equalization                       | 10 |

| 1.7   | Signal Integrity and Eye Diagrams                               | 12 |

| CHAPT | ER 2 SYSTEM-ASSISTED I/O DESIGN STUDIES                         | 14 |

| 2.1   | Introduction                                                    | 14 |

| 2.2   | Objectives                                                      | 14 |

| 2.3   | Receiver Input Bandwidth Extension                              | 15 |

| 2.4   | Receive Sampling via Variable-Reference ADC                     | 16 |

| 2.5   | Backplane High-Speed I/O Utilizing Coding                       | 17 |

| CHAPT | ER 3 TRANSMITTER AND RECEIVER BANDWIDTH ESTIMATION              | 19 |

| 3.1   | Introduction                                                    | 19 |

| 3.2   | Transmitter Schematic and Lumped Element Model                  | 19 |

| 3.3   | Receiver Schematics and Lumped Element Models                   | 21 |

| 3.4   | Bandwidth Estimation Method                                     | 23 |

| 3.5   | Receiver Bandwidth Estimation                                   | 25 |

| 3.5   | .1 First-Order Bandwidth Derivation                             | 25 |

| 3.5   | .2 Second-Order Bandwidth Derivation                            | 25 |

| 3.5   | .3 Bandwidth Estimation Method                                  | 27 |

| 3.5   | .4 Bandwidth Simulations                                        | 29 |

| 3.5   | .5 Analysis of the Estimated Bandwidth                          | 31 |

| 3.6   | Optimization of Receiver Secondary Protection Circuits          | 32 |

| 3.7   | Transmitter Output Bandwidth Estimation                         | 33 |

| 3.8   | Generalized Bandwidth Estimation Method                         | 34 |

| 3.9   | Estimating Bandwidth Extension of Negative Capacitance Circuits | 34 |

| CHAPT | ER 4 RECEIVER INPUT ROOT LOCUS ANALYSIS                         | 36 |

| 4.1   | Introduction                                                    | 36 |

| 4.2    | Receiver Lumped Element Model                              |    |

|--------|------------------------------------------------------------|----|

| 4.3    | Receiver Input Transfer Function                           |    |

| 4.3.1  | Transfer Function Derivation                               |    |

| 4.3.2  | 2 Transfer Function Coefficient Derivations                |    |

| 4.4    | Receiver Input Root Locus                                  |    |

| 4.4.1  | Root Locus Double Root Proof                               |    |

| 4.4.2  | 2 Root Locus Circle Proof                                  |    |

| 4.5    | Maximum –3 dB Bandwidth                                    |    |

| 4.5.1  | Exact and Maximum –3 dB Bandwidth Derivation               |    |

| 4.5.2  | 2 Evaluation of Bandwidth Estimation Method                |    |

| 4.6    | Optimal Capacitance for High-Speed Serial I/O              |    |

| 4.6.1  | Filter Capacitance Derivation                              |    |

| 4.7    | Parasitic Capacitance Budget for High-Speed I/O            |    |

| 4.8    | Parasitic Inductance Budget for High-Speed I/O             |    |

| 4.9    | Transmitter Output Root Locus                              | 50 |

| CHAPTE | R 5 NEGATIVE CAPACITANCE CIRCUITS                          |    |

| 5.1    | Introduction                                               |    |

| 5.2    | Test Chip Overview and Measurement Methodology             |    |

| 5.3    | Basic Receiver Front-End                                   | 55 |

| 5.3.1  | Circuit                                                    | 55 |

| 5.3.2  | 2 Signal Integrity Results                                 |    |

| 5.3.3  | ESD Resiliency Results                                     |    |

| 5.4    | Bandwidth Extension Circuits                               | 59 |

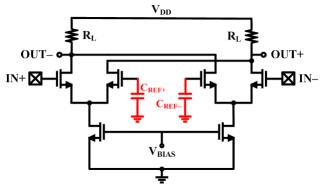

| 5.4.1  | Negative Capacitance Circuits                              | 59 |

| 5.4.2  | 2 Traditional Negative Capacitance Circuit                 |    |

| 5.4.3  | G <sub>m</sub> -Boosted Negative Capacitance Circuit       |    |

| 5.4.4  | Test Chip Negative Capacitance Circuits                    |    |

| 5.5    | Negative Capacitance Circuit ESD Analysis                  |    |

| 5.6    | Receiver Input with Negative Capacitance Root Locus        |    |

| 5.6.1  | Receiver Input with Negative Capacitance Model             |    |

| 5.6.2  | Receiver Input with Negative Capacitance Transfer Function |    |

| 5.6.3  | Receiver Input with Negative Capacitance Root Locus        |    |

| 5.6.4  | Impact of <i>C<sub>NEG</sub></i> on Receiver Input Poles   |    |

| 5.6.5  | 5 Impact of Parasitic Inductance on Receiver Input Poles   |    |

| 5.6.6   | Impact of $g_m$ on Receiver Input Poles                            |     |

|---------|--------------------------------------------------------------------|-----|

| 5.6.7   | G <sub>m</sub> -Boosted Negative Capacitance Root Locus            | 77  |

| 5.7 Ba  | andwidth Extension Circuit Measurement Results                     |     |

| 5.7.1   | Signal Integrity Results                                           | 78  |

| 5.7.2   | ESD Resiliency Results                                             | 80  |

| 5.8 No  | egative Capacitance Circuit Design Considerations                  | 81  |

| 5.8.1   | Utilizing Negative Capacitance Circuits                            | 81  |

| 5.8.2   | Utilizing the G <sub>m</sub> -Boosted Negative Capacitance Circuit | 82  |

| CHAPTER | 6 SINGLE-CORE MULTIPLE-OUTPUT PASSIVE DAC                          | 85  |

| 6.1 In  | troduction                                                         | 85  |

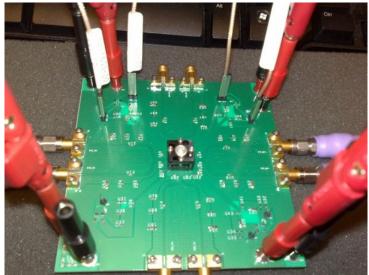

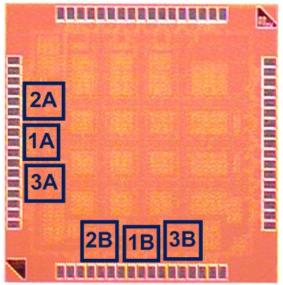

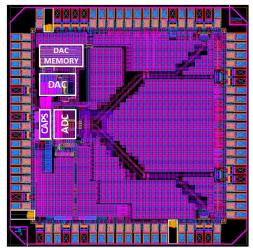

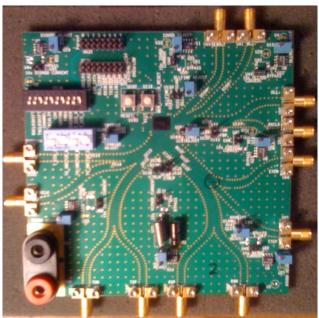

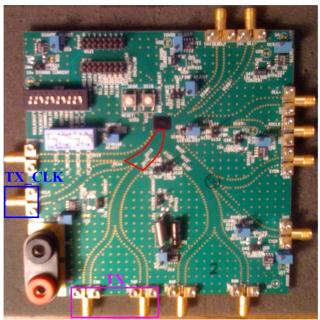

| 6.2 Te  | est Chip and Test Board                                            | 86  |

| 6.2.1   | Test Chip and Test Board Overview                                  | 86  |

| 6.2.2   | Test Chip Architecture and Circuits                                | 87  |

| 6.3 D.  | AC Design Requirements                                             | 88  |

| 6.4 D.  | AC Design Concept                                                  | 90  |

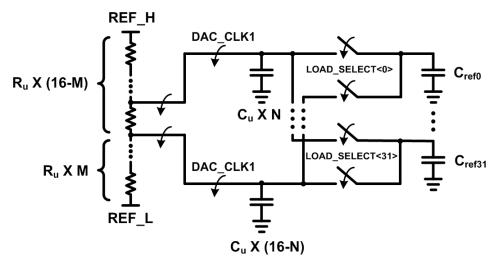

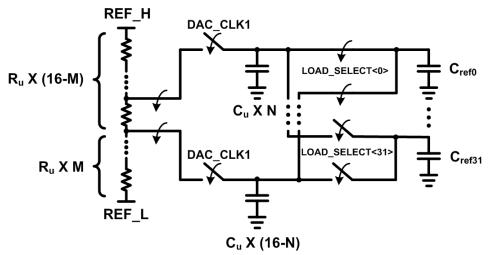

| 6.4.1   | Capacitor Storage of Voltage References                            | 90  |

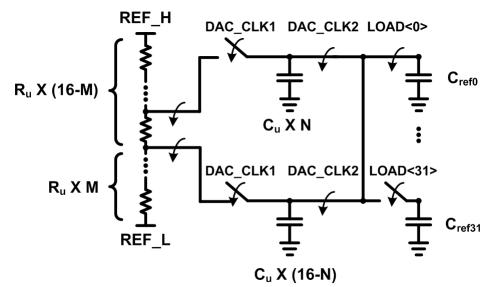

| 6.4.2   | DAC Operation                                                      | 91  |

| 6.4.3   | Low-Area DAC Operation                                             | 93  |

| 6.5 D.  | AC Architecture and Circuits                                       | 95  |

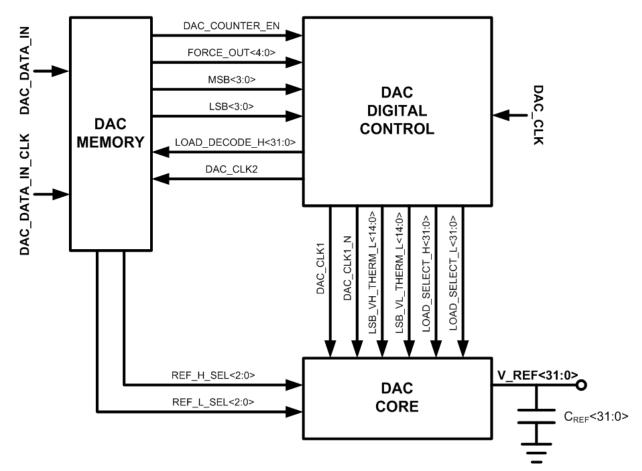

| 6.5.1   | DAC Architecture                                                   | 95  |

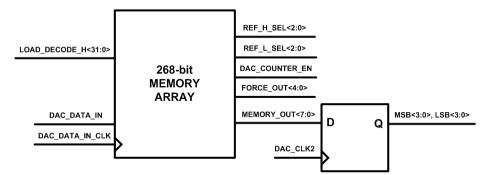

| 6.5.2   | DAC Memory                                                         | 96  |

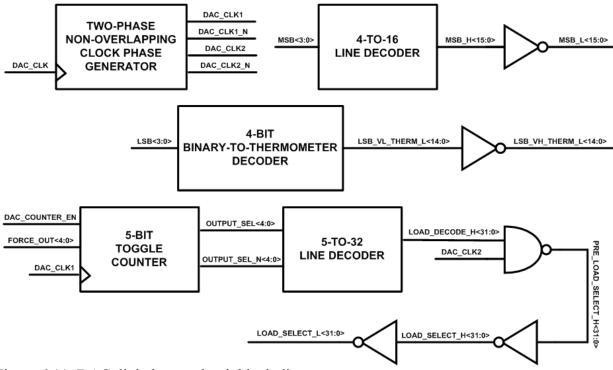

| 6.5.3   | DAC Digital Control                                                | 97  |

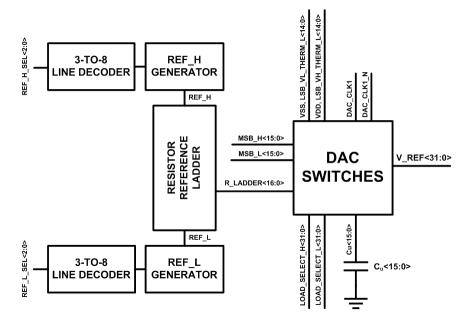

| 6.5.4   | DAC Core                                                           | 99  |

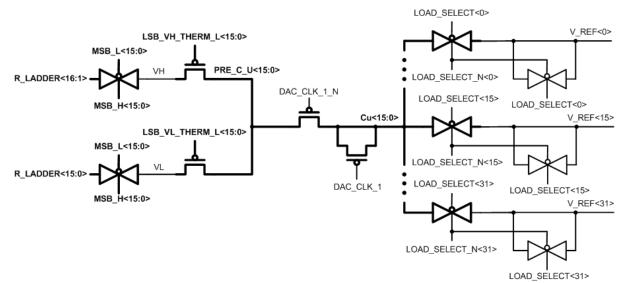

| 6.5.5   | DAC Switches                                                       | 100 |

| 6.6 D.  | AC Simulation Results                                              | 101 |

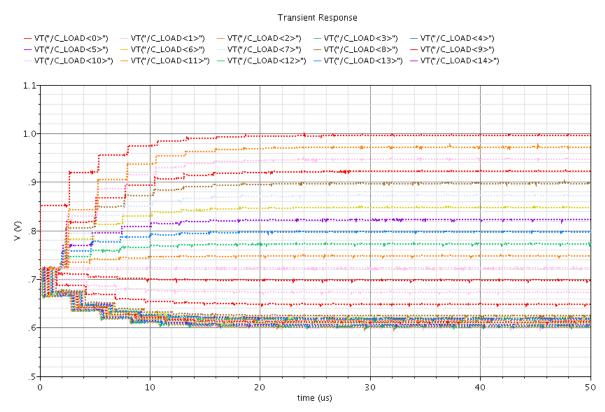

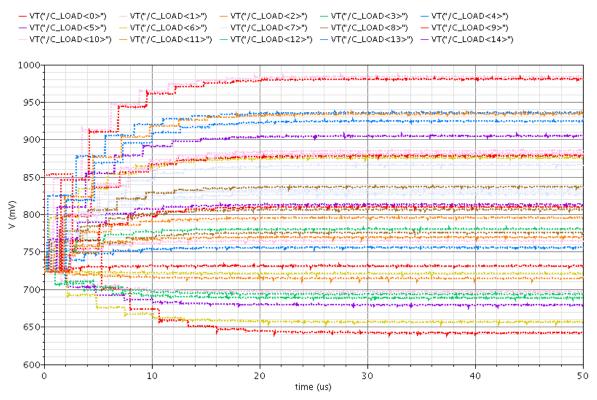

| 6.6.1   | DAC Initialization, Range, and Voltage Variations                  | 102 |

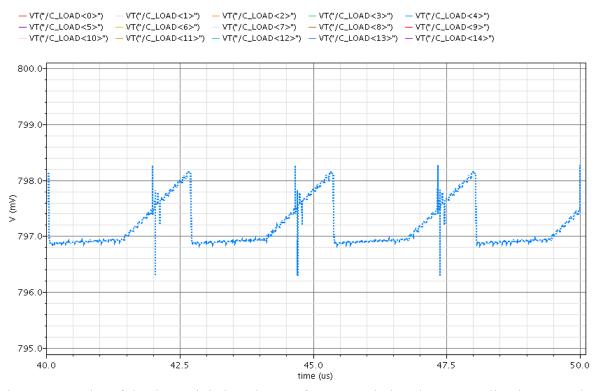

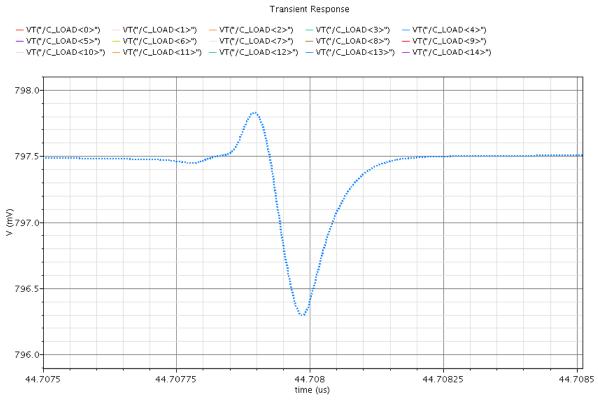

| 6.6.2   | DAC LSB Step Size                                                  | 105 |

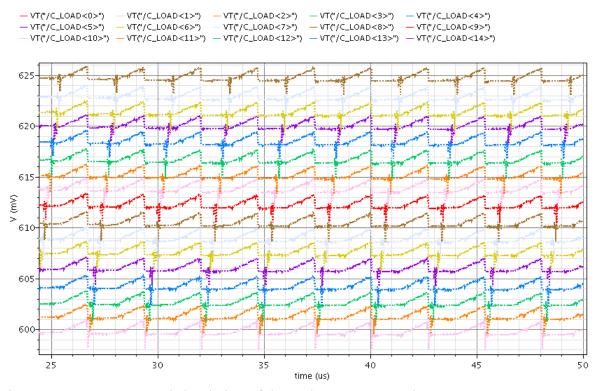

| 6.6.3   | Random Reference Voltage Generation                                | 106 |

| 6.6.4   | DAC Power Consumption                                              | 107 |

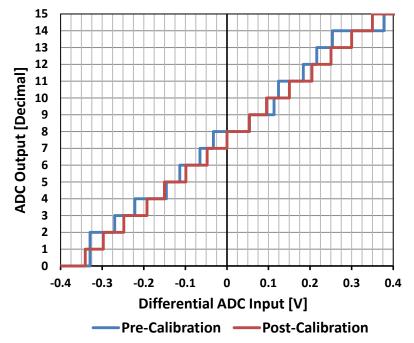

| 6.7 D.  | AC Measurement Results                                             | 108 |

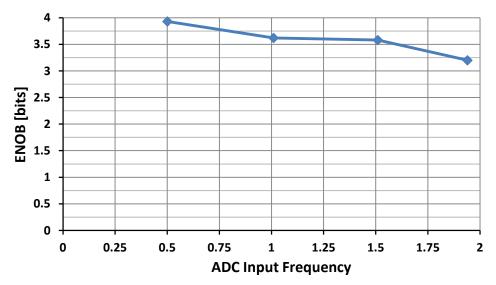

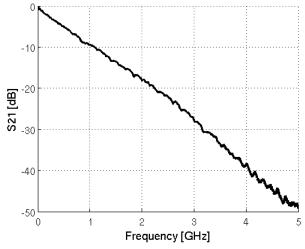

| CHAPTER | 7 FEC-BASED 4Gb/s BACKPLANE TRANSCEIVER IN 90 nm CMOS              | 110 |

|         | troduction                                                         |     |

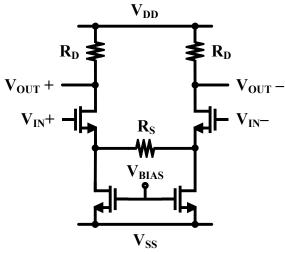

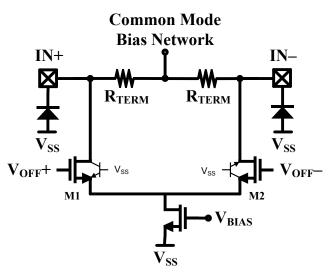

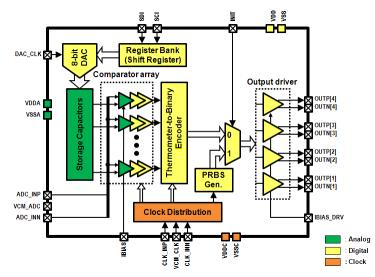

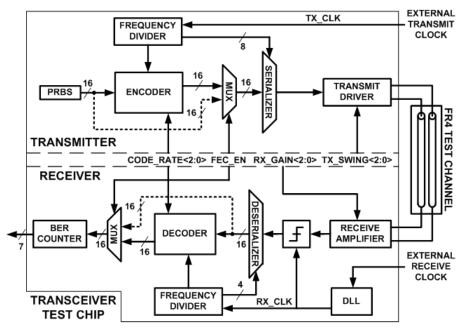

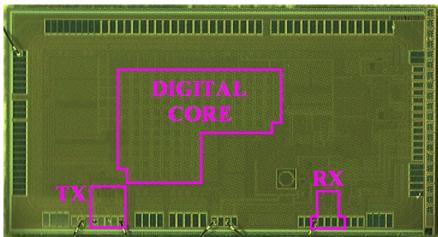

| 7.2 Te  | est Chip Architecture and Circuits                                 | 111 |

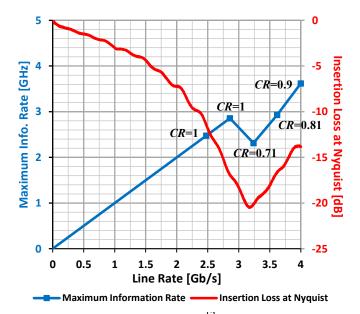

| 7.2.1   | System Design                                                      | 111 |

| 7.2        | .2  | Transceiver Overview                       | 114 |

|------------|-----|--------------------------------------------|-----|

| 7.2        | .3  | Transceiver Circuits                       | 117 |

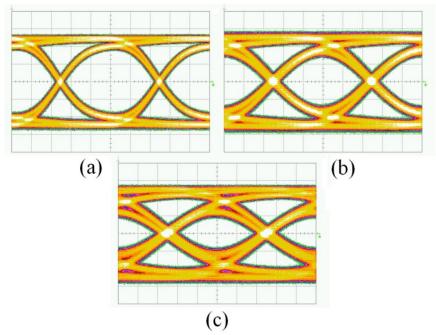

| 7.3        | Hig | h-Loss Channel Measurement Results         | 119 |

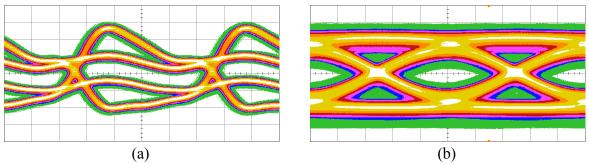

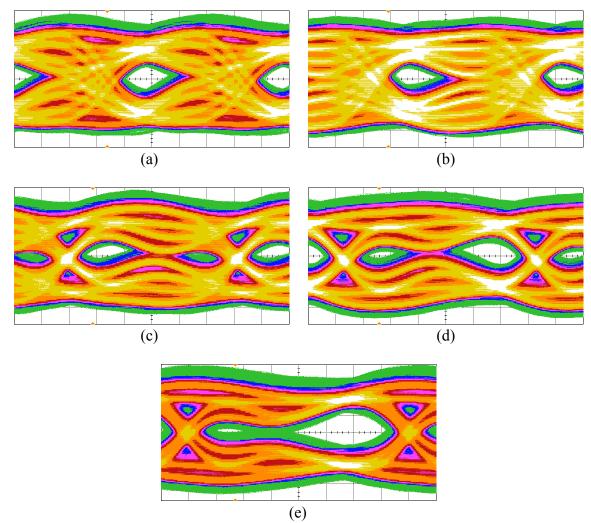

| 7.3        | .1  | Eye Diagrams                               | 119 |

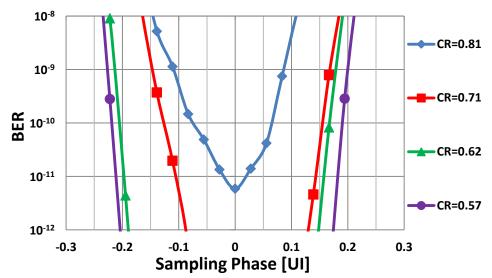

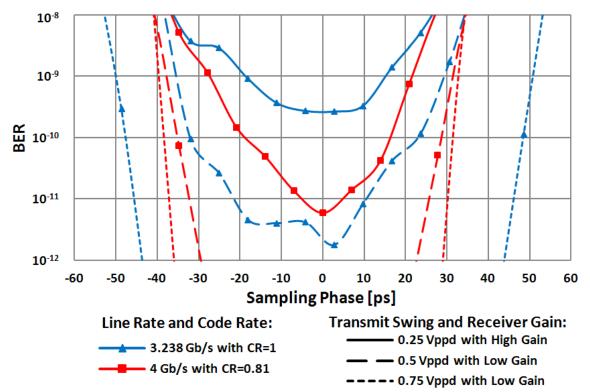

| 7.3        | .2  | BER Performance                            | 121 |

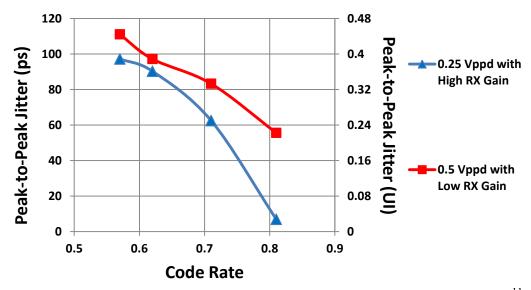

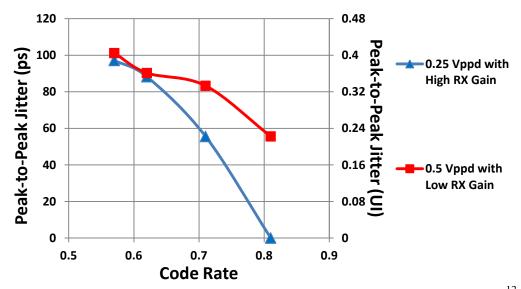

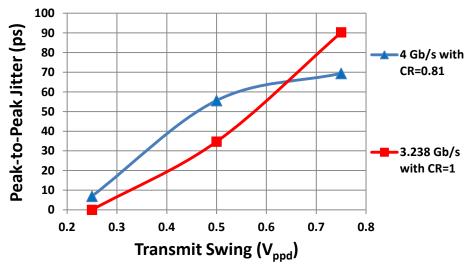

| 7.3        | .3  | Jitter Tolerance                           | 123 |

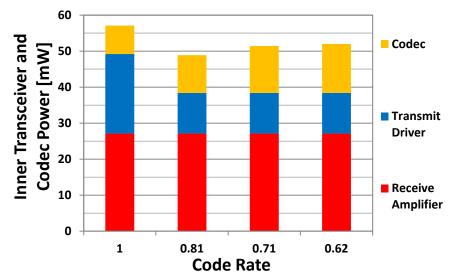

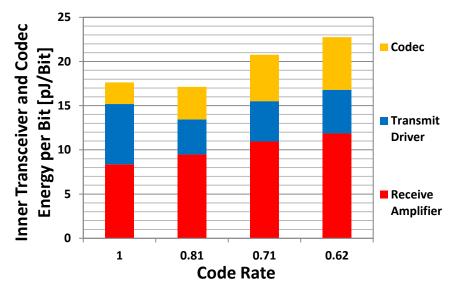

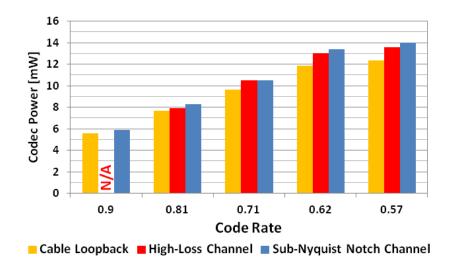

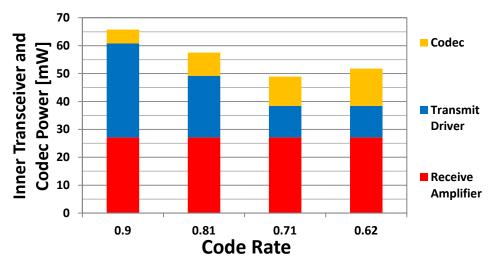

| 7.3        | .4  | Power and Energy Consumption               | 126 |

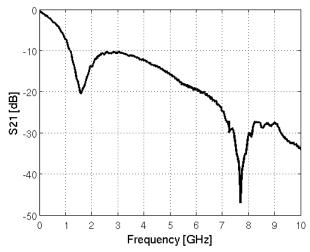

| 7.4        | Sub | -Nyquist Notch Channel Measurement Results | 132 |

| 7.4        | .1  | Eye Diagrams                               | 132 |

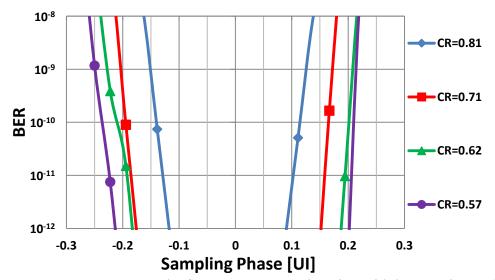

| 7.4        | .2  | BER Performance                            | 133 |

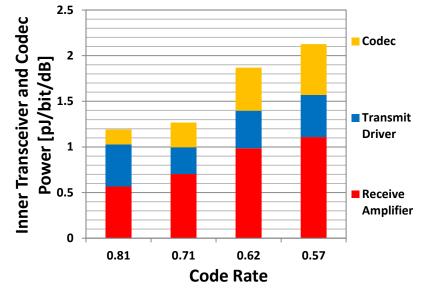

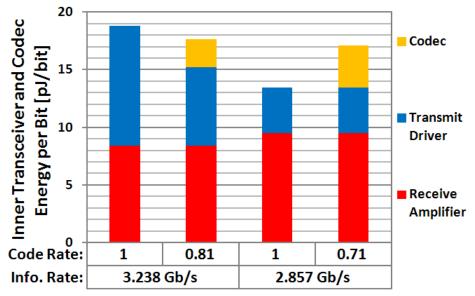

| 7.4        | .3  | Power and Energy Consumption               | 135 |

| 7.5        | Con | clusions                                   | 139 |

| REFERENCES |     |                                            |     |

# **CHAPTER 1**

# **HIGH-SPEED I/O BACKGROUND**

### 1.1 Motivation for High-Speed I/O

In today's media-rich environment, the amount of data being transmitted within modern electronic products has been increasing at a steady rate, increasing the throughput required in chip-to-chip backplane communication links. Due to limitations on board real estate and the number of package pins, the number of transmission lines between board components has been prevented from growing to meet the increased throughput demand. Therefore, to increase the data throughput, the data rate on the transmission lines has been increased. At these high-data rates, the signal integrity of the received signal is degraded due to the non-idealities of the channel and other parasitic elements, requiring additional circuitry with significant design effort and power to insure an acceptable bit error rate (BER) performance. Over the years, desirable component-level performance requirements were developed in order to insure that specific components did not limit the BER performance.

### 1.2 Serial I/O Links

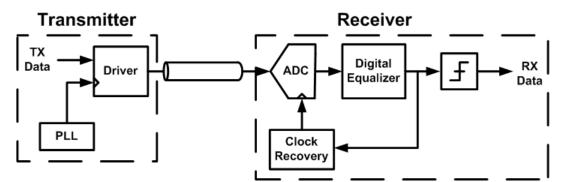

A simplified block diagram of a high-speed serial I/O link can be seen in Figure 1.1; the link is composed of components located on two chips, chip A and chip B, and on the printed circuit board (PCB) on which the transmission line that connects the chips is located. Chip A and chip B may be physically connected to the board through the use of solder, through-hole mounting, or a socket. In many instances, chip A and chip B may be on separate PCBs, using connectors to complete the physical connection to the motherboard. Regardless of how the chips are physically connected, a transmission line is used to electrically connect chip A to chip B. In this simplified block diagram, the serial I/O link is not bi-directional, in that data are only sent in this link from chip A to chip B. As such, chip A has the transmitter and chip B has the receiver. The transmitter is composed of circuits which are specifically designed to convert a data stream into electrical

signals which are sent over the PCB transmission line to the receiver of chip B. The receiver is composed of circuits which are specifically designed to convert the received electrical signals into a reconstructed data stream.

#### Printed Circuit Board (PCB)

Figure 1.1: Basic high-speed serial I/O link block diagram.

Ideally, the data stream generated at the receiver matches the data stream at the transmitter, but the physical limitations discussed in this chapter may corrupt the process. Corruption of data in serial I/O links is measured in terms of BER, which is defined as the rate at which incorrect data bits appear in the reconstructed data stream generated by the receiver. For example, a BER of  $10^{-12}$  signifies that one bit out of every trillion data bits is corrupt. While the BER requirement of a link varies from application to application, this dissertation defines highly reliable serial links as links with BER targets under  $10^{-12}$ . For a 10 Gbps link operating at capacity, a BER of  $10^{-12}$  results in an average of one bit error every 100 seconds. For the high-speed I/O links presented in this dissertation, a BER of  $10^{-12}$  is the reliability performance requirement.

## **1.3 NRZ Signal Power Spectral Density**

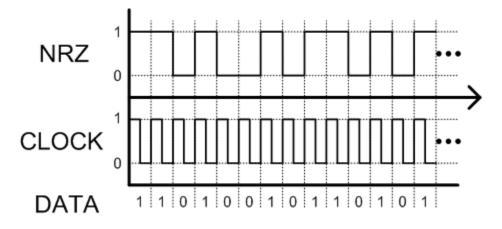

In serial I/O links, the simplest and most common signaling scheme is non-return-to-zero (NRZ). NRZ is the classical digital representation of signals; bits are represented with one of two discrete levels and transitions between levels only occur between symbols (bits). An example of NRZ signaling is shown in Figure 1.2 [1]. All data transmission in this dissertation is done with NRZ signaling.

Figure 1.2: NRZ signaling [1].

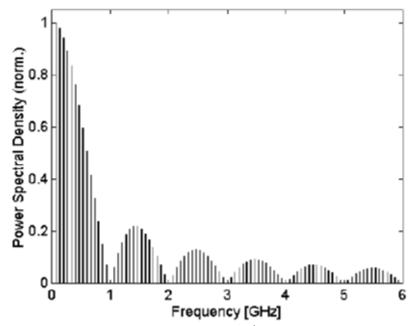

For random NRZ data, the power spectral density is a sinc(f) function with nulls at integer multiples of the data (baud) rate. An example power spectral density for a pseudorandom bit sequence (PRBS) is shown in Figure 1.3 [1]. The results show that the signal is wideband and that a significant percentage of the energy is located at low frequencies.

Figure 1.3: NRZ power spectral density for a 1 Gbps, 2<sup>4</sup>-1 PRBS sequence [1].

## **1.4 Backplane Transmission Lines**

Chip-to-chip communication over a backplane (a circuit board on which electric components and connectors to other circuit boards can be placed) utilizes a transmission line (or lines)

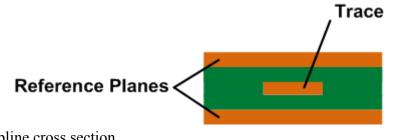

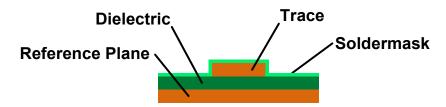

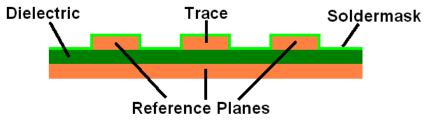

composed of a trace which is electromagnetically coupled to a return path. The two most common PCB backplane trace geometries are stripline and microstrip. Stripline, whose geometry can be seen in Figure 1.4, is a copper trace located between two copper reference planes which constitute the return path. Microstrip, whose geometry can be seen in Figure 1.5, is a copper trace on an exterior PCB layer that is coupled to a single copper reference plane which constitutes the return path. Basic PCBs use FR4, a dielectric, to separate the trace from the reference plane(s). Advanced dielectrics can be used to reduce high-frequency loss. Since the microstrip trace is located on an exterior PCB layer, the trace and adjacent dielectric are covered with a protective solder mask layer.

Figure 1.4: Stripline cross section.

Figure 1.5: Microstrip cross section.

In this dissertation, grounded coplanar transmission lines, as shown in Figure 1.6, are utilized to minimize variation. Since the trace is coupled to multiple reference conductors, variation in dielectric thickness or spacing has a reduced effect on the electrical characteristics.

Figure 1.6: Grounded coplanar transmission line cross section.

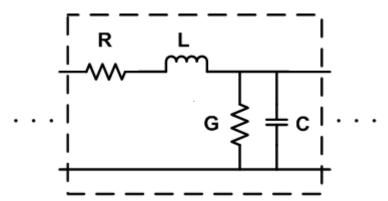

For the stripline geometry, signals travel in the transverse electromagnetic (TEM) mode since the non-TEM modes have very high cut-off frequencies (>100 GHz) [2]. As such, we can generate a distributed model of the transmission line with the circuit model in Figure 1.7. The transmission line parameters for the circuit model can be found in Table 1.1.

Figure 1.7: Transmission line circuit model.

Table 1.1: Transmission Line Parameter Descriptions

| Parameter | Description                 |

|-----------|-----------------------------|

| R         | Resistance per Unit Length  |

| L         | Inductance per Unit Length  |

| G         | Conductance per Unit Length |

| С         | Capacitance per Unit Length |

The distributed model is used to generate the well-known telegrapher's equations in the frequency domain. The telegrapher's equations define the voltage and current waves at a location z along the line.

$$\frac{\partial V(z,j\omega)}{\partial z} = -(R+j\omega L) \cdot I(z,j\omega)$$

(1.1)

$$\frac{\partial I(z,j\omega)}{\partial z} = -(G+j\omega C) \cdot V(z,j\omega)$$

(1.2)

From (1.1) and (1.2), we generate several expressions which describe the response of the channel in the frequency domain. The characteristic impedance  $Z_o$  of the channel is the ratio of the forward propagating voltage wave to the forward propagating current wave.

$$Z_o = \sqrt{\frac{(R+j\omega L)}{(G+j\omega C)}}$$

(1.3)

When a propagating wave encounters a discontinuity or load, a reflected wave is generated with a magnitude scaled by the reflection coefficient

$$\Gamma = \frac{Z_L - Z_o}{Z_L + Z_o},\tag{1.4}$$

where  $Z_L$  is the impedance of the discontinuity or load.

For a serial I/O, the impedances at the ends of the transmission line are those of the receiver and transmitter in a uni-directional link. In a bi-directional link, a transmitter and receiver are located at both ends of the transmission line. An increase in the magnitude of the reflection coefficient corresponds to an increase in the power reflected by the discontinuity or load. The propagation coefficient  $\gamma$  of the channel describes the wave propagation and attenuation.

$$\gamma = \sqrt{(R + j\omega L) (G + j\omega C)}$$

(1.5)

$$= \alpha + j\beta \tag{1.6}$$

For a lossy channel ( $R \neq 0$  or  $G \neq 0$ ),  $\gamma$  has a real component  $\alpha$ , known as the attenuation coefficient, and an imaginary component  $\beta$ , known as the phase coefficient, as seen in (1.6). The term  $\alpha$  describes the attenuation (in nepers per unit length) and  $\beta$  describes the phase change (in radians per unit length). In a lossless channel (R = 0 and G = 0),  $\alpha = 0$  and  $\beta$  is a linear function of the angular frequency,  $\omega$ . Therefore, the phase velocity (1.7) is constant in a lossless channel and frequency dependent in a lossy channel.

$$v_p = \frac{\omega}{\beta} \tag{1.7}$$

Unlike the stripline geometry, in the microstrip and grounded coplanar geometries the electromagnetic fields are not confined within the dielectric layer between the signal trace and the reference plane [2]. The field configuration therefore allows non-TEM propagation at significantly lower frequencies when compared to the stripline geometry [2]. This non-TEM propagation produces a frequency dependent phase shift which is referred to as microstrip dispersion.

At the frequencies which contain the vast majority of the signal power, which will hereafter be referred to as the frequencies of interest, three physical phenomena impact the channel response for both stripline and microstrip transmission lines at high frequencies: the skin effect, the proximity effect, and the dielectric loss [2]. The skin effect alters the current distribution within a conductor at high frequencies. As the frequency of the current increases, the current is confined to a decreasing depth  $\delta$  below the surface of the conductor.

$$\delta = \sqrt{\frac{2}{\omega \,\mu \,\sigma}} \tag{1.8}$$

The decrease in the cross section of the current flow effectively increases the resistance per unit length at higher frequencies.

The change in current distribution also generates an inductive component whose impedance equals the increase in resistance [2]. The proximity effect also alters the current distribution within the conductors [2]. As alternating current flows in the conductors, a changing magnetic field is generated around the conductors as a result of Ampere's law. When the magnetic field of the trace interacts with the return path, the current of the return path is attracted toward the trace. Similarly, the current of the trace is attracted toward the return path. This change in current distribution results in an additional resistance per unit length which increases as the frequency increases.

Dielectric loss is the dissipation of signal power due to conduction current through the dielectric at high frequencies [2]. The dielectric loss is modeled as a shunt conductance which increases with frequency.

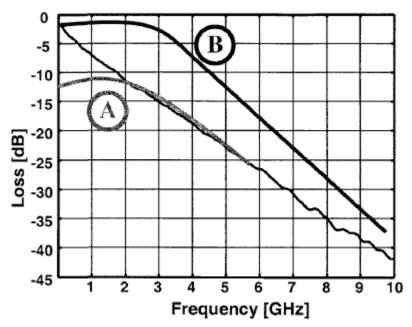

In high-speed I/O traces, the skin effect, the proximity effect, and dielectric loss change the attenuation coefficient  $\alpha$  and vary the phase coefficient  $\beta$ . As a result of these phenomena, the attenuation coefficient becomes frequency dependent and increases as the frequency increases. For frequencies above 10 MHz,  $\alpha$  increases proportionally to the square root of the frequency due to the skin effect [2]. Above 1 GHz, the attenuation coefficient increases proportionally to the frequency due to dielectric loss [2]. From (1.7), the variation of  $\beta$  due to these phenomena results in a dispersion of the signal since the phase velocity is not constant. The dispersion results in a spread of the signal energy in the time and spatial domains.

The effects of the attenuation and dispersion distort the received signal as it travels within the transmission line. The distortion of the signal at high data rates is significant and may limit the BER performance of the link if left unmitigated.

### **1.5 ESD Protection**

#### 1.5.1 Circuits

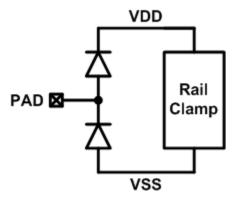

Electrostatic discharge (ESD) protection circuits and devices are utilized to protect integrated circuits against ESD events which occur during packaging, product assembly, and use. These ESD events can produce considerable voltages and currents. In integrated circuits without adequate ESD protection, the voltages and currents result in permanent damage to the devices. Since the transmitter and receiver have an external interface, they are subject to damage from ESD events. For example, without ESD protection circuitry, events such as human handling may damage the transmitter or receiver. The level of protection the ESD devices provide is dependent on many factors, including ESD device type, ESD device size, and the routing of discharge paths.

The drawback of the protection devices is the off-state parasitics they present to the external interfaces they protect. The dominating parasitic of ESD protection devices is a shunt capacitance from the external interface to the substrate in the range of several hundred femtofarads to a couple of picofarads. At high frequencies, the parasitic capacitance modifies the effective impedance at the end of the transmission line, degrading the termination match. From (1.4), this change will cause the reflection coefficient to deviate from zero, resulting in reflection of the signal energy from the receiver. Consequently, the received signals for high-speed I/Os will be distorted, with the magnitude of the distortion dependent on the magnitude of the parasitic capacitance. To provide a higher level of protection, additional devices must be added or the sizes of the current devices must be increased. As a result, the magnitude of the parasitic capacitance increases as the protection level of the ESD devices increases. Additionally, in some ESD protection schemes, a series resistor may be present in the signal path. The impact of the series resistor on the signal integrity is investigated in Chapter 3.

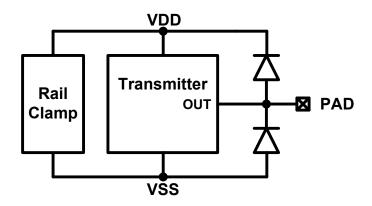

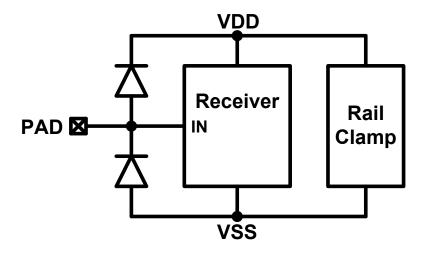

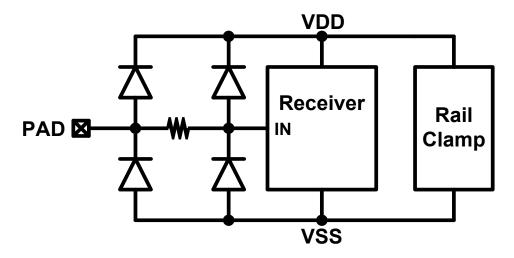

A basic ESD protection scheme, consisting of a pair of primary dual-diodes, for a high-speed I/O is shown in Figure 1.8. The diodes and rail clamp (which can conduct bi-directionally) protect against ESD events which may occur at any of the pins by providing current conduction between the pins and clamping the voltage at the pins. Due to the possibility of positive and negative polarity stresses at the pins, the network is designed to conduct current in and out of the

8

pin as necessary. It is important to note that during standard operation, the diodes and rail clamp are inactive and the current conduction is limited to leakage, such that normal operation may occur.

Figure 1.8: Dual-diode ESD protection scheme.

### **1.5.2 ESD Protection Event Standards and Testing**

While many ESD protection event standards exists, the JEDEC and ESD Association (ESDA) standards and standard test methods are commonly used by industry when determining the ESD resiliency of integrated circuits. The Industry Council on ESD Target Levels investigated ESD related failures for billions of shipped parts and utilized the information to derive protection level recommendations as a function of the ESD controls utilized during packaging and assembly of the integrated circuits [3], [4]. Specifically, the Industry Council has resiliency requirements for both the human body model (HBM) and charged device model (CDM) [3], [4].

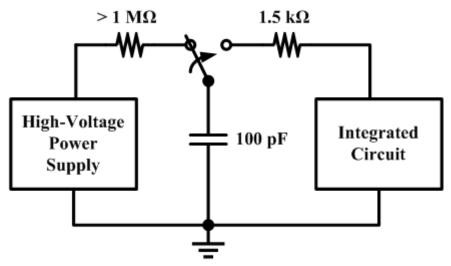

The human body model (HBM) is utilized to model ESD events which occur when a charged individual discharges through the pin of an IC while another IC is connected to a fixed potential, such as ground. A circuit model of a HBM simulator is shown in Figure 1.9 [5]. The event is modeled as a 100 pF capacitor which is discharged through a 1.5 k $\Omega$  resistor. The capacitor models the charge stored on the individual, and the resistor models the impedance of the individual and the spark resistance of the HBM event. In the figure, the 100 pF capacitor is charged up before the event using a high-voltage power supply with a series impedance of greater than 1 M $\Omega$ . The event occurs when the switch is closed and the capacitance discharges through the IC. A typical HBM event has a 10 ns risetime and a 100 ns duration. The HBM event

level is defined as the precharge voltage of the capacitor before the event. The Industry Council recommends a 1 kV protection level to provide adequate protection with margin when basic ESD control methods are utilized [3]. The peak current during a 1 kV HBM event is 0.66 A.

Fig 1.9: Human body model circuit model [5].

Due to triboelectric charging, an IC can be charged such that potential is developed [4]. The charged device model (CDM) is utilized to model the discharge of the IC through a single pin in contact with a fixed potential, such as ground. The CDM event level is defined as the precharge voltage of the integrated circuit before the event. A CDM event has a significantly shorter risetime and duration in comparison with a HBM event. Typically, a CDM event has a risetime on the order of a few hundred ps and an approximate duration of one ns [4]. The Industry Council recommends a 250 V protection level to provide adequate protection with margin when basic ESD control methods are utilized [4]. The peak current during a 250 V CDM event can be several amperes, and is dependent on the IC packaging [4].

### **1.6 Intersymbol Interference and Equalization**

Due to the signal integrity degradation of the channel and other parasitic elements of the I/O link, intersymbol interference (ISI) is produced [6]. ISI occurs when signal distortion results in the energy of one symbol (one bit) entering another symbol (another bit).

If significant ISI is present, the BER of the link may be too high to support reliable data transmission. State-of-the-art high-speed I/O links which are ISI dominated implement

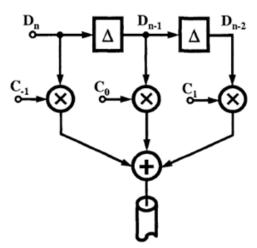

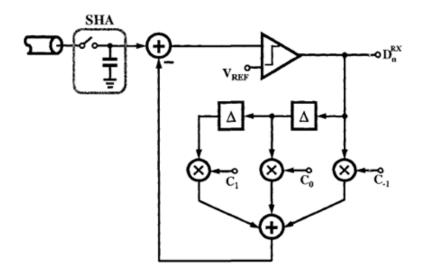

equalization which reduces ISI [6]. By reducing the ISI, the equalizer assists in the proper reconstruction of a bit. A common design is to implement feed-forward equalization (FFE) and decision-feedback equalization (DFE) to reduce ISI [6]. An example FFE architecture can be seen in Figure 1.10 and an example DFE architecture can be seen in Figure 1.11. The FFE is utilized to reduce the precursor ISI, which is ISI resulting from bits transmitted after the bit being resolved. The DFE is utilized to reduce the post-cursor ISI, which is ISI resulting from bits transmitted after the bit being transmitted before the bit being resolved. In general, equalization requires active circuitry which dissipates power. It can be assumed that the more equalization effort exerted to reduce the ISI, the more complex the equalizer will be, resulting in higher power consumption.

Figure 1.10: Transmit pre-emphasis finite impulse response (FIR) filter which implements feed-forward equalization [6].

Figure 1.11: Sample and hold followed by a DFE equalizer [6].

Instead of attempting to reduce the ISI through the addition of mitigation signals at the transmitter or receiver, a frequency shaping filter can be utilized to flatten the channel response as shown in Figure 1.12 [6]. One such frequency shaping filter is transmit pre-emphasis, as utilized in Chapter 7, where the low-frequency content is attenuated through RC source degeneration of the transmit driver.

Figure 1.12: Two ways of equalization through a frequency shaping filter [6]. (a) Attenuation of low frequencies. (b) Boosting high frequencies.

### **1.7 Signal Integrity and Eye Diagrams**

Signal integrity is a qualitative term which refers to the degradation of the signal due to ISI and noise. If a signal is said to have excellent signal integrity, then the signal has not been significantly impacted by ISI and noise. Therefore, the transmitted data stream can be reconstructed quite easily. On the other hand, if a signal is said to have poor signal integrity, then the signal has been significantly impacted by ISI and noise. Therefore, reconstruction of the data stream is quite difficult. When a signal is transitioning away from excellent signal integrity toward poor signal integrity, the transition can be described as degrading the signal integrity.

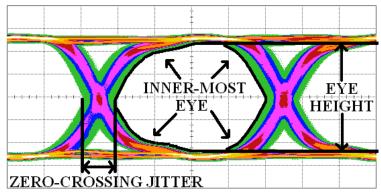

Often an eye diagram is utilized to determine the signal integrity of a high-speed I/O link. An eye diagram, example shown in Figure 1.13, is a measurement plot of a PRBS signal where the signal waveform has been overlapped upon itself at a specified interval, usually the period of the

symbol (bit period for NRZ signaling). The quality of the signal integrity is determined through a qualitative assessment of several factors including zero-crossing jitter, eye opening (height), and the shape of the inner-most (worst-case) eye.

Figure 1.13: Eye diagram of a 4 Gb/s, 0.5  $V_{ppd}$  PRBS sequence generated with a commercial transmitter (horizontal scale = 50 ps/div. and vertical scale = 100 mV/div.).

# **CHAPTER 2**

# **SYSTEM-ASSISTED I/O DESIGN STUDIES**

### 2.1 Introduction

The state-of-the-art design methodology for high-speed I/O links is to specify component-level design requirements to achieve high-quality component-level performance. The components are then unified and the high-quality component performance is used to guarantee link performance, specifically the bit error rate. While the methodology guarantees a reliable link, it does not inherently optimize the link for metrics such as the power, design complexity, or bit error rate performance. Recently, due to the increased demand for data bandwidth in backplane I/O, a system-assisted design methodology has been developed to optimize the system for a given set of metrics. By optimizing on the system level rather than the component level, the performance at the component level can be reduced from high-quality to sufficient when utilized in the co-designed I/O link system. The reduction in component-level performance requirements provides additional design margin which allows for optimization of the desired metrics. These novel system-level approaches may require the design of analog and mixed-signal circuits with unique functionality requirements. The unique functionality requirements encourage the utilization of novel circuit architectures in the context of high-speed I/O links.

## 2.2 Objectives

In this dissertation, novel analog and mixed-signal circuitry for system-assisted high-speed I/O links is presented. In the context of system-assisted design methodology, the circuits do not present ground-breaking fidelity. Instead, the circuit architectures were designed to provide unique characteristics which enable novel system architectures. The novel circuit architectures were developed by expanding traditional analog and mixed-signal circuit architectures to achieve system-level design goals while exploiting the advantages of the design methodology. Due to the

fundamental goals of the system-assisted and state-of-the-art commercial IC design, the power and area were also important design characteristics.

In this dissertation, three system-level design studies were investigated. In the first system-level study, the transmitter output and receiver input bandwidth was investigated. If codesign of the I/O link shows that the input bandwidth of the receiver limits the bit error rate performance of the link, then negative capacitance circuits can be implemented to provide bandwidth extension to mitigate the system-level limitations. In the second system-level study, the utilization of a variable-reference analog-to-digital converter (ADC) for receive sampling was investigated. Since the performance metric for high-speed I/O links is BER rather than sampling fidelity, the design requirements for an ADC in a high-speed I/O link may be modified from those of traditional ADCs. The system-level solution included an optimization of the reference levels to reduce the complexity of the ADC. Therefore, a digital-to-analog converter (DAC) was designed to generate the variable reference levels for the ADC. In the third system-level study, the utilization of coding in high-speed backplane links was investigated. The utilization of coding relaxes the BER requirement at the input of the receive slicer, allowing for a reduction of inner-transceiver power and design complexity.

### 2.3 Receiver Input Bandwidth Extension

The non-idealities of backplane I/O links limit the signal integrity at the input of the receiver, as noted in Chapter 1. The degraded signal integrity may limit the bit error rate performance of the link. The current design methodology for high-speed I/O links minimizes or mitigates the effect of each non-ideality with a component view of the problem: minimizing the sizing of the ESD protection, implementing equalization to negate the channel induced ISI, etc. In a system-level codesign of the link, attempting to minimize or mitigate all of the non-idealities may be unnecessary. For example, in [7], the effect of ESD parasitic capacitance on the BER performance is shown to be dependent on the characteristics of the link. In some links, the BER is insensitive to changes in the ESD parasitic capacitance, thereby relaxing the design constraint on the ESD protection circuitry. For links where the BER is sensitive to the parasitic capacitance, [7] investigates the usage of equalization to mitigate the impact of the parasitic capacitance on the BER.

In this system-assisted study, a lumped element model is developed to capture the effect of parasitics at the output of the transmitter and the input of the receiver. The lumped element model is reduced to a first- or second-order system to generate compact equations for the bandwidth at the output of the transmitter or the input of the receiver. The compact equations for the bandwidth can be analyzed to provide an understanding of how the parasitic elements interact to limit the bandwidth. The first- or second-order system can be used within the system-assisted codesign of the link to determine the effect of the transmitter output and receiver input bandwidth on the BER performance of the link.

Since the first- or second-order system does not sufficiently describe how the receiver input poles change as a function of the parasitic elements, a root locus analysis is performed on the receiver input, with the magnitude of the parasitic capacitance as the variable. The root locus analysis also provides information on the pole location limitations and maximum achievable bandwidth. Additionally, the analysis is utilized to formulate parasitic capacitance and inductance budgets.

If the receiver input bandwidth is shown to limit the bit error rate performance of the link, then several system-level and component-level solutions exist. The component-level solution is to restrict the parasitic elements to magnitudes that do not affect the performance of the link; i.e., they set a maximum level of parasitic capacitance for the ESD protection circuitry. On the system-level, equalization [7] or bandwidth extension [8], [9], [10], circuits can be utilized to improve the BER performance to an acceptable level. In this dissertation, the usage of negative capacitance circuit is implemented and measured for the first time. The g<sub>m</sub>-boosted negative capacitance, in a system-assisted approach, utilizes the inherent gain of the receive amplifier to enhance the characteristics of the traditional negative capacitance circuit.

### 2.4 Receive Sampling via Variable-Reference ADC

In the past five years, the usage of high-speed ADCs in backplane links to sample the receive signal has been presented [11], [12], [13]. The advantage of utilizing a high-speed ADC is that it allows for the use of digital receiver equalization. In prior work, the required ADC resolution to

effectively equalize the link has been in the range of 4.5 to 6 bits. Due to power constraints of high-precision ADCs, precisions higher than 6 bits have not been implemented.

In [14], a BER-optimal ADC-based receive architecture is presented. The optimal BER performance for an ADC does not necessarily occur for uniformly distributed quantization levels [14]. Therefore, a variable-reference ADC is required for the system-assisted design of a BER-optimal ADC-based receiver. In fact, [14] showed that the number of thresholds for a variable-level ADC can be reduced while maintaining a BER performance equal to or exceeding that of a uniform ADC with a higher number of thresholds. A reduction in the number of thresholds can result in a significant power savings in the ADC, especially if a flash ADC architecture is utilized [14].

In the second system-assisted study, a variable-reference ADC for receive sampling was implemented in 90 nm CMOS. The variable-reference ADC maintains the same core structure as a uniform ADC, but the reference levels provided to the threshold decision circuits are modified to obtain the desired BER-optimal thresholds. As such, the DAC, which provides the reference levels, must be modified to generate the optimum thresholds. In Chapter 5, a novel single-core multiple-output DAC architecture is presented which fulfills the requirements of the BER-optimal ADC receiver without negating the power advantage from the reduction in the number of threshold levels.

### 2.5 Backplane High-Speed I/O Utilizing Coding

Multi-Gb/s backplane serial links strive to achieve a bit error rate (BER)  $< 10^{-12}$  in the presence of significant channel loss and dispersion. Traditionally, such low BERs are achieved exclusively through the application of transmit side pre-distortion (i.e., pre-emphasis) and/or receive side equalization [11], [15]. The combination of channel loss and pre-emphasis equalization reduces the received signal swing such that circuit noise, clock jitter and crosstalk can limit the BER. In such a scenario, forward error correction (FEC) can be an effective technique for enhancing BER and/or reducing energy.

Though FEC is ubiquitous in wireless and long-haul wireline communication links [16], it has not found application in backplane links thus far. In [17] and [18], the application of FEC to 10 Gb/s signaling over channels with 12 to 15 dB loss at the Nyquist frequency via analysis and

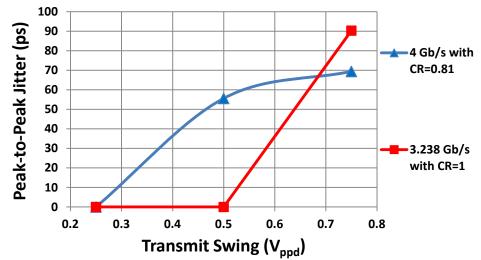

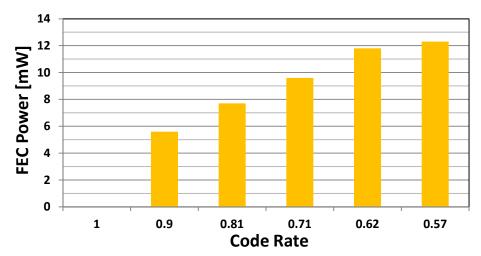

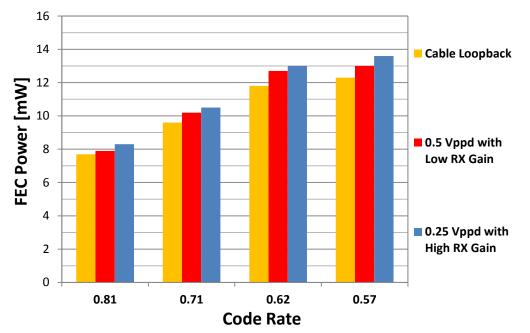

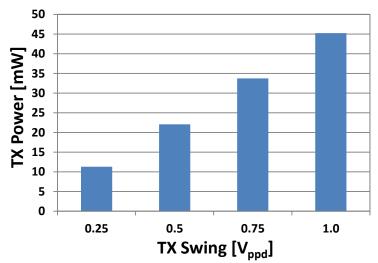

simulations was studied, and it was concluded that binary Bose and Ray-Chaudhuri (BCH) codes along with receive equalization provides a coding gain of 3 to 6 dB at a BER of  $10^{-15}$ . The reduced signal-to-noise ratio (SNR) requirements represented by the coding gain may be employed to: (*a*) reduce transmit swing, (*b*) reduce equalizer complexity, (*c*) enhance jitter-tolerance, and (*d*) improve comparator offset tolerance.

The third system-assisted study presents the results of a 90nm CMOS implementation of a 4 Gb/s line rate backplane transceiver employing FEC. The measurement results provide a quantitative assessment of how coding gain affects the trade-off between transmit swing, jitter tolerance, BER, and power. The results show that much of the promise of FEC identified in [17] and [18] can indeed be fulfilled in practice.

# **CHAPTER 3**

# TRANSMITTER AND RECEIVER BANDWIDTH ESTIMATION

### 3.1 Introduction

This chapter investigates the effect of ESD protection and other parasitics on the signal integrity of multi-Gb/s wireline transmitters and receivers. A lumped element model of the transmitter output or receiver input is used to generate a compact approximation for the bandwidth. The resulting expressions elucidate the sensitivity of the frequency response to the ESD protection devices and other parasitics. For the receiver input, Chapter 5 will present test chip measurement data to quantify the effect of ESD protection on the signal integrity at the receiver input as a function of the data rate, and also to validate the lumped model analysis.

### **3.2 Transmitter Schematic and Lumped Element Model**

In this section, a lumped model is developed for the signal path in a system consisting of a wireline transmit driver and its load, i.e., the termination, transmission line, package, and all on-chip elements at the driver output. The parasitic elements in the package and on-chip, including those associated with the ESD protection circuit, will be shown to deteriorate the termination match of the transmitter to the transmission line at high frequencies, placing an upper bound on the transmitter output bandwidth.

First, we model the impedance at the input of the transmission line. For this analysis, we do not explicitly follow the traditional frequency-domain analysis of the transmission line impedance for two reasons. First, a periodic steady-state does not exist for I/O links transmitting random data. Second, any signal arriving at the transmitter due to reflection is generally considered ISI due to transit time considerations and, therefore, will be treated as noise. As such, we model the transmission line with its characteristic impedance,  $Z_O$ . The signal propagated down the transmission line is therefore equal to  $V_{BEGIN}$ , the voltage across the resistor  $Z_O$ .

19

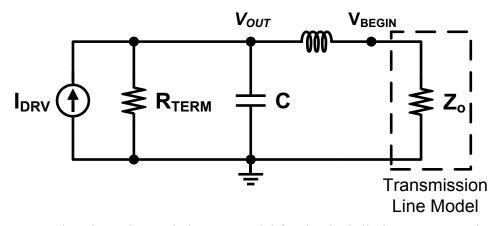

The dominant packaging-related parasitic element is often a series inductance, L, located between the transmission line and the input pads. On-chip, a shunt termination resistance  $R_{TERM}$ is placed at the output of the driver, with the pad also contributing parasitic capacitance  $C_{BONDPAD}$ . The other on-chip parasitic elements vary with the ESD protection scheme; the dual-diode based protection scheme of Figure 3.1 is commonly used as primary protection for high-speed I/O links, due to its relatively low parasitic capacitance [19]. This circuit contributes a parasitic capacitance  $C_{ESD}$  that is in parallel with  $R_{TERM}$ ,  $C_{BONDPAD}$ , and  $C_{TX}$ , the capacitance of the driver output transistors. Driving our output node, we model the transconductance transistors of our driver as a current source,  $I_{DRV}$ . The complete lumped element model is shown in Figure 3.2.

Figure 3.1: Transmitter dual-diode ESD protection scheme.

Figure 3.2: Transmitter input lumped element model for the dual-diode ESD protection scheme of Figure 3.1. For this circuit,  $V_{PAD} = V_{OUT}$  and  $C = C_{BONDPAD} + C_{ESD} + C_{TX}$ .

#### **3.3 Receiver Schematics and Lumped Element Models**

In this section, lumped models are developed for the signal path in a system consisting of a wireline receiver and its feed, i.e., the transmission line, package, and all on-chip elements up to the input transistor. The parasitic elements in the package and on-chip, including those associated with the ESD protection circuit, will be shown to deteriorate the termination match of the receiver to the transmission line at high frequencies, placing an upper bound on the receiver bandwidth.

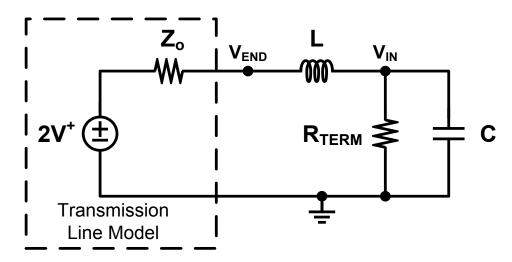

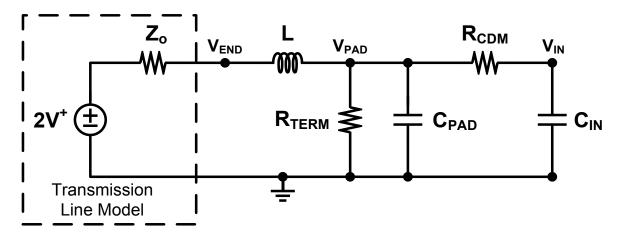

First, a Thevenin equivalent model of the transmission line is constructed, based on the time-domain transmission line equations

$$V_{END}(t) = V^+(t) \cdot (1 + \Gamma_L) \tag{3.1}$$

and

$$\Gamma_L \equiv \frac{Z_L - Z_0}{Z_L + Z_0},\tag{3.2}$$

where,  $V_{END}$  is the voltage at the end of the transmission line where it abuts the package,  $V^+$  is the signal incident on this end point,  $\Gamma_L$  is the reflection coefficient at the end of the transmission line,  $Z_L$  is the impedance seen at the end of the transmission line, and  $Z_O$  is the characteristic impedance of the transmission line. Inserting (3.2) into (3.1) produces

$$V_{END}(t) = 2V^{+}(t) \frac{Z_L}{Z_0 + Z_L}.$$

(3.3)

The dominant packaging-related parasitic element is often a series inductance, L, located between the transmission line and the input pads; this is the case for the high-speed QFN package used in Chapter 5. On-chip, a termination resistance  $R_{TERM}$  is placed at the input pad, with the pad also contributing parasitic capacitance  $C_{BONDPAD}$ . The other on-chip parasitic elements vary with the ESD protection scheme; the dual-diode based primary protection scheme of Figure 3.3 is commonly used on high-speed I/O links, due to its relatively low parasitic capacitance [19], and is employed in this dissertation. This circuit contributes a parasitic capacitance  $C_{ESD}$  that is in parallel with  $R_{TERM}$ ,  $C_{BONDPAD}$ , and  $C_{RX}$ , the capacitance of the receiver input. The complete lumped element model is shown in Figure 3.4.

Figure 3.3: Receiver dual-diode ESD protection scheme.

Figure 3.4: Receiver input lumped element model for the dual-diode ESD protection scheme of Figure 3.3. For this circuit,  $V_{PAD} = V_{IN}$  and  $C = C_{BONDPAD} + C_{ESD} + C_{RX}$ .

If a CDM protection level is specified, additional ESD circuitry may be implemented on-chip. This is shown in Figure 3.5, where a series CDM resistor  $R_{CDM}$  and secondary ESD protection circuit have been added between the input pad and the receiver input. Here, the secondary ESD protection circuit is depicted as another dual-diode circuit, presumably with much smaller devices than in the primary protection circuit. A new lumped element model is generated for this CDM-protected receiver, as shown in Figure 3.6. In this model, the parasitic capacitances are partitioned on either side of  $R_{CDM}$  into  $C_{PAD}$  and  $C_{IN}$ , where  $C_{PAD} = C_{BONDPAD} + C_{ESD}$  and  $C_{IN} = C_{ESD2} + C_{RX}$ . The parasitic capacitance of the secondary protection device(s) is denoted by  $C_{ESD2}$ .

Figure 3.5: Dual-diode primary ESD protection scheme which has been augmented with a series resistor and secondary dual-diode devices to improve CDM resiliency.

Figure 3.6: Receiver input lumped element model for the ESD protection scheme of Figure 3.5.  $C_{PAD} = C_{BONDPAD} + C_{ESD}$  and  $C_{IN} = C_{ESD2} + C_{RX}$ .

### 3.4 Bandwidth Estimation Method

Using the transmitter model of Figure 3.2 or receiver models of Figures 3.4 and 3.6, one can derive a transfer function to relate  $V_{BEGIN}(f)$  to  $I_{IN}(f)$  for the transmitter or  $V_{IN}(f)$  to  $V^+(f)$  for the receiver. The transfer function of a linear system with lumped elements, H(s) [20], is

$$H(s) = \frac{a_0 + a_1 s + a_2 s^2 + \dots + a_m s^m}{1 + b_1 s + b_2 s^2 + \dots + b_n s^n}.$$

(3.4)

Deriving the transfer function of a multiple element RLC circuit can be tedious, and thus it is preferable to use convenient techniques to obtain the coefficients of the first one  $(b_1)$  or two  $(b_1)$

and  $b_2$ ) terms in the denominator [20]. If the system has dominant poles, then the overall bandwidth can be well approximated using these few coefficients.

The procedure for calculating the bandwidth is an application of the circuit analysis in [20] and expanded to calculate the bandwidth of the second-order system. The bandwidth of the first-order system,  $\hat{f}_{-3dB}$ , is equal to

$$\hat{f}_{-3dB} = \frac{1}{2\pi b_1},\tag{3.5}$$

which requires the calculation of  $b_1$ . The bandwidth of the second-order system,  $\bar{f}_{-3dB}$ , is equal to

$$\bar{f}_{-3dB} = f_n \sqrt{1 - \frac{1}{2Q^2} + \sqrt{\frac{1}{4Q^4} - \frac{1}{Q^2} + 2}},$$

(3.6)

which requires the calculation of  $f_n$ , the natural frequency of the second-order system, and Q, the quality factor of the second-order system. The natural frequency is equal to

$$f_n = \frac{1}{2\pi\sqrt{b_2}},$$

(3.7)

which requires the calculation of  $b_2$ . The second-order quality factor can be calculated from  $b_1$  and  $b_2$  as

$$Q = \frac{\sqrt{b_2}}{b_1} \tag{3.8}$$

and rewritten in terms of  $\hat{f}_{-3dB}$  and  $\bar{f}_{-3dB}$ :

$$Q = \frac{\hat{f}_{-3dB}}{f_n} \tag{3.9}$$

The calculation of  $b_1$  and  $b_2$  for the receiver lumped element models is shown in bandwidth calculations in Section 3.5.

The analysis of [20] notes the impact of zeros on the bandwidth estimation and derives a modified bandwidth estimation in the presence of significant zero(s). Inspecting the circuits in Figure 3.2, 3.4, and 3.6, it is obvious that all transfer constants,  $H^{ijk...}$ , defined in [20] are equal to zero since infinitely valuing any reactive element results in isolation between the transmission line and the transmitter or receiver [20]. Therefore,

$$a_i = 0$$

, for  $i \ge 1$ . (3.10)

Since the numerator of the transfer function is a constant, no finite zeros exist. Therefore, the bandwidth equations (3.5) and (3.6) do not need to be modified to improve their accuracy in the presence of significant zeros since no finite zeros exist.

## 3.5 Receiver Bandwidth Estimation

### **3.5.1 First-Order Bandwidth Derivation**

To calculate the first-order system bandwidth for Figures 3.4 and 3.6,  $b_1$  must be derived. From [20],  $b_1$  is equal to the sum of all zero-value time constants. Therefore, for Figure 3.4

$$b_1 = \frac{L}{Z_o + R_{TERM}} + (Z_o || R_{TERM})C$$

(3.11)

and

$$b_1 = \frac{L}{Z_o + R_{TERM}} + (Z_o || R_{TERM}) C_{PAD} + [R_{CDM} + (Z_o || R_{TERM})] C_{IN}$$

(3.12)

for Figure 3.6. For Figure 3.4, the first-order bandwidth can be calculated by inserting (3.11) into (3.5):

$$f_{-3dB} = \frac{Z_o + R_{TERM}}{2\pi (L + R_{TERM} Z_o C)}.$$

(3.13)

If the termination is matched to the characteristic impedance of the channel, then (3.13) simplifies to

$$f_{-3dB} = \frac{1}{\pi(\frac{L}{Z_0} + Z_0 C)}.$$

(3.14)

Similarly for Figure 3.6, the first-order bandwidth can be calculated by inserting (3.12) into (3.5):

$$f_{-3dB} = \frac{Z_o + R_{TERM}}{2\pi [L + R_{TERM} Z_o (C_{PAD} + C_{IN}) + (R_{TERM} + Z_o) R_{CDM} C_{IN}]}.$$

(3.15)

If the termination is matched to the characteristic impedance of the channel, then (3.15) simplifies to

$$f_{-3dB} = \frac{1}{\pi \left[\frac{L}{Z_o} + Z_o(C_{PAD} + C_{IN}) + 2R_{CDM}C_{IN}\right]}.$$

(3.16)

### 3.5.2 Second-Order Bandwidth Derivation

To calculate the second-order system bandwidth for Figures 3.4 and 3.6,  $b_1$  and  $b_2$  must be derived. The derivation of the first-order bandwidth in Section 3.5.1 includes the derivation of  $b_1$ . From [20],  $b_2$  can be calculated from a set of time constants. Therefore, for Figure 3.4

$$b_2 = \frac{L}{Z_0 + R_{TERM}} R_{TERM} C \tag{3.17}$$

and

$$b_{2} = \frac{L}{Z_{o} + R_{TERM}} R_{TERM} C_{PAD} + \frac{L}{Z_{o} + R_{TERM}} (R_{TERM} + R_{CDM}) C_{IN} + (Z_{o} || R_{TERM}) R_{CDM} C_{PAD} C_{IN}$$

$$(3.18)$$

for Figure 3.6. For Figure 3.4, the second-order natural frequency can be calculated by inserting (3.17) into (3.7):

$$f_n = \frac{1}{2\pi} \sqrt{\frac{R_{TERM} + Z_o}{R_{TERM} LC}}.$$

(3.19)

If the termination is matched to the characteristic impedance of the channel, then (3.19) simplifies to

$$f_n = \frac{1}{\pi} \sqrt{\frac{1}{2LC}}.$$

(3.20)

Similarly for Figure 3.6, the second-order natural frequency can be calculated by inserting (3.18) into (3.7):

$$f_n = \frac{1}{2\pi} \sqrt{\frac{R_{TERM} + Z_o}{R_{TERM} L(C_{PAD} + C_{IN}) + (L + R_{TERM} Z_o C_{PAD}) R_{CDM} C_{IN}}}.$$

(3.21)

If the termination is matched to the characteristic impedance of the channel, then (3.21) simplifies to

$$f_n = \frac{1}{\sqrt{2}\pi} \sqrt{\frac{1}{L(C_{PAD} + C_{IN}) + (\frac{L}{Z_0} + Z_0 C_{PAD}) R_{CDM} C_{IN}}}.$$

(3.22)

The second-order system quality factor can then be calculated from first-order bandwidth and second-order natural frequencies:

$$Q = \frac{\hat{f}_{-3dB}}{f_n}.$$

(3.23)

Then, the natural frequency and quality factor can be utilized to calculate the second-order bandwidth

$$\bar{f}_{-3dB} = f_n \sqrt{1 - \frac{1}{2Q^2} + \sqrt{\frac{1}{4Q^4} - \frac{1}{Q^2} + 2}}.$$

(3.24)

#### 3.5.3 Bandwidth Estimation Method

The first- and second-order bandwidth derivations from Sections 3.5.1 and 3.5.2 can be utilized to generate a bandwidth estimation method. The first-order bandwidth estimation does not determine the location of the poles on the real-imaginary plane [20]. If the dominant poles of the system are complex, then the bandwidth can be severely underestimated by the first-order bandwidth estimation [20]. In the second-order system, the quality factor, Q, provides information about the location of the two poles. If Q < 0.5, then the second-order system consists of two distinct real poles. If Q = 0.5, then the second-order system consists of two identical real poles (a double pole). If Q > 0.5, then the second-order system consists of a pair of complex conjugates. While the second-order system is a better approximation for the system since fewer higher-order terms are ignored, the first-order system is desirable for small Q values. When Q is < 0.5 and small, changes in the element values may quickly change Q. When Q quickly changes, it is difficult to understand how the parasitic elements interact to limit the bandwidth of the system. On the other hand, for small O, the system is well approximated by the first-order system since the second-order system has a dominant pole. Therefore, the first-order bandwidth approximation can be used without a significant loss in accuracy while providing an equation which allows for analysis of how the parasitic elements interact to limit the bandwidth of the system. Therefore, the first-order bandwidth is utilized to approximate the bandwidth when  $Q \le 0.5$  and the second-order bandwidth is utilized to approximate the bandwidth when Q is  $\geq 0.5$ .

The procedure for bandwidth estimation is detailed below, for the case that  $R_{TERM} = Z_O$ , i.e., the termination has been matched to the characteristic impedance of the transmission line. If the termination is not matched to the transmission line, then the corresponding equations from Sections 3.5.1 and 3.5.2 should be used instead.

Step 1: Calculate the estimator  $\hat{f}_{-3dB}$  using

$$\hat{f}_{-3dB} = \frac{1}{\pi(\frac{L}{Z_0} + Z_0 C)}$$

(3.25)

for the receiver model of Figure 3.4, or

$$\hat{f}_{-3dB} = \frac{1}{\pi \left[\frac{L}{Z_o} + Z_o(C_{PAD} + C_{IN}) + 2R_{CDM}C_{IN}\right]}$$

(3.26)

for that shown in Figure 3.6.

Step 2: Calculate  $f_n$  as

$$f_n = \frac{1}{\pi\sqrt{2LC}} \tag{3.27}$$

for the model of Figure 3.4, or

$$f_n = \frac{1}{\pi \sqrt{2[L(C_{PAD} + C_{IN}) + (\frac{L}{Z_o} + Z_o C_{PAD})R_{CDM}C_{IN}]}}$$

(3.28)

for the model of Figure 3.6.

Step 3: Calculate Q as

$$Q = \frac{\hat{f}_{-3dB}}{f_n} \,. \tag{3.29}$$

Step 4: Calculate the estimator  $\bar{f}_{-3dB}$  as

$$\bar{f}_{-3dB} = f_n \sqrt{1 - \frac{1}{2Q^2} + \sqrt{\frac{1}{4Q^4} - \frac{1}{Q^2} + 2}} .$$

(3.30)

Step 5: If  $Q \ge 0.5$ , then the estimated -3 dB bandwidth  $f_{-3dB}$  is

$$f_{-3dB} = \bar{f}_{-3dB} , \qquad (3.31)$$

else the estimated -3 dB bandwidth  $f_{-3dB}$  is

$$f_{-3dB} = \hat{f}_{-3dB} \,. \tag{3.32}$$

In step 1, the estimator  $\hat{f}_{-3dB}$ , the approximate bandwidth of the first-order system, is calculated. In step 2,  $f_n$ , the natural frequency of the second-order system, is calculated. In step 3, the quality factor, Q, of the second-order system is calculated, and in step 4, the -3 dB

bandwidth of the second-order system is calculated. In step 5, the Q value is used to determine if the second-order system contains complex poles. If  $Q \ge 0.5$ , then there are complex poles (or double pole in the event of Q = 0.5), and the second-order system bandwidth is the bandwidth estimate. Otherwise, the first-order system bandwidth is the bandwidth estimate.

#### **3.5.4 Bandwidth Simulations**

To evaluate the receiver bandwidth estimation formulas presented above, the circuits of Figures 3.4 and 3.6 were simulated using Spectre and the results are compared to (3.31) and (3.32). In all simulations, the characteristic impedance of the transmission line and the termination is 50  $\Omega$ .

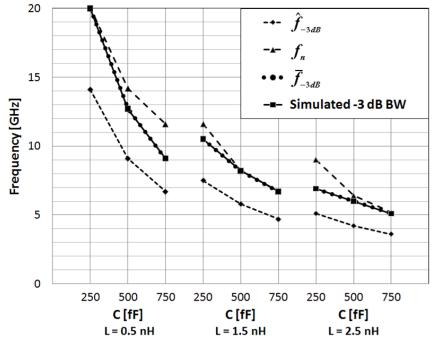

The simulated bandwidth of the circuit in Figure 3.4 is shown in Figure 3.7, as a function of L and C. The results are equivalent to the results for the circuit in Figure 3.6 with  $R_{CDM} = 0 \Omega$  and  $C = C_{PAD} + C_{IN}$ . For the investigated range of L and C values,  $Q \ge 0.5$ , and, according to (3.31),  $\bar{f}_{-3dB}$  should be used to estimate  $f_{-3dB}$ . The results shown in Figure 3.7 confirm this assertion and, in fact,  $\bar{f}_{-3dB}$  is exactly equal to the simulated bandwidth, because the circuit of Figure 3.4 is precisely a second-order system.

Figure 3.7. Simulated bandwidth of the circuit in Figure 3.4, as a function of *C* for L = 0.5 nH, 1.5 nH, and 2.5 nH.  $Z_o = R_{TERM} = 50 \Omega$ . Equations (3.22), (3.24), and (3.27) are also plotted.

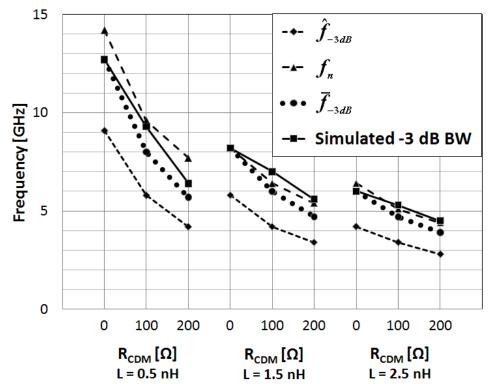

The simulated bandwidth of the circuit in Figure 3.6 is shown in Figure 3.8. Here,  $C_{PAD}$  and  $C_{IN}$  are fixed, but *L* and  $R_{CDM}$  are varied. As  $R_{CDM}$  increases, the bandwidth is deteriorated. In the considered range of *L* and *C* values, the quality factor is greater than 0.5, and  $\bar{f}_{-3dB}$  should be used to estimate  $f_{-3dB}$ . Due to the presence of a third pole in the complete transfer function,  $\bar{f}_{-3dB}$  provides a conservative estimate of the bandwidth, as shown in Figure 3.8.

Figure 3.8. Simulated bandwidth of the circuit in Figure 3.6 as a function of  $R_{CDM}$  for L = 0.5 nH, 1.5 nH, 2.5 nH.  $C_{PAD} = 400$  fF,  $C_{IN} = 100$  fF, and  $Z_o = R_{TERM} = 50 \Omega$ . Equations (3.23), (3.25), and (3.27) are also plotted.

The results of Figures 3.7 and 3.8 show that, for the investigated range of parasitic elements, a two pole model of the receiver input is more accurate than a single pole model. For wirebond packages with inductances on the order of a nanohenry, such as QFNs, the improved accuracy will allow for the formulation of a more precise capacitance budget for the ESD protection circuit [21]. In contrast, for very low inductance packages, such as flip chip BGAs, a single pole model of the receiver may provide an accurate estimate of the frequency response.

While the bandwidth estimation method can produce an excellent bandwidth estimate, as shown in Figures 3.7 and 3.8, the bandwidth estimation method may not be sufficient for the optimization of ESD protection. Whenever a high-order system is approximated with a lower

order system, the approximation will result in a loss in precision, potentially changing the sensitivity of the bandwidth to an element. For some systems, the loss in precision may be small as the dominant system dynamics can be represented by the lower order system, while for other systems, the loss in precision may be significant as the dominant system dynamics cannot be represented by the lower order system. In Figures 3.7 and 3.8, the impact of reducing the lower order system approximation from second-order to first-order is shown to be significant. In Chapter 4, it will be shown that both poles of the circuit in Figure 3.4 are significant for a wide range of element values, resulting in an imprecise first-order system approximation. To determine the impact of approximating a third-order system, such as the circuit in Figure 3.6 or the receiver input with negative capacitance presented in Chapter 5, as a second-order system in order to estimate the bandwidth, the dynamics of the third-order system must be ascertained. In Chapter 4 and 5, a root locus analysis method is presented to determine how an element within a circuit impacts the location of the poles. If the root locus analysis demonstrates, for the magnitude range of interest for each element, that two poles dominate the response, then the bandwidth estimation method should provide excellent accuracy. In this scenario, the bandwidth estimation method can be utilized in order to optimize the design of the ESD protection circuitry. Utilizing the bandwidth estimation method is desirable as the relationship between the elements and the -3 dB bandwidth can be determined algebraically. If the root locus analysis demonstrates that three or more poles dominate the response, then the bandwidth estimation method will underestimate the -3 dB bandwidth and the sensitivity of the bandwidth to individual elements may be distorted. In this scenario, the root locus analysis method, instead of the bandwidth estimation method, should be utilized to optimize the design of the ESD protection circuitry.

#### 3.5.5 Analysis of the Estimated Bandwidth

The simulation results indicate that both the parasitic series inductance and parasitic capacitance limit the input bandwidth of the receiver. Therefore, the amount of parasitic capacitance that a high-speed receiver can tolerate for a specific signal integrity requirement is strongly dependent on the package inductance. An engineering rule of thumb can be formulated for receiver inputs with Q < 0.5, based on (3.25): if  $Z_O = 50 \Omega$ , the signal integrity effect of 0.25 nH of package inductance (*L*) is equivalent to 100 fF of parasitic capacitance from the ESD

protection circuit ( $C_{ESD}$ ). A separate rule of thumb can be formulated for receiver inputs with  $Q \ge 0.5$ ; this rule is based on  $f_n$  of (3.24) which, as shown in Figure 3.7 and 3.8, provides an upper-bound on  $f_{-3dB}$ . For receiver inputs with  $Q \ge 0.5$  and for a fixed bandwidth specification, a 20% decrease in the parasitic inductance allows for a 25% increase in the total parasitic capacitance at the input of the receiver.

The derivation in Section 3.5.3 shows that the addition of a series resistor  $R_{CDM}$  results in an additional term in the denominator of the bandwidth estimator, reducing the bandwidth. By reorganizing (3.26) to

$$\hat{f}_{-3dB} = \frac{1}{\pi [\frac{L}{Z_0} + Z_0 C_{PAD} + (1 + 2\frac{R_{CDM}}{Z_0}) Z_0 C_{IN}]}$$

(3.33)

and (3.28) to

$$f_n = \frac{1}{\pi \sqrt{2[LC_{PAD} + (1 + \frac{R_{CDM}}{Z_o} + \frac{Z_o C_{PAD}}{L} R_{CDM}) LC_{IN}]}}$$

(3.34)

for Figure 3.6 and comparing to (3.25) and (3.27) of Figure 3.4, the addition of the series resistor can be seen as applying a magnification factor to the effect of  $C_{IN}$ . For a receiver with Q < 0.5,  $R_{CDM}$  magnifies the bandwidth limiting effect of  $C_{IN}$  parasitic capacitance by a factor of  $1 + 2 \frac{R_{CDM}}{Z_o}$ . For a receiver with  $Q \ge 0.5$ ,  $R_{CDM}$  magnifies the effect of  $C_{IN}$  by a factor of  $1 + \frac{R_{CDM}}{Z_o} + \frac{Z_o C_{PAD}}{L} R_{CDM}$ . Since  $R_{CDM}$  is often greater than  $Z_o$ , the magnification factor can be significant. For example, if  $R_{CDM}$  is 100  $\Omega$  and  $Z_o$  is 50  $\Omega$ , then  $C_{RX}$  and  $C_{ESD2}$  are magnified by at least a factor of 3.

## **3.6 Optimization of Receiver Secondary Protection Circuits**

A common CDM design rule is to set the product of the series CDM resistor and width of the secondary protection device(s) to a constant. Reasonably assuming that  $C_{ESD2}$  is a linear function of the width of the secondary protection device(s), this design rule requires that  $\tau$ , defined below, also be a constant.

$$\tau = R_{CDM} C_{ESD2} \,. \tag{3.35}$$

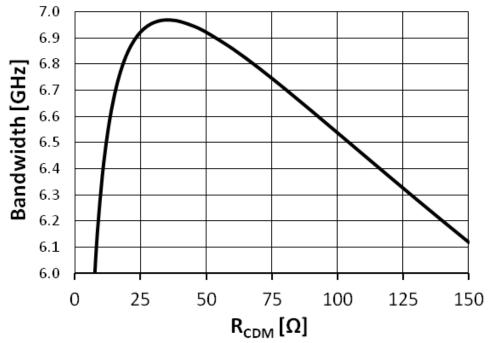

Utilizing (3.35) as a design constraint to the bandwidth estimation method, a plot of the bandwidth as a function of  $R_{CDM}$  can be generated as in Figure 3.9. From the plot, an optimal CDM resistor value exists which optimizes the bandwidth. Utilizing (3.26) and (3.28)

constrained by (3.35), the CDM resistor value which maximizes the bandwidth,  $R_{CDM,OPT}$ , while achieving the targeted CDM resiliency level can then be calculated from

$$R_{CDM,OPT} = \sqrt{\frac{Z_o \tau}{2C_{RX}}}$$

(3.36)

for Q < 0.5 and

$$R_{CDM,OPT} = \sqrt{\frac{\tau}{(\frac{1}{Z_0} + \frac{Z_0 C_{PAD}}{L})C_{RX}}}$$

(3.37)

for  $Q \ge 0.5$ . For example, if  $\tau = 100 \ \Omega \cdot 25 \ \text{fF}$ ,  $C_{PAD} = 400 \ \text{fF}$ ,  $L = 1.5 \ \text{nH}$ ,  $C_{RX} = 75 \ \text{fF}$ , and  $Z_O = 50 \ \Omega$ , then  $R_{CDM,OPT}$  is 31.6  $\Omega$ .

Figure 3.9: Bandwidth as a function of  $R_{CDM}$ , with a design constraint  $\tau = R_{CDM}C_{ESD2} = 2500 \ \Omega \cdot \text{fF}$ . L = 1.5 nH,  $C_{PAD} = 400 \text{ fF}$ , and  $C_{RX} = 75 \text{ fF}$ .

# 3.7 Transmitter Output Bandwidth Estimation

In Section 3.2, a lumped element model for a transmitter, shown in Figure 3.2, was generated. Similar to the receiver input poles, the transmitter output poles can degrading the signal integrity. By observation, the sourceless lumped element model of Figure 3.2 is identical to that of the receiver input, Figure 3.4, with relabeled nodes. Since the poles of a circuit are independent of the choice of input or output [20], the poles of Figure 3.2 are identical to the poles of Figure 3.4. Additionally, by inspection, the transfer function for the network of

Figure 3.2 does not contain any finite zeroes [20], so the entire analysis of the receiver of Figure 3.4 can be applied directly to the lumped element model of the transmitter in Figure 3.2.

# **3.8** Generalized Bandwidth Estimation Method

The bandwidth estimation method presented in Section 3.5 can be utilized as a general bandwidth estimation method. In the lumped element models investigated, Figures 3.2, 3.4, and 3.6, second- or third-order models of the transmitter output and receiver input ports are utilized. If a higher-order lumped element model of the transmitter and receiver is generated (or for any other input or output network), then the method described in Section 3.4 can be utilized to generate a first- and second-order bandwidth estimate by re-deriving  $b_1$  and  $b_2$  utilizing the methods in [20].

# **3.9 Estimating Bandwidth Extension of Negative Capacitance Circuits**

In Chapter 5, circuits which present an impedance to negate parasitic capacitance will be presented as a method to enhance bandwidth. When evaluating whether it is worthwhile to include a negative capacitance circuit in the receiver front-end, one estimates the maximum possible bandwidth that can be obtained by ideally cancelling some or all of the pad capacitance. Utilizing the appropriate receiver model – Figure 3.4 or Figure 3.6 – one can evaluate the corresponding equations in Section 3.5.3 to find the maximum values of  $\hat{f}_{-3dB}$  and  $\bar{f}_{-3dB}$  as a function of  $C [C_{PAD}]$ ; these, in turn, are used to obtain a good estimate of the maximum possible bandwidth. Due to the presence of packaging inductance, the maximum possible bandwidth does not necessarily occur for C or  $C_{PAD}$  equal to zero. For some applications, other parasitics will limit the achievable bandwidth extension. For the packages with significant series inductance; such as the test chip presented in Chapter 5, the bondwire inductance will limit the effectiveness of the negative capacitance circuits and place an upper-bound on the achievable bandwidth extension. If the optimal negative capacitance circuits, the bandwidth estimation method can also be

used to estimate the achievable bandwidth extension as a function of the magnitude of achievable negative capacitances.

When estimating the bandwidth extension utilizing the method presented above, the capacitance mitigation is assumed to be ideal. In Chapter 5, the performance of negative capacitance circuits is shown to be limited by the negative resistance component of the impedance. The negative resistance of the circuit drastically impacts the receiver input pole locations and invalidates the ideal capacitance mitigation assumption. Therefore, estimating the bandwidth extension is a useful tool when determining the initial viability of a negative capacitance circuit, while the root locus method presented in Chapter 5 should be utilized to determine how much impact the addition of a negative capacitance circuit can have on the receiver input pole locations and bandwidth.

# **CHAPTER 4**

# **RECEIVER INPUT ROOT LOCUS ANALYSIS**

# 4.1 Introduction

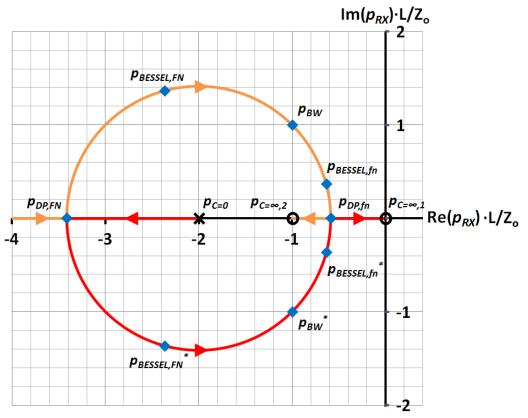

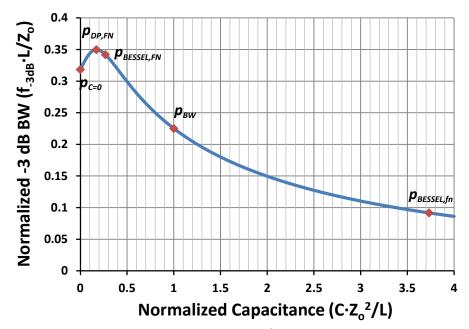

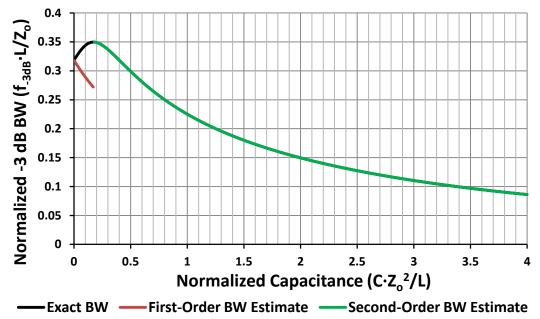

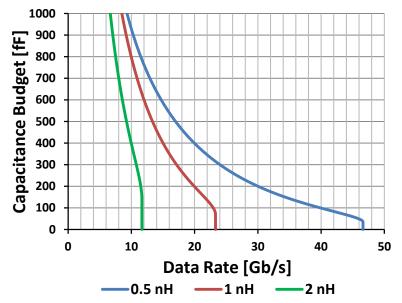

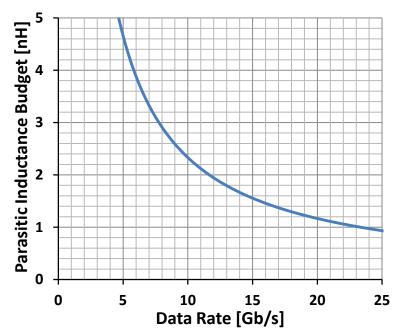

In Chapter 3, a bandwidth estimation method was generated to analyze the bandwidth limitation at the receiver input. In this chapter, a scalable root locus plot of the receiver input poles will be generated in order to analyze how the poles change as a function of the parasitic capacitance. Additionally, a scalable plot of the corresponding -3 dB bandwidth will be generated with the significant points on the root locus identified. The results will lead to a suggested optimal design point for the magnitude of the parasitic capacitance. If the parasitic capacitance at the input of the receiver is under the optimal design point, then the addition of parasitic capacitance to the input is trivial. If the parasitic capacitance at the input of the receiver is over the optimal design point, the utilization of negative capacitance circuits for bandwidth extension will be investigated in Chapter 5. At the end of this chapter, the scalable -3 dB bandwidth plot will be used to generate parasitic capacitance and inductance budgets for the input of high-speed receivers.

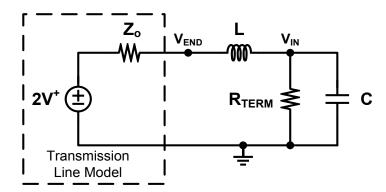

# 4.2 Receiver Lumped Element Model

In Chapter 3, lumped element models were generated for the signal path consisting of a wireline receiver and its feed, i.e., the transmission line, package, and all on-chip elements up to the input transistor. For a receiver utilizing a primary-only ESD protection circuit, the corresponding lumped element model is shown in Figure 4.1, where  $V^+$  is the signal incident at the end of the trace,  $V_{END}$  is voltage at the end of the transmission line where it abuts the package, and  $V_{IN}$  is the voltage at the input of the receiver. The trace is defined to be the transmission line with characteristic impedance  $Z_O$ , and is terminated with an on-chip termination resistance  $R_{TERM}$ . While an acceptable lumped element model for a package will vary, in this dissertation, the effect of packaging-related series inductance, L, located between the

trace and the receiver will be investigated. On-chip, there are several sources of parasitic capacitance at the input of the receiver which combine to generate a shunt capacitance C: the bondpad,  $C_{BONDPAD}$ , the ESD protection devices,  $C_{ESD}$ , and receiver input,  $C_{RX}$ .

Figure 4.1: Receiver input lumped element model with a primary-only ESD protected circuit.  $C = C_{BONDPAD} + C_{ESD} + C_{RX}$

# 4.3 Receiver Input Transfer Function

#### **4.3.1 Transfer Function Derivation**

Using a lumped element model of the receiver permits the derivation of a transfer function, H(s), in the Laplace domain to relate  $V_{IN}$  to  $V^+$ .

$$H(s) = \frac{V_{IN}}{V^+} = \frac{a_0 + a_1 s + a_2 s^2 + \dots + a_m s^m}{1 + b_1 s + b_2 s^2 + \dots + b_n s^n}.$$

(4.1)

Deriving the transfer function of a multiple element RLC circuit can be tedious, and thus it is preferable to use short-cuts to obtain the coefficients, see, for example, [20]. Once the coefficients are obtained, the transfer function can be utilized to perform a root locus analysis for the elements of the model.

In this dissertation, it is assumed that the termination has been matched to the characteristic impedance of the trace, i.e.,  $R_{TERM} = Z_0$ . The effect of mismatch between the termination and characteristic impedance can also be investigated through the methods presented, but this dissertation will focus on the effect of the parasitic reactive elements. The transfer function for the circuit of Figure 4.1 is

$$H(s) = \frac{V_{IN}}{V^+} = \frac{\frac{1}{2}}{1 + \frac{1}{2}(\frac{L}{Z_0} + Z_0 C)s + \frac{LC}{2}s^2}.$$

(4.2)

## 4.3.2 Transfer Function Coefficient Derivations

To derive the coefficients of H(s), the methods presented in [20] are utilized. The circuit in Figure 4.1 has no significant zero since no reactive element can be infinite valued without making the resultant transfer constants,  $H^{ijk...}$ , zero [20]. Therefore,

$$a_i = 0, \text{ for } i \ge 1. \tag{4.3}$$

Since the numerator of the transfer function is a constant, no finite zeros exist. Solving for the DC gain,

$$a_0 = \frac{R_{TERM}}{Z_o + R_{TERM}} \tag{4.4}$$

$$=\frac{1}{2}.$$

(4.5)

The circuit of Figure 4.1 has two reactive elements; therefore,

$$b_i = 0$$

, for  $i \ge 3$ . (4.6)

Solving for the two denominator coefficients,

$$b_{1} = \frac{L}{Z_{o} + R_{TERM}} + (Z_{o} || R_{TERM})C$$

(4.7)

$$=\frac{1}{2}(\frac{L}{Z_{o}}+Z_{o}C)$$

(4.8)

$$b_2 = \frac{L}{Z_o + R_{TERM}} R_{TERM} C \tag{4.9}$$

$$b_2 = \frac{LC}{2} \tag{4.10}$$

# 4.4 Receiver Input Root Locus

To determine the pole locations of H(s), let us define, and set to zero, the denominator, D(s), of (4.2)

$$D(s) = 1 + \frac{1}{2} \left( \frac{L}{Z_o} + Z_o C \right) s + \frac{LC}{2} s^2 = 0.$$

(4.11)

To demonstrate how the magnitude of the parasitic capacitance, C, impacts the poles of the receiver input, a root locus analysis will be performed. Traditionally, root locus analysis is performed on closed-loop systems with feedback, and the forward gain is utilized as a variable. In this dissertation, the root locus analysis will instead demonstrate how the receiver input poles change as a function of the parasitic capacitance. Rearranging (4.11) in an attempt to generate an equation suitable for root locus analysis produces

$$1 + C \frac{\frac{Z_0}{2} s + \frac{L}{2} s^2}{1 + \frac{L}{2Z_0} s} = 0.$$

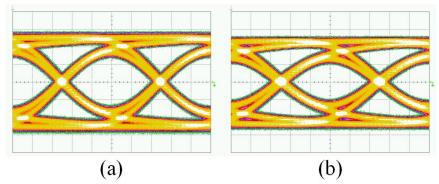

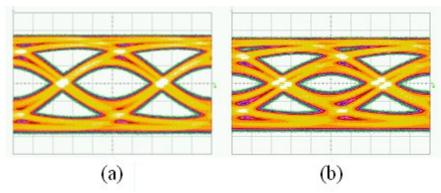

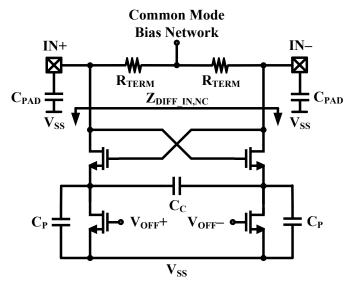

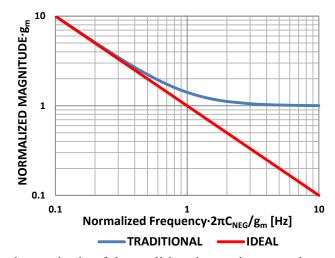

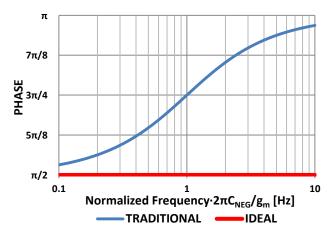

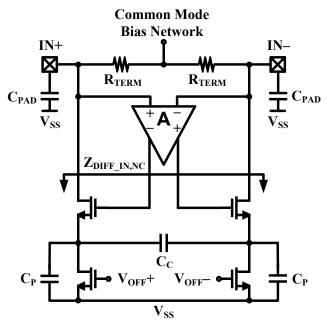

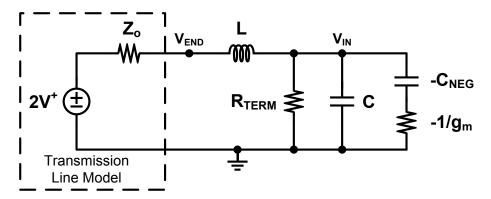

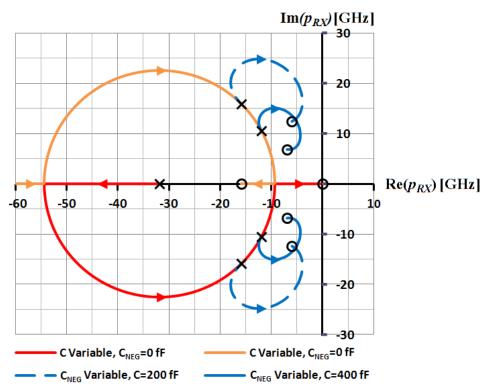

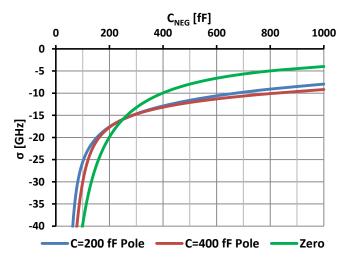

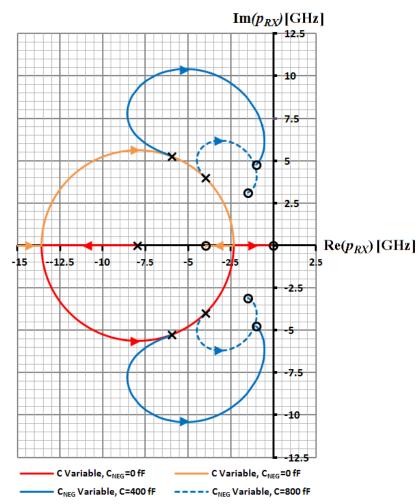

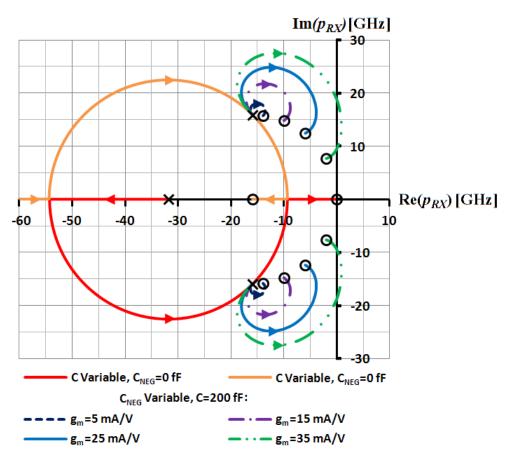

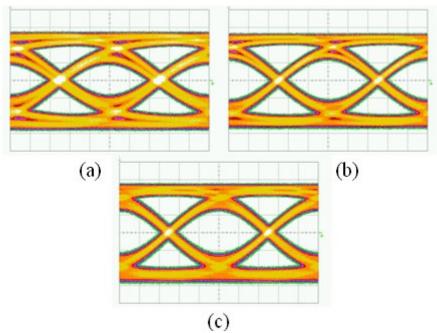

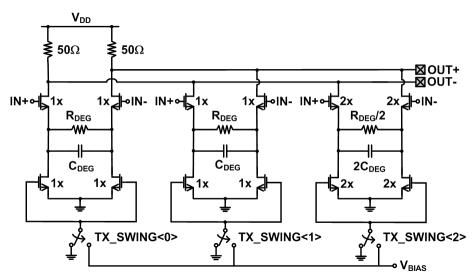

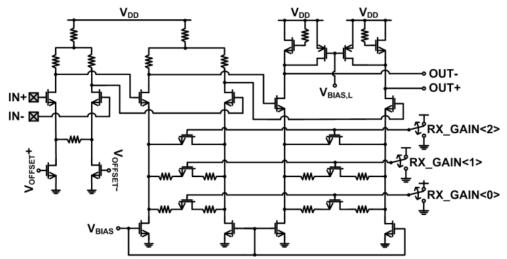

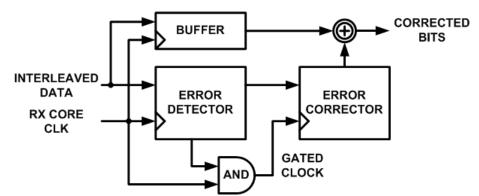

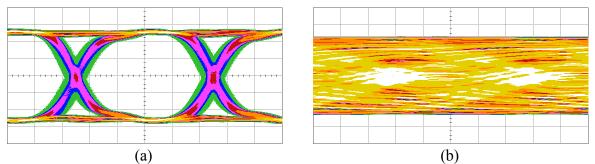

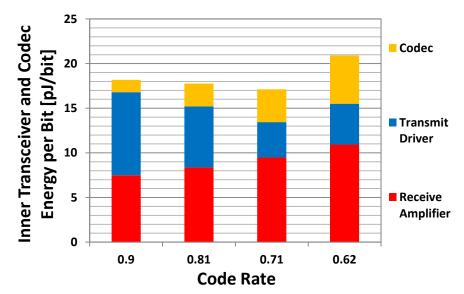

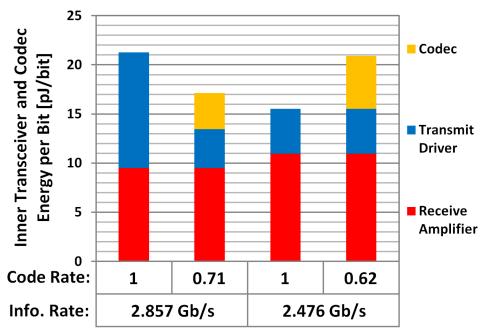

(4.12)