# DESIGN AND EVALUATION OF INFORMATION FLOW SIGNATURE FOR SECURE COMPUTATION OF APPLICATIONS

BY

PRATEEK PATEL

### THESIS

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2012

Urbana, Illinois

Adviser:

Professor Ravishankar K. Iyer

### ABSTRACT

This thesis presents an architectural solution that provides secure and reliable execution of an application that computes critical data, in spite of potential hardware and software vulnerabilities. The technique does not require source code of or specifications about the malicious library function(s) called during execution of an application. The solution is based on the concept of Information Flow Signatures (IFS). The technique uses both a model-checker-based symbolic fault injection analysis tool called SymPLFIED to generate an IFS for an application or operating system, and runtime signature checking at the level of hardware to protect the integrity of critical data. The runtime checking is implemented in the IFS module. Reliable computation of data is ensured by the critical value re-computation (CVR) module.

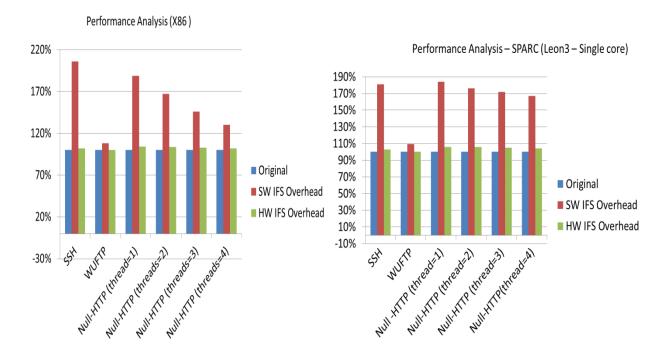

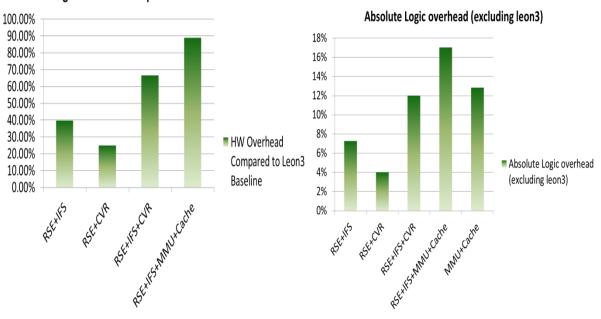

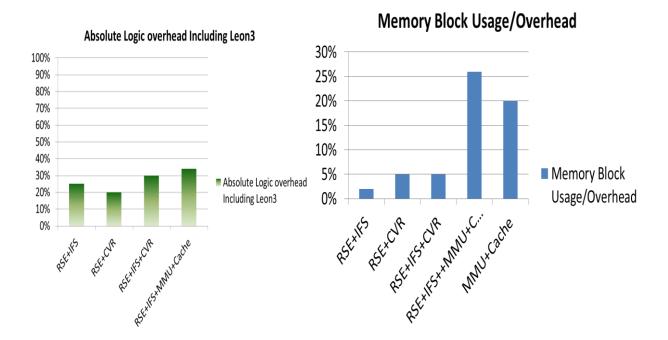

Prototype implementation of the signature checking and reliability module on a soft processor within an FPGA incurs no performance overhead and about 12% chip area overhead. The security module itself incurs about 7.5% chip area overhead. Performance evaluations indicate that the IFS module incurs as little as 3-4% overhead compared to 88-100% overhead when the runtime checking is implemented as a part of software. Preliminary testing indicates that the technique can provide 100% coverage for insider attacks that manifest as memory corruption and change the architectural state of the processor. Hence the IFS and CVR implementation offers a flexible, low-overhead, high-coverage method for ensuring reliable and secure computing.

### ACKNOWLEDGMENTS

This project drew upon the efforts and insights of many people, without whom it could not have succeeded. I am grateful for the support and guidance offered by my adviser, Ravishankar K. Iyer. I also deeply appreciate the insights and encouragement offered by Prof. Zbigniew Kalbarczyk. Thanks also to Prof. Nithin Nakka, who played a pivotal role in helping me through the design process; Karthik Pattabiraman, who produced the SymPLFIED framework and LLVM instrumentation utilized by this project during the initial phase; and Flore Yuan, who was instrumental in resolving issues related to evaluation and providing insights on SymPLFIED. Additionally, I would like to thank all the other members of the DEPEND research group for being so cooperative and encouraging me throughout the process. This project could not have produced as the working prototype that exists today without the hard work and contributions of the aforementioned individuals. Finally, thanks to my friends and family, who supported me during this process.

## **TABLE OF CONTENTS**

| CHAPTER 1 | INTRODUCTION1                                    |   |

|-----------|--------------------------------------------------|---|

| CHAPTER 2 | RELATED WORK7                                    |   |

| CHAPTER 3 | INFORMATION FLOW SIGNATURE FOR DATA INTEGRITY    | б |

| CHAPTER 4 | SYMPLFIED                                        | 7 |

| CHAPTER 5 | RELIABILITY AND SECURITY ENGINE (RSE)4           | 1 |

| CHAPTER 6 | INFORMATION FLOW SIGNATURE MODULE: ARCHITECTURE4 | 6 |

| CHAPTER 7 | QUALITATIVE ANALYSIS: INSIDER ATTACK             | 7 |

| CHAPTER 8 | RELIABILITY AND SECURITY: UNIFIED FRAMEWORK6     | 8 |

| CHAPTER 9 | RESULTS AND CONCLUSIONS                          | 5 |

| REFERENCE | .8:<br>                                          | 5 |

### **CHAPTER 1**

### INTRODUCTION

Memory corruption attacks represent a major part of security attacks reported in recent years [1]. Applications written in unsafe languages like C or C++ are still numerous and are vulnerable to attacks exploiting memory errors like buffer overflow and underflow [2], [3], dangling pointers [4], or double frees [5]. Theft and modification of sensitive information on computer systems contribute to billions of dollars in annual losses and often reflect organized crime.

As for defensive techniques, the most complete solutions often incur either high runtime or memory space overhead (e.g., duplication of critical data). Current software-based security techniques tend to focus on remote vulnerabilities, such as buffer overflow attacks, format string attacks, and other memory corruption attacks, looking either to "plug" every potential hole in the software, or to make sure the statistical likelihood of a successful attack is extremely low. Several hardware-based runtime security techniques have also emerged to prevent similar classes of attacks. These techniques improve upon the performance overheads of the software-based techniques. Techniques to detect anomalous execution based on control flow monitoring have also been proposed to protect against code injection into an application. However, these approaches focus on defending against attacks rather than protecting critical data.

The piecewise nature of current defenses against computer security vulnerabilities continues to allow malicious attackers to gain unauthorized access into computer systems. Hardware defenses against malicious tampering can ensure that attacks are detected reliably and nearly instantaneously. The Reliability and Security Engine (RSE), a low-level interface to the internal signals of a microprocessor, is a generic hardware framework that can be leveraged by a hardware designer to implement powerful mechanisms in modules that improve the reliability and security of a computer system [6]. The RSE presents a standard interface of pipeline signals that can be used to monitor the state of a processor and ensure reliability and security of the executing code. Because the RSE gives low-level access to processor signals, it is possible to develop techniques that can guarantee the integrity of data within a system by ensuring trustworthy execution of code that computes these data. In addition to providing such guarantees, RSE modules can be designed so that they have no effect on performance and little hardware area overheads on the host processor. The Information Flow Signatures (discussed in this thesis) technique for data integrity implemented as RSE modules does exactly this. Using the technique, it is possible for a software developer to select which critical data must be protected within a program or operating system and to have the data automatically protected during runtime. Because the runtime protection happens at a low level in hardware, it is possible to detect security violations with extremely low latencies, thus allowing action to be taken before corruption of data occurs.

### **1.1 Motivation**

Insider attacks have been widely reported in the financial and critical infrastructure sectors [7, 8], in which the attackers' goals have been financial gain and disruption of essential services, respectively. Such attacks are becoming increasingly prevalent due to the outsourcing of software components, often spanning geographic boundaries, and the increased distribution of

libraries and third-party modules over the internet. Also, as process technologies continue to shrink and margins decrease [9], the likelihood of memory corruption errors, which impact an application's integrity [10], is on the rise. Further, as critical systems increasingly deploy commodity components, there is a greater opportunity for malicious individuals or nation-states to launch such attacks. Therefore, insider attacks are underrepresented in the literature and will become increasingly important in the future.

Application-level insider attacks are particularly hard to detect because third-party modules and library functions are often distributed in binary form, and their source code is not available. Even if the code is available, only a detailed security audit can find logical loopholes in it, and such detailed audits are time- and effort-intensive. Further, the malicious library or module may exhibit its malicious behavior only under exceptional situations triggered by the attacker's input. Such inputs are unlikely to be provided during testing unless exhaustive testing is performed, which is often impractical. Finally, the insider has almost unrestricted privileges to write to any part of the application data space or execute arbitrary code. Under those circumstances, it is extremely difficult to identify a specific module or library as the cause of the attack, so insiders can effectively cover their tracks. Finding these attacks requires extensive instrumentation of the application and incurs high performance and resource overheads or hardware requirements [11]. These overheads represent more than an annoyance; for example, time-critical systems may not be able to accommodate a high runtime overhead, while embedded systems may not be able to accommodate excessive hardware requirements. Moreover, such techniques also detect a number of benign errors (errors that have no detrimental impact on a program's execution) [12] and therefore unnecessarily expend computational resources on their detection. Several

hardware-based runtime security mechanisms based on these techniques have also emerged to prevent similar classes of attacks. Hardware-based runtime security techniques, covered in detail in Chapter 2, improve upon the performance overheads of software-based techniques. Techniques to detect anomalous execution based on control flow monitoring have been proposed to protect against code injection into an application [13]. However, these approaches focus on defending against attacks rather than protecting critical data. For example, with the increasing processor power available as a result of from shrinking process technology, computers can now efficiently run many applications simultaneously on the same system. While some of these applications are well-written and secure, others are not. Insecure applications can pose a threat to those that are secure, since current security techniques do not focus on protecting the target of attacks (critical data such as passwords or user authentication variables), but instead look to mitigate classes of attacks. In the face of such vulnerabilities, it is worthwhile to consider security techniques that operate under the assumption that a "hole" in the virtual fence may be found at any time. Thus, by protecting the critical data target of malicious attacks, a technique may prevent both current and future attack vectors.

In order to minimize the performance and area overhead associated with duplication detection mechanisms, a method is proposed whereby only critical variables are considered for detection.

#### **1.2 Contributions**

This thesis presents a new method for application source code analysis to derive the critical signature along with the hardware-implemented enforcement of Information Flow Signatures. The implementation ensures that, during runtime, security-critical data are computed according

to source code semantics, even under the threat of hardware or software vulnerabilities. If an attacker attempts to tamper with the protected program execution or data used by the application, the system will be notified so that it can take appropriate actions. Though this technique can also be used to provide protection against a wide range of memory corruption attacks, we focus on the hardware-based mechanism for protecting security-critical data against malicious tampering due to external and insider attacks.

The specific contributions of this thesis are:

- Design, implementation, and demonstration of IFS (Information Flow Signatures) that check hardware for trustworthy execution of instructions computing critical data. An FPGA-based prototype has been developed with real-world applications to demonstrate the efficacy of the concept.

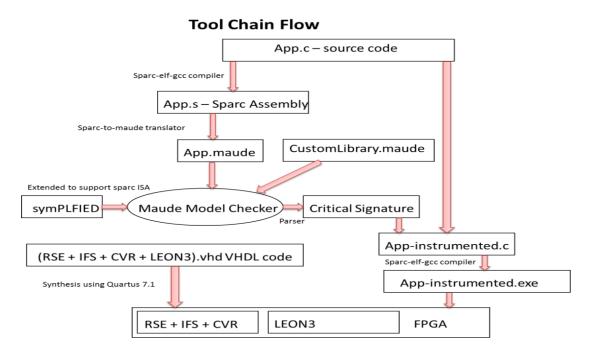

- 2. Augmentation of the Maude model-checker-based SymPLFIED [14] tool to support (i) a prototype (SPARC-Leon3-based) architecture, (ii) exhaustive symbolic fault injection for application analysis to derive the signature of the application, and (iii) application instrumentation to facilitate an interface between the application and IFS checking hardware.

- 3. Qualitative analysis of the technique's coverage of memory corruption (generic and targeted) attacks and detailed evaluation of hardware resource overhead and performance overhead for real-world applications.

### **1.3 Organization**

The rest of the thesis is organized as follows. In Chapter 2 we describe some of the related security work. Chapter 3 addresses the basic concept of the IFS, the attack model, the software implementation, and, briefly, the new proposed analysis method and hardware-based architectural solution. In Chapter 4 we introduce the tool SymPLFIED, explain how it is used for source code analysis, and we describe the extensions made to it to support IFS. The chapter also describes in great detail the limitations of the previous compiler-based static analysis and how symbolic error injection overcomes all these limitations. Chapter 5 describes the Reliability and Security Engine, a hardware-based framework for monitoring of applications, and its new modified architecture for easier coding and extensibility. Chapter 6 gives more details on the architectural features of the IFS module, its runtime checking operation, and how a hardwarebased solution removes the vulnerabilities present in the software-based IFS implementation. Chapter 7 details the nature of insider attacks, the importance of preventing such attacks, different attack scenarios, and the efficacy of the IFS method in detecting those attacks. Chapter 8 describes another major contribution of this thesis, which is the design and implementation of a unified framework for security and reliability; hence, we briefly describe the reliability module and how it was integrated with the security module and the main processor on a single fabric. Finally, Chapter 9 presents results that include hardware footprints for different configurations and performance overhead due to IFS, along with conclusions and plans for future work.

### **CHAPTER 2**

### **RELATED WORK**

A multitude of techniques have been proposed to address the security concerns discussed in the Introduction. Some of these techniques offer low-level detection or correction but operate in a manner largely indifferent to the needs of the application being protected. To support application-aware detection, several techniques utilize static analysis of application source code or dynamic analysis of application invariants to provide error detection services that are geared to the needs of individual applications. Others utilize hardware and software redundancy; such techniques rely on either software duplication or hardware duplication. All of these methods have their benefits and drawbacks. The properties of a secure software application can be summarized as follows:

- 1. Instructions cannot be directly stolen, inferred, or modified;

- 2. Data cannot be directly stolen, inferred, or modified;

- 3. Execution flow cannot be tampered with or monitored;

- 4. The application and all of its subcomponents can only be used by authorized entities;

5. Authorized users cannot be denied usage of or access to an application or its subcomponents.

Nearly all direct attacks against software, despite variations in methodology and sophistication, exhibit intentions that fall under one of the previously stated protection properties. While it is generally accepted that no system can completely protect against all classes of threats, the

properties listed above provide a general upper bound on protection goals for all systems that attempt to protect software.

#### 2.1 Security Architectures

The following sections present an overview of architectures for securing software. Discussions of design issues associated with software protection architectures can be found in [15] and [16]. These design issues are extended in [17], which discusses similar issues arising from the combination of software security and multiprocessors. The purpose, protection, and design assumptions of security architectures range from custom-designed processors to small jump tables.

The concept of using hardware to protect software was first publicly introduced by Robert Best, who patented the idea of a crypto-microprocessor in the early 1970s [18], [19]. The crypto-microprocessor was a microprocessor outfitted with encryption hardware that could decrypt encrypted memory for a single application using a single key. This concept was again revisited in [20] and was realized as a commercial product in the Maxim DS5002FP [21] secure microcontroller, which could access 128kB of encrypted random access memory (RAM).

Dyad [22], [23] was one of the first architectures to rely on a secure micro-kernel. Dyad examined the necessary protocols and procedures for networked hosts utilizing secure coprocessors. Specific applications of interest were audit trails, electronic transactions, and copy protection. The secure coprocessor was responsible for providing a secure compartment for execution and security functionality not available in the OS. The secure coprocessor was not

responsible for enforcing security policies, because the OS was booted securely and verified using the coprocessor. Keys and other secret material were assumed to be stored exclusively on the coprocessor's internal, nonvolatile memory. The Dyad architecture was neither simulated nor implemented.

The Cerium [24] architecture created security by utilizing a tamper-resistant CPU in coordination with a micro-kernel. The micro-kernel, much like the secure kernel used in Dyad, was responsible for providing process separation and was specifically responsible for address space separation, protection during cache-evicts, cryptographic processes (e.g., authentication, encryption/decryption), and certificate creation/signing. The Cerium architecture was neither simulated nor implemented. Similarly, the ChipLock [25] architecture relied on a secure microkernel, in addition to processor modifications, to provide integrity and confidentiality for both instructions and data. Unlike Cerium, however, ChipLock placed security functions in hardware and not in the micro-kernel. Another security architecture proposed by Gilmont et al. [26], [27] modified traditional, architectural memory management structures; included a hardware cipher unit and a permanent memory for storing keys; and appended TLB, page registers, and an L1 cache interface to allow for prefetching. This architecture moves security farther toward the outside of the processor but still keeps it within the processor boundary. Gilmont's MMU security architecture fails to address the protection of data and ignores issues related to operation in a multitasking environment, such as shared libraries and different security levels. The architecture was evaluated using simulation and showed overhead costs between 2.5% and 6%.

An important aspect of hardware-based security solutions that modify or redesign processor internals is the effect of adding the additional security hardware to the processor. The additional hardware consumes logic resources that would otherwise be used for cache or memory that are essential to performance. Also, the additional security hardware might also impact timing and other requirements. Together the loss of logic resources and possible timing impact could severely hinder performance. These critical system issues have not been addressed in the design and characterization of existing processor redesign software security solutions.

Other recent efforts at placing security features at the chip boundary include the SafeOps architecture by Zambreno et al. [28], [29] and CODESEAL [30], developed by Gelbart et al. The SafeOps architecture attempted to protect software integrity using a combined compiler and FPGA approach. The compiler examined the executable for sequences of register usage and employs this knowledge to check for integrity and consistency. Additionally, the compiler could embed several nonessential instructions to add to the register usage patterns and perform opcode obfuscation. At execution time, instructions were pushed through the FPGA hardware that compared the register sequence to the register sequence established in the static analysis. If discrepancies were detected, the FPGA hardware halted the processor. SafeOps was evaluated using SimpleScalar [31], which showed average performance degradation to be around 20%. The CODESEAL architecture extended the SafeOps architecture to include instruction decryption and hashing of blocks of information. This architecture was also validated using SimpleScalar and demonstrated performance degradation between 4% and 42%, depending on the type of protections incorporated and the benchmark applications.

### 2.2 Software Solutions

Terra [32] introduced the idea of trusted virtual machine monitors that compartmentalize applications or sets of applications using the virtual machine concept. Terra relied on the existence of a tamper-resistant platform. Obfuscation methods that attempt to complicate program analysis have also been explored.

Wang [33] used a compiler implementation that produced obfuscated programs that made static analysis of the program difficult. The obfuscated software is unobfuscated by the operating system using a runtime interpreter. Duvarney et al. [34] presented the idea of extending traditional executable formats, particularly the Executable Linking Format (ELF) [35], to include security information. Their particular application appended standard ELFs with information that was used to perform runtime monitoring, static monitoring, and program transformation. This allowed security information to be added postcompile if necessary. Another platform under development in the commercial sector under the names of the Next Generation Computing Base (NGSCB) [36], Trusted Computing Platform Alliance, and Palladium utilizes a combination of hardware and software techniques to provide protection from software-based attacks. The NGSCB is not designed to prevent physical attacks on the local machine. NGSCB utilizes a small security coprocessor called a *trusted platform module*, which is attached to the motherboard to store and limit access to sensitive information, e.g., keys and certificates.

#### **2.3 Hardware-Based Security Solutions**

The first class of hardware solutions for protecting execution flow aims to provide execution flow confidentiality. Zhuang et al. [37] utilized a fairly simple obfuscation mechanism, called a

*shuffle buffer*, to complicate memory and address access monitoring as a method for gaining information about an executing application. The shuffle buffer is a circular memory of recently accessed memory blocks. When a memory block is accessed, a block is replaced in the shuffle buffer, and the information being replaced in the buffer is written back to memory. This process attempts to create a "random" memory access pattern. The tracking of memory blocks throughout memory as a method for breaking the obfuscation method was not addressed.

Another similar architecture by Zhuang et al., named HIDE [38], also examined the protection of instruction access sequences, likely obtained (leaked) by monitoring memory or disk accesses, using hardware. The HIDE architecture attempted to make instruction accesses independent of program execution using multilevel prefetch buffers in addition to a hot function set. As hot functions were identified and added to the set, the entire function block was prefetched and stored in the prefetch buffers. As the functions were requested, the prefetch buffers were accessed to retrieve the appropriate portions of the function. This required that the size of the function be added to the executable description such that the prefetch buffer hardware would know the appropriate amount of memory to allocate. Also, the prefetch controller was required to encrypt and decrypt memory for writing blocks back that have been encrypted with a different key such that blocks cannot be tracked as they are moved within memory. Evaluation of the HIDE architecture method was performed using the SimpleScalar [31] simulation platform and the SPEC benchmarks [39]. Performance degradation was shown to be approximately 38%.

Barrantes et al. [40] sought to prevent code injection attacks (that could potentially alter execution flow) by implementing a form of program obfuscation called *instruction set*

randomization. They proposed the production of a machine-specific executable using a pseudorandom sequence loaded at runtime that is XORed with instructions by an interpreter that resides in the process's virtual address space. The method was evaluated using an emulator and demonstrated a 5% performance degradation. Another approach for preventing invalid code injection was dynamic information flow tracking [41] that utilized the operating system to mark sources of information flow as possibly malevolent. The classification of information was used by a custom processor, which included architectural support at the TLB and registers, to tag information from these possibly malevolent sources. Tags were propagated to the data produced, if the data consumed contained tags. The SimpleScalar [31] was used to evaluate the architecture, which demonstrated modest performance degradation of around 5% and an approximate storage overhead of about 5%. The architecture does, however, require a custom processor and was not implemented.

The next two hardware architectures, basic block signatures [42] and runtime execution monitoring [43], used signature methods for verifying execution flow. Basic block signature verification attempted to prevent execution of unauthorized code by verifying runtime block signatures calculated by hardware with signatures created during the install process. The signatures were created during the install process using secret coefficients and the relative address of the basic block. Because this method verified the integrity of instruction sequences, access to the instruction pipeline hardware was necessary. The method was evaluated using traces from the SPEC [39] benchmarks for an Alpha processor. Analysis of the method compared the number of misses in the basic block signature table to the number of instruction cache misses. The results indicated that if the number of sets in the basic block signature is

sufficiently large, basic block signature misses are relatively small compared to the number of cache misses and should not contribute greatly to system performance degradation. Specific performance degradation numbers were not cited.

Runtime execution monitoring protected execution flow integrity by comparing precomputed hashes of basic program blocks after they were loaded into L1 caches. If the hashes calculated on instructions and data passing through to the fetch and load store units did not match the original hashes, an exception was raised. This method required the addition of hash compute and comparison hardware to the processor (behind caches) as well as a hash pointer instruction to the instruction set architecture (ISA). The concept was evaluated using the SimpleScalar simulation framework and SPEC2000 benchmarks. The additional hash information increased application size by 40% to 100%. Performance reduction ranged from 6.4% to 40% depending on hash block size, cache sizes, and memory bandwidth consumed retrieving hashes from memory.

#### 2.4 Formal Security Analysis

The goal of formal systems is to verify the operation of a subsystem or system, or interaction within a collection of systems, using formal methods. Formal methods have generally fallen into two categories: theorem proving and model checking [44]. Several generally accepted rules-of-thumb relating to the use and application of formal methods can be found in [45]. In the security domain, formal methods have been utilized to support claims concerning security. One of the initial uses of formal methods in the security domain was cryptographic protocol analysis [46], [47], which uncovered an attack on the Needham-Schroeder exchange protocol [48]. Other variations of formal protocol analysis [49], [50], [51] examine abstract state machines and team

automata as methods for examining cryptographic protocols. Lowe [52] made one of the first attempts at automating the protocol analysis process by creating a compiler, called *Casper*, which would generate process algebra descriptions automatically from a more abstract description. The analysis was completed by processing the algebras with a standard model checker.

Butler et al. [53] examined the use of formal methods for validating and modeling trust. Another area of interest is secure systems. With the arrival of the secure coprocessor (as discussed in Section 2.2.1), much effort was focused on formal verification of these systems, such as in [54]. A practical example of formal security analysis of a secure coprocessor, specifically the Infineon SLE88, can be found in [55]. The analysis utilizes a combination of model checking and theorem proving, called *interacting state machines*, that was created and applied to the Infineon SLE88 [56], [57], [58], [59]. Recently, several custom architectures have been proposed as methods to provide security functionality. These systems, like other hardware and/or software [60], are subject to functional verification and are also subject to security verification. For example, the security features of the XOM architecture [61], [62] were analyzed and verified using model checking on a scaled-down model; this was one of the few efforts to apply formal methods to security hardware.

### **CHAPTER 3**

### **INFORMATION FLOW SIGNATURE FOR DATA INTEGRITY**

### **3.1 Principles**

The Information Flow Signatures (IFS) technique is used to protect the integrity of critical data within an application or operating system. The data may be selected as the highest-priority security variables, such as variables that hold information about user authentication in an SSH application or structures containing information about processes currently running within an operating system.

The crux of the approach is to allow programmers to specify critical data in applications (i.e., data that are important for the application's secure execution) and ensure that the data cannot be corrupted by untrusted third-party libraries or modules. This enforcement is done at runtime using the Information Flow Signatures (IFS) of the critical data. The IFS represents the sequence of legitimate instructions that are allowed to write to the critical data from within the trusted module. If an instruction that is not part of the IFS attempts to write to the critical data, it is considered an attack. Similarly, if an instruction that is part of the IFS writes to the critical data in a different order than determined by the IFS, it is also considered an attack. Thus, only instructions within the IFS can write to the critical data, and only in the order in which they appear in the IFS.

#### **3.2 Attack Model**

In this work, we consider application-level memory corruption attacks that alter the integrity of an application. This section further explains the above definition.

**Application-level attacks:** The goal of an application-level attack is not to corrupt the behavior or gain control of the whole system (e.g., launch a root shell), but to alter the normal behavior of the attacked application (corrupted output, login with wrong password, etc.). Application-level attacks can be achieved by exploiting vulnerabilities (e.g., buffer overflow or format string), or by changing the code of an application (e.g., trojan). We focus on application-level attacks conducted by memory corruption.

**Memory corruption attacks:** All attacks that corrupt either data or the control flow of an application (or both) by overwriting data or addresses in memory are considered memory corruption attacks. They include, for example, the usual buffer overflow, integer overflow, and format string attacks, but also logic bombs or third-party libraries that modify memory locations, which they are not allowed to modify semantically.

In this work, we assume that the attacker's goal is to alter the integrity of data produced by the application, i.e., to corrupt data produced by the application. Therefore, we do not consider attacks targeting the confidentiality of data, where the goal is to steal information from the application. Furthermore, we assume in this work that the attacker does not want to crash the application. Any attacks that result in a system exception being raised or a system crash are considered to be "detectable" attacks and thus are not considered. In general, the IFS technique described here can be used to prevent data corruption attacks. The aim of the technique is to

preserve data integrity rather than its confidentiality. Hence, the technique does not address sidechannel attacks. The threat model assumes that the attacker can execute arbitrary code and overwrite program variables stored in both memory and processor registers. We assume all malicious memory accesses are visible to the processor pipeline. Thus, malicious DMA transfers are *not* covered by this threat model. We also assume that the IFS hardware is initialized prior to the attack conditions; thus, the technique protects against runtime attacks, but only if the correct signatures have been loaded into the hardware.

### **3.3 Software Implementation of IFS**

In this section we briefly describe the initial design and implementation of the Information Flow Signature Module. In the proposed approach, the portion of the program that manipulates the critical data (i.e., the trusted module) is statically analyzed and instrumented to ensure that runtime modifications of the critical data follow the language-level semantics of the application. This corresponds to static extraction of the backward slice of the critical data [63], and ensures that only the instructions within the slice can modify the critical data, and only in accordance with their execution order as specified by the program code. A third-party module or a memory corruption attack that overwrites the critical data or violates the established dependencies in the slice is detected. Because the approach ensures that information flows to the critical data in accordance with the program source code, we call it the *Information Flow Signatures (IFS)* technique.

**Invariants:** The instrumentation added by the IFS technique ensures that the following invariants are maintained at runtime.

1. Only the instructions that are allowed to write to data operands in the backward slice of the critical data (according to the static data dependencies) in fact do so.

2. The instructions in the backward slices of the critical data are executed in the order of their occurrence along a valid acyclic path in the program.

3. Either all the instructions in the backward slice along a control path are executed, or no instruction along the path is executed.

### 3.3.1 Phase 0: Identification of Critical Data (Carried Out by the Programmer)

The critical data in a program can refer to both program variables (i.e., local and global variables) and dynamically allocated memory objects on the heap. The programmer identifies critical data in the program through annotations in the source code. In the case of program variables (local or global), the annotations are placed on the definitions of the variables. In the case of dynamically allocated memory objects, the annotations are placed on the allocation sites (i.e., the instruction that makes the function call) in the program (e.g., calls to *malloc*). It is assumed that all objects allocated at an annotated *malloc* call are critical.

### 3.3.2 Phase 1: Static Analysis (Carried Out by Our Enhancements to the Compiler)

1. Extract intra-procedural backward slice of the critical data by identifying all instructions within a function in the program that can influence critical data. It is assumed that the function that manipulates the critical data is trusted, and its source code is available for the analysis.

2. For each instruction in the backward slice, insert an encoding operation after the instruction and pass the value computed by the instruction as an argument to the encoding operation.

3. Before every use of an operand that has been encoded in the backward slice, insert a call to the decoding operation and pass it the value returned by the encoding operation.

4. Generate the sequences of instructions for each acyclic control-flow path in the function. Do this for each function in the program.

5. Since we consider intra-procedural paths, add instrumentation functions at the beginning and end of function calls in order to push and pop the current state of the function's state machine on to a runtime stack (see phase 3). (State machines track the sequence of calls to the encoding functions and check if the program control flow is valid.)

### 3.3.3 Phase 2: Code Generation (Carried Out by Custom Programs)

6. Generate finite-state machines to encode the sequences of calls to the encoding operations within a function for all control paths identified in step 5. Mark the final state of each state machine as an accepting state.

7. Generate the encoding and decoding operations to check the data-values of the program as it executes (see phase 3). Also, check the validity of the program control-flow using the state machines derived in step 6.

8. Track the runtime path based on the state machines generated in step 6. If the path does not correspond to a valid path, raise an alarm and stop the program.

20

9. Encode data values depending on where the encoding operation is called in the original program. Check the value for consistency by decoding it before its use, i.e., check if the decoded value matches the encoded operand. If the value is inconsistent, raise an alarm and stop the program.

**Slicing Algorithm:** The backward slices of the critical data are computed on a path-specific basis, i.e., each execution path in the function is considered separately for slice extraction. This is based on our earlier work on extracting backward slices for detecting transient errors in programs [64].

**State machines:** The state machines track the sequence of calls to the encoding functions and check if the program control flow is valid. The state is tracked on a per-function basis, since we consider only intra-procedural slices. A separate stack is maintained at runtime to push and pop the current state of the state machine (for the function) at the beginning and end of function calls. At the entry point to a function, the corresponding state machine is reset to the start state. Similarly, the state-machine state is checked just before the function returns to ensure that the state machine is in an *accepting state*, i.e., the state machine has accepted the observed sequence of encoding calls (invariant 3). Finally, we check that every encoding call executed by the program corresponds to a valid state transition from the current state of the state machine (invariant 2).

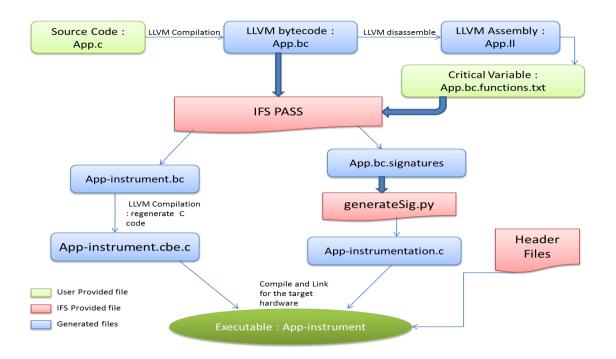

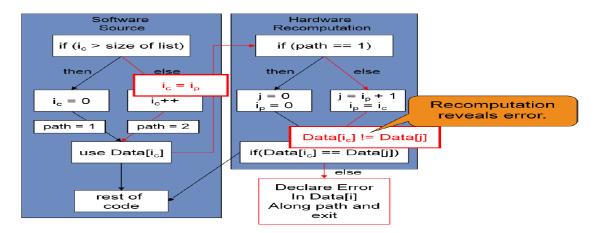

Fig. 3.1: Tool chain for software implementation of IFS

Figure 3.1 describes the tool chain for implementing IFS checks in software. There are a number of limitations and shortcomings in this approach which we overcome with our new proposed method, for which a prototype has been developed to demonstrate efficacy. The major limitations come from the preprocessing method of the code, which is based on compiler static analysis; it is discussed in detail in Chapter 4, where the new analysis method based on model checking and error injection has been described and contrasted with the compiler-based analysis. The approach involves major performance degradation and vulnerability due to the inherent problems of handling everything (encoding and decoding operations) in software. The instrumentation is done at a level of intermediate code that is still high-level C code, hence providing a vulnerable window for attackers to attack the code successfully without being detected. By implementing the IFS module in hardware, we reduce this vulnerable window to 0

for any practical purpose and also have a huge performance boost, which is described in Chapter 6 (in the discussion on advantages of hardware-based IFS) and Chapter 8 (performance results).

### **3.4 New Approach and Algorithm**

*Critical data* is defined as any variable or memory object that, if corrupted by an attacker, can lead to security compromise of the application. The programmer identifies critical data through type annotations in the code. The approach consists of two phases:

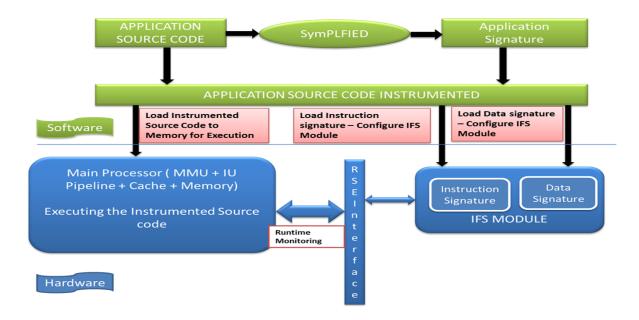

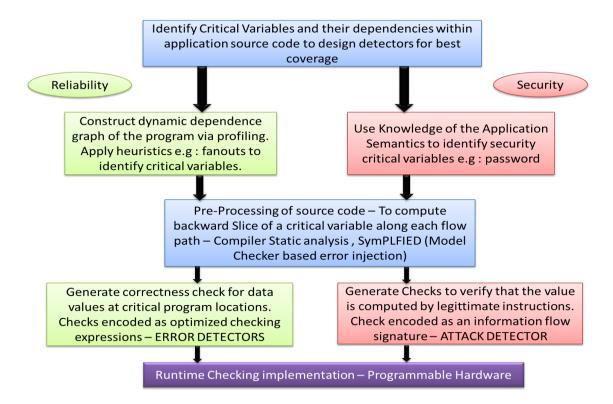

- A compile time phase to extract the trusted signature of the application source code. This is done completely in software. As described (Fig. 3.2), the application source code has to go through SymPLFIED analysis to extract the application signature, which is used to instrument the application source code.

- A runtime phase, in which the IFS module enforces the integrity of critical data using the trusted signature of the application configured in the hardware itself. It does so at the hardware level. The instrumented source code is loaded onto the processor, which, upon execution, configures the IFS hardware with the application's instruction and data signature. Later, during the course of execution, the IFS module enforces the integrity of critical data using the signature initially loaded.

Fig. 3.2: Conceptual design flow: IFS

### 3.4.1 Compile Time Phase

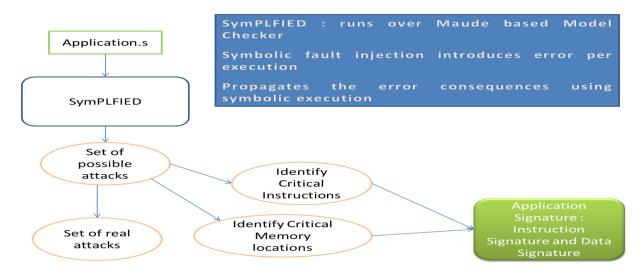

We leverage a formal tool, SymPLFIED [14], to find the minimum yet exhaustive set of critical data locations that one needs to protect. SymPLFIED uses symbolic execution and fault injection to comprehensively enumerate all possible memory errors that can be corrupted by malicious instructions to cause a program failure.

SymPLFIED runs on top of the Maude model checker and models applications' execution at the assembly level using rewriting logic. SymPLFIED-supported symbolic fault injection introduces a single error per execution in one memory location and propagates the error's consequences using symbolic execution. The results from the symbolic fault injections are then used to determine the complete set of memory locations and the corresponding critical stores that need to be protected. This set of memory locations and critical store instructions forms the signature for an application. The original program is instrumented to load the signature in the IFS module

during the runtime. More details on the compilation and extraction of signatures for an application's source code are provided in the next two chapters, which address the SymPLFIED analysis and loading of signatures to the hardware module.

Fig. 3.3: Proposed compilation phase framework

Figure 3.3 shows the conceptual flow of the proposed compilation phase framework. SymPLFIED [14] exhaustively simulates and analyzes the processor state at instruction-level granularity and hence helps in identifying all possible sources of vulnerabilities that can be exploited to achieve the attacker's goal, namely, compromise of the integrity of critical data being computed by the application. The set of real-world attacks is a subset of all the possible attack scenarios analyzed, and hence we claim that the signature extracted by the proposed framework (by analyzing and parsing the successful attack cases) can theoretically provide 100% coverage. The obtained coverage is verified with simulations and error injection experiments discussed later in this thesis.

### 3.4.2 Runtime Phase

The instrumented code is loaded onto the processor. The coprocessor instructions (in the SPARC instruction set) are modified to act as an interface between the application running on the main core and the signature-checking hardware. Hence, the checking is done in parallel with minimum performance overhead due to instrumented code. The instrumented code also configures the IFS hardware to load the corresponding critical instruction and data signatures during the initialization of the program. The IFS module then enforces the integrity of the critical data to be maintained during the execution of the application.

The instrumentation added by the IFS technique ensures that the following invariants are maintained at runtime.

1. Only the instructions that are allowed to write to data operands in the backward slice of the critical data (according to the static data dependencies) in fact do so.

2. The instructions in the backward slices of the critical data are executed in the order of their occurrence along a valid acyclic path in the program.

### **CHAPTER 4**

### SYMPLFIED

In this chapter we discuss the formal model-checker-based tool called SymPLFIED and how it is extended to support the analysis required for extracting application-specific signatures to configure the Information Flow Signature module and hence monitor the application during the execution of the instrumented source code.

SymPLFIED [14] is a program-level formal framework that runs on top of the Maude model checker. It has been designed to enable reasoning about application vulnerabilities using symbolic execution and model checking. We leverage the symbolic fault-injection capabilities of SymPLFIED along with the flexible design of the machine model in order to design, model, and verify detection mechanisms. Critical variables along with associated critical code are identified using SymPLFIED's symbolic fault injector.

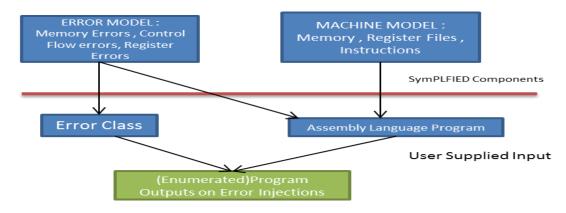

Fig. 4.1: Conceptual design flow of SymPLFIED

SymPLFIED is implemented using rewriting logic. Equations are used to model deterministic actions such as the program execution or memory and register lookups. Rules are used to introduce nondeterministic transitions when errors are injected. Figure 4.1 describes the conceptual design components used in the Maude-based model checker SymPLFIED. Error model describes the class of errors to be analyzed; "machine model" describes the architectural state of the hardware processor, and the assembly of the source code is the input to the processor.

A machine state describes the states of the registers, memory, program counter, etc., during the execution of an application. The whole application's execution consists of going from one machine state to another through transitions. In other words, transitions modeling the fault-free execution of an application are written with equations, and transitions involving errors are written with rules.

#### 4.1 SymPLFIED: Extended Implementation for SPARC

The existing tool SymPLFIED emulated MIPS ISA. We extended the tool to support the SPARC instruction set architecture because our experimental platform is based on the open-source Leon3 processor, to which we attached the custom-designed IFS hardware to support the runtime error checking of the application.

The extension of the existing tool consisted of two implementation phases:

- 1. We modified the front end of the SymPLFIED tool to support all the instruction formats of SPARC V8. The execution behavior of the new instructions, which determine the states of the application and the processor after a particular instruction is emulated, was implemented as re-writing rules for Maude. The dependency and define list for the SPARC instructions that define the resulting values (on execution), the initial state (of the processor), and the dependency of an instruction on registers and memory locations was re-implemented. For the new Maude instructions defined, we implemented the state transition functions that would define the subsequent states after the execution of a particular instruction by adding rules to the constraint checker for Maude.

- 2. We implemented a translator that interprets the SPARC V8 assembly instructions and maps them to the corresponding Maude formalism to enable symbolic execution of instructions. A Maude instruction representation mimics the behavior of the corresponding assembly instruction in SPARC. To incorporate all the unique features of the SPARC-based Leon3 architecture, a single instruction can map to multiple Maude instructions. Unlike MIPS, SPARC uses register windows to minimize access to memory. For example, to support function calling conventions, for instructions like *save* and *restore*, Leon 3 passes the top 6 arguments through the output registers. These registers overlap with the set of input registers for the function called. Consequently, before the function is called, a *save* instruction is executed to increment the register windows. At the same time, in the stack frame layout, the top 64 bytes are reserved for pushing the register values onto the stack in case of register spilling, which happens once the processor runs out of new sets of register windows. To mimic this behavior, we intentionally push the

registers onto the stack every time a save instruction is executed (as described in Figure 4.2) and reload the registers when the *restore* instruction is executed, which in the processor decrements the window pointer and returns the access to the previous set of register windows. Pushing registers onto the stack frame, even when the processor has available register windows that can be used, increases the memory locations that must be protected, which is fine because in an actual system (with kernel and other processes running simultaneously), the resource usage for a processor at any particular time is unpredictable. Thus the methodology proposed in this thesis should abstract away such concerns while the application's source code is being instrumented.

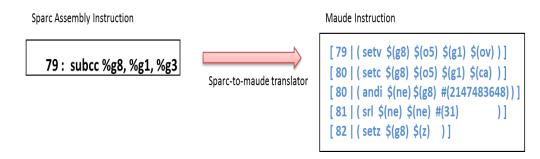

| Sparc Assembly Instruction                            | Maude Instruction                                                                                                                    |                                             |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 79 : save %sp, -120, %sp<br>Sparc-to-maude translator | [ 0   ( addi \$(sp) \$(sp) #(-120)<br>[ 1   ( savest \$(l0) #(0) \$(sp)<br>save reg  1 save reg  2<br>Save all 16 registers on stack | )]<br>)] save reg l0                        |

|                                                       | [ 17   (movsp \$(i7) \$(o7) ) ] rename reg o7 -> i7 rename reg o1 -> i1rename all output registers to input registers                |                                             |

|                                                       | [ 24   ( subi \$(fp) \$(sp) #(-120)                                                                                                  | )] – set the value of new %fp<br>to old %sp |

Fig. 4.2: Example of mapping a single SPARC instruction to multiple Maude instructions to accurately simulate the architectural state of the processor

Another case that requires mapping of a single instruction to multiple Maude instructions is the instruction that sets condition code registers. Unlike the MIPS architecture, which does not have condition code registers and uses *slt* instructions and a comparator to make branching decisions, the SPARC architecture uses four condition code registers to make branching decisions. Mapping of a complex instruction to multiple Maude instructions gives us better granularity in cases where we can set breakpoints, even within an atomic instruction, and makes it easier to

debug and monitor the architectural state of the processor. Also, it offers a better way to extend Maude to different instruction set architectures, as opposed to redesigning complex Maude instructions to map to specific complex instructions, which would increase the verification complexity of the model checker. While mapping a single instruction to multiple instructions in cases like the one in Figure 4.3, one has to be careful to avoid including any redundant memory locations as a part of the backward slice.

Fig. 4.3: Example SPARC instruction mapped to multiple Maude instructions

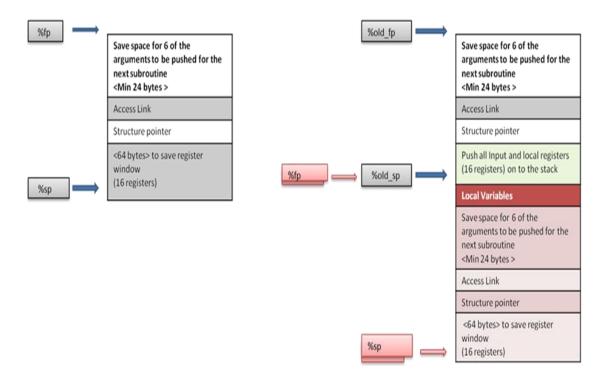

### 4.2 Stack Memory Management in SymPLFIED

In order to emulate the SPARC architecture behavior, the *save* instruction is translated to multiple *save-store* instructions in Maude, which push the set of input registers onto the stack space allocated to the called subroutine. Similarly, on the *restore* instruction, we pop the values from the stack into the corresponding registers in the reverse order before tearing down the stack frame for the called function. The stack frame layout after every subroutine call is shown in Fig. 4.4.

Fig. 4.4: Stack memory frame layout before and after subroutine call in SymPLFIED

#### 4.3 Register File Management for SPARC Architecture in SymPLFIED

When a function call is made, all the input and local registers are pushed onto the stack frame. The save instruction, which is mapped to multiple movsp instructions to emulate a behavior similar to the overlapping of registers, is executed; i.e., the values in the output registers are moved into the input registers. Similarly, on a restore instruction, the values of the input registers are are moved to the output registers, and values of the frame pointer and stack pointer register are restored to tear down the called function's stack frame. Figure 4.5 describes register overlapping before and after a save instruction is executed on a function call.

Fig. 4.5: Register overlapping in a SPARC ISA-based architecture

That behavior is not exactly what SPARC processors do (because SPARC processors push the oldest set of used registers onto the stack frame). But the current design does not introduce any false negatives (i.e., it does not compromise an application's critical signature, and hence no critical memory locations are eliminated) because register spilling is forced on every function call. In a very conservative analysis, the bottom 64 bytes of every new stack frame allocated must be included in the application signature and then invalidated as soon as the stack frame is torn down. In most critical applications, objects allocated on stack memory usually are associated with temporary calculations and are not that critical to the application's security. If an object is indeed a critical variable, then it is guaranteed to be included in the application's signature until the function stack frame is alive; after returning to the caller, the stack frame (for the called function) is free to be used. In usual programming practice, data are never accessed

(by reference) from a lost stack frame; hence the correct design is to prevent such memory locations from being part of the application's signature.

#### **4.4 Error Injection**

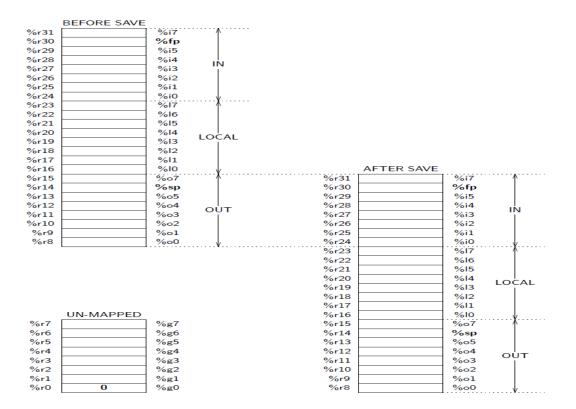

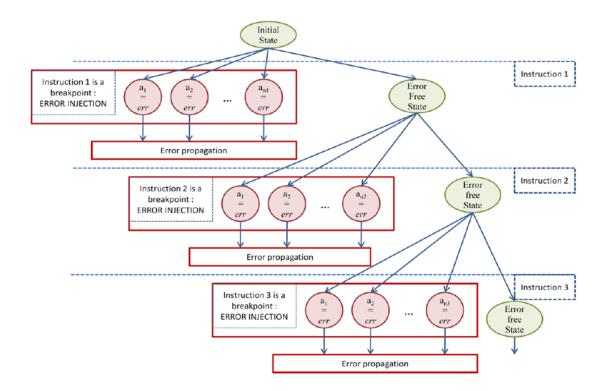

The error injection mechanism mimics the behavior of existing fault injectors such as NFTAPE [65]. SymPLFIED uses symbolic fault injection. A breakpoint is set at a given application's execution point. When the breakpoint is reached, the *err* symbol is injected at one memory location. Then, the application's execution resumes propagating the error.

#### 4.4.1 Error Injection Mechanism

At each run, the user is able to specify where to inject the symbolic error (into the register, memory or the program counter). In this technique, as we wish to model memory corruption attacks, we only consider memory errors. The user can also specify when to inject the error by setting breakpoints. By default, SymPLFIED exhaustively and successively injects errors at every available memory location and at every possible breakpoint. Figure 4.6 illustrates the exhaustive fault injection process. Within each state,  $a_i$  denotes memory location *i* and  $a_i = err$  denotes the fact that the memory location  $a_i$  contains the error symbol. Note that there is at most one error injected on each path of the state diagram (Figure 4.6).

Fig. 4.6: State diagram of error injection of all memory addresses at all possible breakpoints

The initial state is a state in which no instruction has been executed yet. After instruction 1 is executed, n1 + 1 states can be reached from the initial state (n1 being the number of memory locations available). In the n1 state, a unique symbolic error *err* is injected. In the first state, an error is injected into memory location 1, and in the  $i^{th}$  state, an error is injected into memory location 1, and in the  $i^{th}$  state, an error is injected into memory location *i*. Once injected, each error is propagated independently from the others. The  $(n1 + 1)^{th}$  state is an error-free state from which new states are forked after the execution of the second instruction. Table 4.1 gives the injection commands defined in SymPLFIED. The "Search" command defined in Maude enables us to explore all reachable states from the initial state given the specified injections.

Table 4.1: Basic commands to inject memory errors in SymPLFIED

| Maude commands                                                                                                     | Explanation                                                                                                                                                                                               |  |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Search allMemoryErrors (program,<br>first, input) =>! (S:State)                                                    | , Search all reachable states after injecting one<br>and only one symbolic error into all possible<br>memory locations at all possible breakpoints.                                                       |  |

| Search allMemoryErrors(program,<br>first, input) =>! (S:State) such that<br>getException(S:State) == noException . | Search all reachable states where the exception<br>field is equal to 'no exception' after injecting one<br>and only one symbolic error into all possible<br>memory locations at all possible breakpoints. |  |

| Search allMemoryErrosWithin<br>(program, first, input, pcmin, pcmax)<br>=>! (S:State)                              | Search all reachable states after injecting one<br>and only one symbolic error into all possible<br>memory locations and where breakpoints PCs<br>are between <i>pcmin</i> and <i>pcmax</i> .             |  |

# 4.4.2 Error Propagation

Once the error has been injected into the program, the error is propagated. Every operation involving *err* will return error expressions merging *err* symbols (e.g., err + 2 = err, err + err = err).

The interesting part of the error propagation is the way the tool handles branching or comparison involving the *err* symbol. When branching and comparison are not involved, merging expressions into *err* is sufficient. But if we need to evaluate a predicate in order to determine how to branch, merging of expressions into *err* is no longer possible. SymPLFIED uses rules to fork the execution when evaluating a predicate that involves the *err* symbol; in other words, a predicate containing an *err* symbol is evaluated to both true and false.

# 4.4.3 SymPLFIED Outputs

SymPLFIED logs the result of the error injection experiments. The results enumerate all the cases that match the search criteria, for example, attacks that were successful in modifying the critical variable. The logged results describe the precise instructions and the memory locations at

which the errors were injected; hence, one can identify the critical instructions and the corresponding memory locations with which they are associated. The critical instruction signature and data signature for the application are formed by the set of instructions and memory locations that upon error injection were successful in exploiting the application's vulnerability, for example by changing the system password in the SSH program. The check instructions encoding this information are used to instrument the original application, which, upon execution, configures the IFS hardware module and enforces runtime checking.

SymPLFIED considers the effect of all possible transient hardware errors on computation. Our focus in this thesis is on memory-corruption-related errors when a program is being executed under a specific input. SymPLFIED uses symbolic execution and model-checking to exhaustively reason about the effect of the error on the program. The key innovation of SymPLFIED is that it combines an entire set of errors into a single abstract class and symbolically reasons about the effects of the error class as a whole. This grouping effectively collapses into a single state the entire set of errors, in turn greatly enhancing the scalability of SymPLFIED compared to exhaustive fault injection. However, the scalability is obtained at the cost of accuracy, as this abstraction can lead to false positives, i.e., erroneous outcomes that occur in the model but not in the real system. However, the loss in accuracy is acceptable in practice, as the detectors can be conservatively overdesigned to protect against a few false positives.

#### **4.5 SymPLFIED vs. Compiler Static Analysis**

Compared to previous work (namely software implementation, as discussed in Chapter 3), computation of the backward slice of a critical variable in the program based on static analysis has certain limitations, such as intra-procedural slicing, conditional dependencies of a control flow path that computes critical variables and difficulties in Pointer analysis. The proposed method of having exhaustive symbolic fault injection running over model checker overcomes most of those limitations, as discussed below.

- 1. Intra-procedural slicing: The IFS technique considers only intra-procedural slices; i.e., it truncates the slice at the beginning of functions. Hence, any corruption of the slice prior to the function call will not be detected by the technique. There are different ways of mitigating the impact of this using function in-lining, which is not practical for large pieces of code. The user can choose critical variables in each function, but again that is not practical for millions of lines of application software. From the perspective of SymPLFIED analysis, the function boundaries are transparent. The analysis is done at the abstraction level of instructions that modify memory locations. Function boundaries are transparent to such a design approach and hence obviate the limitation presented by the static compiler analysis methodology.

- 2. Annotation of critical instructions at the RTL level gives finer granularity and precision than the backward slices given by static analysis of compiler-generated intermediate code representation of an application's source code. Even the intermediate representation used for analysis of routines is a relatively high level of code and does not exactly represent the change in the architectural state of the processor during execution of an application. To ensure the integrity of critical data, it is important that no window of vulnerability be

left open during runtime checking; hence, it is better to have more fine-tuned analysis, such as checking at the instruction level. The RTL-level-checking approach described in this thesis presents a better picture of the architectural state of a processor and is more suited to solving the problem of eliminating all windows of vulnerability.

3. The analysis of an application or a part of the application that is the trusted module using SymPLFIED is complete in the sense that it includes all conditional dependencies for which a static analysis using the compilers cannot account. The control flow fault is the backdoor for most of the crafted attacks and hence requires a method that can include all possible dependencies for a critical variable.

```

int main()

int critical = 0;

int temp, a;

scanf(%d,&temp);

a = foo(temp); // foo() - 3<sup>rd</sup> party library function

if(*a > 0)

critical = critical + 1:

else

critical = critical - 1;

if(critical == 1){

printf("authenticated");

//Execute Shell or other system code

---- :

-----: }

else

printf("User denied");

return critical; }

```

Fig 4.7: Example code exposing the limitation of compiler static analysis approach

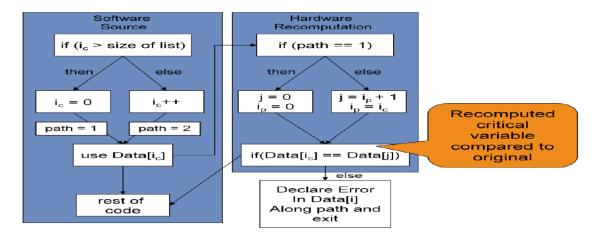

In the piece of code in Figure 4.7, neither the value of variable a nor the memory location of the variable a is a part of the backward slice computed for the critical variable. Hence it is easy to craft an attack by corrupting the memory location a. Such dependencies are not represented in the backward slice generated by compiler analysis techniques.

4. Another big limitation of the backward slices produced using compiler techniques is the level of indirection of pointers supported (points-to analysis) and pointer alias analysis.

Even a compiler with advanced pointer analysis capabilities, like IMPACT or LLVM, cannot guarantee memory safety with a given backward slice.

- **Pointer-alias analysis**: \*(critical) and \*(xyz\_variable) (where xyz\_variable is any random pointer variable) can both point to the same critical object, but there can be cases where xyz\_variable is never a part of the backward slice or even a part of the source code (e.g., xyz\_variable is a part of the dynamically loaded shared library), as seen in the example in Figure 4.7.

- **Points-to analysis**: The variables (a, critical: in the piece of code in Figure 4.7) can have multiple levels of indirection (which is very common in industry software written in C++). One can compromise the integrity of the system by corrupting the memory location at any level of indirection of those pointers; the pointers may or may not be a part of the backward slice, depending on the level of indirection supported by the compilers.

We overcome all these limitations because symbolic fault injection gives us all the possible memory locations that can compromise an application's integrity, and hence we can annotate all the critical instructions that are accessing a particular memory location and need to be protected. All the memory locations that we need to protect are determined by SymPLFIED analysis. Also, the set of attack scenarios simulated by SymPLFIED is a superset of the real-world attacks.

# **CHAPTER 5**

# **RELIABILITY AND SECURITY ENGINE (RSE)**

The RSE used to evaluate the IFS technique is implemented on the Leon 3 soft processor [6]. This chapter introduces the Leon 3 processor we used as the RSE development platform, in this thesis, and describes the RSE implementation for the Leon 3, including the details of the CHK instruction used by an application to communicate with RSE modules.

# 5.1 The Leon 3 Processor

The Gaisler Research Leon 3 processor was chosen as the new RSE development platform because of its clear and concise documentation, easy-to-use tools, preconfigured FPGA synthesis examples, operating system support, large development community, and active mailing list. The GRLIB peripheral library included with this processor has an Ethernet controller, video graphics array (VGA) controller, several types of memory controllers, and a significant number of device controllers and interfaces. The AMBA bus standard is used for all peripherals in GRLIB. The hardware description of the entire GRLIB was written in very high-speed integrated circuit hardware description language (VHDL) using a special two-process state machine format developed at Gaisler research [66]. The Leon 3 processor implements the SPARC v8 instruction set. It is a seven-stage pipelined processor with configurable caches, a floating point unit. The seven stages of the processor and their functionalities are as follows:

- Fetch: The first stage of the processor controls the instruction cache and does program counter calculations, including loading of branch addresses and changing of addresses for exception handling.

- **Decode:** This stage decodes the instructions into microcode to be used by the processor as control signals, determines branch instructions, and loads the addresses for register access.

- **Register file access:** Operands to each instruction are loaded by the Register File Access stage. This stage handles register bypassing from the execution unit and retrieves and pads immediate values from the instruction to be used as operands.

- **Execute:** Arithmetic and logical operations are processed in the Execute stage. Floating point instructions and addressing for the data cache and branch instructions are calculated are also calculated at this time.

- **Memory:** The Memory stage generates control signals for the data cache and generates the appropriate interrupt control signals for the following stage.

- **Exception:** Traps for interrupts and exceptions are generated in the Exception stage. The final address calculations are made here before they are sent back to the Fetch stage. This stage also generates the signals used by the Writeback stage to control the register file.

- Writeback: Results of instructions are written back to the register file in this stage.

### **5.2 The Reliability and Security Engine**

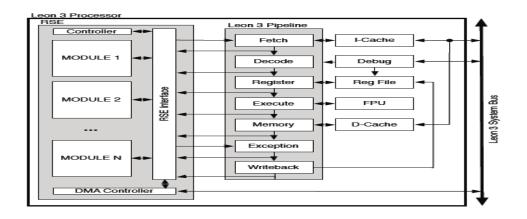

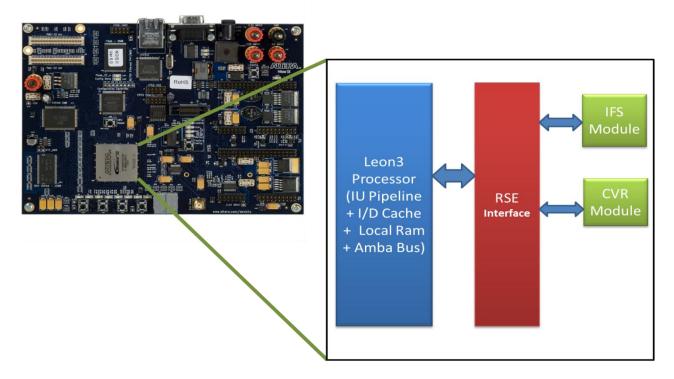

The Reliability and Security Engine (RSE) [6] is a framework that provides a standard interface between a processor pipeline and hardware modules that implement reliability and security services for the executing application. Figure 5.1 provides a block diagram of the RSE connected to the Gaisler Research Leon 3 open-source VHDL processor pipeline. The modules are running alongside the host processor, monitoring the behavior of the executing application. Although shown with the Leon 3, the RSE framework is general enough to be integrated with any general-purpose processor. Additionally, the RSE is nonintrusive to the main processor pipeline, as it only needs to monitor execution behavior. It does so by inserting probes into the pipeline of the host processor that continuously transfers selected state information to the RSE modules.

Reconfigurable hardware slices similar to those in an FPGA may be used to implement the modules, allowing for instantiation of the desired modules based on the requirements of the current application. Alternatively, a module can be implemented as an ASIC IP core, which is imported by a processor designer to suit the demands imposed by the customers and the market. In our design, we override the SPARC v8 instruction set architecture's co-processor operation instruction (CPOP1), converting it into a CHK instruction. This CHK instruction is used for communication between an instrumented application and the RSE modules. It is ignored by the main pipeline of the processor and considered a NOP. The CHK instructions are uniquely identified to specify the modules for which they are intended. For example, during application initialization, the Information Flow Signatures technique uses CHK instructions to convey the signatures of the trusted instructions and critical data that are required to enforce the checks in hardware.

Fig. 5.1: RSE framework

The RSE also contains a DMA controller connected to the system bus in parallel with the processor. With the RSE, module designers need not worry about making direct changes to a processor pipeline. This allows one to focus on the performance of only the components being added, rather than their interaction with the rest of the processor. Additionally, the RSE minimizes the intrusiveness of developing new techniques, which decreases the chances of RSE module designers introducing errors that affect the functionality of the chip in unexpected ways.

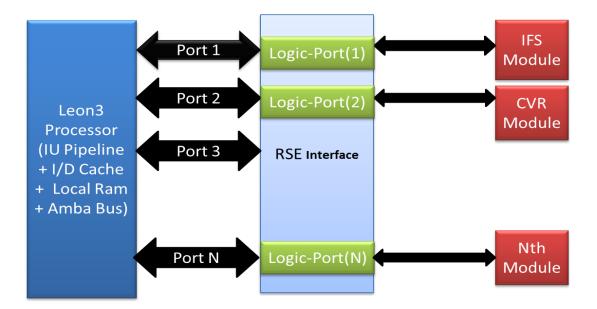

Fig. 5.2: New RSE architecture

The concept of RSE as an interface to tap in to the pipeline signals remains the same, but the architectural interface has been modified to make it easier to extend the RSE interface to incorporate new modules for different kinds of monitoring tools without requiring any changes in the original source code of the hardware. Figure 5.2 describes the modified architecture for the RSE framework. Hence, for a new user who wants to add a module, it is easier to code the module without making any changes in the original RSE interface code.

The advantage of having an interface like RSE is that it is very easily extensible. RSE has been implemented such that it is possible to add customized ports by concatenating the bits of required control signals from the pipeline to form a customized bundle of signals for a particular port. Each individual port can have its own associated logic to control a custom module designed for monitoring purposes. This design methodology also eases the use of the interface with a new monitoring tool where the user does not have to modify any of the original code and instead just needs to define its own port and custom control logic associated with the tool. As a result, the RSE interface does not add any performance overhead in the execution of the main application. Communication with the RSE interface depends on the instrumented CHECK instructions. Each module has its own check decoders and handlers, which allows the user to conveniently switch modules on and off at will. A program not instrumented with CHECK instructions executes as if it were oblivious to the existence of such a monitoring interface. The current implementation of RSE controls two different modules: IFS for secure computation of the critical data, and CVR (critical value recomputation) [67] for reliable computation of data. More details on integrating the reliability module (CVR) with the security module to achieve both secure and reliable computing are presented in Chapter 8.

# **CHAPTER 6**

# INFORMATION FLOW SIGNATURE MODULE: ARCHITECTURE

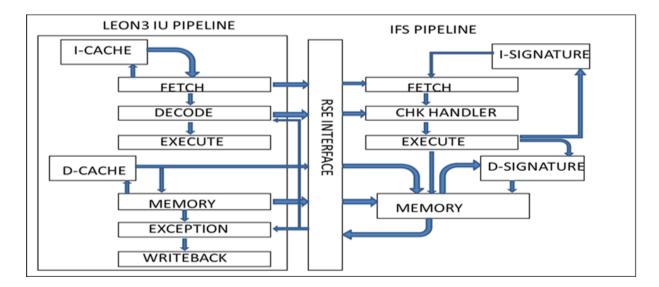

The Information Flow Signature (IFS) technique is implemented using a combination of hardware and software. The hardware implementation requires the addition of a special CHK instruction to the instruction set of the processor, but no other direct modifications to the pipeline. The critical signature is loaded from an instrumented program at load time by using the CHK instruction (recall that the program load path is trusted). CHK instructions are interpreted as no-operations by the main processor, and thus are to be used only by the checking module as it snoops on signals from the main processor. The processor's caches are not modified. Instead, a content addressable memory (CAM) outside of the processor's pipeline is used to store the critical signature of the application being executed. The check is implemented in hardware, which guarantees that the check does not add performance overhead and is performed on every executed instruction. The IFS module itself is implemented as pipelined stages similar to those of Leon3 to maintain coherency with the main integer unit pipeline. This module snoops required signals from the Leon 3 processor pipeline through a generic interface (RSE) to control its own pipelined stages. These signals include 1) the current instruction and its pointer, 2) pipeline stall and flush, and 3) cache control. Signals are used directly from the processor's pipeline without modifications. Outputs from the checking module trigger an error signal if a critical variable (that is included in the application's critical data signature) is corrupted, which in turn raises the integer unit trap signal to stall the propagation of the error to the register files and other memory locations. The Check instructions through which the IFS module is configured

from the main processor pipeline are implemented as C macros, as shown in Figure 6.1. These C macros contain the critical information about the signature needed to configure the instruction signature and data signature modules within IFS that enforce runtime checking of the security-critical variables. These CHK instructions are overwritten coprocessor instructions provided by the Leon3-SPARC V8 ISA; after the decode stage of the main pipeline they are transformed to NOP instructions and hence do not modify the processor state during the execution.

#define chk(top5, low19) ".word 0x81B00000 + ((" top5 " & 0x1F) << 25) + ((" low19 ") & 0x7FFFF)"

asm(chk("0x09", "0x41f808e0"));

asm(chk("0x09", "0x41f8099c"));</pre>

Fig. 6.1: C Macro for the CHECK instruction and the example CHECK instruction

### **6.1 Critical Signature**

In this section, we discuss the critical signature for an application source code. The critical signature has two components: the *instruction signature* and the *data signature*. CHK instructions have been implemented to configure the instruction signature and data signature during the initial loading of the program. The *instruction signature* is fully configured at the beginning of the program by means of a dump file that marks the critical program counters that are virtual addresses. The design has been implemented such that one need not bother about the address translation mechanism by the MMU. The *data signature*, on the other hand, can be configured statically using check instructions to protect global and initialized memory locations that contain critical global data that are required for the application and can be found in the dump files. (Dump files are produced by generating an assembly dump from the source code, from which one can find the relative offsets and relative addresses for critical variables. These relative addresses are then used to configure the critical data signature in the IFS module.) Since the